Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | <u>.</u>                                                                   |

| Peripherals                | POR, WDT                                                                   |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 64 x 8                                                                     |

| RAM Size                   | 68 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 18-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f84at-04-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

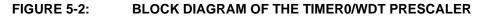

#### 5.2.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on the fly" during program execution).

Note: To avoid an unintended device RESET, a specific instruction sequence (shown in the PIC<sup>®</sup> Mid-Range Reference Manual, DS33023) must be executed when changing the prescaler assignment from Timer0 to the WDT. This sequence must be followed even if the WDT is disabled.

#### 5.3 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit T0IF (INTCON<2>). The interrupt can be masked by clearing bit T0IE (INTCON<5>). Bit T0IF must be cleared in software by the Timer0 module Interrupt Service Routine before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from SLEEP since the timer is shut-off during SLEEP.

#### TABLE 5-1: REGISTERS ASSOCIATED WITH TIMER0

| Address | Name       | Bit 7                  | Bit 6  | Bit 5 | Bit 4                         | Bit 3 | Bit 2 | Bit 1     | Bit 0     | Value on<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|---------|------------|------------------------|--------|-------|-------------------------------|-------|-------|-----------|-----------|-------------------------|---------------------------------|

| 01h     | TMR0       | Timer0 Module Register |        |       |                               |       |       | xxxx xxxx | uuuu uuuu |                         |                                 |

| 0Bh,8Bh | INTCON     | GIE                    | EEIE   | T0IE  | INTE                          | RBIE  | T0IF  | INTF      | RBIF      | 0000 000x               | 0000 000u                       |

| 81h     | OPTION_REG | RBPU                   | INTEDG | TOCS  | T0SE                          | PSA   | PS2   | PS1       | PS0       | 1111 1111               | 1111 1111                       |

| 85h     | TRISA      |                        | _      | _     | PORTA Data Direction Register |       |       | 1 1111    | 1 1111    |                         |                                 |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

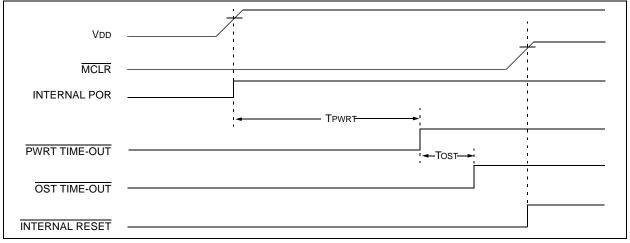

FIGURE 6-7: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

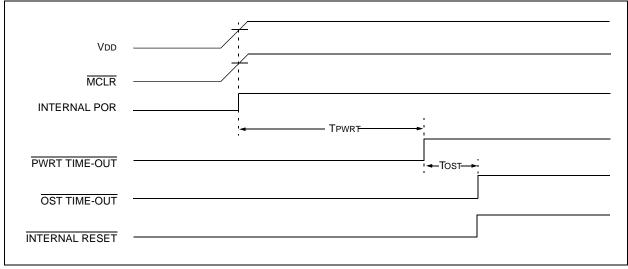

FIGURE 6-8: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD): FAST VDD RISE TIME

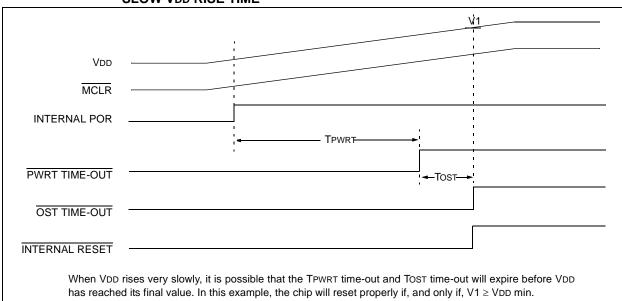

#### FIGURE 6-9: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD): SLOW VDD RISE TIME

### 6.7 Time-out Sequence and \_\_\_\_\_ Power-down Status Bits (TO/PD)

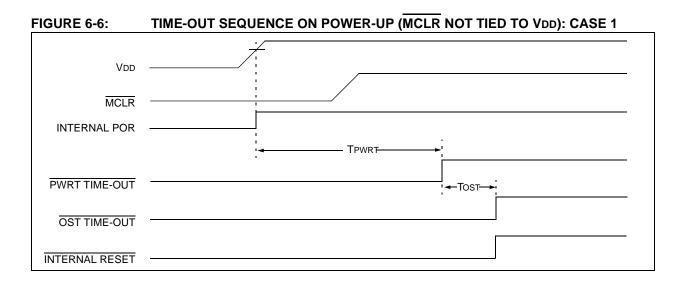

On power-up (Figures 6-6 through 6-9), the time-out sequence is as follows:

- 1. PWRT time-out is invoked after a POR has expired.

- 2. Then, the OST is activated.

The total time-out will vary based on oscillator configuration and PWRTE configuration bit status. For example, in RC mode with the PWRT disabled, there will be no time-out at all.

# TABLE 6-5:TIME-OUT IN VARIOUSSITUATIONS

| Oscillator    | Powe                | Wake-up          |               |  |

|---------------|---------------------|------------------|---------------|--|

| Configuration | PWRT<br>Enabled     | PWRT<br>Disabled | from<br>SLEEP |  |

| XT, HS, LP    | 72 ms +<br>1024Tosc | 1024Tosc         | 1024Tosc      |  |

| RC            | 72 ms               | _                | _             |  |

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then bringing  $\overline{\text{MCLR}}$  high, execution will begin immediately (Figure 6-6). This is useful for testing purposes or to synchronize more than one PIC16F84A device when operating in parallel.

Table 6-6 shows the significance of the  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits. Table 6-3 lists the RESET conditions for some special registers, while Table 6-4 lists the RESET conditions for all the registers.

TABLE 6-6: STATUS BITS AND THEIR SIGNIFICANCE

| то | PD | Condition                           |  |  |  |

|----|----|-------------------------------------|--|--|--|

| 1  | 1  | Power-on Reset                      |  |  |  |

| 0  | x  | llegal, TO is set on POR            |  |  |  |

| х  | 0  | legal, PD is set on POR             |  |  |  |

| 0  | 1  | NDT Reset (during normal operation) |  |  |  |

| 0  | 0  | NDT Wake-up                         |  |  |  |

| 1  | 1  | MCLR during normal operation        |  |  |  |

| 1  | 0  | MCLR during SLEEP or interrupt      |  |  |  |

|    |    | wake-up from SLEEP                  |  |  |  |

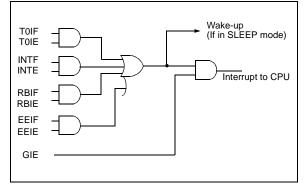

#### 6.8 Interrupts

The PIC16F84A has 4 sources of interrupt:

- External interrupt RB0/INT pin

- TMR0 overflow interrupt

- PORTB change interrupts (pins RB7:RB4)

- Data EEPROM write complete interrupt

The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also contains the individual and global interrupt enable bits.

The global interrupt enable bit, GIE (INTCON<7>), enables (if set) all unmasked interrupts or disables (if cleared) all interrupts. Individual interrupts can be disabled through their corresponding enable bits in INTCON register. Bit GIE is cleared on RESET.

The "return from interrupt" instruction, RETFIE, exits interrupt routine as well as sets the GIE bit, which re-enables interrupts.

The RB0/INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with 0004h. For external interrupt events, such as the RB0/INT pin or PORTB change interrupt, the interrupt latency will be three to four instruction cycles. The exact latency depends when the interrupt event occurs. The latency is the same for both one and two cycle instructions. Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid infinite interrupt requests.

Note: Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

#### FIGURE 6-10: INTERRUPT LOGIC

#### 6.8.1 INT INTERRUPT

External interrupt on RB0/INT pin is edge triggered: either rising if INTEDG bit (OPTION\_REG<6>) is set, or falling if INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, the INTF bit (INTCON<1>) is set. This interrupt can be disabled by clearing control bit INTE (INTCON<4>). Flag bit INTF must be cleared in software via the Interrupt Service Routine before re-enabling this interrupt. The INT interrupt can wake the processor from SLEEP (Section 6.11) only if the INTE bit was set prior to going into SLEEP. The status of the GIE bit decides whether the processor branches to the interrupt vector following wake-up.

#### 6.8.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in TMR0 will set flag bit T0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit T0IE (INTCON<5>) (Section 5.0).

#### 6.8.3 PORTB INTERRUPT

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit RBIE (INTCON<3>) (Section 4.2).

Note: For a change on the I/O pin to be recognized, the pulse width must be at least TCY wide.

#### 6.8.4 DATA EEPROM INTERRUPT

At the completion of a data EEPROM write cycle, flag bit EEIF (EECON1<4>) will be set. The interrupt can be enabled/disabled by setting/clearing enable bit EEIE (INTCON<6>) (Section 3.0).

#### 6.11.3 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake-up from SLEEP. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

#### 6.12 Program Verification/Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

### 6.13 ID Locations

Four memory locations (2000h - 2004h) are designated as ID locations to store checksum or other code identification numbers. These locations are not accessible during normal execution but are readable and writable only during program/verify. Only the four Least Significant bits of ID location are usable.

### 6.14 In-Circuit Serial Programming

PIC16F84A microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground, and the programming voltage. Customers can manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product, allowing the most recent firmware or custom firmware to be programmed.

For complete details of Serial Programming, please refer to the In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) Guide, (DS30277).

NOTES:

| RLF              | Rotate Left f through Carry                                                                                                                                                                                                          |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RLF f,d                                                                                                                                                                                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                      |

| Operation:       | See description below                                                                                                                                                                                                                |

| Status Affected: | С                                                                                                                                                                                                                                    |

| Description:     | The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry Flag. If 'd' is 0, the<br>result is placed in the W register.<br>If 'd' is 1, the result is stored back<br>in register 'f'.<br>- C - Register f |

| SUBLW            | Subtract W from Literal                                                                                                      |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] SUBLW k                                                                                                     |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                          |  |  |  |  |  |

| Operation:       | $k \text{ - } (W) \to (W)$                                                                                                   |  |  |  |  |  |

| Status Affected: | : C, DC, Z                                                                                                                   |  |  |  |  |  |

| Description:     | The W register is subtracted (2's complement method) from the eight-bit literal 'k'. The result is placed in the W register. |  |  |  |  |  |

| RRF              | Rotate Right f through Carry                                                                                                                                                                                      |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RRF f,d                                                                                                                                                                                                   |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                   |

| Operation:       | See description below                                                                                                                                                                                             |

| Status Affected: | С                                                                                                                                                                                                                 |

| Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry Flag. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'. |

|                  | C Register f                                                                                                                                                                                                      |

| SUBWF            | Subtract W from f                                                                                                                                                                         |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] SUBWF f,d                                                                                                                                                                |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                         |

| Operation:       | (f) - (W) $\rightarrow$ (destination)                                                                                                                                                     |

| Status Affected: | C, DC, Z                                                                                                                                                                                  |

| Description:     | Subtract (2's complement method)<br>W register from register 'f'. If 'd' is 0,<br>the result is stored in the W regis-<br>ter. If 'd' is 1, the result is stored<br>back in register 'f'. |

#### SLEEP

| Syntax:          | [ label ] SLEEP                                                                                                                                                                                                                      |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | None                                                                                                                                                                                                                                 |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \ \text{prescaler}, \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                                                          |

| Status Affected: | TO, PD                                                                                                                                                                                                                               |

| Description:     | The power-down status bit, $\overline{\text{PD}}$ is cleared. Time-out status bit, $\overline{\text{TO}}$ is set. Watchdog Timer and its prescaler are cleared.<br>The processor is put into SLEEP mode with the oscillator stopped. |

| SWAPF            | Swap Nibbles in f                                                                                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] SWAPF f,d                                                                                                                                                   |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                              |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                                      |

| Status Affected: | None                                                                                                                                                                         |

| Description:     | The upper and lower nibbles of<br>register 'f' are exchanged. If 'd' is<br>0, the result is placed in W regis-<br>ter. If 'd' is 1, the result is placed in<br>register 'f'. |

# PIC16F84A

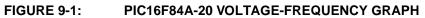

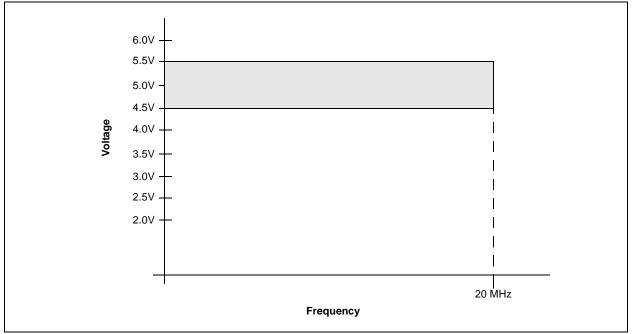

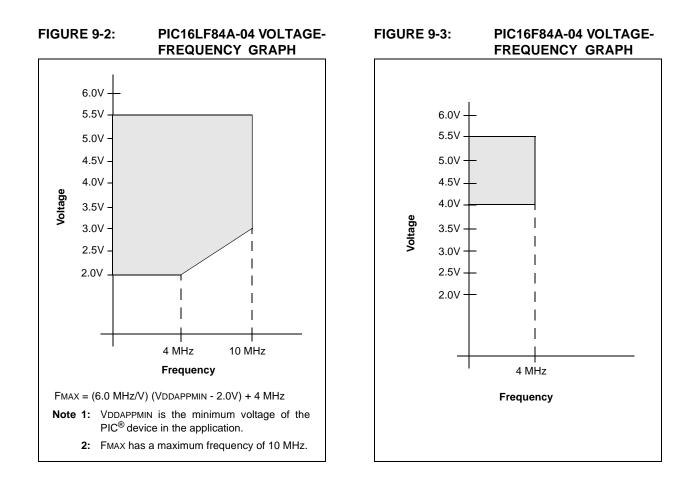

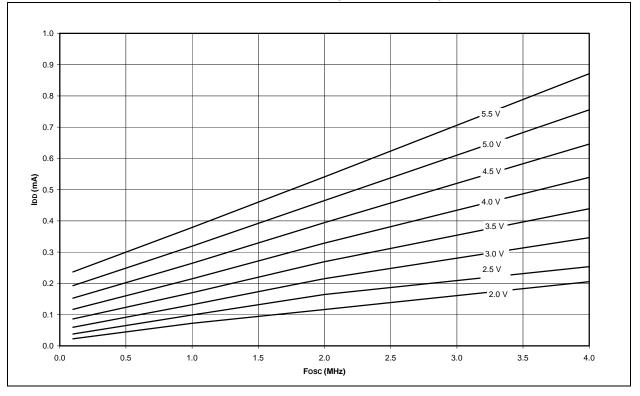

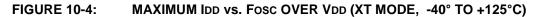

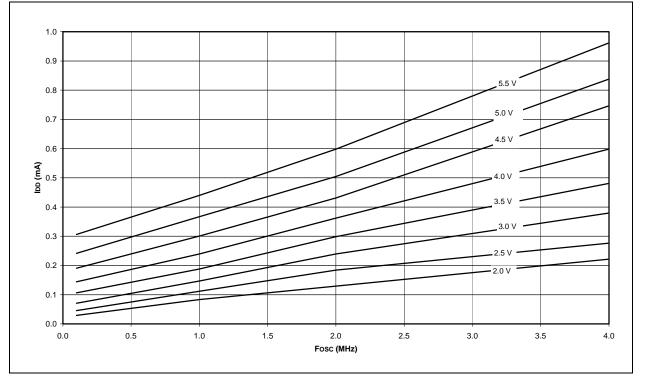

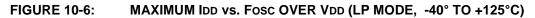

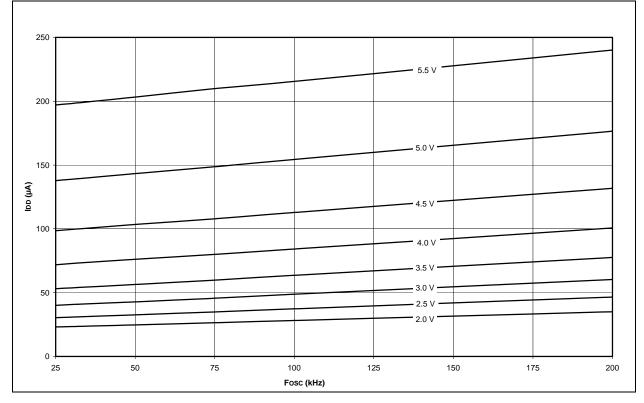

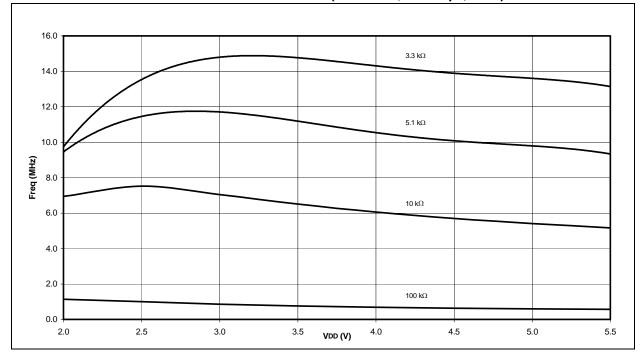

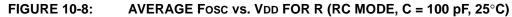

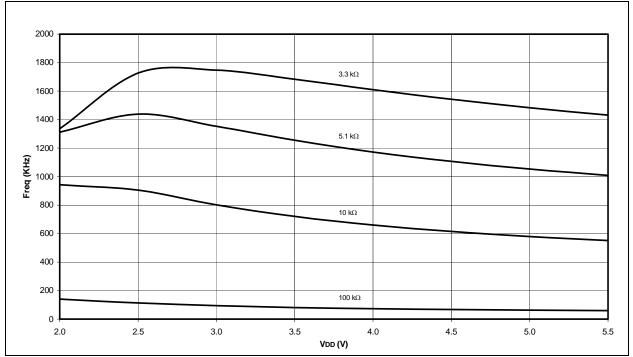

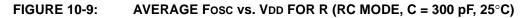

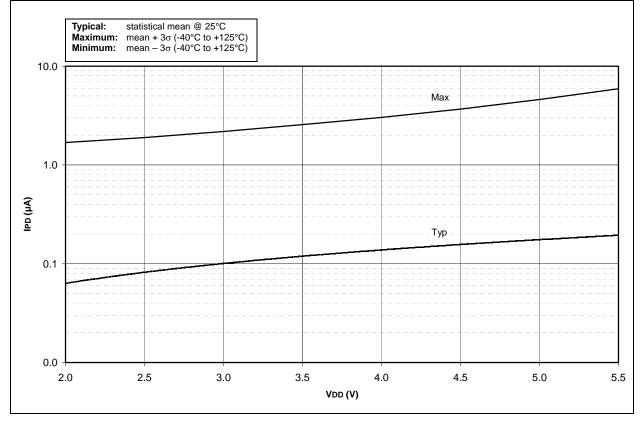

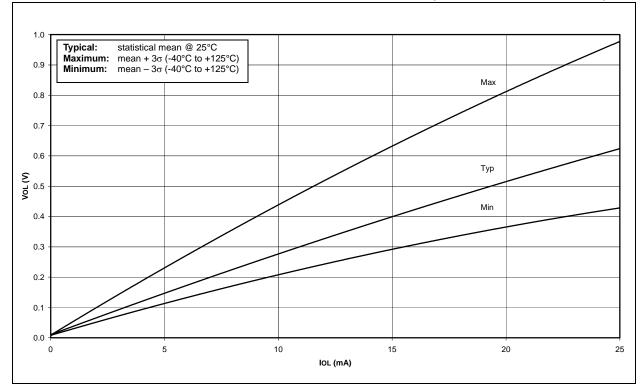

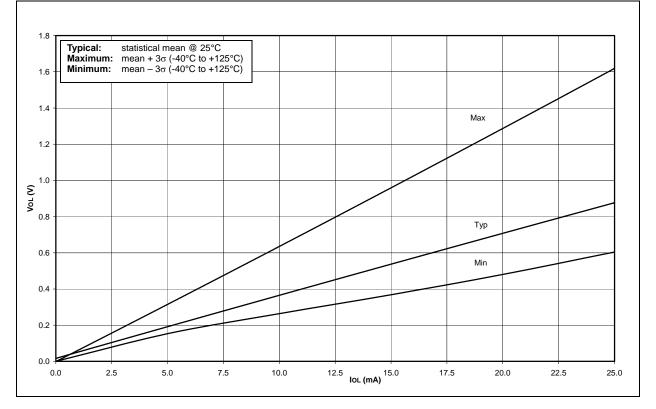

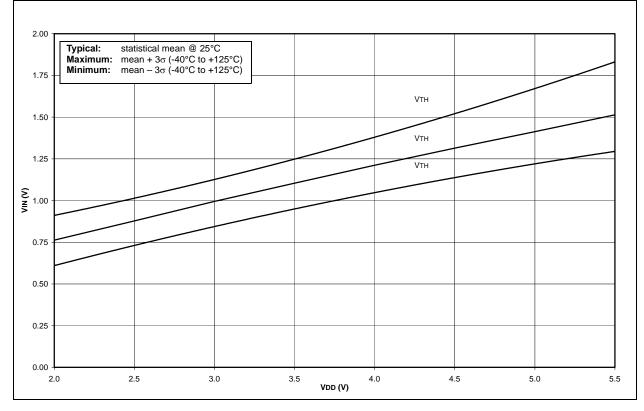

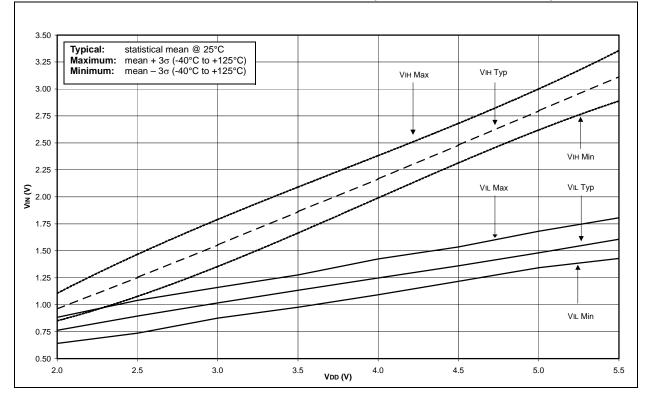

# 10.0 DC/AC CHARACTERISTIC GRAPHS

The graphs provided in this section are for **design guidance** and are **not tested**.

In some graphs, the data presented are **outside specified operating range** (i.e., outside specified VDD range). This is for **information only** and devices are ensured to operate properly only within the specified range.

The data presented in this section is a **statistical summary** of data collected on units from different lots over a period of time and matrix samples. 'Typical' represents the mean of the distribution at 25°C. 'Max' or 'Min' represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ), respectively, where  $\sigma$  is a standard deviation over the whole temperature range.

FIGURE 10-3: TYPICAL IDD vs. Fosc OVER VDD (XT MODE, 25°C)

© 2001-2013 Microchip Technology Inc.

FIGURE 10-5: TYPICAL IDD vs. Fosc OVER VDD (LP MODE, 25°C)

FIGURE 10-7: AVERAGE FOSC vs. VDD FOR R (RC MODE, C = 22 pF, 25°C)

# PIC16F84A

FIGURE 10-15: TYPICAL, MINIMUM AND MAXIMUM Vol vs. Iol (VDD = 5V, -40°C TO +125°C)

FIGURE 10-18: MINIMUM AND MAXIMUM VIN vs. VDD (ST INPUT, -40°C TO +125°C)

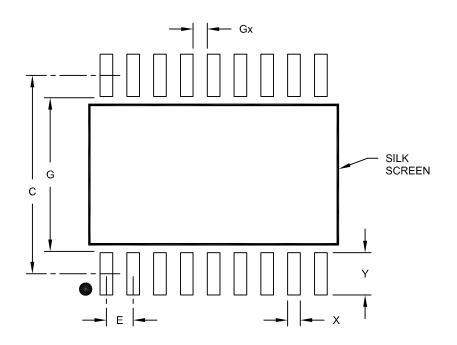

18-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                       | Units            |          |      | MILLIMETERS |  |  |  |

|-----------------------|------------------|----------|------|-------------|--|--|--|

| Dimension             | Dimension Limits |          | NOM  | MAX         |  |  |  |

| Contact Pitch E       |                  | 1.27 BSC |      |             |  |  |  |

| Contact Pad Spacing   | С                |          | 9.40 |             |  |  |  |

| Contact Pad Width     | Х                |          |      | 0.60        |  |  |  |

| Contact Pad Length    | Y                |          |      | 2.00        |  |  |  |

| Distance Between Pads | Gx               | 0.67     |      |             |  |  |  |

| Distance Between Pads | G                | 7.40     |      |             |  |  |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2051A

# PIC16F84A

| Prescaler, Timer0                |

|----------------------------------|

| Assignment (PSA Bit)9            |

| Rate Select (PS2:PS0 Bits)9      |

| Program Counter 11               |

| PCL Register7, 11, 25            |

| PCLATH Register7, 11, 25         |

| Reset Conditions24               |

| Program Memory5                  |

| General Purpose Registers6       |

| Interrupt Vector 5, 29           |

| RESET Vector5                    |

| Special Function Registers 6, 7  |

| Programming, Device Instructions |

# R

| RAM. See Data Memory                           |

|------------------------------------------------|

| Reader Response                                |

| Register File                                  |

| Register File Map 6                            |

| Registers                                      |

| Configuration Word 21                          |

| EECON1 (EEPROM Control)13                      |

| INTCON                                         |

| OPTION                                         |

| STATUS                                         |

| Reset                                          |

| Block Diagram24, 26                            |

| MCLR Reset. See MCLR                           |

| Power-on Reset (POR). See Power-on Reset (POR) |

| Reset Conditions for All Registers 25          |

| Reset Conditions for Program Counter           |

| Reset Conditions for STATUS Register 24        |

| WDT Reset. See Watchdog Timer (WDT)            |

| Revision History                               |

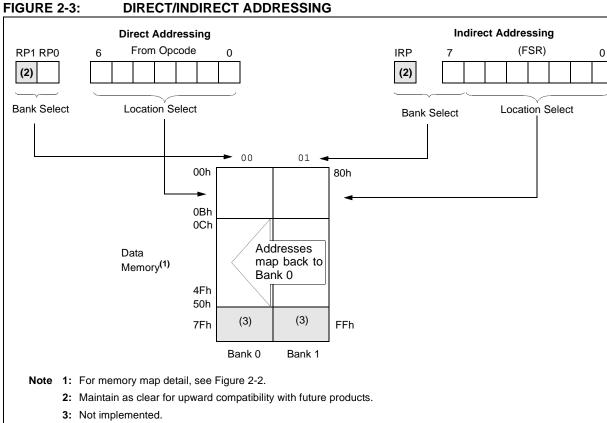

| RP1:RP0 (Bank Select) bits                     |

# S

| Saving W Register and STATUS in R |   |

|-----------------------------------|---|

| SLEEP                             |   |

| Software Simulator (MPLAB SIM)    |   |

| Special Features of the CPU       |   |

| Special Function Registers        |   |

| Speed, Operating                  |   |

| Stack                             |   |

| STATUS Register                   |   |

| C Bit                             | 8 |

| DC Bit                            |   |

| PD Bit                            |   |

| Reset Conditions                  |   |

| RP0 Bit                           | 6 |

| TO Bit                            |   |

| Z Bit                             |   |

### Т

Time-out (TO) Bit. See Power-on Reset (POR) Timer0.....

| mer0                                | 19        |

|-------------------------------------|-----------|

| Associated Registers                |           |

| Block Diagram                       |           |

| Clock Source Edge Select (T0SE Bit) | 9         |

| Clock Source Select (T0CS Bit)      | 9         |

| Overflow Enable (T0IE Bit)          | 10, 29    |

| Overflow Flag (T0IF Bit)            |           |

| Overflow Interrupt                  | 20, 29    |

| Prescaler. See Prescaler            |           |

| RA4/T0CKI Pin, External Clock       | 19        |

| TMR0 Register                       | 7, 20, 25 |

| Timing Conditions                          | 54     |

|--------------------------------------------|--------|

| Timing Diagrams                            |        |

| CLKOUT and I/O                             | 56     |

| Diagrams and Specifications                | 55     |

| CLKOUT and I/O Requirements                | 56     |

| External Clock Requirements                |        |

| RESET, Watchdog Timer, Oscillator          |        |

| Start-up Timer and Power-up                |        |

| Timer Requirements                         | 57     |

| Timer0 Clock Requirements                  | 58     |

| External Clock                             | 55     |

| RESET, Watchdog Timer, Oscillator Start-up |        |

| Timer and Power-up Timer                   | 57     |

| Time-out Sequence on Power-up              | 27, 28 |

| Timer0 Clock                               |        |

| Wake-up From Sleep Through Interrupt       | 32     |

| Timing Parameter Symbology                 | 53     |

| TO bit                                     |        |

|                                            |        |

# W

| W Register                  | 25, 30             |

|-----------------------------|--------------------|

| Wake-up from SLEEP          | 21, 26, 28, 29, 32 |

| Interrupts                  |                    |

| MCLR Reset                  |                    |

| WDT Reset                   |                    |

| Watchdog Timer (WDT)        | 21, 30             |

| Block Diagram               | 31                 |

| Postscaler. See Prescaler   |                    |

| Programming Considerations  | 31                 |

| RC Oscillator               | 30                 |

| Time-out Period             | 30                 |

| WDT Reset, Normal Operation |                    |

| WDT Reset, SLEEP            |                    |

| WWW Address                 |                    |

| WWW, On-Line Support        |                    |

| -                           |                    |

# Ζ

| Z (Zero) bit | 8 |

|--------------|---|

|--------------|---|

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MTP, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

Analog-for-the-Digital Age, Application Maestro, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, SQI, Serial Quad I/O, Total Endurance, TSHARC, UniWinDriver, WiperLock, ZENA and Z-Scale are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

GestIC and ULPP are registered trademarks of Microchip Technology Germany II GmbH & Co. & KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2001-2013, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 9781620769409

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEEL0Q® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.