Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | POR, WDT                                                                   |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 64 x 8                                                                     |

| RAM Size                   | 68 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

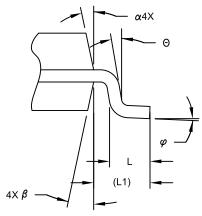

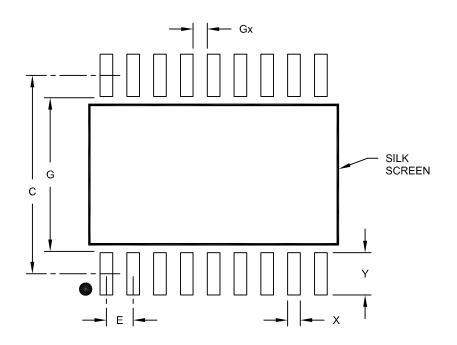

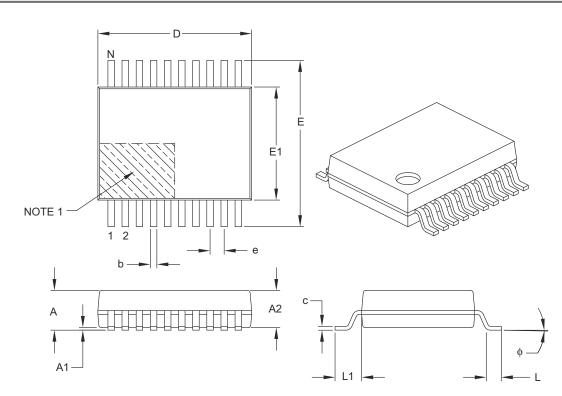

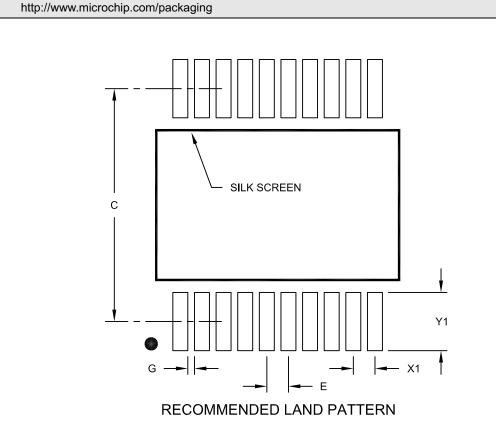

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f84at-20-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.0 MEMORY ORGANIZATION

There are two memory blocks in the PIC16F84A. These are the program memory and the data memory. Each block has its own bus, so that access to each block can occur during the same oscillator cycle.

The data memory can further be broken down into the general purpose RAM and the Special Function Registers (SFRs). The operation of the SFRs that control the "core" are described here. The SFRs used to control the peripheral modules are described in the section discussing each individual peripheral module.

The data memory area also contains the data EEPROM memory. This memory is not directly mapped into the data memory, but is indirectly mapped. That is, an indirect address pointer specifies the address of the data EEPROM memory to read/write. The 64 bytes of data EEPROM memory have the address range 0h-3Fh. More details on the EEPROM memory can be found in Section 3.0.

Additional information on device memory may be found in the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023).

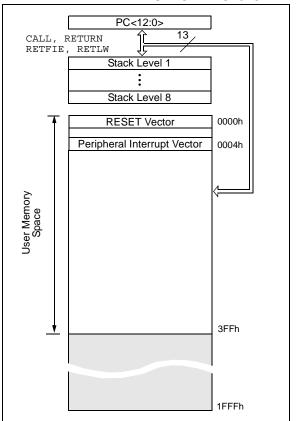

#### 2.1 Program Memory Organization

The PIC16FXX has a 13-bit program counter capable of addressing an 8K x 14 program memory space. For the PIC16F84A, the first 1K x 14 (0000h-03FFh) are physically implemented (Figure 2-1). Accessing a location above the physically implemented address will cause a wraparound. For example, for locations 20h, 420h, 820h, C20h, 1020h, 1420h, 1820h, and 1C20h, the instruction will be the same.

The RESET vector is at 0000h and the interrupt vector is at 0004h.

#### FIGURE 2-1:

#### PROGRAM MEMORY MAP AND STACK - PIC16F84A

#### 2.3.2 OPTION REGISTER

bit

bit

bit

bit

bit

bit

The OPTION register is a readable and writable register which contains various control bits to configure the TMR0/WDT prescaler, the external INT interrupt, TMR0, and the weak pull-ups on PORTB.

| Note: | When the prescaler is assigned to   |  |  |  |  |  |  |  |  |

|-------|-------------------------------------|--|--|--|--|--|--|--|--|

|       | the WDT (PSA = '1'), TMR0 has a 1:1 |  |  |  |  |  |  |  |  |

|       | prescaler assignment.               |  |  |  |  |  |  |  |  |

## REGISTER 2-2: OPTION REGISTER (ADDRESS 81h)

| R/W-1                               | R/W-1                             | R/W-1             | R/W-1         | R/W-1        | R/W-1      | R/W-1        | R/W-1 |  |

|-------------------------------------|-----------------------------------|-------------------|---------------|--------------|------------|--------------|-------|--|

| RBPU                                | INTEDG                            | TOCS              | TOSE          | PSA          | PS2        | PS1          | PS0   |  |

| bit 7                               |                                   |                   |               |              |            |              | bit ( |  |

| RBPU: PO                            | ORTB Pull-up                      | Enable bit        |               |              |            |              |       |  |

|                                     | TB pull-ups a                     |                   |               |              |            |              |       |  |

|                                     | TB pull-ups a                     |                   | oy individual | port latch v | alues      |              |       |  |

|                                     | Interrupt Edg                     |                   |               |              |            |              |       |  |

|                                     | upt on rising<br>upt on falling   |                   |               |              |            |              |       |  |

| TOCS: TM                            | IR0 Clock So                      | urce Select       | bit           |              |            |              |       |  |

|                                     | sition on RA4,<br>nal instruction |                   | (CLKOUT)      |              |            |              |       |  |

|                                     | IR0 Source E                      | -                 | . ,           |              |            |              |       |  |

|                                     | ment on high                      | •                 |               | 4/T0CKI pin  |            |              |       |  |

| 0 = Incre                           | ment on low-                      | to-high trans     | ition on RA   | 4/T0CKI pin  |            |              |       |  |

| PSA: Pres                           | scaler Assign                     | ment bit          |               |              |            |              |       |  |

|                                     | caler is assign                   |                   |               |              |            |              |       |  |

|                                     | aler is assign                    |                   |               | le           |            |              |       |  |

| PS2:PS0: Prescaler Rate Select bits |                                   |                   |               |              |            |              |       |  |

| Bit Value                           | TMR0 Rate                         | WDT Rate          |               |              |            |              |       |  |

| 000                                 | 1:2                               | 1:1               |               |              |            |              |       |  |

| 001<br>010                          | 1:4<br>1:8                        | 1:2<br>1:4        |               |              |            |              |       |  |

| 010                                 | 1:8                               | 1:8               |               |              |            |              |       |  |

| 100                                 | 1:32                              | 1:16              |               |              |            |              |       |  |

| 101                                 | 1:64                              | 1:32              |               |              |            |              |       |  |

| 110                                 | 1:128                             | 1 : 64<br>1 : 128 |               |              |            |              |       |  |

| 111                                 | 1 : 256                           | 1.120             |               |              |            |              |       |  |

| Legend:                             |                                   |                   |               |              |            |              |       |  |

| R = Read                            | able bit                          | W = W             | ritable bit   | U = Unir     | nplemented | bit, read as | '0'   |  |

| - n = Valu                          |                                   | '1' = B           |               | 101 011      | s cleared  | x = Bit is u |       |  |

## 4.0 I/O PORTS

Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Additional information on I/O ports may be found in the PIC<sup>®</sup> Mid-Range Reference Manual (DS33023).

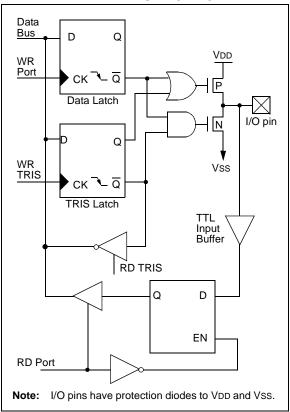

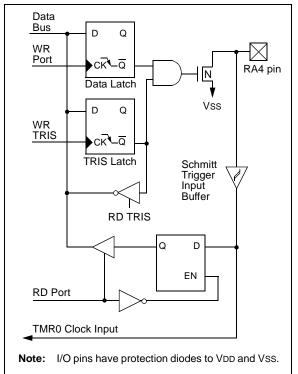

### 4.1 PORTA and TRISA Registers

PORTA is a 5-bit wide, bi-directional port. The corresponding data direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin).

| Note: | On a Power-on Reset, these pins are con- |

|-------|------------------------------------------|

|       | figured as inputs and read as '0'.       |

Reading the PORTA register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read. This value is modified and then written to the port data latch.

Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL input levels and full CMOS output drivers.

| BCF   | STATUS, RPO | ; |                       |

|-------|-------------|---|-----------------------|

| CLRF  | PORTA       | ; | Initialize PORTA by   |

|       |             | ; | clearing output       |

|       |             | ; | data latches          |

| BSF   | STATUS, RPO | ; | Select Bank 1         |

| MOVLW | 0x0F        | ; | Value used to         |

|       |             | ; | initialize data       |

|       |             | ; | direction             |

| MOVWF | TRISA       | ; | Set RA<3:0> as inputs |

|       |             | ; | RA4 as output         |

|       |             | ; | TRISA<7:5> are always |

|       |             | ; | read as '0'.          |

|       |             |   |                       |

#### FIGURE 4-1:

#### BLOCK DIAGRAM OF PINS RA3:RA0

FIGURE 4-2:

BLOCK DIAGRAM OF PIN RA4

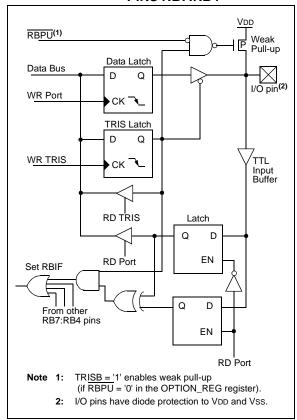

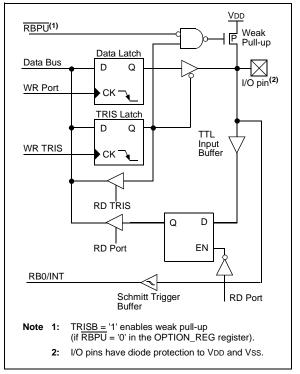

#### 4.2 PORTB and TRISB Registers

PORTB is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

EXAMPLE 4-2: INITIALIZING PORTB

| BCF   | STATUS, RPO | ; |                       |

|-------|-------------|---|-----------------------|

| CLRF  | PORTB       | ; | Initialize PORTB by   |

|       |             | ; | clearing output       |

|       |             | ; | data latches          |

| BSF   | STATUS, RPO | ; | Select Bank 1         |

| MOVLW | 0xCF        | ; | Value used to         |

|       |             | ; | initialize data       |

|       |             | ; | direction             |

| MOVWF | TRISB       | ; | Set RB<3:0> as inputs |

|       |             | ; | RB<5:4> as outputs    |

|       |             | ; | RB<7:6> as inputs     |

| 1     |             |   |                       |

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (OPTION<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Four of PORTB's pins, RB7:RB4, have an interrupt-onchange feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupton-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>).

This interrupt can wake the device from SLEEP. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

#### FIGURE 4-3: BLOCK DIAGRAM OF PINS RB7:RB4

FIGURE 4-4:

BLOCK DIAGRAM OF PINS RB3:RB0

#### TABLE 7-2: PIC16CXXX INSTRUCTION SET

| Operands         Description         Cycles         MSb         LSb         Affected         Note           BYTE-ORIENTED FILE REGISTER OPERATIONS           ADDWF         f, d         Add W and f         1         00         0111         dfff         ffff         Z         1,2           ANDWF         f, d         AND W with f         1         00         00101         dfff         ffff         Z         1,2           CLRF         f         Clear f         1         00         00101         dfff         fff         Z         1,2           CDECF         f, d         Decrement f, Skip if 0         1 (2)         00         1010         dfff         fff         Z         1,2           DECF         f, d         Increment f, Skip if 0         1 (2)         00         1010         dfff         fff         1,2           INCFSZ         f, d         Increment f, Skip if 0         1 (2)         00         1111         dfff         1,2         1,2           INCFSZ         f, d         Increment f, Skip if 0         1 (2)         00         1100         0000         dff ffff         1,2           INCFSZ         f, d         Notate Left (through Carry                                                                                 | Mnemonic,<br>Operands |                                        | Description                 |        |      | 14-Bit | Opcode | Status |          |       |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------------------------|-----------------------------|--------|------|--------|--------|--------|----------|-------|--|

| ADDWF         f, d         Add W and f         1         00         0111         dff ffff         C,DC,Z         1.2           ANDWF         f, d         AND W with f         1         00         0101         dfff ffff         Z         2           CLRF         f         Clear f         1         00         0001         dfff ffff         Z         2           COMF         f, d         Complement f         1         00         0001         dfff ffff         Z         1.2           DECFSZ         f, d         Decrement f, Skip if 0         1 (2)         00         1011         dfff ffff         Z         1.2           INCFS         f, d         Increment f, Skip if 0         1 (2)         00         1111         dfff ffff         Z         1.2           INCFSZ         f, d         Increment f, Skip if 0         1 (2)         00         1111         dfff fffff         Z         1.2           INCFSZ         f, d         Move f         1         00         0000         dfff ffff         Z         1.2           MOVF         f, d         Rotate Left fthrough Carry         1         00         0000         dfff ffff         C         1.2                                                                                        |                       |                                        |                             |        | MSb  |        |        | LSb    | Affected | Notes |  |

| ANDWF         f, d         AND With f         1         00         0101         dff ffff         Z         12           CLRF         f         Clear f         1         00         0001         lfff ffff         Z         12           CLRW         -         Clear W         1         00         0001         lfff ffff         Z         12           COMF         f, d         Decrement f         1         00         0011         dfff ffff         Z         12           DECFSZ         f, d         Decrement f, Skip if 0         1 (2)         00         111         dfff ffff         Z         1,2           INCFSZ         f, d         Increment f, Skip if 0         1 (2)         00         1111         dfff ffff         Z         1,2           IORVF         f, d         Increment f, Skip if 0         1 (2)         00         1111         dfff ffff         Z         1,2           MOVF         f, d         Move f         1         00         0000         0xx0         0000           REF         f, d         Rotate Right fft mough Carry         1         00         110         dff ffff         C         1,2           SUBWF         f, d                                                                                              |                       | BYTE-ORIENTED FILE REGISTER OPERATIONS |                             |        |      |        |        |        |          |       |  |

| CLRF         f         Clear f         Clear f         1         00         0001         lfff         fff         Z         2           COMF         f, d         Complement f         1         00         0001         0xxx <xxxx< td="">         Z         2           DECF         f, d         Decrement f, Skip if 0         1 (2)         00         1011         dfff ffff         Z         1,2           DECFSZ         f, d         Decrement f, Skip if 0         1 (2)         00         1111         dfff ffff         Z         1,2           INCF         f, d         Increment f, Skip if 0         1 (2)         00         1111         dfff ffff         Z         1,2           INCFVF         f, d         Move f         1         00         1001         dfff ffff         Z         1,2           INCFVF         f         Move f         1         00         100         dfff ffff         Z         1,2           MOVF         f         Move f         1         00         100         100         100         100         100         100         110         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2</xxxx<>                                                                                    | ADDWF                 | f, d                                   | Add W and f                 | 1      | 00   | 0111   | dfff   | ffff   | C,DC,Z   | 1,2   |  |

| CLRW         -         Clear W         1         00         0001         0xxx         xxxx         Z           COMF         f, d         Complement f         1         00         0011         dfff         ffff         Z         1,2           DECF         f, d         Decrement f, Skip if 0         1 (2)         00         1011         dfff         ffff         Z         1,2           INCF         f, d         Increment f         1         00         1010         dfff         ffff         Z         1,2           INCFSZ         f, d         Increment f, Skip if 0         1 (2)         00         1111         dfff         ffff         Z         1,2           MOVF         f, d         Increment f, Skip if 0         1 (2)         00         1111         dfff         T         1,2           MOVF         f, d         Move f         1         00         0000         1ff         T         1,2           MOVF         f, d         Rotate Left fthrough Carry         1         00         1010         dfff         C,DC,Z         1,2           SUBWF         f, d         Subtract W from f         1         00         0100         dffff                                                                                                   | ANDWF                 | f, d                                   | AND W with f                | 1      | 00   | 0101   | dfff   | ffff   | Z        | 1,2   |  |

| COMF         f, d         Complement f         1         00         1001         dfff         ffff         Z         1,2           DECF         f, d         Decrement f, Skip if 0         1 (2)         00         1011         dfff         ffff         Z         1,2           INCF         f, d         Increment f, Skip if 0         1 (2)         00         1010         dfff         ffff         Z         1,2           INCF         f, d         Increment f, Skip if 0         1 (2)         00         1010         dfff         ffff         Z         1,2           INCFSZ         f, d         Increment f         1         00         1000         dfff         ffff         Z         1,2           INCFV         f, d         Move W with f         1         00         1000         dfff         ffff         Z         1,2           MOVF         f, d         Rotate Left fthrough Carry         1         00         1000         0000         0xco 0000         RC         1,2           SUBWF         f, d         Subtract W from f         1         00         1100         dfff         ffff         Z         1,2           SUBWF         f, d         Sub                                                                                      | CLRF                  | f                                      | Clear f                     | 1      | 00   | 0001   | lfff   | ffff   | Z        | 2     |  |

| DECF         f, d         Decrement f, Skip if 0         1         0         0011         dfff         fff         Z         1/2           DECFSZ         f, d         Increment f, Skip if 0         1 (2)         00         1011         dfff         fff         1/2           INCFSZ         f, d         Increment f, Skip if 0         1 (2)         00         1010         dfff         fff         Z         1/2           INCFSZ         f, d         Increment f, Skip if 0         1 (2)         00         1111         dfff         ffff         Z         1/2           INCFSZ         f, d         Increment f, Skip if 0         1         00         0100         dfff         ffff         Z         1/2           MOVF         f, d         Move f         1         00         0100         dfff         ffff         Z         1/2           MOVF         f, d         Rotate Left fhrough Carry         1         00         1010         dfff         ffff         Z         1/2           SUBWF         f, d         Subtract W from f         1         00         1010         dfff         ffff         1/2         1/2           SUBWF         f, d         Subtract W f                                                                             | CLRW                  | -                                      | Clear W                     | 1      | 00   | 0001   | 0xxx   | xxxx   | Z        |       |  |

| DECF         f, d         Decrement f, Skip if 0         1         00         0011         dfff         fff         Z         1, 2           DECFSZ         f, d         Decrement f, Skip if 0         1         1         00         1010         dfff         ffff         Z         1, 2           INCF         f, d         Increment f, Skip if 0         1         1         00         1010         dfff         ffff         Z         1, 2           INCFSZ         f, d         Increment f, Skip if 0         1         1         00         0100         dfff         ffff         Z         1, 2           INCFSZ         f, d         Inclusive OR W with f         1         00         0100         dfff         ffff         Z         1, 2           MOVF         f         Move f         No operation         1         00         0000         0000         0000         R         RF         f, d         Subtract W from f         1         00         1010         dfff         ffff         C         1, 2           SUBWF         f, d         Subtract W from f         1         00         1010         dfff         ffff         1, 2         1, 2         1, 2         1, 2<                                                                      | COMF                  | f, d                                   | Complement f                | 1      | 00   | 1001   | dfff   | ffff   | Z        | 1,2   |  |

| INCF         f, d         Increment f, Skip if 0         1         0         1010         dfff         ffff         Z         1,2           INCFSZ         f, d         Increment f, Skip if 0         1 (2)         00         1111         dfff         ffff         Z         1,2           IORWF         f, d         Inclusive OR W with f         1         00         0100         dfff         ffff         Z         1,2           MOVF         f, d         Move W to f         1         00         1000         dfff         ffff         Z         1,2           MOVF         f         Move W to f         1         00         1000         dfff         ffff         Z         1,2           MOVF         f, d         Rotate Left fthrough Carry         1         00         1100         dfff         ffff         C         1,2           SUBWF         f, d         Subtract W from f         1         00         1100         dfff         ffff         Z         1,2           XORWF         f, d         Subtract W from f         1         00         01010         dfff         ffff         Z         1,2           XORWF         f, d         Bit Set f                                                                                              | DECF                  | f, d                                   |                             | 1      | 00   | 0011   | dfff   | ffff   | Z        | 1,2   |  |

| INCF         f, d         Increment f, Skip if 0         1         0         1010         dfff         ffff         Z         1,2           INCFSZ         f, d         Increment f, Skip if 0         1 (2)         00         1111         dfff         ffff         Z         1,2           IORWF         f, d         Inclusive OR W with f         1         00         0100         dfff         ffff         Z         1,2           MOVF         f, d         Move W to f         1         00         1000         dfff         ffff         Z         1,2           MOVF         f         Move W to f         1         00         1000         dfff         ffff         Z         1,2           MOVF         f, d         Rotate Left fthrough Carry         1         00         1100         dfff         ffff         C         1,2           SUBWF         f, d         Subtract W from f         1         00         1100         dfff         ffff         Z         1,2           XORWF         f, d         Subtract W from f         1         00         01010         dfff         ffff         Z         1,2           XORWF         f, d         Bit Set f                                                                                              | DECFSZ                | f, d                                   | Decrement f, Skip if 0      | 1 (2)  | 00   | 1011   | dfff   | ffff   |          | 1,2,3 |  |

| INCFSZ         f, d         Increment f, Skip if 0         1 (2)         00         1111         dfff         ffff         1,2,           IORWF         f, d         Inclusive OR W with f         1         00         0100         dfff         ffff         Z         1,2,           MOVF         f, d         Move f         1         00         0100         dfff         ffff         Z         1,2,           MOVF         f, d         Move f         1         00         0100         dfff         ffff         Z         1,2,           MOVF         f         Move f         1         00         0000         0x00                                                                                 | INCF                  | f. d                                   | Increment f                 | . ,    | 00   | 1010   | dfff   | ffff   | Z        | 1,2   |  |

| IORWF         f, d         Inclusive OR W with f         1         00         0100         dfff         ffff         Z         1, 2           MOVF         f, d         Move f         1         00         1000         dfff         ffff         Z         1, 2           MOVWF         f         Move W to f         1         00         1000         dfff         ffff         Z         1, 2           MOVF         f         Move W to f         1         00         1000         dfff         ffff         Z         1, 2           RF         f, d         Rotate Left fthrough Carry         1         00         1100         dfff         ffff         C         1, 2           SUBWF         f, d         Swap nibbles in f         1         00         101         dfff         ffff         1, 2           XORWF         f, d         Exclusive OR W with f         1         0         0100         dfff         ffff         1, 2           XORWF         f, d         Exclusive OR W with f         1         1         00         101         01bb         bfff         ffff         2         1, 2           XORWF         f, d         Bit Test f, Skip if Clear                                                                                            | INCFSZ                | f. d                                   | Increment f. Skip if 0      | 1 (2)  | 00   | 1111   | dfff   | ffff   |          | 1,2,3 |  |

| MOVF         f, d         Move f         1         00         1000         dfff         ffff         Z         1, 2           MOVF         f         Move W to f         1         00         0000         10ff         ffff         Z         1, 2           NOP         -         No Operation         1         00         0000         0xx0         0000         Cxx0         Cx1, 2         Cxx0         Cxx0         Cxx0         Cx1, 2         Cxx0         Cx1, 2         Cxx0         Cxx0         Cx0, Cx         Cx1, 2         Cxx0         Cxx0         Cx1, 2         C                                      | IORWF                 | ,                                      |                             |        |      |        |        |        | Z        | 1,2   |  |

| MOWWF         f         Move W to f         1         00         0000         1ff ffff         fff           NOP         -         No Operation         1         00         0000         0xx0         0xx0         0x00         0x00         0xx0         0x00         0xx0         0x00                                                         | -                     | ,                                      |                             |        |      |        |        |        |          |       |  |

| NOP         -         No Operation         1         00         0000         0xx0         0000           RLF         f, d         Rotate Left fthrough Carry         1         00         1101         dfff         ffff         C         1,2           RRF         f, d         Subtract W from f         1         00         1000         dfff         ffff         C         1,2           SWAPF         f, d         Swap nibbles in f         1         00         0110         dfff         ffff         Z         1,2           XORWF         f, d         Exclusive OR W with f         1         00         0110         dfff         ffff         Z         1,2           BIT-ORIENTED FILE REGISTER OPERATIONS           BCF         f, b         Bit Clear f         1         01         00bb         bfff         ffff         1,2           BSF         f, b         Bit Set f         1         01         01bb         bfff         ffff         3           BTFSS         f, b         Bit Test f, Skip if Clear         1 (2)         01         11bb         bfff         ffff         3           CALL         k         Call subroutine         2                                                                                                          |                       | , -                                    |                             | -      |      |        |        |        | _        | .,_   |  |

| RLF         f, d         Rotate Left fthrough Carry         1         00         1101         dfff         ffff         C         1,2           RRF         f, d         Rotate Right fthrough Carry         1         00         1100         dfff         ffff         C         1,2           SUBWF         f, d         Subtract W from f         1         00         0100         dfff         ffff         C,DC,Z         1,2           SWAPF         f, d         Swap nibbles in f         1         00         1110         dfff         ffff         Z,DC,Z         1,2           XORWF         f, d         Exclusive OR W with f         1         00         1100         dfff         ffff         Z         1,2           XORWF         f, d         Bit Clear f         1         01         00bb         bfff         ffff         1,2           BCF         f, b         Bit Test f, Skip if Clear         1         1         01         00bb         bfff         ffff         1,2           BTFSC         f, b         Bit Test f, Skip if Set         1         1         11         1111         111x         kkkk kkkk         Z           ADDLW         k         Add litera                                                                             |                       |                                        |                             |        |      |        |        |        |          |       |  |

| RRF         f, d         Rotate Right f through Carry         1         00         1100         dfff         fff         C         1,2           SUBWF         f, d         Subtract W from f         1         00         0010         dfff         ffff         C,DC,Z         1,2           SWAPF         f, d         Swap nibbles in f         1         00         0110         dfff         ffff         Z,DC,Z         1,2           XORWF         f, d         Exclusive OR W with f         1         00         0110         dfff         ffff         Z         1,2           BIT-ORIENTED FILE REGISTER OPERATIONS           BCF         f, b         Bit Clear f         1         01         00bb         bfff         ffff         1,2           BTFSC         f, b         Bit Test f, Skip if Clear         1 (2)         01         10bb         bfff         ffff         3           CLITERAL AND CONTROL OPERATIONS         LITERAL AND CONTROL OPERATIONS         Z         Z         Add literal and W         1         11         11101         kkkk kkkk         Z         Z           ADDLW         k         Add literal and W         1         1         11         1000         kkkk kkkk                                                          | -                     | f. d                                   |                             | -      |      |        |        |        | С        | 1,2   |  |

| SUBWF         f, d         Subtract W from f         1         00         0010         dfff         ffff         C,DC,Z         1,2           SWAPF         f, d         Swap nibbles in f         1         00         0110         dfff         ffff         Z         1,2           XORWF         f, d         Exclusive OR W with f         1         00         0110         dfff         ffff         Z         1,2           BIT-ORIENTED FILE REGISTER OPERATIONS           BCF         f, b         Bit Clear f         1         01         00bb         bfff         ffff         1,2           BSF         f, b         Bit Test f, Skip if Clear         1         01         01bb         bfff         ffff         1,2           BTFSS         f, b         Bit Test f, Skip if Set         1 (2)         01         10bb         bfff         ffff         3           LITERAL AND CONTROL OPERATIONS         Interal and W         1         11         111x         kkkk kkkk         Z         Z           ADDLW         k         Add literal and W         1         1         11         111x         kkkk kkkk         Z           CALL         k         Call subroutine                                                                                   |                       | , -                                    |                             | -      |      |        |        |        | -        | 1,2   |  |

| SWAPF<br>XORWF         f, d         Swap nibbles in f<br>Exclusive OR W with f         1         00         1110         dfff         ffff         1,2           BIT-ORIENTED FILE REGISTER OPERATIONS           BIT-ORIENTED FILE REGISTER OPERATIONS           BCF         f, b         Bit Clear f         1         01         00bb         bfff         ffff         1,2           BSF         f, b         Bit Set f         1         01         00bb         bfff         ffff         1,2           BTFSC         f, b         Bit Test f, Skip if Clear         1         01         01bb         bfff         ffff         1,2           LITERAL AND CONTROL OPERATIONS           ADDLW         k         Add literal and W         1         11         111.001         kkkk         kkkk         Z           ANDLW         k         Add literal and W         1         11         11001         kkkk         kkkk         Z           CALL         k         Call subroutine         2         10         0kkk         kkkkk         Z           GOTO         k         Go to address         2         10         111.0000         kkkkkkkk         Z </td <td></td> <td>,</td> <td></td> <td>-</td> <td></td> <td></td> <td></td> <td></td> <td>-</td> <td>,</td> |                       | ,                                      |                             | -      |      |        |        |        | -        | ,     |  |

| XORWF         f, d         Exclusive OR W with f         1         00         0110         dfff         ffff         Z         1,2           BIT-ORIENTED FILE REGISTER OPERATIONS           BCF         f, b         Bit Clear f         1         01         00bb         bfff         ffff         1,2           BSF         f, b         Bit Clear f         1         1         01         01bb         bfff         ffff         1,2           BTFSC         f, b         Bit Test f, Skip if Clear         1         1         01         01bb         bfff         ffff         1,2           ADDLW         k         Add literal and W         1         1         111         111x         kkkk         kkkk         Z         Z           ADDLW         k         Add literal and W         1         1         11         111x         kkkk         kkkk         Z           ADDLW         k         Call subroutine         2         10         0kkk         kkkk         Z         Z           GOTO         k         Go to address         2         10         0kkk         kkkk         Z           OCOTO         K                                                                                                                                              |                       | ,                                      |                             |        |      |        |        |        | 0,20,2   |       |  |

| BIT-ORIENTED FILE REGISTER OPERATIONS         BCF       f, b       Bit Clear f       1       01       00bb       bfff       ffff       1,2         BSF       f, b       Bit Set f       1       01       01bb       bfff       ffff       1,2         BTFSC       f, b       Bit Test f, Skip if Clear       1 (2)       01       10bb       bfff       ffff       3         BTFSS       f, b       Bit Test f, Skip if Set       1 (2)       01       11bb       bfff       ffff       3         LITERAL AND CONTROL OPERATIONS         ADDLW       k       Add literal and W       1       11       111       111x       kkkk       kkkk       Z         ADDLW       k       Add literal with W       1       1       11       1001       kkkk       kkkk       Z         CALL       k       Call subroutine       2       10       0kkk       kkkk       Z       TO,PD         GOTO       k       Go to address       2       10       11kkk       kkkk       Z       MOVLW       TO,PD         GOTO       k       Inclusive OR literal with W       1       11       1000       kkkk kkkk                                                                                                                                                                                      |                       | ,                                      |                             | -      |      |        |        |        | 7        |       |  |

| BCFf, bBit Clear f10100bbbfffffff1,2BSFf, bBit Set f10101bbbfffffff1,2BTFSCf, bBit Test f, Skip if Clear1 (2)0110bbbfffffff3BTFSSf, bBit Test f, Skip if Set1 (2)0111bbbfffffff3LITERAL AND CONTROL OPERATIONSADDLWkAdd literal and W111111kkkkkkkZADDLWkAND literal with W1111001kkkkkkkkZCALLkCall subroutine2100kkkkkkkZCLRWDT-Clear Watchdog Timer11000000100TO,PDGOTOkGo to address2101kkkkkkkZIORLWkInclusive OR literal with W111000xkkkkZMOVLWkMove literal to W111000xkkkkZRETFIE-Return from interrupt20000001001RETLWRETURN-Return with literal in W21101xxkkkkKkkkRETURN-Return from Subroutine20000001000SLEEP-Go into standby mode100000010011TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                       | ., a                                   |                             |        |      |        | 4111   |        | _        | •,=   |  |

| BSFf, bBit Set f10101bbbfffffff1,2BTFSCf, bBit Test f, Skip if Clear11110bbbfffffff3BTFSSf, bBit Test f, Skip if Set1(2)0111bbbfffffff3LITERAL AND CONTROL OPERATIONSADDLWkAdd literal and W111111111xkkkkkkkkZANDLWkAdd literal with W1111001kkkkkkkkZCALLkCall subroutine2100kkkkkkkKkkkZGOTOkGo to address2101kkkkkkkZIORLWkInclusive OR literal with W1111000kkkkZMOVLWkReturn from interrupt200000000011001RETLWkReturn with literal in W21101xxkkkkkkkkRETURN-Return from Subroutine20000000001TO,PDSLEEP-Go into standby mode10000000101TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | DOF                   | 6.1                                    |                             | -      | -    | -      |        |        |          | 4.0   |  |

| BTFSC<br>BTFSSf, bBit Test f, Skip if Clear<br>Bit Test f, Skip if Set1 (2)0110bbbfffffff3LITERAL AND CONTROL OPERATIONSADDLW<br>ANDLWkAdd literal and W111111111xkkkkkkkkZANDLW<br>CALLkAdd literal with W1111111001kkkkkkkkZCALL<br>GOTOkCall subroutine2100kkkkkkkkkkkZCIRWDT<br>GOTOClear Watchdog Timer<br>Go to address1111000kkkkKkkkZIORLW<br>KInclusive OR literal with W1111000kkkkZMOVLW<br>RETFIE<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -                     | , -                                    |                             | -      | -    |        |        |        |          |       |  |

| BTFSSf, bBit Test f, Skip if Set1 (2)0111bbbfffffff3LITERAL AND CONTROL OPERATIONSADDLWkAdd literal and W111111111xkkkkkkkkC,DC,ZANDLWkAND literal with W1111001kkkkkkkkZCALLkCall subroutine2100kkkkkkkkkkkZCLRWDT-Clear Watchdog Timer100000001100100TO,PDGOTOkGo to address2101kkkkkkkZIORLWkInclusive OR literal with W1111000kkkkkkkkMOVLWkMove literal to W1110000000001001RETLWkReturn from interrupt200000000001001RETLWkReturn with literal in W21101xxkkkkkkkkRETURN-Return from Subroutine20000000001TO,PDSLEEP-Go into standby mode10000000110TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -                     | ,                                      |                             | -      | -    |        |        |        |          | ,     |  |

| LITERAL AND CONTROL OPERATIONSADDLWkAdd literal and W111111111xkkkkkkkkC,DC,ZANDLWkAND literal with W11111001kkkkkkkkZCALLkCall subroutine2100kkkkkkkkkkkZCLRWDT-Clear Watchdog Timer100000001100100TO,PDGOTOkGo to address2101kkkkkkkkkkkZIORLWkInclusive OR literal with W1111000kkkkkkkkZMOVLWkMove literal to W1110000000001001RETFIERETFIE-Return from interrupt200000000001001RETLWRETURN-Return from Subroutine200000000001000SLEEP-Go into standby mode10000000110TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                       | ,                                      |                             |        | -    |        |        |        |          |       |  |

| ADDLWkAdd literal and W111111 111xkkkkkkkkC,DC,ZANDLWkAND literal with W1111001kkkkkkkkZCALLkCall subroutine2100kkkkkkkkkkkZCLRWDT-Clear Watchdog Timer100000001100100TO,PDGOTOkGo to address2101kkkkkkkkkkkZIORLWkInclusive OR literal with W1111000kkkkkkkkZMOVLWkMove literal to W111000xxkkkkkkkkZRETFIE-Return from interrupt200000000011001RETLWkReturn with literal in W21101xxkkkkkkkkRETURN-Return from Subroutine20000000001TO,PDSLEEP-Go into standby mode10000000110TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | BIESS                 | f, b                                   |                             |        | -    | 11bb   | bfff   | ffff   |          | 3     |  |

| ANDLWkAND literal with W1111001kkkkkkkkZCALLkCall subroutine2100kkkkkkkkkkkKkkkZCLRWDT-Clear Watchdog Timer100000001100100TO,PDGOTOkGo to address2101kkkkkkkkkkkKkkkZIORLWkInclusive OR literal with W1111000kkkkkkkkZMOVLWkMove literal to W111000000001001FRETFIE-Return from interrupt200000000001001RETLWkReturn with literal in W21101xxkkkkkkkkRETURN-Return from Subroutine200000000001000SLEEP-Go into standby mode10000000110TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                       |                                        | LITERAL AND CONTROL         | OPERAT | IONS |        |        |        |          |       |  |

| CALLkCall subroutine2100kkkkkkkkkkkkkkkCLRWDT-Clear Watchdog Timer100000001100100TO,PDGOTOkGo to address2101kkkkkkkkkkkZIORLWkInclusive OR literal with W1111000kkkkkkkkZMOVLWkMove literal to W111000000001001FRETFIE-Return from interrupt200000000001001RETLWkReturn with literal in W21101xxkkkkkkkkRETURN-Return from Subroutine200000000001000SLEEP-Go into standby mode10000000110TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ADDLW                 | k                                      | Add literal and W           | 1      | 11   | 111x   | kkkk   | kkkk   | C,DC,Z   |       |  |

| CLRWDT       -       Clear Watchdog Timer       1       00       0000       0110       0100         GOTO       k       Go to address       2       10       1kkk       kkkk       kkkk         IORLW       k       Inclusive OR literal with W       1       11       1000       kkkk       kkkk         IORLW       k       Inclusive OR literal with W       1       11       1000       kkkk       kkkk         MOVLW       k       Move literal to W       1       11       00000       0000       1001         RETFIE       -       Return from interrupt       2       00       0000       0000       1001         RETLW       k       Return with literal in W       2       11       01xx       kkkk       kkkk         RETURN       -       Return from Subroutine       2       00       0000       0001       1000         SLEEP       -       Go into standby mode       1       00       0000       0110       TO,PD                                                                                                                                                                                                                                                                                                                                                  | ANDLW                 | k                                      | AND literal with W          | 1      | 11   | 1001   | kkkk   | kkkk   | Z        |       |  |

| GOTO         k         Go to address         2         10         1kkk         kkkk         kkkk           IORLW         k         Inclusive OR literal with W         1         11         1000         kkkk         kkkk         Z           MOVLW         k         Move literal to W         1         11         1000         kkkk         kkkk         Z           RETFIE         -         Return from interrupt         2         00         0000         1001           RETLW         k         Return with literal in W         2         11         01xx         kkkk         kkkk           RETURN         -         Return from Subroutine         2         00         0000         1000           SLEEP         -         Go into standby mode         1         00         0000         011         TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CALL                  | k                                      | Call subroutine             | 2      | 10   | 0kkk   | kkkk   | kkkk   |          |       |  |

| IORLW         k         Inclusive OR literal with W         1         11         1000         kkk         kkkk         Z           MOVLW         k         Move literal to W         1         11         1000         kkkk         kkkk         Z           RETFIE         -         Return from interrupt         2         00         0000         0000         1001           RETLW         k         Return with literal in W         2         11         01xx         kkkk         kkkk           RETURN         -         Return from Subroutine         2         00         0000         1000           SLEEP         -         Go into standby mode         1         00         0000         011         TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CLRWDT                | -                                      | Clear Watchdog Timer        | 1      | 00   | 0000   | 0110   | 0100   | TO,PD    |       |  |

| MOVLW         k         Move literal to W         1         11         00xx         kkkk         kkkk           RETFIE         -         Return from interrupt         2         00         0000         0001         1001           RETLW         k         Return with literal in W         2         11         01xx         kkkk         kkkk           RETURN         -         Return from Subroutine         2         00         0000         1000           SLEEP         -         Go into standby mode         1         00         0000         011         TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | GOTO                  | k                                      | Go to address               | 2      | 10   | 1kkk   | kkkk   | kkkk   |          |       |  |

| RETFIE         -         Return from interrupt         2         00         0000         1001           RETLW         k         Return with literal in W         2         11         01xx         kkkk         kkkk           RETURN         -         Return from Subroutine         2         00         0000         1000           SLEEP         -         Go into standby mode         1         00         0000         011         TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | IORLW                 | k                                      | Inclusive OR literal with W | 1      | 11   | 1000   | kkkk   | kkkk   | Z        |       |  |

| RETLW         k         Return with literal in W         2         11         01xx         kkkk         kkkk           RETURN         -         Return from Subroutine         2         00         0000         1000           SLEEP         -         Go into standby mode         1         00         0000         011         TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | MOVLW                 | k                                      | Move literal to W           | 1      | 11   | 00xx   | kkkk   | kkkk   |          |       |  |

| RETURN         -         Return from Subroutine         2         00         0000         1000           SLEEP         -         Go into standby mode         1         00         0000         011         TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | RETFIE                | -                                      | Return from interrupt       | 2      | 00   | 0000   | 0000   | 1001   |          |       |  |

| SLEEP         -         Go into standby mode         1         00         0000         0110         0011         TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | RETLW                 | k                                      | Return with literal in W    | 2      | 11   | 01xx   | kkkk   | kkkk   |          |       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | RETURN                | -                                      | Return from Subroutine      | 2      | 00   | 0000   | 0000   | 1000   |          |       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SLEEP                 | -                                      | Go into standby mode        | 1      | 00   | 0000   | 0110   | 0011   | TO,PD    |       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SUBLW                 | k                                      | Subtract W from literal     | 1      | 11   |        |        |        | C,DC,Z   |       |  |

| XORLW k Exclusive OR literal with W 1 11 1010 kkkk kkkk Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                       |                                        |                             | 1      |      |        |        |        |          |       |  |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

**3:** If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

**Note:** Additional information on the mid-range instruction set is available in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023).

| XORLW                   | Exclusive OR Literal with W                                                                | XORWF            | Exclusive OR W with f                                                                                                                                                       |  |  |  |

|-------------------------|--------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:                 | [ <i>label</i> ] XORLW k                                                                   | Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                  |  |  |  |

| Operands:<br>Operation: | $0 \le k \le 255$<br>(W) .XOR. $k \rightarrow$ (W)                                         | Operands:        | 0 ≤ f ≤ 127<br>d ∈ [0,1]                                                                                                                                                    |  |  |  |

| Status Affected:        | Z                                                                                          | Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                   |  |  |  |

| Description:            | The contents of the W register                                                             | Status Affected: | Z                                                                                                                                                                           |  |  |  |

|                         | are XOR'ed with the eight-bit lit-<br>eral 'k'. The result is placed in<br>the W register. | Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |  |  |  |

## 8.11 PICkit 2 Development Programmer/Debugger and PICkit 2 Debug Express

The PICkit<sup>™</sup> 2 Development Programmer/Debugger is a low-cost development tool with an easy to use interface for programming and debugging Microchip's Flash families of microcontrollers. The full featured Windows® programming interface supports baseline (PIC10F, PIC12F5xx, PIC16F5xx), midrange (PIC12F6xx, PIC16F), PIC18F, PIC24, dsPIC30, dsPIC33, and PIC32 families of 8-bit, 16-bit, and 32-bit microcontrollers, and many Microchip Serial EEPROM products. With Microchip's powerful MPLAB Integrated Development Environment (IDE) the PICkit<sup>™</sup> 2 enables in-circuit debugging on most PIC<sup>®</sup> microcontrollers. In-Circuit-Debugging runs, halts and single steps the program while the PIC microcontroller is embedded in the application. When halted at a breakpoint, the file registers can be examined and modified.

The PICkit 2 Debug Express include the PICkit 2, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

#### 8.12 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an MMC card for file storage and data applications.

## 8.13 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

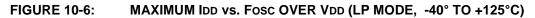

## 9.1 DC Characteristics (Continued)

| PIC16LF84A-04<br>(Commercial, Industrial)                                                                |        |                                         | Opera | ting ter                                                                                                                                                                                                                              | mperat     | ure      | ditions (unless otherwise stated)<br>$0^{\circ}C \le TA \le +70^{\circ}C$ (commercial)<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ (industrial)<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ (extended)<br>ditions (unless otherwise stated) |  |  |