Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | POR, WDT                                                                   |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 64 x 8                                                                     |

| RAM Size                   | 68 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            |                                                                            |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf84a-04-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.0 MEMORY ORGANIZATION

There are two memory blocks in the PIC16F84A. These are the program memory and the data memory. Each block has its own bus, so that access to each block can occur during the same oscillator cycle.

The data memory can further be broken down into the general purpose RAM and the Special Function Registers (SFRs). The operation of the SFRs that control the "core" are described here. The SFRs used to control the peripheral modules are described in the section discussing each individual peripheral module.

The data memory area also contains the data EEPROM memory. This memory is not directly mapped into the data memory, but is indirectly mapped. That is, an indirect address pointer specifies the address of the data EEPROM memory to read/write. The 64 bytes of data EEPROM memory have the address range 0h-3Fh. More details on the EEPROM memory can be found in Section 3.0.

Additional information on device memory may be found in the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023).

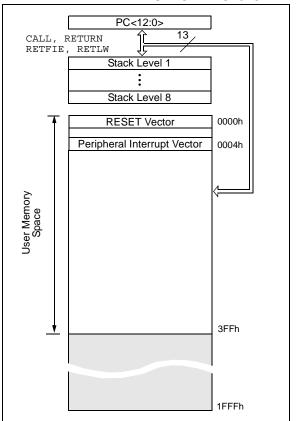

### 2.1 Program Memory Organization

The PIC16FXX has a 13-bit program counter capable of addressing an 8K x 14 program memory space. For the PIC16F84A, the first 1K x 14 (0000h-03FFh) are physically implemented (Figure 2-1). Accessing a location above the physically implemented address will cause a wraparound. For example, for locations 20h, 420h, 820h, C20h, 1020h, 1420h, 1820h, and 1C20h, the instruction will be the same.

The RESET vector is at 0000h and the interrupt vector is at 0004h.

#### FIGURE 2-1:

#### PROGRAM MEMORY MAP AND STACK - PIC16F84A

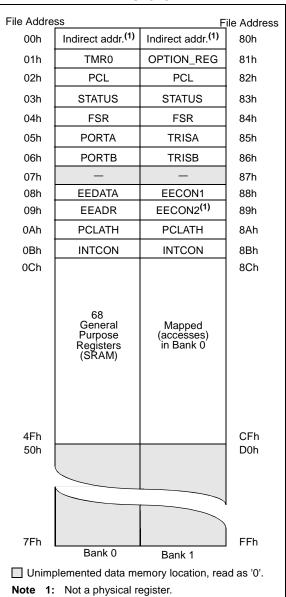

## 2.2 Data Memory Organization

The data memory is partitioned into two areas. The first is the Special Function Registers (SFR) area, while the second is the General Purpose Registers (GPR) area. The SFRs control the operation of the device.

Portions of data memory are banked. This is for both the SFR area and the GPR area. The GPR area is banked to allow greater than 116 bytes of general purpose RAM. The banked areas of the SFR are for the registers that control the peripheral functions. Banking requires the use of control bits for bank selection. These control bits are located in the STATUS Register. Figure 2-2 shows the data memory map organization.

Instructions MOVWF and MOVF can move values from the W register to any location in the register file ("F"), and vice-versa.

The entire data memory can be accessed either directly using the absolute address of each register file or indirectly through the File Select Register (FSR) (Section 2.5). Indirect addressing uses the present value of the RP0 bit for access into the banked areas of data memory.

Data memory is partitioned into two banks which contain the general purpose registers and the special function registers. Bank 0 is selected by clearing the RP0 bit (STATUS<5>). Setting the RP0 bit selects Bank 1. Each Bank extends up to 7Fh (128 bytes). The first twelve locations of each Bank are reserved for the Special Function Registers. The remainder are General Purpose Registers, implemented as static RAM.

#### 2.2.1 GENERAL PURPOSE REGISTER FILE

Each General Purpose Register (GPR) is 8-bits wide and is accessed either directly or indirectly through the FSR (Section 2.5).

The GPR addresses in Bank 1 are mapped to addresses in Bank 0. As an example, addressing location 0Ch or 8Ch will access the same GPR.

#### FIGURE 2-2: REGISTER FILE MAP -PIC16F84A

#### 2.3.3 INTCON REGISTER

The INTCON register is a readable and writable register that contains the various enable bits for all interrupt sources.

**Note:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>).

#### REGISTER 2-3: INTCON REGISTER (ADDRESS 0Bh, 8Bh)

- n = Value at POR

|       | R/W-0       | R/W-0                       | R/W-0          | R/W-0        | R/W-0                     | R/W-0        | R/W-0          | R/W-x |

|-------|-------------|-----------------------------|----------------|--------------|---------------------------|--------------|----------------|-------|

|       | GIE         | EEIE                        | TOIE           | INTE         | RBIE                      | T0IF         | INTF           | RBIF  |

|       | bit 7       |                             |                |              | ·                         |              |                | bit 0 |

|       |             |                             |                |              |                           |              |                |       |

| bit 7 |             | I Interrupt E               |                |              |                           |              |                |       |

|       |             | s all unmasi                |                | ots          |                           |              |                |       |

| h:+ C |             | es all interru              |                | 4 Enabla bit |                           |              |                |       |

| bit 6 |             | Vrite Comple                |                |              |                           |              |                |       |

|       |             | s the EE Wr<br>es the EE W  |                |              |                           |              |                |       |

| bit 5 |             | 0 Overflow I                |                | •            |                           |              |                |       |

|       |             | s the TMR0                  | -              |              |                           |              |                |       |

|       | 0 = Disable | es the TMRC                 | ) interrupt    |              |                           |              |                |       |

| bit 4 | INTE: RB0   | /INT Externa                | al Interrupt I | Enable bit   |                           |              |                |       |

|       |             | s the RB0/I                 |                |              |                           |              |                |       |

|       |             | es the RB0/I                |                |              |                           |              |                |       |

| bit 3 |             | Port Change                 | -              |              |                           |              |                |       |

|       |             | s the RB po<br>es the RB po |                |              |                           |              |                |       |

| bit 2 |             | 0 Overflow I                | •              |              |                           |              |                |       |

|       |             |                             |                | •            | eared in softwa           | ire)         |                |       |

|       | 0 = TMR0    | register did                | not overflov   | v            |                           |              |                |       |

| bit 1 |             | INT Externa                 |                | •            |                           |              |                |       |

|       |             |                             | •              | •            | must be cleared           | d in softwar | e)             |       |

| h:: 0 |             | 30/INT exter                |                |              | cur                       |              |                |       |

| bit 0 |             | Port Change                 | •              | •            | d atata (muat ba          | . cloared in | ooffworo)      |       |

|       |             | of the RB7:R                |                | •            | d state (must be<br>state | e cleared in | sollware)      |       |

|       |             |                             |                |              |                           |              |                |       |

|       | Legend:     |                             |                |              |                           |              |                |       |

|       | R = Reada   | ble bit                     | VV = V         | Vritable bit | U = Unimpl                | emented b    | it, read as '( | )'    |

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

## 2.4 PCL and PCLATH

The program counter (PC) specifies the address of the instruction to fetch for execution. The PC is 13 bits wide. The low byte is called the PCL register. This register is readable and writable. The high byte is called the PCH register. This register contains the PC<12:8> bits and is not directly readable or writable. If the program counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP. All updates to the PCH register go through the PCLATH register.

### 2.4.1 STACK

The stack allows a combination of up to 8 program calls and interrupts to occur. The stack contains the return address from this branch in program execution.

Mid-range devices have an 8 level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not modified when the stack is PUSHed or POPed.

After the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

## 2.5 Indirect Addressing; INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*). This is indirect addressing.

#### EXAMPLE 2-1: INDIRECT ADDRESSING

- Register file 05 contains the value 10h

- Register file 06 contains the value 0Ah

- Load the value 05 into the FSR register

- A read of the INDF register will return the value of 10h

- Increment the value of the FSR register by one (FSR = 06)

- A read of the INDF register now will return the value of 0Ah.

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no-operation (although STATUS bits may be affected).

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-2.

#### EXAMPLE 2-2: HOW TO CLEAR RAM USING INDIRECT ADDRESSING

|        | movlw | 0x20  | ;initialize pointer  |

|--------|-------|-------|----------------------|

|        | movwf | FSR   | ;to RAM              |

| NEXT   | clrf  | INDF  | clear INDF register; |

|        | incf  | FSR   | ;inc pointer         |

|        | btfss | FSR,4 | ;all done?           |

|        | goto  | NEXT  | ;NO, clear next      |

| CONTIN | IUE   |       |                      |

|        | :     |       | ;YES, continue       |

|        |       |       |                      |

An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 2-3. However, IRP is not used in the PIC16F84A.

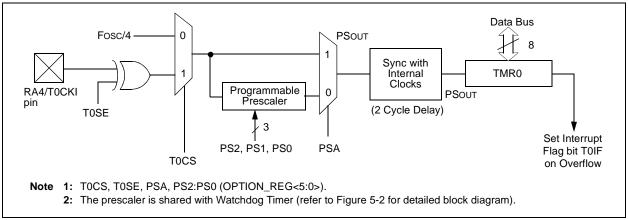

## 5.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- · Internal or external clock select

- Edge select for external clock

- 8-bit software programmable prescaler

- Interrupt-on-overflow from FFh to 00h

Figure 5-1 is a simplified block diagram of the Timer0 module.

Additional information on timer modules is available in the PIC<sup>®</sup> Mid-Range Reference Manual (DS33023).

## 5.1 Timer0 Operation

Timer0 can operate as a timer or as a counter.

Timer mode is selected by clearing bit TOCS (OPTION\_REG<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting bit TOCS (OPTION\_REG<5>). In Counter mode, Timer0 will increment, either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit, TOSE (OPTION\_REG<4>). Clearing bit TOSE selects the rising edge. Restrictions on the external clock input are discussed below.

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization. Additional information on external clock requirements is available in the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023).

#### 5.2 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer, respectively (Figure 5-2). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that there is only one prescaler available which is mutually exclusively shared between the Timer0 module and the Watchdog Timer. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa.

The prescaler is not readable or writable.

The PSA and PS2:PS0 bits (OPTION\_REG<3:0>) determine the prescaler assignment and prescale ratio.

Clearing bit PSA will assign the prescaler to the Timer0 module. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4, ..., 1:256 are selectable.

Setting bit PSA will assign the prescaler to the Watchdog Timer (WDT). When the prescaler is assigned to the WDT, prescale values of 1:1, 1:2, ..., 1:128 are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT.

Note: Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count, but will not change the prescaler assignment.

### FIGURE 5-1: TIMER0 BLOCK DIAGRAM

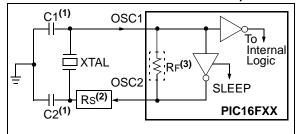

## 6.2 Oscillator Configurations

#### 6.2.1 OSCILLATOR TYPES

The PIC16F84A can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

## 6.2.2 CRYSTAL OSCILLATOR/CERAMIC RESONATORS

In XT, LP, or HS modes, a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 6-1).

#### FIGURE 6-1: CRYSTAL/CERAMIC RESONATOR OPERATION (HS, XT OR LP OSC CONFIGURATION)

- Note 1: See Table 6-1 for recommended values of C1 and C2.

- **2:** A series resistor (Rs) may be required for AT strip cut crystals.

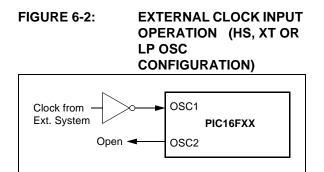

The PIC16F84A oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP, or HS modes, the device can have an external clock source to drive the OSC1/CLKIN pin (Figure 6-2).

## TABLE 6-1:CAPACITOR SELECTION FOR<br/>CERAMIC RESONATORS

| Ranges Tested:                                 |                                                                                                                                                                 |                                                                                                                     |                                                                                                                       |  |  |  |  |  |

|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Mode                                           | Freq                                                                                                                                                            | OSC1/C1                                                                                                             | OSC2/C2                                                                                                               |  |  |  |  |  |

| ХТ                                             | 455 kHz<br>2.0 MHz<br>4.0 MHz                                                                                                                                   | 2.0 MHz 15 - 33 pF 15 -                                                                                             |                                                                                                                       |  |  |  |  |  |

| HS                                             | 8.0 MHz<br>10.0 MHz                                                                                                                                             | 15 - 33 pF<br>15 - 33 pF                                                                                            | 15 - 33 pF<br>15 - 33 pF                                                                                              |  |  |  |  |  |

| id<br>Hi<br>of<br>sta<br>gu<br>its<br>cc<br>ap | ecommended<br>entical to the r<br>gher capacita<br>the oscillato<br>art-up time. Th<br>idance only.<br>own charac<br>onsult the reso<br>opropriate val<br>ents. | anges tested<br>nce increases<br>r, but also ir<br>hese values a<br>Since each re<br>teristics, the<br>mator manufa | in this table.<br>Is the stability<br>increases the<br>re for design<br>esonator has<br>user should<br>cturer for the |  |  |  |  |  |

| Note: | When using resonators with frequencies   |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|

|       | above 3.5 MHz, the use of HS mode rather |  |  |  |  |  |

|       | than XT mode, is recommended. HS mode    |  |  |  |  |  |

|       | may be used at any VDD for which the     |  |  |  |  |  |

|       | controller is rated.                     |  |  |  |  |  |

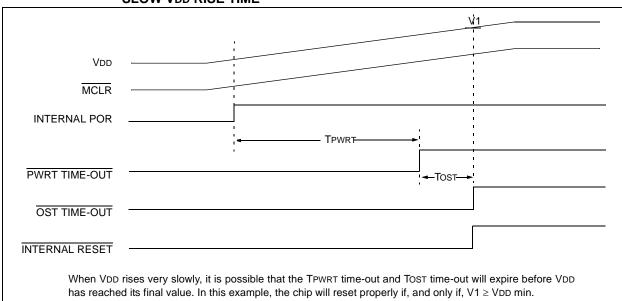

### FIGURE 6-9: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD): SLOW VDD RISE TIME

## 6.7 Time-out Sequence and \_\_\_\_\_ Power-down Status Bits (TO/PD)

On power-up (Figures 6-6 through 6-9), the time-out sequence is as follows:

- 1. PWRT time-out is invoked after a POR has expired.

- 2. Then, the OST is activated.

The total time-out will vary based on oscillator configuration and PWRTE configuration bit status. For example, in RC mode with the PWRT disabled, there will be no time-out at all.

## TABLE 6-5:TIME-OUT IN VARIOUSSITUATIONS

| Oscillator    | Powe                | Wake-up          |               |  |

|---------------|---------------------|------------------|---------------|--|

| Configuration | PWRT<br>Enabled     | PWRT<br>Disabled | from<br>SLEEP |  |

| XT, HS, LP    | 72 ms +<br>1024Tosc | 1024Tosc         | 1024Tosc      |  |

| RC            | 72 ms               | _                | _             |  |

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then bringing  $\overline{\text{MCLR}}$  high, execution will begin immediately (Figure 6-6). This is useful for testing purposes or to synchronize more than one PIC16F84A device when operating in parallel.

Table 6-6 shows the significance of the  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits. Table 6-3 lists the RESET conditions for some special registers, while Table 6-4 lists the RESET conditions for all the registers.

TABLE 6-6: STATUS BITS AND THEIR SIGNIFICANCE

| то | PD | Condition                           |  |  |  |  |  |

|----|----|-------------------------------------|--|--|--|--|--|

| 1  | 1  | Power-on Reset                      |  |  |  |  |  |

| 0  | x  | Illegal, TO is set on POR           |  |  |  |  |  |

| х  | 0  | Illegal, PD is set on POR           |  |  |  |  |  |

| 0  | 1  | WDT Reset (during normal operation) |  |  |  |  |  |

| 0  | 0  | WDT Wake-up                         |  |  |  |  |  |

| 1  | 1  | MCLR during normal operation        |  |  |  |  |  |

| 1  | 0  | MCLR during SLEEP or interrupt      |  |  |  |  |  |

|    |    | wake-up from SLEEP                  |  |  |  |  |  |

## 6.11.3 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs **during or after** the execution of a SLEEP instruction, the device will immediately wake-up from SLEEP. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

### 6.12 Program Verification/Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

## 6.13 ID Locations

Four memory locations (2000h - 2004h) are designated as ID locations to store checksum or other code identification numbers. These locations are not accessible during normal execution but are readable and writable only during program/verify. Only the four Least Significant bits of ID location are usable.

## 6.14 In-Circuit Serial Programming

PIC16F84A microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground, and the programming voltage. Customers can manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product, allowing the most recent firmware or custom firmware to be programmed.

For complete details of Serial Programming, please refer to the In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) Guide, (DS30277).

NOTES:

## 8.11 PICkit 2 Development Programmer/Debugger and PICkit 2 Debug Express

The PICkit<sup>™</sup> 2 Development Programmer/Debugger is a low-cost development tool with an easy to use interface for programming and debugging Microchip's Flash families of microcontrollers. The full featured Windows® programming interface supports baseline (PIC10F, PIC12F5xx, PIC16F5xx), midrange (PIC12F6xx, PIC16F), PIC18F, PIC24, dsPIC30, dsPIC33, and PIC32 families of 8-bit, 16-bit, and 32-bit microcontrollers, and many Microchip Serial EEPROM products. With Microchip's powerful MPLAB Integrated Development Environment (IDE) the PICkit<sup>™</sup> 2 enables in-circuit debugging on most PIC<sup>®</sup> microcontrollers. In-Circuit-Debugging runs, halts and single steps the program while the PIC microcontroller is embedded in the application. When halted at a breakpoint, the file registers can be examined and modified.

The PICkit 2 Debug Express include the PICkit 2, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

## 8.12 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an MMC card for file storage and data applications.

## 8.13 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

## 9.1 DC Characteristics

| PIC16LF84A-04<br>(Commercial, Industrial)                                                                |        |                                                                  |            |                                                      |            |        |                                                                                                  |  |  |  |

|----------------------------------------------------------------------------------------------------------|--------|------------------------------------------------------------------|------------|------------------------------------------------------|------------|--------|--------------------------------------------------------------------------------------------------|--|--|--|

| PIC16F84A-04<br>(Commercial, Industrial, Extended)<br>PIC16F84A-20<br>(Commercial, Industrial, Extended) |        |                                                                  |            | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |            |        |                                                                                                  |  |  |  |

| Param<br>No.                                                                                             | Symbol | Characteristic                                                   | Min        | Тур†                                                 | Max        | Units  | Conditions                                                                                       |  |  |  |

|                                                                                                          | Vdd    | Supply Voltage                                                   |            |                                                      |            |        |                                                                                                  |  |  |  |

| D001                                                                                                     |        | 16LF84A                                                          | 2.0        | —                                                    | 5.5        | V      | XT, RC, and LP osc configuration                                                                 |  |  |  |

| D001<br>D001A                                                                                            |        | 16F84A                                                           | 4.0<br>4.5 | _                                                    | 5.5<br>5.5 | V<br>V | XT, RC and LP osc configuration<br>HS osc configuration                                          |  |  |  |

| D002                                                                                                     | Vdr    | RAM Data Retention<br>Voltage (Note 1)                           | 1.5        | —                                                    | —          | V      | Device in SLEEP mode                                                                             |  |  |  |

| D003                                                                                                     | Vpor   | VDD Start Voltage to ensure<br>internal Power-on Reset<br>signal | —          | Vss                                                  | —          | V      | See section on Power-on Reset for details                                                        |  |  |  |

| D004                                                                                                     | Svdd   | VDD Rise Rate to ensure<br>internal Power-on Reset<br>signal     | 0.05       | —                                                    | —          | V/ms   |                                                                                                  |  |  |  |

|                                                                                                          | Idd    | Supply Current (Note 2)                                          |            |                                                      |            |        |                                                                                                  |  |  |  |

| D010                                                                                                     |        | 16LF84A                                                          | —          | 1                                                    | 4          | mA     | RC and XT osc configuration (Note 4)<br>Fosc = 2.0 MHz, VDD = 5.5V                               |  |  |  |

| D010                                                                                                     |        | 16F84A                                                           | —          | 1.8                                                  | 4.5        | mA     | RC and XT osc configuration (Note 4)<br>FOSC = 4.0 MHz, VDD = 5.5V                               |  |  |  |

| D010A                                                                                                    |        |                                                                  | —          | 3                                                    | 10         | mA     | RC and XT osc configuration (Note 4)<br>Fosc = 4.0 MHz, VDD = 5.5V<br>(During FLASH programming) |  |  |  |

| D013                                                                                                     |        |                                                                  | —          | 10                                                   | 20         | mA     | HS osc configuration (PIC16F84A-20)<br>Fosc = 20 MHz, VDD = 5.5V                                 |  |  |  |

| D014                                                                                                     |        | 16LF84A                                                          | —          | 15                                                   | 45         | μA     | LP osc configuration<br>Fosc = 32 kHz, VDD = 2.0V, WDT disabled                                  |  |  |  |

Legend: Rows with standard voltage device data only are shaded for improved readability.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

NR Not rated for operation.

- **Note 1:** This is the limit to which VDD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

- The test conditions for all IDD measurements in active operation mode are:

- OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD,

- T0CKI = VDD,  $\overline{MCLR}$  = VDD; WDT enabled/disabled as specified.

- **3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- **4:** For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula IR = VDD/2REXT (mA) with REXT in kOhm.

- 5: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD measurement.

## 9.2 DC Characteristics: PIC16F84A-04 (Commercial, Industrial) PIC16F84A-20 (Commercial, Industrial) PIC16LF84A-04 (Commercial, Industrial)

| DC Characteristics<br>All Pins Except Power Supply Pins |        |                                         | Standard Operating Conditions (unless otherwise stated)Operating temperature $0^{\circ}C \leq TA \leq +70^{\circ}C$ (commercial) $-40^{\circ}C \leq TA \leq +85^{\circ}C$ (industrial)Operating voltage VDD range as described in DC specifications(Section 9.1) |      |            |        |                                                                                                                             |  |  |

|---------------------------------------------------------|--------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------|--------|-----------------------------------------------------------------------------------------------------------------------------|--|--|

| Param<br>No.                                            | Symbol | Characteristic                          | Min                                                                                                                                                                                                                                                              | Тур† | Мах        | Units  | Conditions                                                                                                                  |  |  |

|                                                         | VIL    | Input Low Voltage                       |                                                                                                                                                                                                                                                                  |      |            |        |                                                                                                                             |  |  |

|                                                         |        | I/O ports:                              |                                                                                                                                                                                                                                                                  |      |            |        |                                                                                                                             |  |  |

| D030                                                    |        | with TTL buffer                         | Vss                                                                                                                                                                                                                                                              | —    | 0.8        | V      | $4.5V \le VDD \le 5.5V$ (Note 4)                                                                                            |  |  |

| D030A                                                   |        |                                         | Vss                                                                                                                                                                                                                                                              | —    | 0.16Vdd    | V      | Entire range (Note 4)                                                                                                       |  |  |

| D031                                                    |        | with Schmitt Trigger buffer             | Vss                                                                                                                                                                                                                                                              | —    | 0.2Vdd     | V      | Entire range                                                                                                                |  |  |

| D032                                                    |        | MCLR, RA4/T0CKI                         | Vss                                                                                                                                                                                                                                                              | —    | 0.2Vdd     | V      |                                                                                                                             |  |  |

| D033                                                    |        | OSC1 (XT, HS and LP modes)              | Vss                                                                                                                                                                                                                                                              | —    | 0.3Vdd     | V      | (Note 1)                                                                                                                    |  |  |

| D034                                                    |        | OSC1 (RC mode)                          | Vss                                                                                                                                                                                                                                                              |      | 0.1Vdd     | V      |                                                                                                                             |  |  |

|                                                         | Vih    | Input High Voltage                      |                                                                                                                                                                                                                                                                  |      |            |        |                                                                                                                             |  |  |

|                                                         |        | I/O ports:                              |                                                                                                                                                                                                                                                                  | —    |            |        |                                                                                                                             |  |  |

| D040<br>D040A                                           |        | with TTL buffer                         | 2.0<br>0.25VDD+0.8                                                                                                                                                                                                                                               | _    | Vdd<br>Vdd | V<br>V | 4.5V ≤ VDD ≤ 5.5V ( <b>Note 4</b> )<br>Entire range ( <b>Note 4</b> )                                                       |  |  |

| D041                                                    |        | with Schmitt Trigger buffer             | 0.8 Vdd                                                                                                                                                                                                                                                          | —    | Vdd        |        | Entire range                                                                                                                |  |  |

| D042                                                    |        | MCLR,                                   | 0.8 Vdd                                                                                                                                                                                                                                                          | —    | Vdd        | V      |                                                                                                                             |  |  |

| D042A                                                   |        | RA4/T0CKI                               | 0.8 Vdd                                                                                                                                                                                                                                                          | —    | 8.5        | V      |                                                                                                                             |  |  |

| D043                                                    |        | OSC1 (XT, HS and LP modes)              | 0.8 Vdd                                                                                                                                                                                                                                                          | —    | Vdd        | V      | (Note 1)                                                                                                                    |  |  |

| D043A                                                   |        | OSC1 (RC mode)                          | 0.9 Vdd                                                                                                                                                                                                                                                          |      | Vdd        | V      |                                                                                                                             |  |  |

| D050                                                    | VHYS   | Hysteresis of Schmitt Trigger<br>Inputs | —                                                                                                                                                                                                                                                                | 0.1  | _          | V      |                                                                                                                             |  |  |

| D070                                                    | IPURB  | PORTB Weak Pull-up Current              | 50                                                                                                                                                                                                                                                               | 250  | 400        | μΑ     | VDD = 5.0V, VPIN = VSS                                                                                                      |  |  |

|                                                         | lı∟    | Input Leakage Current<br>(Notes 2, 3)   |                                                                                                                                                                                                                                                                  |      |            |        |                                                                                                                             |  |  |

| D060                                                    |        | I/O ports                               | _                                                                                                                                                                                                                                                                | —    | ±1         | μΑ     | $\label{eq:VSS} \begin{split} &V{\sf SS} \leq V{\sf PIN} \leq V{\sf DD}, \\ &P{\sf in} \mbox{ at hi-impedance} \end{split}$ |  |  |

| D061                                                    |        | MCLR, RA4/T0CKI                         | —                                                                                                                                                                                                                                                                | —    | ±5         | μΑ     | $Vss \leq V PIN \leq V DD$                                                                                                  |  |  |

| D063                                                    |        | OSC1                                    | _                                                                                                                                                                                                                                                                | _    | ±5         | μA     | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP osc configuration                                                                 |  |  |

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1 pin is a Schmitt Trigger input. Do not drive the PIC16F84A with an external clock while the device is in RC mode, or chip damage may result.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

**3:** Negative current is defined as coming out of the pin.

4: The user may choose the better of the two specs.

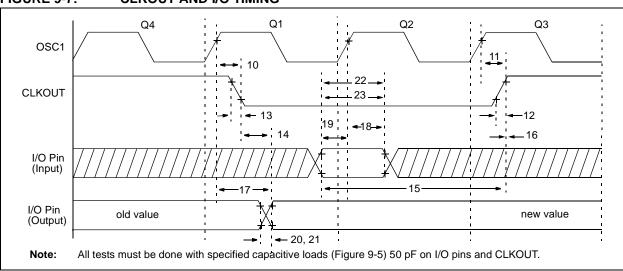

#### **CLKOUT AND I/O TIMING** FIGURE 9-7:

| Param<br>No. | Sym      | Characteristic                        |               | Min          | Тур† | Мах        | Units | Conditions |

|--------------|----------|---------------------------------------|---------------|--------------|------|------------|-------|------------|

| 10           | TosH2ckL | OSC1↑ to CLKOUT↓                      | Standard      | _            | 15   | 30         | ns    | (Note 1)   |

| 10A          |          |                                       | Extended (LF) |              | 15   | 120        | ns    | (Note 1)   |

| 11           | TosH2ckH | OSC1↑ to CLKOUT↑                      | Standard      |              | 15   | 30         | ns    | (Note 1)   |

| 11A          |          |                                       | Extended (LF) | —            | 15   | 120        | ns    | (Note 1)   |

| 12           | TckR     | CLKOUT rise time                      | Standard      | —            | 15   | 30         | ns    | (Note 1)   |

| 12A          |          |                                       | Extended (LF) |              | 15   | 100        | ns    | (Note 1)   |

| 13           | TckF     | CLKOUT fall time                      | Standard      | —            | 15   | 30         | ns    | (Note 1)   |

| 13A          |          |                                       | Extended (LF) | —            | 15   | 100        | ns    | (Note 1)   |

| 14           | TckL2ioV | CLKOUT $\downarrow$ to Port out valid | •             |              | _    | 0.5Tcy +20 | ns    | (Note 1)   |

| 15           | TioV2ckH | Port in valid before                  | Standard      | 0.30Tcy + 30 | _    | _          | ns    | (Note 1)   |

|              |          | CLKOUT ↑                              | Extended (LF) | 0.30Tcy + 80 | _    | _          | ns    | (Note 1)   |

| 16           | TckH2iol | Port in hold after CLKOUT 1           | •             | 0            | —    | _          | ns    | (Note 1)   |

| 17           | TosH2ioV | OSC1↑ (Q1 cycle) to                   | Standard      | —            | _    | 125        | ns    |            |

|              |          | Port out valid                        | Extended (LF) | —            | _    | 250        | ns    |            |

| 18           | TosH2iol | OSC1 <sup>↑</sup> (Q2 cycle) to Port  | Standard      | 10           | _    | _          | ns    |            |

|              |          | input invalid (I/O in hold time)      | Extended (LF) | 10           | _    | _          | ns    |            |

| 19           | TioV2osH | Port input valid to OSC1↑             | Standard      | -75          | _    | _          | ns    |            |

|              |          | (I/O in setup time)                   | Extended (LF) | -175         | _    | _          | ns    |            |

| 20           | TioR     | Port output rise time                 | Standard      | —            | 10   | 35         | ns    |            |

| 20A          |          |                                       | Extended (LF) | —            | 10   | 70         | ns    |            |

| 21           | TioF     | Port output fall time                 | Standard      | —            | 10   | 35         | ns    |            |

| 21A          |          |                                       | Extended (LF) | —            | 10   | 70         | ns    |            |

| 22           | TINP     | INT pin high                          | Standard      | 20           | —    | _          | ns    |            |

| 22A          |          | or low time                           | Extended (LF) | 55           | _    | _          | ns    |            |

| 23           | Trbp     | RB7:RB4 change INT                    | Standard      | Tosc§        | —    | _          | ns    |            |

| 23A          |          | high or low time                      | Extended (LF) | Tosc§        | _    |            | ns    |            |

Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested. † §

By design.

Note 1: Measurements are taken in RC mode where CLKOUT output is 4 x Tosc.

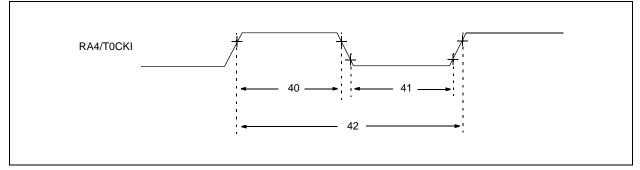

### FIGURE 9-9: TIMER0 CLOCK TIMINGS

## TABLE 9-5: TIMER0 CLOCK REQUIREMENTS

| Parameter<br>No. | Sym  | Characteristic  |                | Min                  | Тур† | Мах | Units | Conditions                                                                                        |

|------------------|------|-----------------|----------------|----------------------|------|-----|-------|---------------------------------------------------------------------------------------------------|

| 40               | Tt0H | U               | No Prescaler   | 0.5Tcy + 20          | —    | —   | ns    |                                                                                                   |

|                  |      | Width           | With Prescaler | 50<br>30             | _    | _   |       | $\begin{array}{l} 2.0V \leq V \text{DD} \leq 3.0V \\ 3.0V \leq V \text{DD} \leq 6.0V \end{array}$ |

| 41               | Tt0L | T0CKI Low Pulse | No Prescaler   | 0.5Tcy + 20          | —    | _   | ns    |                                                                                                   |

|                  |      | Width           | With Prescaler | 50<br>20             | _    | _   | -     | $\begin{array}{l} 2.0V \leq V\text{DD} \leq 3.0V\\ 3.0V \leq V\text{DD} \leq 6.0V \end{array}$    |

| 42               | Tt0P | T0CKI Period    |                | <u>Tcy + 40</u><br>N | —    | _   | ns    | N = prescale value<br>(2, 4,, 256)                                                                |

† Data in "Typ" column is at 5.0V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

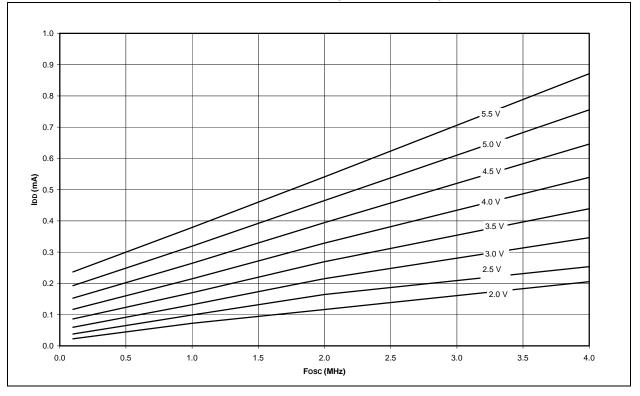

FIGURE 10-3: TYPICAL IDD vs. Fosc OVER VDD (XT MODE, 25°C)

© 2001-2013 Microchip Technology Inc.

# PIC16F84A

NOTES:

## **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| S35007C                                                                                       |  |  |  |

|-----------------------------------------------------------------------------------------------|--|--|--|

|                                                                                               |  |  |  |

|                                                                                               |  |  |  |

|                                                                                               |  |  |  |

| <ol> <li>How does this document meet your hardware and software development needs?</li> </ol> |  |  |  |

|                                                                                               |  |  |  |

|                                                                                               |  |  |  |

|                                                                                               |  |  |  |

|                                                                                               |  |  |  |

|                                                                                               |  |  |  |

| 4. What additions to the document do you think would enhance the structure and subject?       |  |  |  |

|                                                                                               |  |  |  |

| What deletions from the document could be made without affecting the overall usefulness?      |  |  |  |

|                                                                                               |  |  |  |

|                                                                                               |  |  |  |

| 6. Is there any incorrect or misleading information (what and where)?                         |  |  |  |

|                                                                                               |  |  |  |

|                                                                                               |  |  |  |

|                                                                                               |  |  |  |

|                                                                                               |  |  |  |

|                                                                                               |  |  |  |

DS35007C-page 86

## **PIC16F84A PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information (e.g., on pricing or delivery) refer to the factory or the listed sales office.

| PART NO.             | -XX X /XX XXX<br>Frequency Temperature Package Pattern<br>Range Range                                          | Examples:<br>a) PIC16F84A -04/P 301 = Commercial<br>temp., PDIP package, 4 MHz, normal VDD<br>limits, QTP pattern #301.                            |

|----------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Device               | PIC16F84A <sup>(1)</sup> , PIC16F84AT <sup>(2)</sup><br>PIC16LF84A <sup>(1)</sup> , PIC16LF84AT <sup>(2)</sup> | <ul> <li>b) PIC16LF84A - 04I/SO = Industrial temp.,<br/>SOIC package, 200 kHz, Extended VDD<br/>limits.</li> </ul>                                 |

| Frequency Range      | 04 = 4 MHz<br>20 = 20 MHz                                                                                      | <ul> <li>c) PIC16F84A - 20I/P = Industrial temp.,<br/>PDIP package, 20 MHz, normal VDD limits.</li> </ul>                                          |

| Temperature<br>Range | $- = 0^{\circ}C$ to $+70^{\circ}C$<br>I = $-40^{\circ}C$ to $+85^{\circ}C$                                     |                                                                                                                                                    |

| Package              | P = PDIP<br>SO = SOIC (Gull Wing, 300 mil body)<br>SS = SSOP                                                   | <ul> <li>Note 1: F = Standard VDD range<br/>LF = Extended VDD range</li> <li>2: T = in tape and reel - SOIC and<br/>SSOP packages only.</li> </ul> |

| Pattern              | QTP, SQTP, ROM Code (factory specified) or<br>Special Requirements . Blank for OTP and<br>Windowed devices.    |                                                                                                                                                    |

NOTES: