#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product StatusActiveCore ProcessorPICCore Size8-BitSpeed4MHzConnectivity-            |      |

|--------------------------------------------------------------------------------------|------|

| Core Size     8-Bit       Speed     4MHz                                             |      |

| Speed 4MHz                                                                           |      |

|                                                                                      |      |

| Connectivity -                                                                       |      |

|                                                                                      |      |

| Peripherals POR, WDT                                                                 |      |

| Number of I/O 13                                                                     |      |

| Program Memory Size 1.75KB (1K x 14)                                                 |      |

| Program Memory Type FLASH                                                            |      |

| EEPROM Size     64 x 8                                                               |      |

| RAM Size 68 x 8                                                                      |      |

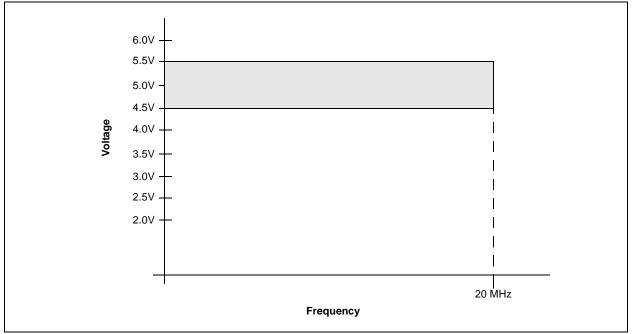

| Voltage - Supply (Vcc/Vdd) 2V ~ 5.5V                                                 |      |

| Data Converters -                                                                    |      |

| Oscillator Type External                                                             |      |

| Operating Temperature -40°C ~ 85°C (TA)                                              |      |

| Mounting Type Through Hole                                                           |      |

| Package / Case         18-DIP (0.300", 7.62mm)                                       |      |

| Supplier Device Package 18-PDIP                                                      |      |

| Purchase URL https://www.e-xfl.com/product-detail/microchip-technology/pic16lf84a-04 | łi-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

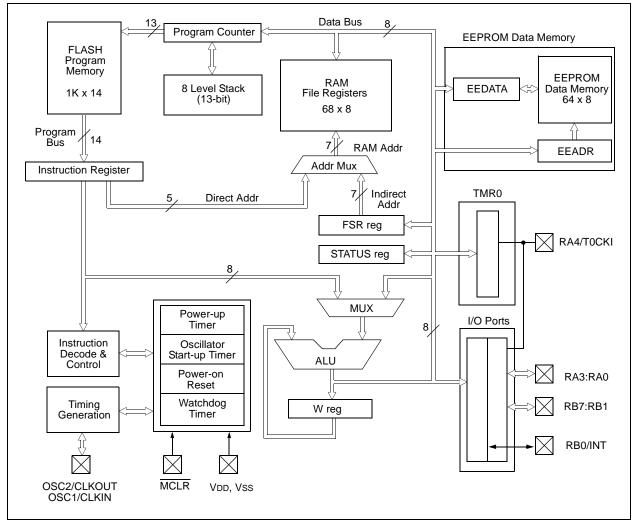

## 1.0 DEVICE OVERVIEW

This document contains device specific information for the operation of the PIC16F84A device. Additional information may be found in the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023), which may be downloaded from the Microchip website. The Reference Manual should be considered a complementary document to this data sheet, and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules.

The PIC16F84A belongs to the mid-range family of the  $PIC^{\textcircled{R}}$  microcontroller devices. A block diagram of the device is shown in Figure 1-1.

The program memory contains 1K words, which translates to 1024 instructions, since each 14-bit program memory word is the same width as each device instruction. The data memory (RAM) contains 68 bytes. Data EEPROM is 64 bytes.

There are also 13 I/O pins that are user-configured on a pin-to-pin basis. Some pins are multiplexed with other device functions. These functions include:

- External interrupt

- · Change on PORTB interrupt

- Timer0 clock input

Table 1-1 details the pinout of the device with descriptions and details for each pin.

FIGURE 1-1: PIC16F84A BLOCK DIAGRAM

| Pin Name         | PDIP<br>No. | SOIC<br>No. | SSOP<br>No. | l/O/P<br>Type | Buffer<br>Type         | Description                                                                                                                                                                                              |

|------------------|-------------|-------------|-------------|---------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN       | 16          | 16          | 18          | I             | ST/CMOS <sup>(3)</sup> | Oscillator crystal input/external clock source input.                                                                                                                                                    |

| OSC2/CLKOUT      | 15          | 15          | 19          | 0             | _                      | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. In RC mode, OSC2 pin outputs CLKOUT, which has 1/4 the frequency of OSC1 and denotes the instruction cycle rate. |

| MCLR             | 4           | 4           | 4           | I/P           | ST                     | Master Clear (Reset) input/programming voltage input. This pin is an active low RESET to the device.                                                                                                     |

|                  |             |             |             |               |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                      |

| RA0              | 17          | 17          | 19          | I/O           | TTL                    |                                                                                                                                                                                                          |

| RA1              | 18          | 18          | 20          | I/O           | TTL                    |                                                                                                                                                                                                          |

| RA2              | 1           | 1           | 1           | I/O           | TTL                    |                                                                                                                                                                                                          |

| RA3              | 2           | 2           | 2           | I/O           | TTL                    |                                                                                                                                                                                                          |

| RA4/T0CKI        | 3           | 3           | 3           | I/O           | ST                     | Can also be selected to be the clock input to the TMR0 timer/counter. Output is open drain type.                                                                                                         |

| RB0/INT          | 6           | 6           | 7           | I/O           | TTL/ST <sup>(1)</sup>  | PORTB is a bi-directional I/O port. PORTB can be<br>software programmed for internal weak pull-up on<br>all inputs.<br>RB0/INT can also be selected as an external                                       |

|                  |             |             |             |               |                        | interrupt pin.                                                                                                                                                                                           |

| RB1              | 7           | 7           | 8           | I/O           | TTL                    |                                                                                                                                                                                                          |

| RB2              | 8           | 8           | 9           | I/O           | TTL                    |                                                                                                                                                                                                          |

| RB3              | 9           | 9           | 10          | I/O           | TTL                    |                                                                                                                                                                                                          |

| RB4              | 10          | 10          | 11          | I/O           | TTL                    | Interrupt-on-change pin.                                                                                                                                                                                 |

| RB5              | 11          | 11          | 12          | I/O           | TTL                    | Interrupt-on-change pin.                                                                                                                                                                                 |

| RB6              | 12          | 12          | 13          | I/O           | TTL/ST <sup>(2)</sup>  | Interrupt-on-change pin.<br>Serial programming clock.                                                                                                                                                    |

| RB7              | 13          | 13          | 14          | I/O           | TTL/ST <sup>(2)</sup>  | Interrupt-on-change pin.<br>Serial programming data.                                                                                                                                                     |

| Vss              | 5           | 5           | 5,6         | Р             | —                      | Ground reference for logic and I/O pins.                                                                                                                                                                 |

| Vdd              | 14          | 14          | 15,16       | Р             | —                      | Positive supply for logic and I/O pins.                                                                                                                                                                  |

| Legend: I= input | 0 =         | Output      |             |               | put/Output             | P = Power                                                                                                                                                                                                |

#### TABLE 1-1:PIC16F84A PINOUT DESCRIPTION

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

## TABLE 6-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR

| Mode  | Freq                                                                                                                                            | OSC1/C1                                                                                                                                                             | OSC2/C2                                                                                                                                                                                              |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LP    | 32 kHz                                                                                                                                          | 68 - 100 pF                                                                                                                                                         | 68 - 100 pF                                                                                                                                                                                          |

|       | 200 kHz                                                                                                                                         | 15 - 33 pF                                                                                                                                                          | 15 - 33 pF                                                                                                                                                                                           |

| XT    | 100 kHz                                                                                                                                         | 100 - 150 pF                                                                                                                                                        | 100 - 150 pF                                                                                                                                                                                         |

|       | 2 MHz                                                                                                                                           | 15 - 33 pF                                                                                                                                                          | 15 - 33 pF                                                                                                                                                                                           |

|       | 4 MHz                                                                                                                                           | 15 - 33 pF                                                                                                                                                          | 15 - 33 pF                                                                                                                                                                                           |

| HS    | 4 MHz                                                                                                                                           | 15 - 33 pF                                                                                                                                                          | 15 - 33 pF                                                                                                                                                                                           |

|       | 20 MHz                                                                                                                                          | 15 - 33 pF                                                                                                                                                          | 15 - 33 pF                                                                                                                                                                                           |

| Note: | of the oscill<br>start-up time<br>guidance on<br>mode, as we<br>driving crysta<br>cation. Sinc<br>characteristic<br>crystal ma<br>values of ext | ator, but also<br>. These values<br>ly. Rs may be<br>ell as XT mode<br>als with low driv<br>e each crysta<br>cs, the user sho<br>nufacturer for<br>ternal component | ses the stability<br>increases the<br>s are for design<br>required in HS<br>, to avoid over-<br>ve level specifi-<br>il has its own<br>buld consult the<br>r appropriate<br>ents.<br>30 pF is recom- |

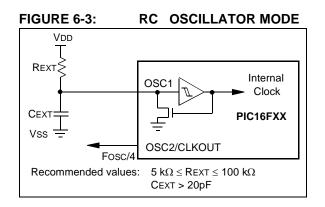

#### 6.2.3 RC OSCILLATOR

For timing insensitive applications, the RC device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) values, capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types also affects the oscillation frequency, especially for low CEXT values. The user needs to take into account variation, due to tolerance of the external R and C components. Figure 6-3 shows how an R/C combination is connected to the PIC16F84A.

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                       |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                            |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                   |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                         |

| Description:     | The contents of register 'f' are<br>decremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'.<br>If the result is 1, the next instruc-<br>tion is executed. If the result is 0,<br>then a NOP is executed instead,<br>making it a 2TCY instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                      |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                                                             |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                              |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                    |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result is<br>placed in the W register. If 'd' is 1,<br>the result is placed back in<br>register 'f'.<br>If the result is 1, the next instruc-<br>tion is executed. If the result is 0,<br>a NOP is executed instead, making<br>it a 2TCY instruction. |

| GOTO             | Unconditional Branch                                                                                                                                                                              |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                           |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                                |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                                   |

| Status Affected: | None                                                                                                                                                                                              |

| Description:     | GOTO is an unconditional branch.<br>The eleven-bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a two-<br>cycle instruction. |

| IORLW            | Inclusive OR Literal with W                                                                                               |

|------------------|---------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                                  |

| Operands:        | $0 \leq k \leq 255$                                                                                                       |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                              |

| Status Affected: | Z                                                                                                                         |

| Description:     | The contents of the W register are<br>OR'ed with the eight-bit literal 'k'.<br>The result is placed in the W<br>register. |

| IORWF            | Inclusive OR W with f                                                                                                                                                   |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] IORWF f,d                                                                                                                                                       |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                         |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                                |

| Status Affected: | Z                                                                                                                                                                       |

| Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is 0, the result is<br>placed in the W register. If 'd' is 1,<br>the result is placed back in<br>register 'f'. |

| INCF             | Increment f                                                                                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCF f,d                                                                                                                                                       |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                        |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                    |

| Status Affected: | Z                                                                                                                                                                      |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'. |

# PIC16F84A

| MOVF             | Move f                                                                                                                                                                                                                                                                              |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                         |

| Operation:       | (f) $\rightarrow$ (destination)                                                                                                                                                                                                                                                     |

| Status Affected: | Z                                                                                                                                                                                                                                                                                   |

| Description:     | The contents of register f are<br>moved to a destination dependant<br>upon the status of d. If $d = 0$ , des-<br>tination is W register. If $d = 1$ , the<br>destination is file register f itself.<br>d = 1 is useful to test a file register,<br>since status flag Z is affected. |

| RETFIE           | Return from Interrupt                         |

|------------------|-----------------------------------------------|

| Syntax:          | [label] RETFIE                                |

| Operands:        | None                                          |

| Operation:       | $TOS \rightarrow PC$ ,<br>1 $\rightarrow GIE$ |

| Status Affected: | None                                          |

| MOVLW            | Move Literal to W                                                                          |

|------------------|--------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                   |

| Operands:        | $0 \leq k \leq 255$                                                                        |

| Operation:       | $k \rightarrow (W)$                                                                        |

| Status Affected: | None                                                                                       |

| Description:     | The eight-bit literal 'k' is loaded into W register. The don't cares will assemble as 0's. |

| RETLW            | Return with Literal in W                                                                                                                                                            |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                            |  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                                                                                 |  |  |  |  |  |  |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow PC$                                                                                                                                        |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                |  |  |  |  |  |  |

| Description:     | The W register is loaded with the<br>eight-bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address).<br>This is a two-cycle instruction. |  |  |  |  |  |  |

| MOVWF            | Move W to f                                |  |  |  |  |

|------------------|--------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVWF f                   |  |  |  |  |

| Operands:        | $0 \leq f \leq 127$                        |  |  |  |  |

| Operation:       | $(W) \rightarrow (f)$                      |  |  |  |  |

| Status Affected: | None                                       |  |  |  |  |

| Description:     | Move data from W register to register 'f'. |  |  |  |  |

| RETURN           | Return from Subroutine                                                                                                                                     |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] RETURN                                                                                                                                             |  |  |  |  |  |

| Operands:        | None                                                                                                                                                       |  |  |  |  |  |

| Operation:       | $TOS \rightarrow PC$                                                                                                                                       |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                       |  |  |  |  |  |

| Description:     | Return from subroutine. The stack<br>is POPed and the top of the stack<br>(TOS) is loaded into the program<br>counter. This is a two-cycle<br>instruction. |  |  |  |  |  |

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| XORLW                   | Exclusive OR Literal with W                                                                | XORWF            | Exclusive OR W with f                                                                                                                                                       |

|-------------------------|--------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                 | [ <i>label</i> ] XORLW k                                                                   | Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                  |

| Operands:<br>Operation: | $0 \le k \le 255$<br>(W) .XOR. $k \rightarrow$ (W)                                         | Operands:        | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                          |

| Status Affected:        | Z                                                                                          | Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                   |

| Description:            | The contents of the W register                                                             | Status Affected: | Z                                                                                                                                                                           |

|                         | are XOR'ed with the eight-bit lit-<br>eral 'k'. The result is placed in<br>the W register. | Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |

#### 8.7 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 8.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with incircuit debugger systems (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 8.9 MPLAB ICD 3 In-Circuit Debugger System

MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost effective high-speed hardware debugger/programmer for Microchip Flash Digital Signal Controller (DSC) and microcontroller (MCU) devices. It debugs and programs PIC<sup>®</sup> Flash microcontrollers and dsPIC<sup>®</sup> DSCs with the powerful, yet easyto-use graphical user interface of MPLAB Integrated Development Environment (IDE).

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

#### 8.10 PICkit 3 In-Circuit Debugger/ Programmer and PICkit 3 Debug Express

The MPLAB PICkit 3 allows debugging and programming of PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB Integrated Development Environment (IDE). The MPLAB PICkit 3 is connected to the design engineer's PC using a full speed USB interface and can be connected to the target via an Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup>.

The PICkit 3 Debug Express include the PICkit 3, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

# PIC16F84A

## 9.3 AC (Timing) Characteristics

#### 9.3.1 TIMING PARAMETER SYMBOLOGY

The timing parameter symbols have been created following one of the following formats:

1. TppS2ppS

2. TppS

| Т         |                                    |         |                           |

|-----------|------------------------------------|---------|---------------------------|

| F         | Frequency                          | Т       | Time                      |

| Lowercase | e letters (pp) and their meanings: |         |                           |

| рр        |                                    |         |                           |

| 2         | to                                 | OS, OSC | OSC1                      |

| ck        | CLKOUT                             | ost     | oscillator start-up timer |

| су        | cycle time                         | pwrt    | power-up timer            |

| io        | I/O port                           | rbt     | RBx pins                  |

| inp       | INT pin                            | tO      | TOCKI                     |

| mp        | MCLR                               | wdt     | watchdog timer            |

| Uppercase | e letters and their meanings:      |         |                           |

| S         |                                    |         |                           |

| F         | Fall                               | Р       | Period                    |

| н         | High                               | R       | Rise                      |

| I         | Invalid (high impedance)           | V       | Valid                     |

| L         | Low                                | Z       | High Impedance            |

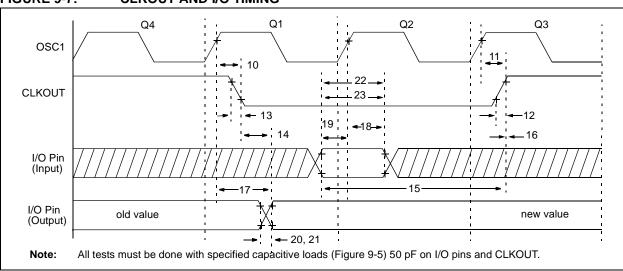

#### **CLKOUT AND I/O TIMING** FIGURE 9-7:

| Param<br>No. | Sym      | Characteristic                        | ;             | Min          | Тур† | Мах        | Units | Conditions |

|--------------|----------|---------------------------------------|---------------|--------------|------|------------|-------|------------|

| 10           | TosH2ckL | OSC1↑ to CLKOUT↓                      | Standard      | _            | 15   | 30         | ns    | (Note 1)   |

| 10A          |          |                                       | Extended (LF) |              | 15   | 120        | ns    | (Note 1)   |

| 11           | TosH2ckH | OSC1↑ to CLKOUT↑                      | Standard      |              | 15   | 30         | ns    | (Note 1)   |

| 11A          |          |                                       | Extended (LF) | —            | 15   | 120        | ns    | (Note 1)   |

| 12           | TckR     | CLKOUT rise time                      | Standard      | —            | 15   | 30         | ns    | (Note 1)   |

| 12A          |          |                                       | Extended (LF) |              | 15   | 100        | ns    | (Note 1)   |

| 13           | TckF     | CLKOUT fall time                      | Standard      | —            | 15   | 30         | ns    | (Note 1)   |

| 13A          |          |                                       | Extended (LF) | —            | 15   | 100        | ns    | (Note 1)   |

| 14           | TckL2ioV | CLKOUT $\downarrow$ to Port out valid | •             |              | _    | 0.5Tcy +20 | ns    | (Note 1)   |

| 15           | TioV2ckH | Port in valid before                  | Standard      | 0.30Tcy + 30 | _    | _          | ns    | (Note 1)   |

|              |          | CLKOUT ↑                              | Extended (LF) | 0.30Tcy + 80 | _    | _          | ns    | (Note 1)   |

| 16           | TckH2iol | Port in hold after CLKOUT 1           | •             | 0            | —    | _          | ns    | (Note 1)   |

| 17           | TosH2ioV | OSC1 <sup>↑</sup> (Q1 cycle) to       | Standard      | —            | _    | 125        | ns    |            |

|              |          | Port out valid                        | Extended (LF) | —            | _    | 250        | ns    |            |

| 18           | TosH2iol | OSC1 <sup>↑</sup> (Q2 cycle) to Port  | Standard      | 10           | _    | _          | ns    |            |

|              |          | input invalid (I/O in hold time)      | Extended (LF) | 10           | _    | _          | ns    |            |

| 19           | TioV2osH | Port input valid to OSC1↑             | Standard      | -75          | _    | —          | ns    |            |

|              |          | (I/O in setup time)                   | Extended (LF) | -175         | _    | —          | ns    |            |

| 20           | TioR     | Port output rise time                 | Standard      | —            | 10   | 35         | ns    |            |

| 20A          |          |                                       | Extended (LF) | —            | 10   | 70         | ns    |            |

| 21           | TioF     | Port output fall time                 | Standard      | —            | 10   | 35         | ns    |            |

| 21A          |          |                                       | Extended (LF) | —            | 10   | 70         | ns    |            |

| 22           | TINP     | INT pin high                          | Standard      | 20           | —    | _          | ns    |            |

| 22A          |          | or low time                           | Extended (LF) | 55           | _    | _          | ns    |            |

| 23           | Trbp     | RB7:RB4 change INT                    | Standard      | Tosc§        | —    | _          | ns    |            |

| 23A          |          | high or low time                      | Extended (LF) | Tosc§        | _    |            | ns    |            |

Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested. † §

By design.

Note 1: Measurements are taken in RC mode where CLKOUT output is 4 x Tosc.

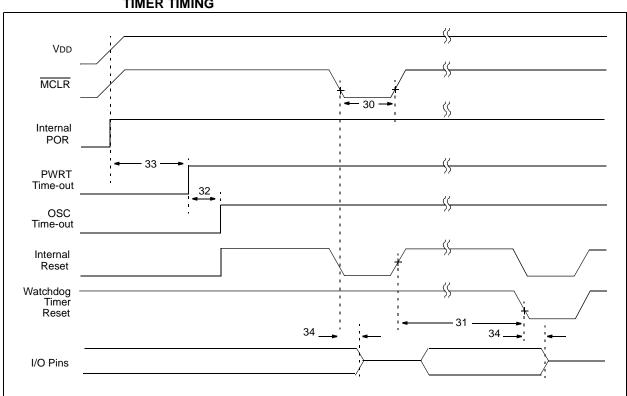

## FIGURE 9-8: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

## TABLE 9-4:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND<br/>POWER-UP TIMER REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                                   | Min | Тур†     | Max | Units | Conditions         |

|------------------|-------|--------------------------------------------------|-----|----------|-----|-------|--------------------|

| 30               | TmcL  | MCLR Pulse Width (low)                           | 2   | _        | _   | μS    | VDD = 5.0V         |

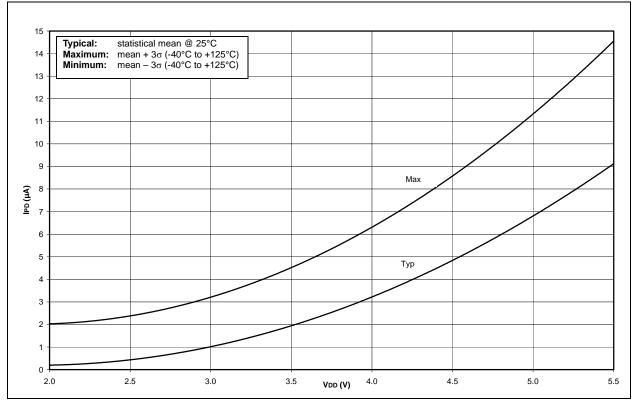

| 31               | TWDT  | Watchdog Timer Time-out<br>Period (No Prescaler) | 7   | 18       | 33  | ms    | VDD = 5.0V         |

| 32               | Tost  | Oscillation Start-up Timer<br>Period             |     | 1024Tosc |     | ms    | Tosc = OSC1 period |

| 33               | TPWRT | Power-up Timer Period                            | 28  | 72       | 132 | ms    | VDD = 5.0V         |

| 34               | Tioz  | I/O hi-impedance from MCLR<br>Low or RESET       | _   | _        | 100 | ns    |                    |

† Data in "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

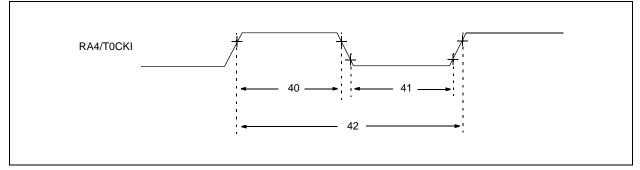

#### FIGURE 9-9: TIMER0 CLOCK TIMINGS

#### TABLE 9-5: TIMER0 CLOCK REQUIREMENTS

| Parameter<br>No. | Sym  | Characteristic  |                | Min                  | Тур† | Мах | Units | Conditions                                                                                        |

|------------------|------|-----------------|----------------|----------------------|------|-----|-------|---------------------------------------------------------------------------------------------------|

| 40               | Tt0H | U               | No Prescaler   | 0.5Tcy + 20          | —    | —   | ns    |                                                                                                   |

|                  |      | Width           | With Prescaler | 50<br>30             | _    | _   |       | $\begin{array}{l} 2.0V \leq V \text{DD} \leq 3.0V \\ 3.0V \leq V \text{DD} \leq 6.0V \end{array}$ |

| 41               | Tt0L | T0CKI Low Pulse | No Prescaler   | 0.5Tcy + 20          | —    | _   | ns    |                                                                                                   |

|                  |      | Width           | With Prescaler | 50<br>20             | _    | _   | -     | $\begin{array}{l} 2.0V \leq V\text{DD} \leq 3.0V\\ 3.0V \leq V\text{DD} \leq 6.0V \end{array}$    |

| 42               | Tt0P | T0CKI Period    |                | <u>Tcy + 40</u><br>N | —    | _   | ns    | N = prescale value<br>(2, 4,, 256)                                                                |

† Data in "Typ" column is at 5.0V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

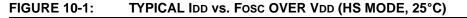

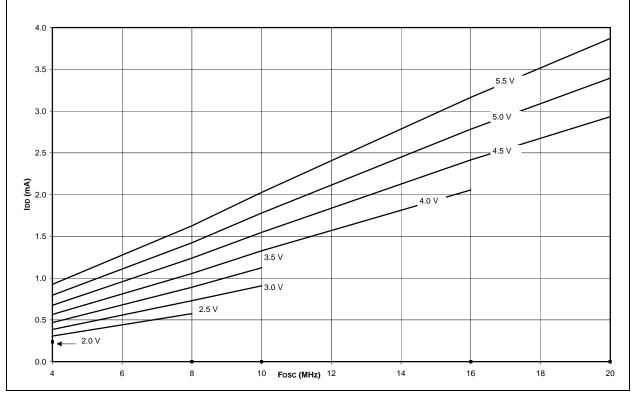

FIGURE 10-2: MAXIMUM IDD vs. Fosc OVER VDD (HS MODE, -40° TO +125°C)

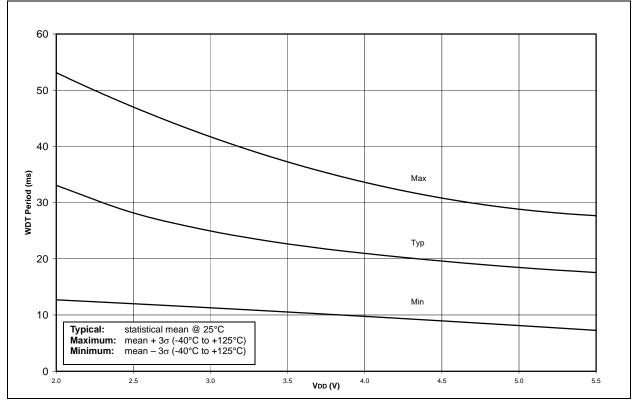

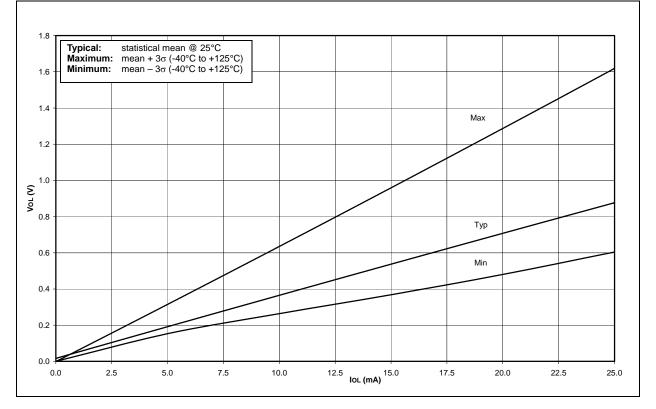

FIGURE 10-15: TYPICAL, MINIMUM AND MAXIMUM Vol vs. Iol (VDD = 5V, -40°C TO +125°C)

D

☐ 0.20 C A-B

2X

NOTE 5 D A Ν пппп Π ПППП E/2 E1 Е 0.10 C D || || || 1 2 3 Ш 0.33 C 2X 2X N/2 TIPS NOTE 1 NX b ⊕0.25@CA-BD NOTE 5 в е TOP VIEW 0.10 C 1 0.10 C NX А SEATING PLANE A2 Ċ A1 SIDE VIEW

VIEW A-A

Microchip Technology Drawing C04-051C Sheet 1 of 2

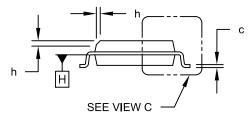

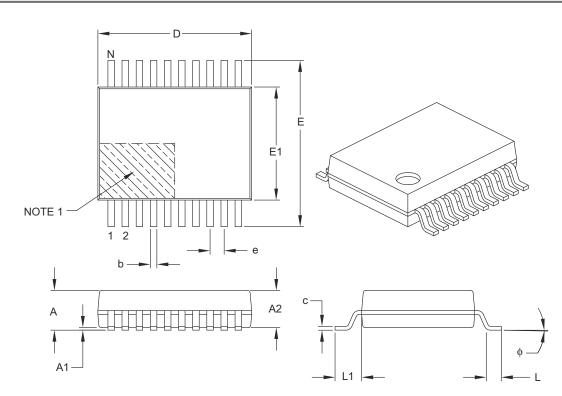

#### 20-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units    |                |          |      |  |

|--------------------------|----------|----------------|----------|------|--|

| Dimension                | n Limits | MIN            | NOM      | MAX  |  |

| Number of Pins           | Ν        |                | 20       |      |  |

| Pitch                    | е        |                | 0.65 BSC |      |  |

| Overall Height           | Α        | -              | -        | 2.00 |  |

| Molded Package Thickness | A2       | 1.65           | 1.75     | 1.85 |  |

| Standoff                 | A1       | 0.05           | -        | -    |  |

| Overall Width            | Е        | 7.40           | 7.80     | 8.20 |  |

| Molded Package Width     | E1       | 5.00           | 5.30     | 5.60 |  |

| Overall Length           | D        | 6.90 7.20 7.50 |          |      |  |

| Foot Length              | L        | 0.55           | 0.75     | 0.95 |  |

| Footprint                | L1       | 1.25 REF       |          |      |  |

| Lead Thickness           | с        | 0.09 – 0.25    |          |      |  |

| Foot Angle               | φ        | 0° 4° 8°       |          |      |  |

| Lead Width               | b        | 0.22           | -        | 0.38 |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-072B

# TABLE 1: CONVERSION CONSIDERATIONS - PIC16C84, PIC16F83/F84, PIC16CR83/CR84, PIC16F84A (CONTINUED)

| Difference                                                 | PIC16C84                                                                                                                                                                                                                   | PIC16F83/F84       | PIC16CR83/<br>CR84 | PIC16F84A          |  |

|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|--------------------|--|

| EEADR<7:6> and IDD                                         | It is recommended that<br>the EEADR<7:6> bits be<br>cleared. When either of<br>these bits is set, the maxi-<br>mum IDD for the device is<br>higher than when both are<br>cleared.                                          | N/A                | N/A                | N/A                |  |

| The polarity of the<br>PWRTE bit                           | PWRTE                                                                                                                                                                                                                      | PWRTE              | PWRTE              | PWRTE              |  |

| Recommended value of<br>REXT for RC oscillator<br>circuits | Rext = 3kΩ - 100kΩ                                                                                                                                                                                                         | Rext = 5kΩ - 100kΩ | Rext = 5kΩ - 100kΩ | Rext = 3kΩ - 100kΩ |  |

| GIE bit unintentional<br>enable                            | If an interrupt occurs while<br>the Global Interrupt<br>Enable (GIE) bit is being<br>cleared, the GIE bit may<br>unintentionally be re-<br>enabled by the user's<br>Interrupt Service Routine<br>(the RETFIE instruction). | N/A                | N/A                | N/A                |  |

| Packages                                                   | PDIP, SOIC                                                                                                                                                                                                                 | PDIP, SOIC         | PDIP, SOIC         | PDIP, SOIC, SSOP   |  |

| Open Drain High<br>Voltage (VoD)                           | 14V                                                                                                                                                                                                                        | 12V                | 12V                | 8.5V               |  |

### APPENDIX C: MIGRATION FROM BASELINE TO MID-RANGE DEVICES

This section discusses how to migrate from a baseline device (i.e., PIC16C5X) to a mid-range device (i.e., PIC16CXXX).

The following is the list of feature improvements over the PIC16C5X microcontroller family:

- Instruction word length is increased to 14-bits. This allows larger page sizes, both in program memory (2K now as opposed to 512K before) and the register file (128 bytes now versus 32 bytes before).

- 2. A PC latch register (PCLATH) is added to handle program memory paging. PA2, PA1 and PA0 bits are removed from the STATUS register and placed in the OPTION register.

- 3. Data memory paging is redefined slightly. The STATUS register is modified.

- 4. Four new instructions have been added: RETURN, RETFIE, ADDLW, and SUBLW. Two instructions, TRIS and OPTION, are being phased out, although they are kept for compatibility with PIC16C5X.

- 5. OPTION and TRIS registers are made addressable.

- 6. Interrupt capability is added. Interrupt vector is at 0004h.

- 7. Stack size is increased to eight-deep.

- 8. RESET vector is changed to 0000h.

- RESET of all registers is revisited. Five different RESET (and wake-up) types are recognized. Registers are reset differently.

- 10. Wake-up from SLEEP through interrupt is added.

- 11. Two separate timers, the Oscillator Start-up Timer (OST) and Power-up Timer (PWRT), are included for more reliable power-up. These timers are invoked selectively to avoid unnecessary delays on power-up and wake-up.

- 12. PORTB has weak pull-ups and interrupt-onchange features.

- 13. T0CKI pin is also a port pin (RA4/T0CKI).

- 14. FSR is a full 8-bit register.

- 15. "In system programming" is made possible. The user can program PIC16CXX devices using only five pins: VDD, VSS, VPP, RB6 (clock) and RB7 (data in/out).

To convert code written for PIC16C5X to PIC16F84A, the user should take the following steps:

- 1. Remove any program memory page select operations (PA2, PA1, PA0 bits) for CALL, GOTO.

- 2. Revisit any computed jump operations (write to PC or add to PC, etc.) to make sure page bits are set properly under the new scheme.

- 3. Eliminate any data memory page switching. Redefine data variables for reallocation.

- 4. Verify all writes to STATUS, OPTION, and FSR registers since these have changed.

- 5. Change RESET vector to 0000h.

## THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

### CUSTOMER SUPPORT

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support