Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | -                                                                           |

| Peripherals                | POR, WDT                                                                    |

| Number of I/O              | 13                                                                          |

| Program Memory Size        | 1.75KB (1K x 14)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 64 x 8                                                                      |

| RAM Size                   | 68 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 18-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf84a-04i-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

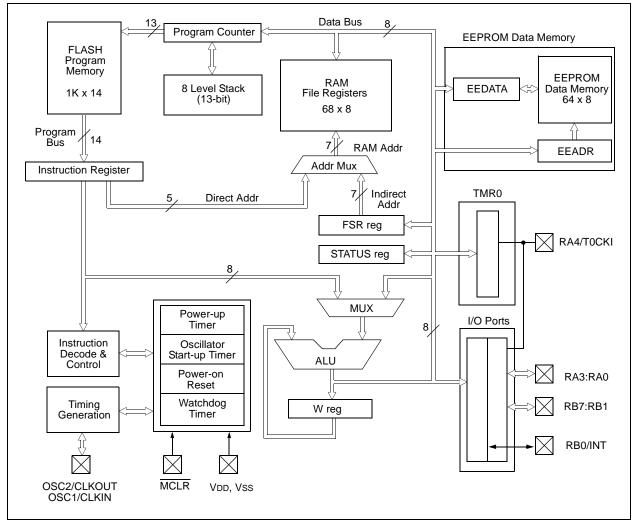

# 1.0 DEVICE OVERVIEW

This document contains device specific information for the operation of the PIC16F84A device. Additional information may be found in the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023), which may be downloaded from the Microchip website. The Reference Manual should be considered a complementary document to this data sheet, and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules.

The PIC16F84A belongs to the mid-range family of the  $PIC^{\textcircled{R}}$  microcontroller devices. A block diagram of the device is shown in Figure 1-1.

The program memory contains 1K words, which translates to 1024 instructions, since each 14-bit program memory word is the same width as each device instruction. The data memory (RAM) contains 68 bytes. Data EEPROM is 64 bytes.

There are also 13 I/O pins that are user-configured on a pin-to-pin basis. Some pins are multiplexed with other device functions. These functions include:

- External interrupt

- · Change on PORTB interrupt

- Timer0 clock input

Table 1-1 details the pinout of the device with descriptions and details for each pin.

FIGURE 1-1: PIC16F84A BLOCK DIAGRAM

# 2.0 MEMORY ORGANIZATION

There are two memory blocks in the PIC16F84A. These are the program memory and the data memory. Each block has its own bus, so that access to each block can occur during the same oscillator cycle.

The data memory can further be broken down into the general purpose RAM and the Special Function Registers (SFRs). The operation of the SFRs that control the "core" are described here. The SFRs used to control the peripheral modules are described in the section discussing each individual peripheral module.

The data memory area also contains the data EEPROM memory. This memory is not directly mapped into the data memory, but is indirectly mapped. That is, an indirect address pointer specifies the address of the data EEPROM memory to read/write. The 64 bytes of data EEPROM memory have the address range 0h-3Fh. More details on the EEPROM memory can be found in Section 3.0.

Additional information on device memory may be found in the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023).

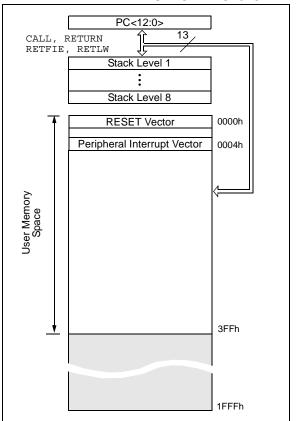

# 2.1 Program Memory Organization

The PIC16FXX has a 13-bit program counter capable of addressing an 8K x 14 program memory space. For the PIC16F84A, the first 1K x 14 (0000h-03FFh) are physically implemented (Figure 2-1). Accessing a location above the physically implemented address will cause a wraparound. For example, for locations 20h, 420h, 820h, C20h, 1020h, 1420h, 1820h, and 1C20h, the instruction will be the same.

The RESET vector is at 0000h and the interrupt vector is at 0004h.

### FIGURE 2-1:

### PROGRAM MEMORY MAP AND STACK - PIC16F84A

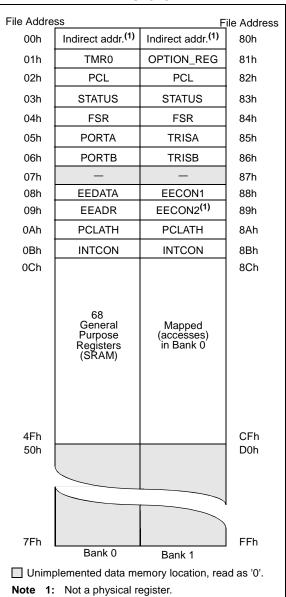

# 2.2 Data Memory Organization

The data memory is partitioned into two areas. The first is the Special Function Registers (SFR) area, while the second is the General Purpose Registers (GPR) area. The SFRs control the operation of the device.

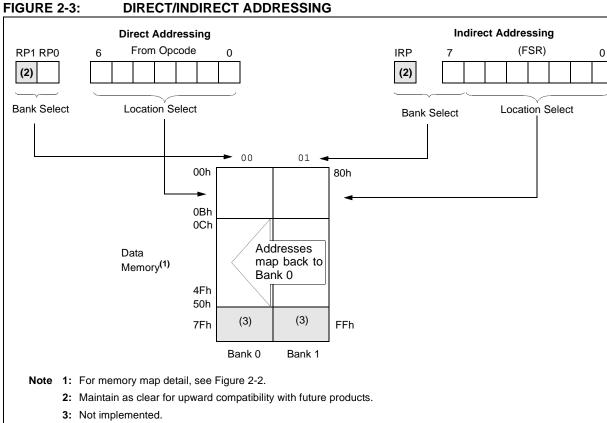

Portions of data memory are banked. This is for both the SFR area and the GPR area. The GPR area is banked to allow greater than 116 bytes of general purpose RAM. The banked areas of the SFR are for the registers that control the peripheral functions. Banking requires the use of control bits for bank selection. These control bits are located in the STATUS Register. Figure 2-2 shows the data memory map organization.

Instructions MOVWF and MOVF can move values from the W register to any location in the register file ("F"), and vice-versa.

The entire data memory can be accessed either directly using the absolute address of each register file or indirectly through the File Select Register (FSR) (Section 2.5). Indirect addressing uses the present value of the RP0 bit for access into the banked areas of data memory.

Data memory is partitioned into two banks which contain the general purpose registers and the special function registers. Bank 0 is selected by clearing the RP0 bit (STATUS<5>). Setting the RP0 bit selects Bank 1. Each Bank extends up to 7Fh (128 bytes). The first twelve locations of each Bank are reserved for the Special Function Registers. The remainder are General Purpose Registers, implemented as static RAM.

#### 2.2.1 GENERAL PURPOSE REGISTER FILE

Each General Purpose Register (GPR) is 8-bits wide and is accessed either directly or indirectly through the FSR (Section 2.5).

The GPR addresses in Bank 1 are mapped to addresses in Bank 0. As an example, addressing location 0Ch or 8Ch will access the same GPR.

#### FIGURE 2-2: REGISTER FILE MAP -PIC16F84A

# 2.3 Special Function Registers

The Special Function Registers (Figure 2-2 and Table 2-1) are used by the CPU and Peripheral functions to control the device operation. These registers are static RAM.

The special function registers can be classified into two sets, core and peripheral. Those associated with the core functions are described in this section. Those related to the operation of the peripheral features are described in the section for that specific feature.

| TABLE 2-1: | SPECIAL FUNCTION REGISTER FILE SUMMARY |

|------------|----------------------------------------|

|------------|----------------------------------------|

| Addr | Name                                                                           | Bit 7                               | Bit 6                                  | Bit 5        | Bit 4          | Bit 3         | Bit 2       | Bit 1             | Bit 0     | Value on<br>Power-on<br>RESET | Details<br>on page |

|------|--------------------------------------------------------------------------------|-------------------------------------|----------------------------------------|--------------|----------------|---------------|-------------|-------------------|-----------|-------------------------------|--------------------|

| Bank | 0                                                                              |                                     |                                        |              |                |               |             |                   |           |                               |                    |

| 00h  | 00h INDF Uses contents of FSR to address Data Memory (not a physical register) |                                     |                                        |              |                |               |             |                   |           |                               | 11                 |

| 01h  | TMR0                                                                           | 8-bit Rea                           | I-Time Clocl                           | k/Counter    |                |               |             |                   |           | xxxx xxxx                     | 20                 |

| 02h  | PCL                                                                            | Low Orde                            | er 8 bits of th                        | ne Prograi   | m Counter (Po  | C)            |             |                   |           | 0000 0000                     | 11                 |

| 03h  | STATUS <sup>(2)</sup>                                                          | IRP                                 | RP1                                    | RP0          | TO             | PD            | Z           | DC                | С         | 0001 1xxx                     | 8                  |

| 04h  | FSR                                                                            | Indirect [                          | Data Memory                            | / Address    | Pointer 0      |               |             |                   |           | xxxx xxxx                     | 11                 |

| 05h  | PORTA <sup>(4)</sup>                                                           | —                                   | _                                      | —            | RA4/T0CKI      | RA3           | RA2         | RA1               | RA0       | x xxxx                        | 16                 |

| 06h  | PORTB <sup>(5)</sup>                                                           | RB7                                 | RB6                                    | RB5          | RB4            | RB3           | RB2         | RB1               | RB0/INT   | XXXX XXXX                     | 18                 |

| 07h  | —                                                                              | Unimpler                            | mented locat                           | tion, read   | as '0'         |               |             |                   |           | —                             | —                  |

| 08h  | EEDATA                                                                         | EEPRON                              | EPROM Data Register                    |              |                |               |             |                   | xxxx xxxx | 13,14                         |                    |

| 09h  | EEADR                                                                          | EEPRON                              | EPROM Address Register                 |              |                |               |             |                   |           | XXXX XXXX                     | 13,14              |

| 0Ah  | PCLATH                                                                         | —                                   |                                        | —            | Write Buffer   | for upper 5   | bits of the | PC <sup>(1)</sup> |           | 0 0000                        | 11                 |

| 0Bh  | INTCON                                                                         | GIE                                 | GIE EEIE TOIE INTE RBIE TOIF INTF RBIF |              |                |               |             |                   | 0000 000x | 10                            |                    |

| Bank | 1                                                                              |                                     |                                        |              |                |               |             |                   |           |                               |                    |

| 80h  | INDF                                                                           | Uses Co                             | ntents of FS                           | R to addre   | ess Data Merr  | nory (not a p | ohysical re | gister)           |           |                               | 11                 |

| 81h  | OPTION_REG                                                                     | RBPU                                | INTEDG                                 | T0CS         | TOSE           | PSA           | PS2         | PS1               | PS0       | 1111 1111                     | 9                  |

| 82h  | PCL                                                                            | Low orde                            | er 8 bits of P                         | rogram Co    | ounter (PC)    | •             | •           |                   |           | 0000 0000                     | 11                 |

| 83h  | STATUS <sup>(2)</sup>                                                          | IRP                                 | RP1                                    | RP0          | TO             | PD            | Z           | DC                | С         | 0001 1xxx                     | 8                  |

| 84h  | FSR                                                                            | Indirect of                         | lata memory                            | address      | pointer 0      |               |             |                   |           | xxxx xxxx                     | 11                 |

| 85h  | TRISA                                                                          | —                                   | — PORTA Data Direction Register        |              |                |               |             |                   | 1 1111    | 16                            |                    |

| 86h  | TRISB                                                                          | PORTB I                             | PORTB Data Direction Register          |              |                |               |             |                   | 1111 1111 | 18                            |                    |

| 87h  | —                                                                              | Unimplemented location, read as '0' |                                        |              |                |               |             | —                 | —         |                               |                    |

| 88h  | EECON1                                                                         | —                                   | — — — EEIF WRERR WREN WR RD            |              |                |               |             |                   | 0 x000    | 13                            |                    |

| 89h  | EECON2                                                                         | EEPRON                              | A Control Re                           | egister 2 (r | not a physical | register)     |             |                   |           |                               | 14                 |

| 0Ah  | PCLATH                                                                         | —                                   | —                                      | —            | Write buffer f | for upper 5   | bits of the | PC <sup>(1)</sup> |           | 0 0000                        | 11                 |

| 0Bh  | INTCON                                                                         | GIE                                 | EEIE                                   | T0IE         | INTE           | RBIE          | T0IF        | INTF              | RBIF      | 0000 000x                     | 10                 |

Legend: x = unknown, u = unchanged. - = unimplemented, read as '0', q = value depends on condition

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a slave register for PC<12:8>. The contents of PCLATH can be transferred to the upper byte of the program counter, but the contents of PC<12:8> are never transferred to PCLATH.

2: The TO and PD status bits in the STATUS register are not affected by a MCLR Reset.

3: Other (non power-up) RESETS include: external RESET through MCLR and the Watchdog Timer Reset.

4: On any device RESET, these pins are configured as inputs.

5: This is the value that will be in the port output latch.

# 2.4 PCL and PCLATH

The program counter (PC) specifies the address of the instruction to fetch for execution. The PC is 13 bits wide. The low byte is called the PCL register. This register is readable and writable. The high byte is called the PCH register. This register contains the PC<12:8> bits and is not directly readable or writable. If the program counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP. All updates to the PCH register go through the PCLATH register.

# 2.4.1 STACK

The stack allows a combination of up to 8 program calls and interrupts to occur. The stack contains the return address from this branch in program execution.

Mid-range devices have an 8 level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not modified when the stack is PUSHed or POPed.

After the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

# 2.5 Indirect Addressing; INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*). This is indirect addressing.

#### EXAMPLE 2-1: INDIRECT ADDRESSING

- Register file 05 contains the value 10h

- Register file 06 contains the value 0Ah

- Load the value 05 into the FSR register

- A read of the INDF register will return the value of 10h

- Increment the value of the FSR register by one (FSR = 06)

- A read of the INDF register now will return the value of 0Ah.

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no-operation (although STATUS bits may be affected).

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-2.

#### EXAMPLE 2-2: HOW TO CLEAR RAM USING INDIRECT ADDRESSING

|        | movlw | 0x20  | ;initialize pointer  |

|--------|-------|-------|----------------------|

|        | movwf | FSR   | ;to RAM              |

| NEXT   | clrf  | INDF  | clear INDF register; |

|        | incf  | FSR   | ;inc pointer         |

|        | btfss | FSR,4 | ;all done?           |

|        | goto  | NEXT  | ;NO, clear next      |

| CONTIN | IUE   |       |                      |

|        | :     |       | ;YES, continue       |

|        |       |       |                      |

An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 2-3. However, IRP is not used in the PIC16F84A.

### 3.1 Reading the EEPROM Data Memory

To read a data memory location, the user must write the address to the EEADR register and then set control bit RD (EECON1<0>). The data is available, in the very next cycle, in the EEDATA register; therefore, it can be read in the next instruction. EEDATA will hold this value until another read or until it is written to by the user (during a write operation).

EXAMPLE 3-1: DATA EEPROM READ

| BCF   | STATUS, RPO | ; | Bank 0          |

|-------|-------------|---|-----------------|

| MOVLW | CONFIG_ADDR | ; |                 |

| MOVWF | EEADR       | ; | Address to read |

| BSF   | STATUS, RPO | ; | Bank 1          |

| BSF   | EECON1, RD  | ; | EE Read         |

| BCF   | STATUS, RPO | ; | Bank 0          |

| MOVF  | EEDATA, W   | ; | W = EEDATA      |

|       |             |   |                 |

# 3.2 Writing to the EEPROM Data Memory

To write an EEPROM data location, the user must first write the address to the EEADR register and the data to the EEDATA register. Then the user must follow a specific sequence to initiate the write for each byte.

EXAMPLE 3-2: DATA EEPROM WRITE

|          | BSF   | STATUS, RPO  | ; | Bank 1        |

|----------|-------|--------------|---|---------------|

|          | BCF   | INTCON, GIE  | ; | Disable INTs. |

|          | BSF   | EECON1, WREN | ; | Enable Write  |

|          | MOVLW | 55h          | ; |               |

|          | MOVWF | EECON2       | ; | Write 55h     |

| _ 0      | MOVLW | AAh          | ; |               |

| uired    | MOVWF | EECON2       | ; | Write AAh     |

| equi     | BSF   | EECON1,WR    | ; | Set WR bit    |

| ec<br>ec |       |              | ; | begin write   |

| ar of    | BSF   | INTCON, GIE  | ; | Enable INTs.  |

|          |       |              | _ |               |

The write will not initiate if the above sequence is not exactly followed (write 55h to EECON2, write AAh to EECON2, then set WR bit) for each byte. We strongly recommend that interrupts be disabled during this code segment. Additionally, the WREN bit in EECON1 must be set to enable write. This mechanism prevents accidental writes to data EEPROM due to errant (unexpected) code execution (i.e., lost programs). The user should keep the WREN bit clear at all times, except when updating EEPROM. The WREN bit is not cleared by hardware.

After a write sequence has been initiated, clearing the WREN bit will not affect this write cycle. The WR bit will be inhibited from being set unless the WREN bit is set.

At the completion of the write cycle, the WR bit is cleared in hardware and the EE Write Complete Interrupt Flag bit (EEIF) is set. The user can either enable this interrupt or poll this bit. EEIF must be cleared by software.

# 3.3 Write Verify

Depending on the application, good programming practice may dictate that the value written to the Data EEPROM should be verified (Example 3-3) to the desired value to be written. This should be used in applications where an EEPROM bit will be stressed near the specification limit.

Generally, the EEPROM write failure will be a bit which was written as a '0', but reads back as a '1' (due to leakage off the bit).

EXAMPLE 3-3: WRITE VERIFY

|      |       | <b>.</b>    |   |                      |

|------|-------|-------------|---|----------------------|

|      | BCF   | STATUS, RPO | ; | Bank 0               |

|      | :     |             | ; | Any code             |

|      | :     |             | ; | can go here          |

|      | MOVF  | EEDATA,W    | ; | Must be in Bank 0    |

|      | BSF   | STATUS, RPO | ; | Bank 1               |

| READ |       |             |   |                      |

|      | BSF   | EECON1, RD  | ; | YES, Read the        |

|      |       |             | ; | value written        |

|      | BCF   | STATUS, RPO | ; | Bank 0               |

|      |       |             | ; |                      |

|      |       |             | ; | Is the value written |

|      |       |             | ; | (in W reg) and       |

|      |       |             | ; | read (in EEDATA)     |

|      |       |             | ; | the same?            |

|      |       |             | ; |                      |

|      | SUBWF | EEDATA, W   | ; |                      |

|      | BTFSS | STATUS, Z   | ; | Is difference 0?     |

|      | GOTO  | WRITE_ERR   | ; | NO, Write error      |

#### TABLE 3-1: REGISTERS/BITS ASSOCIATED WITH DATA EEPROM

| Address | Name   | Bit 7                        | Bit 6                       | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Value on<br>Power-on<br>Reset | Value on<br>all other<br>RESETS |

|---------|--------|------------------------------|-----------------------------|-------|-------|-------|-------|-------|--------|-------------------------------|---------------------------------|

| 08h     | EEDATA | EEPRO                        | PROM Data Register          |       |       |       |       |       |        | XXXX XXXX                     | uuuu uuuu                       |

| 09h     | EEADR  | EEPRO                        | EPROM Address Register      |       |       |       |       |       |        | xxxx xxxx                     | uuuu uuuu                       |

| 88h     | EECON1 |                              | — — — EEIF WRERR WREN WR RD |       |       |       |       |       | 0 x000 | 0 q000                        |                                 |

| 89h     | EECON2 | N2 EEPROM Control Register 2 |                             |       |       |       |       |       |        |                               |                                 |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0', q = value depends upon condition. Shaded cells are not used by data EEPROM.

# 4.0 I/O PORTS

Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Additional information on I/O ports may be found in the PIC<sup>®</sup> Mid-Range Reference Manual (DS33023).

# 4.1 PORTA and TRISA Registers

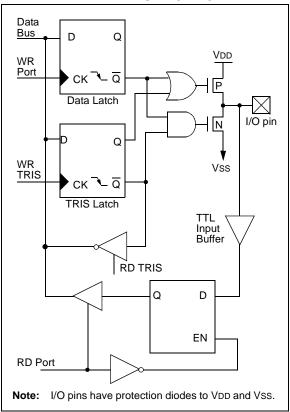

PORTA is a 5-bit wide, bi-directional port. The corresponding data direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin).

| Note: | On a Power-on Reset, these pins are con- |

|-------|------------------------------------------|

|       | figured as inputs and read as '0'.       |

Reading the PORTA register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read. This value is modified and then written to the port data latch.

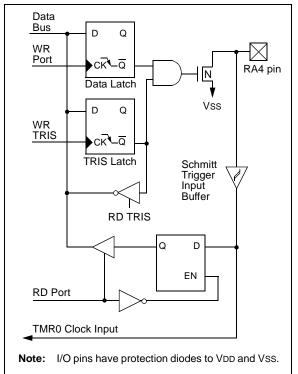

Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL input levels and full CMOS output drivers.

| BCF   | STATUS, RPO | ; |                       |

|-------|-------------|---|-----------------------|

| CLRF  | PORTA       | ; | Initialize PORTA by   |

|       |             | ; | clearing output       |

|       |             | ; | data latches          |

| BSF   | STATUS, RPO | ; | Select Bank 1         |

| MOVLW | 0x0F        | ; | Value used to         |

|       |             | ; | initialize data       |

|       |             | ; | direction             |

| MOVWF | TRISA       | ; | Set RA<3:0> as inputs |

|       |             | ; | RA4 as output         |

|       |             | ; | TRISA<7:5> are always |

|       |             | ; | read as '0'.          |

|       |             |   |                       |

#### FIGURE 4-1:

#### BLOCK DIAGRAM OF PINS RA3:RA0

FIGURE 4-2:

BLOCK DIAGRAM OF PIN RA4

| Name    | Bit  | Buffer Type           | I/O Consistency Function                                                                                               |

|---------|------|-----------------------|------------------------------------------------------------------------------------------------------------------------|

| RB0/INT | bit0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input.<br>Internal software programmable weak pull-up.                          |

| RB1     | bit1 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                         |

| RB2     | bit2 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                         |

| RB3     | bit3 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                         |

| RB4     | bit4 | TTL                   | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up.                           |

| RB5     | bit5 | TTL                   | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up.                           |

| RB6     | bit6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up. Serial programming clock. |

| RB7     | bit7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up. Serial programming data.  |

# TABLE 4-3:PORTB FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger.

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

#### TABLE 4-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address | Name       | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0   | Value on<br>Power-on<br>Reset | Value on<br>all other<br>RESETS |

|---------|------------|--------|--------|--------|--------|--------|--------|--------|---------|-------------------------------|---------------------------------|

| 06h     | PORTB      | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0/INT | xxxx xxxx                     | uuuu uuuu                       |

| 86h     | TRISB      | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0  | 1111 1111                     | 1111 1111                       |

| 81h     | OPTION_REG | RBPU   | INTEDG | TOCS   | T0SE   | PSA    | PS2    | PS1    | PS0     | 1111 1111                     | 1111 1111                       |

| 0Bh,8Bh | INTCON     | GIE    | EEIE   | TOIE   | INTE   | RBIE   | T0IF   | INTF   | RBIF    | 0000 000x                     | 0000 000u                       |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTB.

# 5.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- · Internal or external clock select

- Edge select for external clock

- 8-bit software programmable prescaler

- Interrupt-on-overflow from FFh to 00h

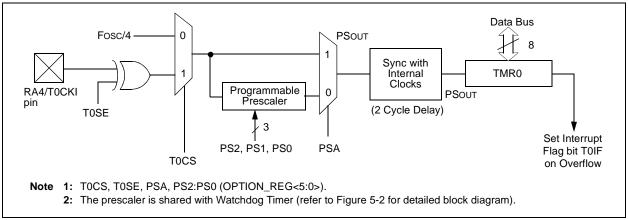

Figure 5-1 is a simplified block diagram of the Timer0 module.

Additional information on timer modules is available in the PIC<sup>®</sup> Mid-Range Reference Manual (DS33023).

# 5.1 Timer0 Operation

Timer0 can operate as a timer or as a counter.

Timer mode is selected by clearing bit TOCS (OPTION\_REG<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting bit TOCS (OPTION\_REG<5>). In Counter mode, Timer0 will increment, either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit, TOSE (OPTION\_REG<4>). Clearing bit TOSE selects the rising edge. Restrictions on the external clock input are discussed below.

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization. Additional information on external clock requirements is available in the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023).

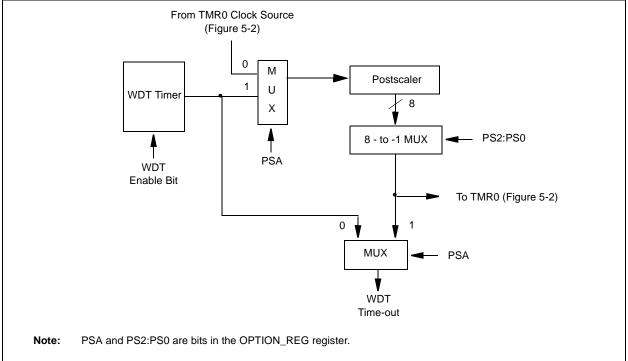

### 5.2 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer, respectively (Figure 5-2). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that there is only one prescaler available which is mutually exclusively shared between the Timer0 module and the Watchdog Timer. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa.

The prescaler is not readable or writable.

The PSA and PS2:PS0 bits (OPTION\_REG<3:0>) determine the prescaler assignment and prescale ratio.

Clearing bit PSA will assign the prescaler to the Timer0 module. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4, ..., 1:256 are selectable.

Setting bit PSA will assign the prescaler to the Watchdog Timer (WDT). When the prescaler is assigned to the WDT, prescale values of 1:1, 1:2, ..., 1:128 are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT.

Note: Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count, but will not change the prescaler assignment.

# FIGURE 5-1: TIMER0 BLOCK DIAGRAM

# TABLE 6-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR

| Mode  | Freq                                                                                                                                            | OSC1/C1                                                                                                                                                             | OSC2/C2                                                                                                                                                                                              |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LP    | 32 kHz                                                                                                                                          | 68 - 100 pF                                                                                                                                                         | 68 - 100 pF                                                                                                                                                                                          |

|       | 200 kHz                                                                                                                                         | 15 - 33 pF                                                                                                                                                          | 15 - 33 pF                                                                                                                                                                                           |

| XT    | 100 kHz                                                                                                                                         | 100 - 150 pF                                                                                                                                                        | 100 - 150 pF                                                                                                                                                                                         |

|       | 2 MHz                                                                                                                                           | 15 - 33 pF                                                                                                                                                          | 15 - 33 pF                                                                                                                                                                                           |

|       | 4 MHz                                                                                                                                           | 15 - 33 pF                                                                                                                                                          | 15 - 33 pF                                                                                                                                                                                           |

| HS    | 4 MHz                                                                                                                                           | 15 - 33 pF                                                                                                                                                          | 15 - 33 pF                                                                                                                                                                                           |

|       | 20 MHz                                                                                                                                          | 15 - 33 pF                                                                                                                                                          | 15 - 33 pF                                                                                                                                                                                           |

| Note: | of the oscill<br>start-up time<br>guidance on<br>mode, as we<br>driving crysta<br>cation. Sinc<br>characteristic<br>crystal ma<br>values of ext | ator, but also<br>. These values<br>ly. Rs may be<br>ell as XT mode<br>als with low driv<br>e each crysta<br>cs, the user sho<br>nufacturer for<br>ternal component | ses the stability<br>increases the<br>s are for design<br>required in HS<br>, to avoid over-<br>ve level specifi-<br>il has its own<br>buld consult the<br>r appropriate<br>ents.<br>30 pF is recom- |

# 6.2.3 RC OSCILLATOR

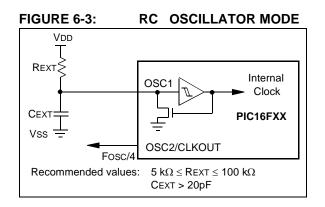

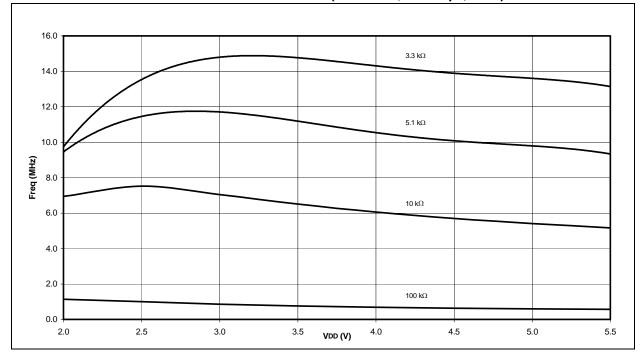

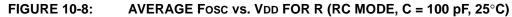

For timing insensitive applications, the RC device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) values, capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types also affects the oscillation frequency, especially for low CEXT values. The user needs to take into account variation, due to tolerance of the external R and C components. Figure 6-3 shows how an R/C combination is connected to the PIC16F84A.

#### 6.10.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken into account that under worst case conditions (VDD = Min., Temperature = Max., Max. WDT Prescaler), it may take several seconds before a WDT time-out occurs.

TABLE 6-7: SUMMARY OF REGISTERS ASSOCIATED WITH THE WATCHDOG TIMER

| Addr  | Name         | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on all<br>other<br>RESETS |

|-------|--------------|-------|--------|-------|-------|----------------------|-------|-------|-------|-------------------------------|---------------------------------|

| 2007h | Config. bits | (2)   | (2)    | (2)   | (2)   | PWRTE <sup>(1)</sup> | WDTE  | FOSC1 | FOSC0 | (2)                           |                                 |

| 81h   | OPTION_REG   | RBPU  | INTEDG | TOCS  | T0SE  | PSA                  | PS2   | PS1   | PS0   | 1111 1111                     | 1111 1111                       |

Legend: x = unknown. Shaded cells are not used by the WDT.

**Note 1:** See Register 6-1 for operation of the PWRTE bit.

2: See Register 6-1 and Section 6.12 for operation of the code and data protection bits.

# 9.3 AC (Timing) Characteristics

# 9.3.1 TIMING PARAMETER SYMBOLOGY

The timing parameter symbols have been created following one of the following formats:

1. TppS2ppS

2. TppS

| Т         |                                    |         |                           |

|-----------|------------------------------------|---------|---------------------------|

| F         | Frequency                          | Т       | Time                      |

| Lowercase | e letters (pp) and their meanings: |         |                           |

| рр        |                                    |         |                           |

| 2         | to                                 | OS, OSC | OSC1                      |

| ck        | CLKOUT                             | ost     | oscillator start-up timer |

| су        | cycle time                         | pwrt    | power-up timer            |

| io        | I/O port                           | rbt     | RBx pins                  |

| inp       | INT pin                            | tO      | TOCKI                     |

| mp        | MCLR                               | wdt     | watchdog timer            |

| Uppercase | e letters and their meanings:      |         |                           |

| S         |                                    |         |                           |

| F         | Fall                               | Р       | Period                    |

| н         | High                               | R       | Rise                      |

| I         | Invalid (high impedance)           | V       | Valid                     |

| L         | Low                                | Z       | High Impedance            |

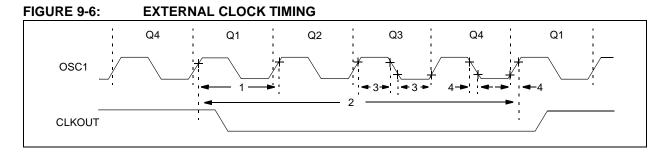

# 9.3.3 TIMING DIAGRAMS AND SPECIFICATIONS

# TABLE 9-2: EXTERNAL CLOCK TIMING REQUIREMENTS

| Param No. | Sym   | Characteristic                          | Min  | Тур†   | Max    | Units | Cond       | litions   |

|-----------|-------|-----------------------------------------|------|--------|--------|-------|------------|-----------|

|           | Fosc  | External CLKIN Frequency <sup>(1)</sup> | DC   |        | 2      | MHz   | XT, RC osc | (-04, LF) |

|           |       |                                         | DC   | —      | 4      | MHz   | XT, RC osc | (-04)     |

|           |       |                                         | DC   | —      | 20     | MHz   | HS osc     | (-20)     |

|           |       |                                         | DC   | —      | 200    | kHz   | LP osc     | (-04, LF) |

|           |       | Oscillator Frequency <sup>(1)</sup>     | DC   | _      | 2      | MHz   | RC osc     | (-04, LF) |

|           |       |                                         | DC   | —      | 4      | MHz   | RC osc     | (-04)     |

|           |       |                                         | 0.1  | —      | 2      | MHz   | XT osc     | (-04, LF) |

|           |       |                                         | 0.1  | —      | 4      | MHz   | XT osc     | (-04)     |

|           |       |                                         | 1.0  | —      | 20     | MHz   | HS osc     | (-20)     |

|           |       |                                         | DC   | —      | 200    | kHz   | LP osc     | (-04, LF) |

| 1         | Tosc  | External CLKIN Period <sup>(1)</sup>    | 500  |        |        | ns    | XT, RC osc | (-04, LF) |

|           |       |                                         | 250  | —      | —      | ns    | XT, RC osc | (-04)     |

|           |       |                                         | 50   | —      | —      | ns    | HS osc     | (-20)     |

|           |       |                                         | 5.0  | —      | —      | μs    | LP osc     | (-04, LF) |

|           |       | Oscillator Period <sup>(1)</sup>        | 500  | _      | _      | ns    | RC osc     | (-04, LF) |

|           |       |                                         | 250  | —      | —      | ns    | RC osc     | (-04)     |

|           |       |                                         | 500  | —      | 10,000 | ns    | XT osc     | (-04, LF) |

|           |       |                                         | 250  | —      | 10,000 | ns    | XT osc     | (-04)     |

|           |       |                                         | 50   | —      | 1,000  | ns    | HS osc     | (-20)     |

|           |       |                                         | 5.0  | _      |        | μs    | LP osc     | (-04, LF) |

| 2         | Тсү   | Instruction Cycle Time <sup>(1)</sup>   | 0.2  | 4/Fosc | DC     | μS    |            |           |

| 3         | TosL, | Clock in (OSC1) High or Low             | 60   | _      | _      | ns    | XT osc     | (-04, LF) |

|           | TosH  | Time                                    | 50   | —      | —      | ns    | XT osc     | (-04)     |

|           |       |                                         | 2.0  | —      | —      | μS    | LP osc     | (-04, LF) |

|           |       |                                         | 17.5 | —      | _      | ns    | HS osc     | (-20)     |

| 4         | TosR, | Clock in (OSC1) Rise or Fall            | 25   | —      | _      | ns    | XT osc     | (-04)     |

|           | TosF  | Time                                    | 50   | —      | —      | ns    | LP osc     | (-04, LF) |

|           |       |                                         | 7.5  | —      | —      | ns    | HS osc     | (-20)     |

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Instruction cycle period (Tcr) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "Min." values with an external clock applied to the OSC1 pin.

When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

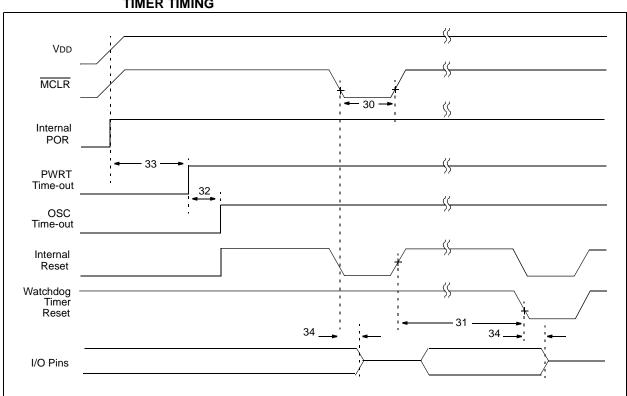

# FIGURE 9-8: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

# TABLE 9-4:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND<br/>POWER-UP TIMER REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                                   | Min | Тур†     | Max | Units | Conditions         |

|------------------|-------|--------------------------------------------------|-----|----------|-----|-------|--------------------|

| 30               | TmcL  | MCLR Pulse Width (low)                           | 2   | —        | _   | μS    | VDD = 5.0V         |

| 31               | TWDT  | Watchdog Timer Time-out<br>Period (No Prescaler) | 7   | 18       | 33  | ms    | VDD = 5.0V         |

| 32               | Tost  | Oscillation Start-up Timer<br>Period             |     | 1024Tosc |     | ms    | Tosc = OSC1 period |

| 33               | TPWRT | Power-up Timer Period                            | 28  | 72       | 132 | ms    | VDD = 5.0V         |

| 34               | Tioz  | I/O hi-impedance from MCLR<br>Low or RESET       | _   | _        | 100 | ns    |                    |

† Data in "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

FIGURE 10-7: AVERAGE FOSC vs. VDD FOR R (RC MODE, C = 22 pF, 25°C)

# PIC16F84A

NOTES:

# THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

# CUSTOMER SUPPORT

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support

# **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| S35007C |

|---------|

|         |

|         |

|         |

|         |

|         |

|         |

|         |

|         |

|         |

|         |

|         |

|         |

|         |

|         |

|         |

|         |

|         |

|         |

|         |

|         |

DS35007C-page 86

# Worldwide Sales and Service

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney Tel: 61-2-9868-6733

Fax: 61-2-9868-6755 China - Beijing

Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3187 Fax: 86-571-2819-3189

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Osaka** Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7828 Fax: 886-7-330-9305

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

# EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Fax: 45-4485-2829

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820

11/29/12