Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 4MHz                                                                         |

| Connectivity               | -                                                                            |

| Peripherals                | POR, WDT                                                                     |

| Number of I/O              | 13                                                                           |

| Program Memory Size        | 1.75KB (1K x 14)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 64 x 8                                                                       |

| RAM Size                   | 68 x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                    |

| Data Converters            | -                                                                            |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 18-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf84at-04i-so |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.0 MEMORY ORGANIZATION

There are two memory blocks in the PIC16F84A. These are the program memory and the data memory. Each block has its own bus, so that access to each block can occur during the same oscillator cycle.

The data memory can further be broken down into the general purpose RAM and the Special Function Registers (SFRs). The operation of the SFRs that control the "core" are described here. The SFRs used to control the peripheral modules are described in the section discussing each individual peripheral module.

The data memory area also contains the data EEPROM memory. This memory is not directly mapped into the data memory, but is indirectly mapped. That is, an indirect address pointer specifies the address of the data EEPROM memory to read/write. The 64 bytes of data EEPROM memory have the address range 0h-3Fh. More details on the EEPROM memory can be found in Section 3.0.

Additional information on device memory may be found in the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023).

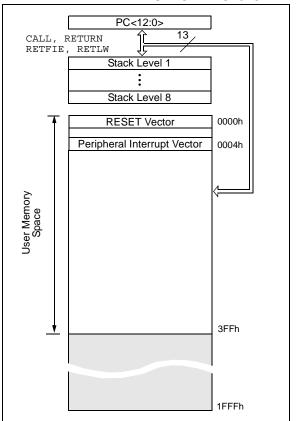

### 2.1 Program Memory Organization

The PIC16FXX has a 13-bit program counter capable of addressing an 8K x 14 program memory space. For the PIC16F84A, the first 1K x 14 (0000h-03FFh) are physically implemented (Figure 2-1). Accessing a location above the physically implemented address will cause a wraparound. For example, for locations 20h, 420h, 820h, C20h, 1020h, 1420h, 1820h, and 1C20h, the instruction will be the same.

The RESET vector is at 0000h and the interrupt vector is at 0004h.

#### FIGURE 2-1:

#### PROGRAM MEMORY MAP AND STACK - PIC16F84A

### 2.3 Special Function Registers

The Special Function Registers (Figure 2-2 and Table 2-1) are used by the CPU and Peripheral functions to control the device operation. These registers are static RAM.

The special function registers can be classified into two sets, core and peripheral. Those associated with the core functions are described in this section. Those related to the operation of the peripheral features are described in the section for that specific feature.

| TABLE 2-1: | SPECIAL FUNCTION REGISTER FILE SUMMARY |

|------------|----------------------------------------|

|------------|----------------------------------------|

| Addr   | Name                  | Bit 7                                               | Bit 6                                                      | Bit 5      | Bit 4         | Bit 3         | Bit 2       | Bit 1             | Bit 0   | Value on<br>Power-on<br>RESET | Details<br>on page |

|--------|-----------------------|-----------------------------------------------------|------------------------------------------------------------|------------|---------------|---------------|-------------|-------------------|---------|-------------------------------|--------------------|

| Bank 0 |                       |                                                     |                                                            |            |               |               |             |                   |         |                               |                    |

| 00h    | INDF                  | Uses cor                                            | ntents of FSI                                              | R to addre | ess Data Mem  | ory (not a p  | hysical re  | gister)           |         |                               | 11                 |

| 01h    | TMR0                  | 8-bit Rea                                           | I-Time Clocl                                               | k/Counter  |               |               |             |                   |         | xxxx xxxx                     | 20                 |

| 02h    | PCL                   | Low Orde                                            | er 8 bits of th                                            | ne Prograi | m Counter (Po | C)            |             |                   |         | 0000 0000                     | 11                 |

| 03h    | STATUS <sup>(2)</sup> | IRP                                                 | RP1                                                        | RP0        | TO            | PD            | Z           | DC                | С       | 0001 1xxx                     | 8                  |

| 04h    | FSR                   | Indirect [                                          | Data Memory                                                | / Address  | Pointer 0     |               |             |                   |         | xxxx xxxx                     | 11                 |

| 05h    | PORTA <sup>(4)</sup>  | —                                                   | _                                                          | —          | RA4/T0CKI     | RA3           | RA2         | RA1               | RA0     | x xxxx                        | 16                 |

| 06h    | PORTB <sup>(5)</sup>  | RB7                                                 | RB6                                                        | RB5        | RB4           | RB3           | RB2         | RB1               | RB0/INT | XXXX XXXX                     | 18                 |

| 07h    | —                     | Unimpler                                            | mented locat                                               | tion, read | as '0'        |               |             |                   |         | —                             | —                  |

| 08h    | EEDATA                | EEPRON                                              | /I Data Regis                                              | ster       |               |               |             |                   |         | xxxx xxxx                     | 13,14              |

| 09h    | EEADR                 | EEPRON                                              | EEPROM Address Register                                    |            |               |               |             |                   |         | XXXX XXXX                     | 13,14              |

| 0Ah    | PCLATH                | —                                                   |                                                            | —          | Write Buffer  | for upper 5   | bits of the | PC <sup>(1)</sup> |         | 0 0000                        | 11                 |

| 0Bh    | INTCON                | GIE                                                 | EEIE                                                       | T0IE       | INTE          | RBIE          | T0IF        | INTF              | RBIF    | 0000 000x                     | 10                 |

| Bank   | 1                     |                                                     |                                                            |            |               |               |             |                   |         |                               |                    |

| 80h    | INDF                  | Uses Co                                             | ntents of FS                                               | R to addre | ess Data Merr | nory (not a p | ohysical re | gister)           |         |                               | 11                 |

| 81h    | OPTION_REG            | RBPU                                                | INTEDG                                                     | T0CS       | TOSE          | PSA           | PS2         | PS1               | PS0     | 1111 1111                     | 9                  |

| 82h    | PCL                   | Low orde                                            | er 8 bits of P                                             | rogram Co  | ounter (PC)   | •             | •           |                   |         | 0000 0000                     | 11                 |

| 83h    | STATUS <sup>(2)</sup> | IRP                                                 | RP1                                                        | RP0        | TO            | PD            | Z           | DC                | С       | 0001 1xxx                     | 8                  |

| 84h    | FSR                   | Indirect of                                         | lata memory                                                | address    | pointer 0     |               |             |                   |         | xxxx xxxx                     | 11                 |

| 85h    | TRISA                 | —                                                   | —                                                          | —          | PORTA Data    | Direction F   | Register    |                   |         | 1 1111                        | 16                 |

| 86h    | TRISB                 | PORTB I                                             | Data Directio                                              | on Registe | er            |               |             |                   |         | 1111 1111                     | 18                 |

| 87h    | —                     | Unimpler                                            | Unimplemented location, read as '0'                        |            |               |               |             |                   |         | —                             | —                  |

| 88h    | EECON1                | —                                                   | — — — EEIF WRERR WREN WR RD                                |            |               |               |             |                   |         | 0 x000                        | 13                 |

| 89h    | EECON2                | EEPROM Control Register 2 (not a physical register) |                                                            |            |               |               |             |                   |         |                               | 14                 |

| 0Ah    | PCLATH                | —                                                   | — — Write buffer for upper 5 bits of the PC <sup>(1)</sup> |            |               |               |             |                   |         | 0 0000                        | 11                 |

| 0Bh    | INTCON                | GIE                                                 | EEIE                                                       | T0IE       | INTE          | RBIE          | T0IF        | INTF              | RBIF    | 0000 000x                     | 10                 |

Legend: x = unknown, u = unchanged. - = unimplemented, read as '0', q = value depends on condition

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a slave register for PC<12:8>. The contents of PCLATH can be transferred to the upper byte of the program counter, but the contents of PC<12:8> are never transferred to PCLATH.

2: The TO and PD status bits in the STATUS register are not affected by a MCLR Reset.

3: Other (non power-up) RESETS include: external RESET through MCLR and the Watchdog Timer Reset.

4: On any device RESET, these pins are configured as inputs.

5: This is the value that will be in the port output latch.

#### 3.1 Reading the EEPROM Data Memory

To read a data memory location, the user must write the address to the EEADR register and then set control bit RD (EECON1<0>). The data is available, in the very next cycle, in the EEDATA register; therefore, it can be read in the next instruction. EEDATA will hold this value until another read or until it is written to by the user (during a write operation).

EXAMPLE 3-1: DATA EEPROM READ

| BCF   | STATUS, RPO | ; | Bank 0          |

|-------|-------------|---|-----------------|

| MOVLW | CONFIG_ADDR | ; |                 |

| MOVWF | EEADR       | ; | Address to read |

| BSF   | STATUS, RPO | ; | Bank 1          |

| BSF   | EECON1, RD  | ; | EE Read         |

| BCF   | STATUS, RPO | ; | Bank 0          |

| MOVF  | EEDATA, W   | ; | W = EEDATA      |

|       |             |   |                 |

## 3.2 Writing to the EEPROM Data Memory

To write an EEPROM data location, the user must first write the address to the EEADR register and the data to the EEDATA register. Then the user must follow a specific sequence to initiate the write for each byte.

EXAMPLE 3-2: DATA EEPROM WRITE

|          | BSF   | STATUS, RPO  | ; | Bank 1        |

|----------|-------|--------------|---|---------------|

|          | BCF   | INTCON, GIE  | ; | Disable INTs. |

|          | BSF   | EECON1, WREN | ; | Enable Write  |

|          | MOVLW | 55h          | ; |               |

|          | MOVWF | EECON2       | ; | Write 55h     |

| _ 0      | MOVLW | AAh          | ; |               |

| uired    | MOVWF | EECON2       | ; | Write AAh     |

| equi     | BSF   | EECON1,WR    | ; | Set WR bit    |

| ec<br>ec |       |              | ; | begin write   |

| ar of    | BSF   | INTCON, GIE  | ; | Enable INTs.  |

|          |       |              | _ |               |

The write will not initiate if the above sequence is not exactly followed (write 55h to EECON2, write AAh to EECON2, then set WR bit) for each byte. We strongly recommend that interrupts be disabled during this code segment. Additionally, the WREN bit in EECON1 must be set to enable write. This mechanism prevents accidental writes to data EEPROM due to errant (unexpected) code execution (i.e., lost programs). The user should keep the WREN bit clear at all times, except when updating EEPROM. The WREN bit is not cleared by hardware.

After a write sequence has been initiated, clearing the WREN bit will not affect this write cycle. The WR bit will be inhibited from being set unless the WREN bit is set.

At the completion of the write cycle, the WR bit is cleared in hardware and the EE Write Complete Interrupt Flag bit (EEIF) is set. The user can either enable this interrupt or poll this bit. EEIF must be cleared by software.

## 3.3 Write Verify

Depending on the application, good programming practice may dictate that the value written to the Data EEPROM should be verified (Example 3-3) to the desired value to be written. This should be used in applications where an EEPROM bit will be stressed near the specification limit.

Generally, the EEPROM write failure will be a bit which was written as a '0', but reads back as a '1' (due to leakage off the bit).

EXAMPLE 3-3: WRITE VERIFY

|      |       | <b>.</b>    |   |                      |

|------|-------|-------------|---|----------------------|

|      | BCF   | STATUS, RPO | ; | Bank 0               |

|      | :     |             | ; | Any code             |

|      | :     |             | ; | can go here          |

|      | MOVF  | EEDATA,W    | ; | Must be in Bank 0    |

|      | BSF   | STATUS, RPO | ; | Bank 1               |

| READ |       |             |   |                      |

|      | BSF   | EECON1, RD  | ; | YES, Read the        |

|      |       |             | ; | value written        |

|      | BCF   | STATUS, RPO | ; | Bank 0               |

|      |       |             | ; |                      |

|      |       |             | ; | Is the value written |

|      |       |             | ; | (in W reg) and       |

|      |       |             | ; | read (in EEDATA)     |

|      |       |             | ; | the same?            |

|      |       |             | ; |                      |

|      | SUBWF | EEDATA, W   | ; |                      |

|      | BTFSS | STATUS, Z   | ; | Is difference 0?     |

|      | GOTO  | WRITE_ERR   | ; | NO, Write error      |

#### TABLE 3-1: REGISTERS/BITS ASSOCIATED WITH DATA EEPROM

| Address | Name   | Bit 7                        | Bit 6                       | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Value on<br>Power-on<br>Reset | Value on<br>all other<br>RESETS |

|---------|--------|------------------------------|-----------------------------|-------|-------|-------|-------|-------|--------|-------------------------------|---------------------------------|

| 08h     | EEDATA | EEPRO                        | EEPROM Data Register        |       |       |       |       |       |        |                               | uuuu uuuu                       |

| 09h     | EEADR  | EEPRO                        | EPROM Address Register      |       |       |       |       |       |        |                               | uuuu uuuu                       |

| 88h     | EECON1 |                              | — — — EEIF WRERR WREN WR RD |       |       |       |       |       | 0 x000 | 0 q000                        |                                 |

| 89h     | EECON2 | V2 EEPROM Control Register 2 |                             |       |       |       |       |       |        |                               |                                 |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0', q = value depends upon condition. Shaded cells are not used by data EEPROM.

| Name    | Bit  | Buffer Type           | I/O Consistency Function                                                                                               |

|---------|------|-----------------------|------------------------------------------------------------------------------------------------------------------------|

| RB0/INT | bit0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input.<br>Internal software programmable weak pull-up.                          |

| RB1     | bit1 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                         |

| RB2     | bit2 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                         |

| RB3     | bit3 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                         |

| RB4     | bit4 | TTL                   | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up.                           |

| RB5     | bit5 | TTL                   | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up.                           |

| RB6     | bit6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up. Serial programming clock. |

| RB7     | bit7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up. Serial programming data.  |

## TABLE 4-3:PORTB FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger.

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

#### TABLE 4-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address | Name       | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0   | Value on<br>Power-on<br>Reset | Value on<br>all other<br>RESETS |

|---------|------------|--------|--------|--------|--------|--------|--------|--------|---------|-------------------------------|---------------------------------|

| 06h     | PORTB      | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0/INT | xxxx xxxx                     | uuuu uuuu                       |

| 86h     | TRISB      | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0  | 1111 1111                     | 1111 1111                       |

| 81h     | OPTION_REG | RBPU   | INTEDG | TOCS   | T0SE   | PSA    | PS2    | PS1    | PS0     | 1111 1111                     | 1111 1111                       |

| 0Bh,8Bh | INTCON     | GIE    | EEIE   | TOIE   | INTE   | RBIE   | T0IF   | INTF   | RBIF    | 0000 000x                     | 0000 000u                       |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTB.

| Register             | Address | Power-on Reset | MCLR during:<br>– normal operation<br>– SLEEP<br>WDT Reset during<br>normal operation | Wake-up from SLEEP:<br>– through interrupt<br>– through WDT Time-out |

|----------------------|---------|----------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| W                    | —       | xxxx xxxx      | uuuu uuuu                                                                             | uuuu uuuu                                                            |

| INDF                 | 00h     |                |                                                                                       |                                                                      |

| TMR0                 | 01h     | xxxx xxxx      | uuuu uuuu                                                                             | uuuu uuuu                                                            |

| PCL                  | 02h     | 0000 0000      | 0000 0000                                                                             | PC + 1 <sup>(2)</sup>                                                |

| STATUS               | 03h     | 0001 1xxx      | 000q quuu <sup>(3)</sup>                                                              | uuuq quuu <sup>(3)</sup>                                             |

| FSR                  | 04h     | xxxx xxxx      | uuuu uuuu                                                                             | uuuu uuuu                                                            |

| PORTA <sup>(4)</sup> | 05h     | x xxxx         | u uuuu                                                                                | u uuuu                                                               |

| PORTB <sup>(5)</sup> | 06h     | xxxx xxxx      | uuuu uuuu                                                                             | uuuu uuuu                                                            |

| EEDATA               | 08h     | xxxx xxxx      | uuuu uuuu                                                                             | uuuu uuuu                                                            |

| EEADR                | 09h     | xxxx xxxx      | uuuu uuuu                                                                             | uuuu uuuu                                                            |

| PCLATH               | 0Ah     | 0 0000         | 0 0000                                                                                | u uuuu                                                               |

| INTCON               | 0Bh     | 0000 000x      | 0000 000u                                                                             | uuuu uuuu <sup>(1)</sup>                                             |

| INDF                 | 80h     |                |                                                                                       |                                                                      |

| OPTION_REG           | 81h     | 1111 1111      | 1111 1111                                                                             | uuuu uuuu                                                            |

| PCL                  | 82h     | 0000 0000      | 0000 0000                                                                             | PC + 1 <sup>(2)</sup>                                                |

| STATUS               | 83h     | 0001 1xxx      | 000q quuu <sup>(3)</sup>                                                              | uuuq quuu <sup>(3)</sup>                                             |

| FSR                  | 84h     | xxxx xxxx      | uuuu uuuu                                                                             | uuuu uuuu                                                            |

| TRISA                | 85h     | 1 1111         | 1 1111                                                                                | u uuuu                                                               |

| TRISB                | 86h     | 1111 1111      | 1111 1111                                                                             | uuuu uuuu                                                            |

| EECON1               | 88h     | 0 x000         | 0 q000                                                                                | 0 uuuu                                                               |

| EECON2               | 89h     |                |                                                                                       |                                                                      |

| PCLATH               | 8Ah     | 0 0000         | 0 0000                                                                                | u uuuu                                                               |

| INTCON               | 8Bh     | 0000 000x      | 0000 000u                                                                             | uuuu uuuu <b>(1)</b>                                                 |

| TABLE 6-4:    | <b>RESET CONDITIONS FOR ALL REGISTERS</b> |

|---------------|-------------------------------------------|

| $IADLL V^{-}$ |                                           |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition

Note 1: One or more bits in INTCON will be affected (to cause wake-up).

**2:** When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: Table 6-3 lists the RESET value for each specific condition.

4: On any device RESET, these pins are configured as inputs.

5: This is the value that will be in the port output latch.

## 6.4 Power-on Reset (POR)

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.2V - 1.7V). To take advantage of the POR, just tie the MCLR pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A minimum rise time for VDD must be met for this to operate properly. See Electrical Specifications for details.

When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met.

For additional information, refer to Application Note AN607, "*Power-up Trouble Shooting*."

The POR circuit does not produce an internal RESET when VDD declines.

## 6.5 **Power-up Timer (PWRT)**

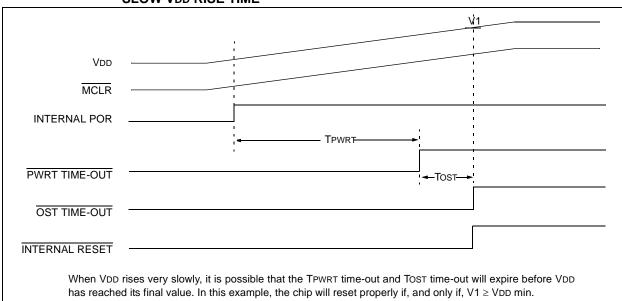

The Power-up Timer (PWRT) provides a fixed 72 ms nominal time-out (TPWRT) from POR (Figures 6-6 through 6-9). The Power-up Timer operates on an internal RC oscillator. The chip is kept in RESET as long as the PWRT is active. The PWRT delay allows the VDD to rise to an acceptable level (possible exception shown in Figure 6-9).

A configuration bit, PWRTE, can enable/disable the PWRT. See Register 6-1 for the operation of the PWRTE bit for a particular device.

The power-up time delay TPWRT will vary from chip to chip due to VDD, temperature, and process variation. See DC parameters for details.

## 6.6 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle delay (from OSC1 input) after the PWRT delay ends (Figure 6-6, Figure 6-7, Figure 6-8 and Figure 6-9). This ensures the crystal oscillator or resonator has started and stabilized.

The OST time-out (TOST) is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

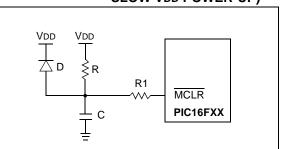

When VDD rises very slowly, it is possible that the TPWRT time-out and TOST time-out will expire before VDD has reached its final value. In this case (Figure 6-9), an external Power-on Reset circuit may be necessary (Figure 6-5).

## FIGURE 6-5: EXTI RES

#### EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Note 1: External Power-on Reset circuit is required only if VDD power-up rate is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- 2: R < 40 k $\Omega$  is recommended to make sure that voltage drop across R does not exceed 0.2V (max leakage current spec on MCLR pin is 5  $\mu$ A). A larger voltage drop will degrade VIH level on the MCLR pin.

- **3:**  $R1 = 100\Omega$  to 1 k $\Omega$  will limit any current flowing into MCLR from external capacitor C, in the event of a MCLR pin breakdown due to ESD or EOS.

## FIGURE 6-9: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD): SLOW VDD RISE TIME

## 6.7 Time-out Sequence and \_\_\_\_\_ Power-down Status Bits (TO/PD)

On power-up (Figures 6-6 through 6-9), the time-out sequence is as follows:

- 1. PWRT time-out is invoked after a POR has expired.

- 2. Then, the OST is activated.

The total time-out will vary based on oscillator configuration and PWRTE configuration bit status. For example, in RC mode with the PWRT disabled, there will be no time-out at all.

# TABLE 6-5:TIME-OUT IN VARIOUSSITUATIONS

| Oscillator    | Powe                | Wake-up          |               |  |

|---------------|---------------------|------------------|---------------|--|

| Configuration | PWRT<br>Enabled     | PWRT<br>Disabled | from<br>SLEEP |  |

| XT, HS, LP    | 72 ms +<br>1024Tosc | 1024Tosc         | 1024Tosc      |  |

| RC            | 72 ms               | _                | _             |  |

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then bringing  $\overline{\text{MCLR}}$  high, execution will begin immediately (Figure 6-6). This is useful for testing purposes or to synchronize more than one PIC16F84A device when operating in parallel.

Table 6-6 shows the significance of the  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits. Table 6-3 lists the RESET conditions for some special registers, while Table 6-4 lists the RESET conditions for all the registers.

TABLE 6-6: STATUS BITS AND THEIR SIGNIFICANCE

| то | PD | Condition                           |  |  |  |

|----|----|-------------------------------------|--|--|--|

| 1  | 1  | Power-on Reset                      |  |  |  |

| 0  | x  | Illegal, TO is set on POR           |  |  |  |

| х  | 0  | Illegal, PD is set on POR           |  |  |  |

| 0  | 1  | WDT Reset (during normal operation) |  |  |  |

| 0  | 0  | WDT Wake-up                         |  |  |  |

| 1  | 1  | MCLR during normal operation        |  |  |  |

| 1  | 0  | MCLR during SLEEP or interrupt      |  |  |  |

|    |    | wake-up from SLEEP                  |  |  |  |

#### 6.11 Power-down Mode (SLEEP)

A device may be powered down (SLEEP) and later powered up (wake-up from SLEEP).

#### 6.11.1 SLEEP

The Power-down mode is entered by executing the SLEEP instruction.

If enabled, the Watchdog Timer is cleared (but keeps running), the PD bit (STATUS<3>) is cleared, the TO bit (STATUS<4>) is set, and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, low, or hi-impedance).

For the lowest current consumption in SLEEP mode, place all I/O pins at either VDD or VSS, with no external circuitry drawing current from the I/O pins, and disable external clocks. I/O pins that are hi-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS. The contribution from on-chip pull-ups on PORTB should be considered.

The MCLR pin must be at a logic high level (VIHMC).

It should be noted that a RESET generated by a WDT time-out does not drive the MCLR pin low.

#### 6.11.2 WAKE-UP FROM SLEEP

The device can wake-up from SLEEP through one of the following events:

- 1. External RESET input on MCLR pin.

- 2. WDT wake-up (if WDT was enabled).

- 3. Interrupt from RB0/INT pin, RB port change, or data EEPROM write complete.

Peripherals cannot generate interrupts during SLEEP, since no on-chip Q clocks are present.

The first event ( $\overline{\text{MCLR}}$  Reset) will cause a device RESET. The two latter events are considered a continuation of program execution. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits can be used to determine the cause of a device RESET. The  $\overline{\text{PD}}$  bit, which is set on power-up, is cleared when SLEEP is invoked. The  $\overline{\text{TO}}$  bit is cleared if a WDT time-out occurred (and caused wake-up).

While the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up occurs regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

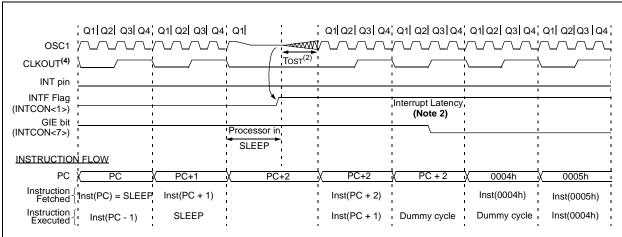

#### FIGURE 6-12: WAKE-UP FROM SLEEP THROUGH INTERRUPT

**Note** 1: XT, HS, or LP oscillator mode assumed.

- 2: TOST = 1024TOSC (drawing not to scale). This delay will not be there for RC osc mode.

- 3: GIE = '1' assumed. In this case after wake-up, the processor jumps to the interrupt routine. If GIE = '0', execution will continue in-line.

4: CLKOUT is not available in these osc modes, but shown here for timing reference.

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                       |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                            |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                   |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                         |

| Description:     | The contents of register 'f' are<br>decremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'.<br>If the result is 1, the next instruc-<br>tion is executed. If the result is 0,<br>then a NOP is executed instead,<br>making it a 2TCY instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                      |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                                                             |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                              |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                    |  |  |  |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result is<br>placed in the W register. If 'd' is 1,<br>the result is placed back in<br>register 'f'.<br>If the result is 1, the next instruc-<br>tion is executed. If the result is 0,<br>a NOP is executed instead, making<br>it a 2TCY instruction. |  |  |  |

| GOTO             | Unconditional Branch                                                                                                                                                                              |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                           |  |  |  |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                                |  |  |  |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                                   |  |  |  |

| Status Affected: | None                                                                                                                                                                                              |  |  |  |

| Description:     | GOTO is an unconditional branch.<br>The eleven-bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a two-<br>cycle instruction. |  |  |  |

| IORLW            | Inclusive OR Literal with W                                                                                               |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                                  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                         |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                              |  |  |  |

| Status Affected: | Z                                                                                                                         |  |  |  |

| Description:     | The contents of the W register are<br>OR'ed with the eight-bit literal 'k'.<br>The result is placed in the W<br>register. |  |  |  |

| IORWF            | Inclusive OR W with f                                                                                                                                                   |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] IORWF f,d                                                                                                                                                       |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                         |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                                |

| Status Affected: | Z                                                                                                                                                                       |

| Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is 0, the result is<br>placed in the W register. If 'd' is 1,<br>the result is placed back in<br>register 'f'. |

| INCF             | Increment f                                                                                                                                                            |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] INCF f,d                                                                                                                                                       |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                     |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                    |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                      |  |  |  |  |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'. |  |  |  |  |

| XORLW                   | Exclusive OR Literal with W                                                                | XORWF            | Exclusive OR W with f                                                                                                                                                       |  |  |

|-------------------------|--------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:                 | [ <i>label</i> ] XORLW k                                                                   | Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                  |  |  |

| Operands:<br>Operation: | $0 \le k \le 255$<br>(W) .XOR. $k \rightarrow$ (W)                                         | Operands:        | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                          |  |  |

| Status Affected:        | Z                                                                                          | Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                   |  |  |

| Description:            | The contents of the W register                                                             | Status Affected: | Z                                                                                                                                                                           |  |  |

|                         | are XOR'ed with the eight-bit lit-<br>eral 'k'. The result is placed in<br>the W register. | Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |  |  |

# 8.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers and dsPIC<sup>®</sup> digital signal controllers are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Compilers/Assemblers/Linkers

- MPLAB C Compiler for Various Device Families

- HI-TECH C<sup>®</sup> for Various Device Families

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers

- MPLAB ICD 3

- PICkit<sup>™</sup> 3 Debug Express

- Device Programmers

- PICkit<sup>™</sup> 2 Programmer

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits, and Starter Kits

## 8.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16/32-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- In-Circuit Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- High-level source code debugging

- Mouse over variable inspection

- Drag and drop variables from source to watch windows

- Extensive on-line help

- Integration of select third party tools, such as IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either C or assembly)

- One-touch compile or assemble, and download to emulator and simulator tools (automatically updates all project information)

- Debug using:

- Source files (C or assembly)

- Mixed C and assembly

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

## 8.2 MPLAB C Compilers for Various Device Families

The MPLAB C Compiler code development systems are complete ANSI C compilers for Microchip's PIC18, PIC24 and PIC32 families of microcontrollers and the dsPIC30 and dsPIC33 families of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

## 8.3 HI-TECH C for Various Device Families

The HI-TECH C Compiler code development systems are complete ANSI C compilers for Microchip's PIC family of microcontrollers and the dsPIC family of digital signal controllers. These compilers provide powerful integration capabilities, omniscient code generation and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

The compilers include a macro assembler, linker, preprocessor, and one-step driver, and can run on multiple platforms.

## 8.4 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

## 8.5 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 8.6 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC devices. MPLAB C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- · Rich directive set

- Flexible macro language

- MPLAB IDE compatibility

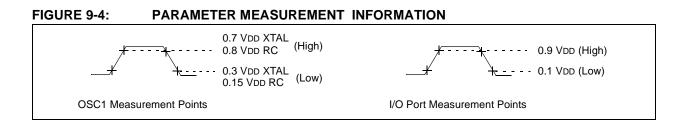

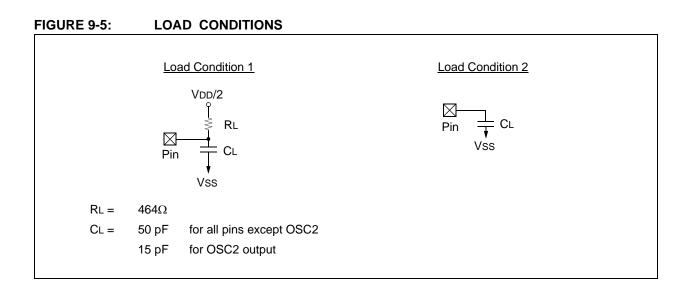

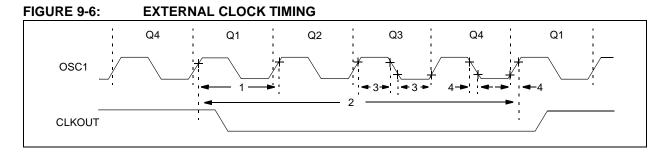

#### 9.3.2 TIMING CONDITIONS

The temperature and voltages specified in Table 9-1 apply to all timing specifications unless otherwise noted. All timings are measured between high and low measurement points as indicated in Figure 9-4. Figure 9-5 specifies the load conditions for the timing specifications.

## TABLE 9-1: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions (unless otherwise stated)                     |  |  |  |

|--------------------|-----------------------------------------------------------------------------|--|--|--|

| AC CHARACTERISTICS | Operating temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial   |  |  |  |

| AC CHARACTERIOTICO | -40°C $\leq$ TA $\leq$ +85°C for industrial                                 |  |  |  |

|                    | Operating voltage VDD range as described in DC specifications (Section 9.1) |  |  |  |

## 9.3.3 TIMING DIAGRAMS AND SPECIFICATIONS

### TABLE 9-2: EXTERNAL CLOCK TIMING REQUIREMENTS

| Param No. | Sym   | Characteristic                          | Min  | Тур†   | Max    | Units | Cond       | litions   |

|-----------|-------|-----------------------------------------|------|--------|--------|-------|------------|-----------|

|           | Fosc  | External CLKIN Frequency <sup>(1)</sup> | DC   |        | 2      | MHz   | XT, RC osc | (-04, LF) |

|           |       |                                         | DC   | —      | 4      | MHz   | XT, RC osc | (-04)     |

|           |       |                                         | DC   | —      | 20     | MHz   | HS osc     | (-20)     |

|           |       |                                         | DC   | —      | 200    | kHz   | LP osc     | (-04, LF) |

|           |       | Oscillator Frequency <sup>(1)</sup>     | DC   | _      | 2      | MHz   | RC osc     | (-04, LF) |

|           |       |                                         | DC   | —      | 4      | MHz   | RC osc     | (-04)     |

|           |       |                                         | 0.1  | —      | 2      | MHz   | XT osc     | (-04, LF) |

|           |       |                                         | 0.1  | —      | 4      | MHz   | XT osc     | (-04)     |

|           |       |                                         | 1.0  | —      | 20     | MHz   | HS osc     | (-20)     |

|           |       |                                         | DC   | —      | 200    | kHz   | LP osc     | (-04, LF) |

| 1         | Tosc  | External CLKIN Period <sup>(1)</sup>    | 500  |        | _      | ns    | XT, RC osc | (-04, LF) |

|           |       |                                         | 250  | —      | —      | ns    | XT, RC osc | (-04)     |

|           |       |                                         | 50   | —      | —      | ns    | HS osc     | (-20)     |

|           |       |                                         | 5.0  | —      | —      | μs    | LP osc     | (-04, LF) |

|           |       | Oscillator Period <sup>(1)</sup>        | 500  | _      | _      | ns    | RC osc     | (-04, LF) |

|           |       |                                         | 250  | —      | —      | ns    | RC osc     | (-04)     |

|           |       |                                         | 500  | —      | 10,000 | ns    | XT osc     | (-04, LF) |

|           |       |                                         | 250  | —      | 10,000 | ns    | XT osc     | (-04)     |

|           |       |                                         | 50   | —      | 1,000  | ns    | HS osc     | (-20)     |

|           |       |                                         | 5.0  | _      | _      | μs    | LP osc     | (-04, LF) |

| 2         | Тсү   | Instruction Cycle Time <sup>(1)</sup>   | 0.2  | 4/Fosc | DC     | μS    |            |           |

| 3         | TosL, | Clock in (OSC1) High or Low             | 60   | _      | _      | ns    | XT osc     | (-04, LF) |

|           | TosH  | Time                                    | 50   | —      | —      | ns    | XT osc     | (-04)     |

|           |       |                                         | 2.0  | —      | —      | μS    | LP osc     | (-04, LF) |

|           |       |                                         | 17.5 | —      | —      | ns    | HS osc     | (-20)     |

| 4         | TosR, | Clock in (OSC1) Rise or Fall            | 25   | —      | _      | ns    | XT osc     | (-04)     |

|           | TosF  | Time                                    | 50   | —      | —      | ns    | LP osc     | (-04, LF) |

|           |       |                                         | 7.5  | —      | —      | ns    | HS osc     | (-20)     |

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Instruction cycle period (Tcr) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "Min." values with an external clock applied to the OSC1 pin.

When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

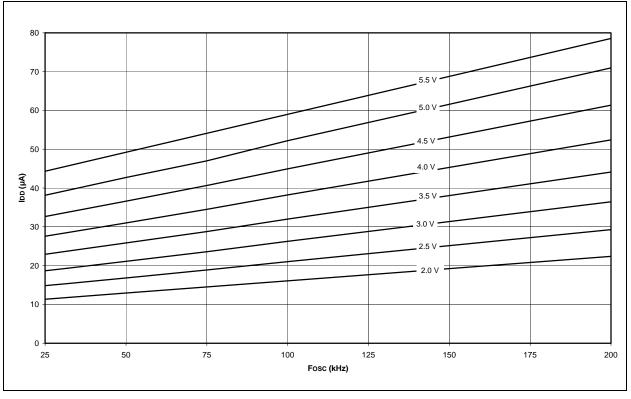

FIGURE 10-5: TYPICAL IDD vs. Fosc OVER VDD (LP MODE, 25°C)

D

☐ 0.20 C A-B

2X

NOTE 5 D A Ν пппп Π ПППП E/2 E1 Е 0.10 C D || || || 1 2 3 Ш 0.33 C 2X 2X N/2 TIPS NOTE 1 NX b ⊕0.25@CA-BD NOTE 5 в е TOP VIEW 0.10 C 1 0.10 C NX А SEATING PLANE A2 Ċ A1 SIDE VIEW

VIEW A-A

Microchip Technology Drawing C04-051C Sheet 1 of 2

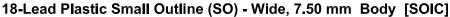

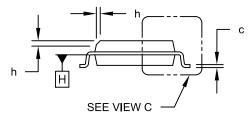

18-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                       | Units  |          |      | S    |

|-----------------------|--------|----------|------|------|

| Dimension             | Limits | MIN      | NOM  | MAX  |

| Contact Pitch         | E      | 1.27 BSC |      |      |

| Contact Pad Spacing   | С      |          | 9.40 |      |

| Contact Pad Width     | Х      |          |      | 0.60 |

| Contact Pad Length    | Y      |          |      | 2.00 |

| Distance Between Pads | Gx     | 0.67     |      |      |

| Distance Between Pads | G      | 7.40     |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2051A

# PIC16F84A

NOTES:

# APPENDIX B: CONVERSION CONSIDERATIONS

Considerations for converting from one PIC16X8X device to another are listed in Table 1.

| PIC1                                                                                                                                    | 6F84A                                                                                                                                                                |                                                                                                                                                                                                                         |                                                                                                                                                                                                     |                                                                                                                                                                                                                            |  |

|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Difference                                                                                                                              | PIC16C84                                                                                                                                                             | PIC16F83/F84                                                                                                                                                                                                            | PIC16CR83/<br>CR84                                                                                                                                                                                  | PIC16F84A                                                                                                                                                                                                                  |  |

| Program Memory Size                                                                                                                     | 1K x 14                                                                                                                                                              | 512 x 14 / 1K x 14                                                                                                                                                                                                      | 512 x 14 / 1K x 14                                                                                                                                                                                  | 1K x 14                                                                                                                                                                                                                    |  |

| Data Memory Size                                                                                                                        | 36 x 8                                                                                                                                                               | 36 x 8 / 68 x 8                                                                                                                                                                                                         | 36 x 8 / 68 x 8                                                                                                                                                                                     | 68 x 8                                                                                                                                                                                                                     |  |

| Voltage Range                                                                                                                           | 2.0V - 6.0V<br>(-40°C to +85°C)                                                                                                                                      | 2.0V - 6.0V<br>(-40°C to +85°C)                                                                                                                                                                                         | 2.0V - 6.0V<br>(-40°C to +85°C)                                                                                                                                                                     | 2.0V - 5.5V<br>(-40°C to +125°C)                                                                                                                                                                                           |  |

| Maximum Operating Fre-<br>quency                                                                                                        | 10 MHz                                                                                                                                                               | 10 MHz                                                                                                                                                                                                                  | 10 MHz                                                                                                                                                                                              | 20 MHz                                                                                                                                                                                                                     |  |

| Supply Current (IDD).<br>See parameter # D014 in<br>the electrical specs for<br>more detail.                                            | IDD (typ) = $60 \mu A$<br>IDD (max) = $400 \mu A$<br>(LP osc, Fosc = $32 \text{ kHz}$ ,<br>VDD = $2.0V$ ,<br>WDT disabled)                                           | $\begin{array}{l} \text{IDD} \mbox{(typ)} = 15 \ \mu\text{A} \\ \text{IDD} \mbox{(max)} = 45 \ \mu\text{A} \\ \mbox{(LP osc, FOSC} = 32 \ \text{kHz}, \\ \text{VDD} = 2.0 \mbox{V}, \\ \text{WDT disabled} \end{array}$ | $\begin{array}{l} \text{IDD} \mbox{ (typ) = 15 } \mu A \\ \text{IDD} \mbox{ (max) = 45 } \mu A \\ \text{(LP osc, Fosc = 32 } \text{kHz}, \\ \text{VDD = 2.0V,} \\ \text{WDT disabled)} \end{array}$ | $\begin{array}{l} \text{IDD} (\text{typ}) = 15 \ \mu\text{A} \\ \text{IDD} (\text{max}) = 45 \ \mu\text{A} \\ (\text{LP osc, Fosc} = 32 \ \text{kHz}, \\ \text{VDD} = 2.0 \ \text{V}, \\ \text{WDT disabled}) \end{array}$ |  |

| Power-down Current<br>(IPD). See parameters #<br>D020, D021, and D021A<br>in the electrical specs for<br>more detail.                   | IPD (typ) = 26 μA<br>IPD (max) = 100 μA<br>(VDD = 2.0V,<br>WDT disabled, industrial)                                                                                 | $\begin{array}{l} \mbox{IPD} (typ) = 0.4 \ \mu A \\ \mbox{IPD} (max) = 9 \ \mu A \\ \mbox{(VDD} = 2.0V, \\ \mbox{WDT} \ \mbox{disabled, industrial)} \end{array}$                                                       | $\begin{array}{l} \mbox{IPD} \mbox{(typ)} = 0.4 \ \mu \mbox{A} \\ \mbox{IPD} \mbox{(max)} = 6 \ \mu \mbox{A} \\ \mbox{(VDD} = 2.0 \mbox{V}, \\ \mbox{WDT} \mbox{ disabled, industrial} \end{array}$ | $\label{eq:PD} \begin{array}{l} \text{IPD} (typ) = 0.4 \ \mu\text{A} \\ \text{IPD} (max) = 1 \ \mu\text{A} \\ (\text{VDD} = 2.0\text{V}, \\ \text{WDT} \text{ disabled, industrial}) \end{array}$                          |  |

| Input Low Voltage (VIL).<br>See parameters # D032<br>and D034 in the electrical<br>specs for more detail.                               | VIL (max) = 0.2VDD<br>(OSC1, RC mode)                                                                                                                                | VIL (max) = 0.1VDD<br>(OSC1, RC mode)                                                                                                                                                                                   | VIL (max) = 0.1VDD<br>(OSC1, RC mode)                                                                                                                                                               | VIL (max) = 0.1VDD<br>(OSC1, RC mode)                                                                                                                                                                                      |  |

| Input High Voltage (VIH).<br>See parameter # D040 in<br>the electrical specs for<br>more detail.                                        | VIH (min) = $0.36$ VDD<br>(I/O Ports with TTL,<br>$4.5$ V $\leq$ VDD $\leq$ $5.5$ V)                                                                                 | VIH (min) = $2.4V$<br>(I/O Ports with TTL,<br>$4.5V \le VDD \le 5.5V$ )                                                                                                                                                 | VIH (min) = $2.4V$<br>(I/O Ports with TTL,<br>$4.5V \le VDD \le 5.5V$ )                                                                                                                             | VIH (min) = $2.4V$<br>(I/O Ports with TTL,<br>$4.5V \le VDD \le 5.5V$ )                                                                                                                                                    |  |

| Data EEPROM Memory<br>Erase/Write cycle time<br>(TDEW). See parameter #<br>D122 in the electrical<br>specs for more detail.             | TDEW (typ) = 10 ms<br>TDEW (max) = 20 ms                                                                                                                             | TDEW (typ) = 10 ms<br>TDEW (max) = 20 ms                                                                                                                                                                                | TDEW (typ) = 10 ms<br>TDEW (max) = 20 ms                                                                                                                                                            | TDEW (typ) = 4 ms<br>TDEW (max) = 8 ms                                                                                                                                                                                     |  |

| Port Output Rise/Fall<br>time (TioR, TioF). See<br>parameters #20, 20A,<br>21, and 21A in the elec-<br>trical specs for more<br>detail. | TioR, TioF (max) = 25 ns<br>(C84)<br>TioR, TioF (max) = 60 ns<br>(LC84)                                                                                              | TioR, TioF (max) = 35 ns<br>(C84)<br>TioR, TioF (max) = 70 ns<br>(LC84)                                                                                                                                                 | TioR, TioF (max) = 35 ns<br>(C84)<br>TioR, TioF (max) = 70 ns<br>(LC84)                                                                                                                             | TioR, TioF (max) = 35 ns<br>(C84)<br>TioR, TioF (max) = 70 ns<br>(LC84)                                                                                                                                                    |  |

| MCLR on-chip filter. See<br>parameter #30 in the<br>electrical specs for more<br>detail.                                                | No                                                                                                                                                                   | Yes                                                                                                                                                                                                                     | Yes                                                                                                                                                                                                 | Yes                                                                                                                                                                                                                        |  |

| PORTA and crystal oscil-<br>lator values less than<br>500 kHz                                                                           | For crystal oscillator con-<br>figurations operating<br>below 500 kHz, the device<br>may generate a spurious<br>internal Q-clock when<br>PORTA<0> switches<br>state. | N/A                                                                                                                                                                                                                     | N/A                                                                                                                                                                                                 | N/A                                                                                                                                                                                                                        |  |

| RB0/INT pin                                                                                                                             | TTL                                                                                                                                                                  | TTL/ST*<br>(*Schmitt Trigger)                                                                                                                                                                                           | TTL/ST*<br>(*Schmitt Trigger)                                                                                                                                                                       | TTL/ST*<br>(*Schmitt Trigger)                                                                                                                                                                                              |  |

# TABLE 1:CONVERSION CONSIDERATIONS - PIC16C84, PIC16F83/F84, PIC16CR83/CR84,<br/>PIC16F84A

# INDEX

## Α

| Absolute Maximum Ratings    | 47 |

|-----------------------------|----|

| AC (Timing) Characteristics | 53 |

| Architecture, Block Diagram | 3  |

| Assembler                   |    |

| MPASM Assembler             | 44 |

## В

| Banking, Data Memory<br>Block Diagrams | 6    |

|----------------------------------------|------|

| Crystal/Ceramic Resonator Operation    | . 22 |

| External Clock Input Operation         | . 22 |

| External Power-on Reset Circuit        | . 26 |