Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                         |

|----------------------------|-----------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                  |

| Core Processor             | ARM® Cortex®-M0                                                                         |

| Core Size                  | 32-Bit Single-Core                                                                      |

| Speed                      | 72MHz                                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART                      |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LVD, POR, PS2, PWM, WDT                  |

| Number of I/O              | 49                                                                                      |

| Program Memory Size        | 32KB (32K x 8)                                                                          |

| Program Memory Type        | FLASH                                                                                   |

| EEPROM Size                | 4K x 8                                                                                  |

| RAM Size                   | 8K x 8                                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                             |

| Data Converters            | A/D 7x12b                                                                               |

| Oscillator Type            | Internal                                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                      |

| Mounting Type              | Surface Mount                                                                           |

| Package / Case             | 64-LQFP                                                                                 |

| Supplier Device Package    | 64-LQFP (7x7)                                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/nuc230sc2ae |

|                            |                                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# nuvoton

| 6.15PS/2 Device Controller (PS2D)74                                   |

|-----------------------------------------------------------------------|

| 6.15.1 Overview                                                       |

| 6.15.2 Features                                                       |

| 6.16I <sup>2</sup> C Serial Interface Controller (I <sup>2</sup> C)75 |

| 6.16.1 Overview                                                       |

| 6.16.2 Features                                                       |

| 6.17Serial Peripheral Interface (SPI)75                               |

| 6.17.1 Overview                                                       |

| 6.17.2 Features                                                       |

| 6.18I <sup>2</sup> S Controller (I <sup>2</sup> S)76                  |

| 6.18.1 Overview                                                       |

| 6.18.2 Features                                                       |

| 6.19USB Device Controller (USBD)77                                    |

| 6.19.1 Overview                                                       |

| 6.19.2 Features                                                       |

| 6.20Controller Area Network (CAN)78                                   |

| 6.20.1 Overview                                                       |

| 6.20.2 Features                                                       |

| 6.21 Analog-to-Digital Converter (ADC)78                              |

| 6.21.1 Overview                                                       |

| 6.21.2 Features                                                       |

| 6.22Analog Comparator (ACMP)79                                        |

| 6.22.1 Overview                                                       |

| 6.22.2 Features                                                       |

| 7 APPLICATION CIRCUIT                                                 |

| 8 ELECTRICAL CHARACTERISTICS                                          |

| 8.1 Absolute Maximum Ratings81                                        |

| 8.2 DC Electrical Characteristics                                     |

| 8.3 AC Electrical Characteristics                                     |

| 8.3.1 External 4~24 MHz High Speed Oscillator                         |

| 8.3.2 External 4~24 MHz High Speed Crystal                            |

| 8.3.3 External 32.768 kHz Low Speed Crystal Oscillator                |

| 8.3.4 Internal 22.1184 MHz High Speed Oscillator                      |

| 8.3.5 Internal 10 kHz Low Speed Oscillator                            |

| 8.4 Analog Characteristics                                            |

- Supports SPI Master/Slave mode

- Full duplex synchronous serial data transfer

- Variable length of transfer data from 8 to 32 bits

- MSB or LSB first data transfer

- Rx and Tx on both rising or falling edge of serial clock independently

- Two slave/device select lines in Master mode, and one slave/device select line in Slave mode

- Supports Byte Suspend mode in 32-bit transmission

- Supports PDMA mode

- Supports three wire, no slave select signal, bi-direction interface

- $I^2C$

- Up to two sets of I<sup>2</sup>C devices

- Master/Slave mode

- Bidirectional data transfer between masters and slaves

- Multi-master bus (no central master)

- Arbitration between simultaneously transmitting masters without corruption of serial data on the bus

- Serial clock synchronization allowing devices with different bit rates to communicate via one serial bus

- Serial clock synchronization used as a handshake mechanism to suspend and resume serial transfer

- Programmable clocks allowing for versatile rate control

- Supports multiple address recognition (four slave address with mask option)

- Supports wake-up function

- I<sup>2</sup>S

- Interface with external audio CODEC

- Operate as either Master or Slave mode

- Capable of handling 8-, 16-, 24- and 32-bit word sizes

- Supports mono and stereo audio data

- Supports I<sup>2</sup>S and MSB justified data format

- Provides two 8 word FIFO data buffers, one for transmitting and the other for receiving

- Generates interrupt requests when buffer levels cross a programmable boundary

- Supports two DMA requests, one for transmitting and the other for receiving

- PS/2 Device

- Host communication inhibit and request to send detection

- Reception frame error detection

- Programmable 1 to 16 bytes transmit buffer to reduce CPU intervention

- Double buffer for data reception

- Software override bus

- CAN 2.0

- Supports CAN protocol version 2.0 part A and B

- Bit rates up to 1M bit/s

- 32 Message Objects

- Each Message Object has its own identifier mask

- Programmable FIFO mode (concatenation of Message Object)

- Maskable interrupt

- Disabled Automatic Re-transmission mode for Time Triggered CAN applications

- Supports Power-down wake-up function

- USB 2.0 Full-Speed Device

- One set of USB 2.0 FS Device 12 Mbps

- On-chip USB Transceiver

- Provides 1 interrupt source with 4 interrupt events

- Supports Control, Bulk In/Out, Interrupt and Isochronous transfers

- Auto suspend function when no bus signaling for 3 ms

- Provides 8 programmable endpoints

- Includes 512 Bytes internal SRAM as USB buffer

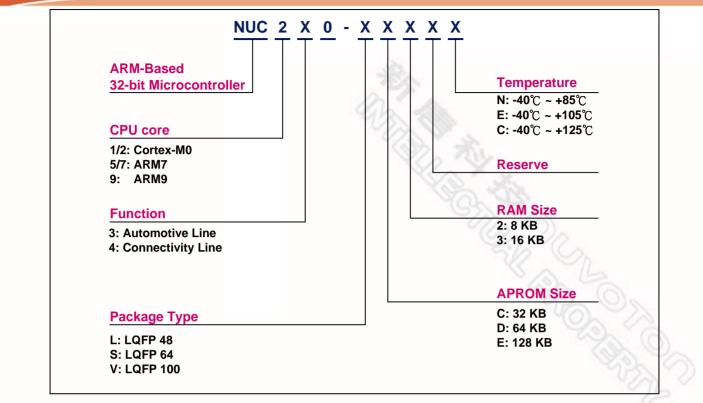

Figure 4-1 NuMicro™ NUC230/240 Series Selection Code

## NuMicro<sup>™</sup> NUC230/240 Datasheet

# nuvoTon

|                 | Pin No.        |                | Dia              |             |                                                                                                              |  |  |  |  |

|-----------------|----------------|----------------|------------------|-------------|--------------------------------------------------------------------------------------------------------------|--|--|--|--|

| LQFP<br>100-pin | LQFP<br>64-pin | LQFP<br>48-pin | Pin Name         | Pin<br>Type | Description                                                                                                  |  |  |  |  |

| 93              | 59             | 45             | PF.1             | I/O         | General purpose digital I/O pin.                                                                             |  |  |  |  |

| 93              | 59             | 40             | XT1_IN           | I           | External 4~24 MHz (high speed) crystal input pin.                                                            |  |  |  |  |

| 94              | 60             | 46             | nRESET           | I           | External reset input: active LOW, with an internal pull-up. Set this<br>bin low reset chip to initial state. |  |  |  |  |

| 95              | 61             |                | V <sub>SS</sub>  | Р           | Ground pin for digital circuit.                                                                              |  |  |  |  |

| 96              | 62             |                | V <sub>DD</sub>  | Р           | Power supply for I/O ports and LDO source for internal PLL and<br>digital circuit.                           |  |  |  |  |

| 97              |                |                | PF.2             | I/O         | General purpose digital I/O pin.                                                                             |  |  |  |  |

| 97              |                |                | PS2_DAT          | I/O         | PS2 data pin.                                                                                                |  |  |  |  |

| 98              |                |                | PF.3             | I/O         | General purpose digital I/O pin.                                                                             |  |  |  |  |

| 90              |                |                | PS2_CLK          | I/O         | PS2 clock pin.                                                                                               |  |  |  |  |

| 99              | 63             | 47             | PV <sub>SS</sub> | Р           | PLL ground.                                                                                                  |  |  |  |  |

|                 |                |                | PB.8             | I/O         | General purpose digital I/O pin.                                                                             |  |  |  |  |

| 100             | 64             | 48             | STADC            | I           | ADC external trigger input.                                                                                  |  |  |  |  |

| 100             | 04             | 40             | ТМ0              | I/O         | Timer0 event counter input / toggle output.                                                                  |  |  |  |  |

|                 |                |                | CLKO             | 0           | Frequency divider clock output pin.                                                                          |  |  |  |  |

**Note:** Pin Type I = Digital Input, O = Digital Output; AI = Analog Input; P = Power Pin; AP = Analog Power

## NuMicro<sup>™</sup> NUC230/240 Datasheet

# nuvoTon

|  |                 | Pin No.        |                |                  |             |                                                       |

|--|-----------------|----------------|----------------|------------------|-------------|-------------------------------------------------------|

|  | LQFP<br>100-pin | LQFP<br>64-pin | LQFP<br>48-pin | Pin Name         | Pin<br>Type | Description                                           |

|  | 79              | 51             | 39             | V <sub>REF</sub> | AP          | Voltage reference input for ADC.                      |

|  | 80              | 52             | 40             | AV <sub>DD</sub> | AP          | Power supply for internal analog circuit.             |

|  | 0.1             |                |                | PD.0             | I/O         | General purpose digital I/O pin.                      |

|  | 81              |                |                | SPI2_SS0         | I/O         | 1 <sup>st</sup> SPI2 slave select pin.                |

|  | 00              |                |                | PD.1             | I/O         | General purpose digital I/O pin.                      |

|  | 82              |                |                | SPI2_CLK         | I/O         | SPI2 serial clock pin.                                |

|  |                 |                |                | PD.2             | I/O         | General purpose digital I/O pin.                      |

|  | 83              |                |                | SPI2_MISO0       | I/O         | 1 <sup>st</sup> SPI2 MISO (Master In, Slave Out) pin. |

|  |                 |                |                | PD.3             | I/O         | General purpose digital I/O pin.                      |

|  | 84              |                |                | SPI2_MOSI0       | I/O         | 1 <sup>st</sup> SPI2 MOSI (Master Out, Slave In) pin. |

|  |                 |                |                | PD.4             | I/O         | General purpose digital I/O pin.                      |

|  | 85              |                |                | SPI2_MISO1       | I/O         | 2 <sup>nd</sup> SPI2 MISO (Master In, Slave Out) pin. |

|  |                 |                |                | PD.5             | I/O         | General purpose digital I/O pin.                      |

|  | 86              |                |                | SPI2_MOSI1       | I/O         | 2nd SPI2 MOSI (Master Out, Slave In) pin.             |

|  |                 | 53             | 41             | PC.7             | I/O         | General purpose digital I/O pin.                      |

|  |                 |                |                | ACMP0_N          | AI          | Comparator0 negative input pin.                       |

|  | 87              |                |                | AD5              | I/O         | EBI Address/Data bus bit5                             |

|  |                 |                |                | SC1_CD           | I           | SmartCard1 card detect pin.                           |

|  |                 |                |                | PC.6             | I/O         | General purpose digital I/O pin.                      |

|  |                 | 54             | 42             | ACMP0_P          | AI          | Comparator0 positive input pin.                       |

|  | 88              |                |                | SC0_CD           | I           | SmartCard0 card detect pin.                           |

|  | 15.             |                |                | AD4              | I/O         | EBI Address/Data bus bit4                             |

|  | 900             |                |                | PC.15            | I/O         | General purpose digital I/O pin.                      |

|  | 89              | 55             |                | AD3              | I/O         | EBI Address/Data bus bit3                             |

|  | 223             | Č.,            |                | ACMP1_N          | AI          | Comparator1 negative input pin.                       |

|  | No.             | 200            |                | PC.14            | I/O         | General purpose digital I/O pin.                      |

|  | 90              | 56             | 2              | AD2              | I/O         | EBI Address/Data bus bit2                             |

|  |                 | Zn.            | 42             | ACMP1_P          | AI          | Comparator1 positive input pin.                       |

|  |                 | 3              |                | PB.15            | I/O         | General purpose digital I/O pin.                      |

|  |                 |                | 20             | INT1             | I           | External interrupt1 input pin.                        |

|  | 91              | 57             | 43             | TM0_EXT          | I           | Timer 0 external capture input pin.                   |

|  |                 |                |                | тмо              | 0           | Timer0 toggle output pin.                             |

|  |                 |                |                | AD6              | 1/0         | EBI Address/Data bus bit6                             |

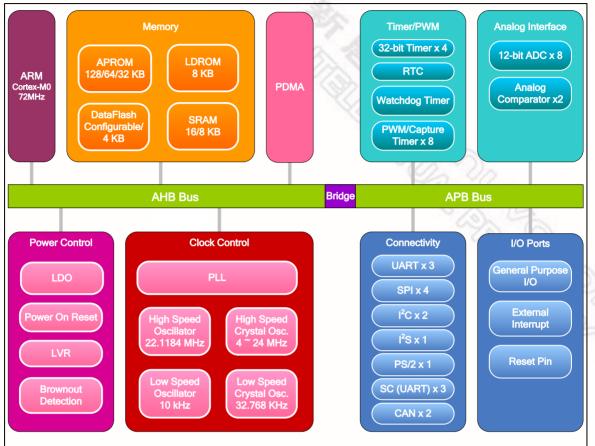

#### 5 **BLOCK DIAGRAM**

### 5.1 NuMicro™ NUC230 Block Diagram

Figure 5-1 NuMicro™ NUC230 Block Diagram

### 6.2.5 System Timer (SysTick)

The Cortex<sup>™</sup>-M0 includes an integrated system timer, SysTick, which provides a simple, 24-bit clear-on-write, decrementing, wrap-on-zero counter with a flexible control mechanism. The counter can be used as a Real Time Operating System (RTOS) tick timer or as a simple counter.

When system timer is enabled, it will count down from the value in the SysTick Current Value Register (SYST\_CVR) to 0, and reload (wrap) to the value in the SysTick Reload Value Register (SYST\_RVR) on the next clock cycle, then decrement on subsequent clocks. When the counter transitions to 0, the COUNTFLAG status bit is set. The COUNTFLAG bit clears on reads.

The SYST\_CVR value is UNKNOWN on reset. Software should write to the register to clear it to 0 before enabling the feature. This ensures the timer will count from the SYST\_RVR value rather than an arbitrary value when it is enabled.

If the SYST\_RVR is 0, the timer will be maintained with a current value of 0 after it is reloaded with this value. This mechanism can be used to disable the feature independently from the timer enable bit.

For more detailed information, please refer to the "ARM<sup>®</sup> Cortex<sup>™</sup>-M0 Technical Reference Manual" and "ARM<sup>®</sup> v6-M Architecture Reference Manual".

## NuMicro<sup>™</sup> NUC230/240 Datasheet

# nuvoTon

| 31 | 15 | SPI1_INT  | SPI1              | SPI1 interrupt                                                        |

|----|----|-----------|-------------------|-----------------------------------------------------------------------|

| 32 | 16 | SPI2_INT  | SPI2              | SPI2 interrupt                                                        |

| 33 | 17 | SPI3_INT  | SPI3              | SPI3 interrupt                                                        |

| 34 | 18 | I2C0_INT  | I <sup>2</sup> C0 | I <sup>2</sup> C0 interrupt                                           |

| 35 | 19 | I2C1_INT  | l <sup>2</sup> C1 | I <sup>2</sup> C1 interrupt                                           |

| 36 | 20 | -         | -                 | Reserved                                                              |

| 37 | 21 | -         | -                 | Reserved                                                              |

| 38 | 22 | SC012_INT | SC0/1/2           | SC0, SC1 and SC2 interrupt                                            |

| 39 | 23 | USB_INT   | USBD              | USB 2.0 FS Device interrupt                                           |

| 40 | 24 | PS2_INT   | PS/2              | PS/2 interrupt                                                        |

| 41 | 25 | ACMP_INT  | ACMP              | Analog Comparator interrupt                                           |

| 42 | 26 | PDMA_INT  | PDMA              | PDMA interrupt                                                        |

| 43 | 27 | I2S_INT   | l <sup>2</sup> S  | I <sup>2</sup> S interrupt                                            |

| 44 | 28 | PWRWU_INT | CLKC              | Clock controller interrupt for chip wake-up from Power-<br>down state |

| 45 | 29 | ADC_INT   | ADC               | ADC interrupt                                                         |

| 46 | 30 | IRC_INT   | IRC               | IRC TRIM interrupt                                                    |

| 47 | 31 | RTC_INT   | RTC               | Real Time Clock interrupt                                             |

Table 6-3 System Interrupt Map

#### 6.2.6.2 Vector Table

When an interrupt is accepted, the processor will automatically fetch the starting address of the interrupt service routine (ISR) from a vector table in memory. For ARMv6-M, the vector table base address is fixed at 0x00000000. The vector table contains the initialization value for the stack pointer on reset, and the entry point addresses for all exception handlers. The vector number on previous page defines the order of entries in the vector table associated with exception handler entry as illustrated in previous section.

| Vector Table Word Offset | Description                                      |

|--------------------------|--------------------------------------------------|

| 0                        | SP_main – The Main stack pointer                 |

| Vector Number            | Exception Entry Pointer using that Vector Number |

Table 6-4 Vector Table Format

### 6.2.6.3 Operation Description

NVIC interrupts can be enabled and disabled by writing to their corresponding Interrupt Set-Enable or Interrupt Clear-Enable register bit-field. The registers use a write-1-to-enable and write-1-to-clear policy, both registers reading back the current enabled state of the corresponding interrupts. When an interrupt is disabled, interrupt assertion will cause the interrupt to become Pending, however, the interrupt will not activate. If an interrupt is Active when it is disabled, it remains in its Active state until cleared by reset or an exception return. Clearing the enable bit prevents new activations of the associated interrupt.

NVIC interrupts can be pended/un-pended using a complementary pair of registers to those used to enable/disable the interrupts, named the Set-Pending Register and Clear-Pending Register respectively. The registers use a write-1-to-enable and write-1-to-clear policy, both registers reading back the current pended state of the corresponding interrupts. The Clear-Pending Register has no effect on the execution status of an Active interrupt.

NVIC interrupts are prioritized by updating an 8-bit field within a 32-bit register (each register supporting four interrupts).

The general registers associated with the NVIC are all accessible from a block of memory in the System Control Space and will be described in next section.

### 6.2.7 System Control

The Cortex<sup>™</sup>-M0 status and operating mode control are managed by System Control Registers. Including CPUID, Cortex<sup>™</sup>-M0 interrupt priority and Cortex<sup>™</sup>-M0 power management can be controlled through these system control registers.

For more detailed information, please refer to the "ARM<sup>®</sup> Cortex<sup>™</sup>-M0 Technical Reference Manual" and "ARM<sup>®</sup> v6-M Architecture Reference Manual".

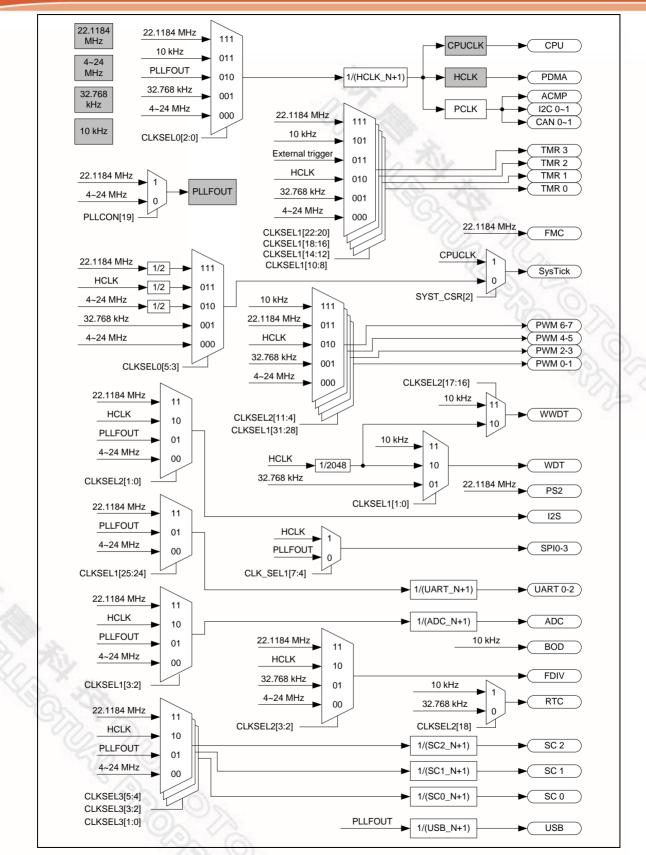

Figure 6-5 Clock Generator Global View Diagram

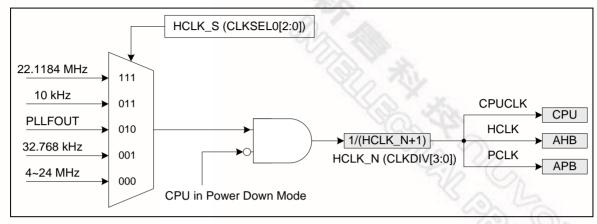

### 6.3.2 System Clock and SysTick Clock

The system clock has 5 clock sources which were generated from clock generator block. The clock source switch depends on the register HCLK\_S (CLKSEL0[2:0]). The block diagram is shown in Figure 6-6.

Figure 6-6 System Clock Block Diagram

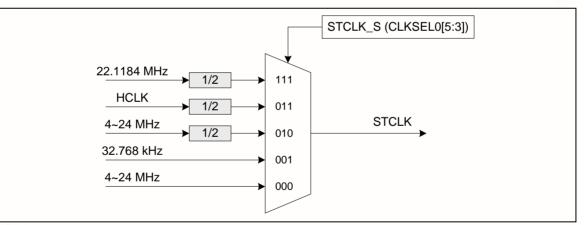

The clock source of SysTick in Cortex<sup>™</sup>-M0 core can use CPU clock or external clock (SYST\_CSR[2]). If using external clock, the SysTick clock (STCLK) has 5 clock sources. The clock source switch depends on the setting of the register STCLK\_S (CLKSEL0[5:3]). The block diagram is shown in Figure 6-7.

Figure 6-7 SysTick Clock Control Block Diagram

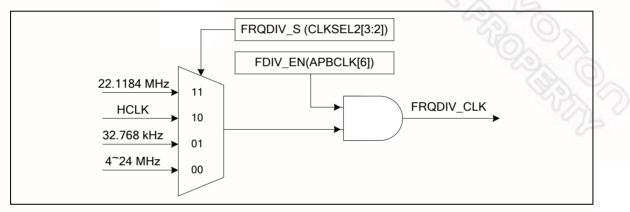

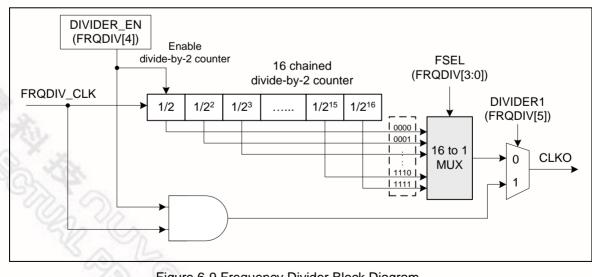

### 6.3.4 Frequency Divider Output

This device is equipped with a power-of-2 frequency divider which is composed by16 chained divide-by-2 shift registers. One of the 16 shift register outputs selected by a sixteen to one multiplexer is reflected to CLKO function pin. Therefore there are 16 options of power-of-2 divided clocks with the frequency from  $F_{in}/2^1$  to  $F_{in}/2^{16}$  where Fin is input clock frequency to the clock divider.

The output formula is  $F_{out} = F_{in}/2^{(N+1)}$ , where  $F_{in}$  is the input clock frequency,  $F_{out}$  is the clock divider output frequency and N is the 4-bit value in FSEL (FRQDIV[3:0]).

When writing 1 to DIVIDER\_EN (FRQDIV[4]), the chained counter starts to count. When writing 0 to DIVIDER\_EN (FRQDIV[4]), the chained counter continuously runs till divided clock reaches low state and stay in low state.

If DIVIDER1(FRQDIV[5]) is set to 1, the frequency divider clock (FRQDIV\_CLK) will bypass power-of-2 frequency divider. The frequency divider clock will be output to CLKO pin directly.

Figure 6-8 Clock Source of Frequency Divider

Figure 6-9 Frequency Divider Block Diagram

### 6.4 Flash Memory Controller (FMC)

### 6.4.1 Overview

The NuMicro<sup>™</sup> NUC230/240 series has 128/64/32K bytes on-chip embedded Flash for application program memory (APROM) that can be updated through ISP procedure. The In-System-Programming (ISP) function enables user to update program memory when chip is soldered on PCB. After chip is powered on, Cortex<sup>™</sup>-M0 CPU fetches code from APROM or LDROM decided by boot select (CBS) in CONFIG0. By the way, the NuMicro<sup>™</sup> NUC230/240 series also provides additional Data Flash for user to store some application dependent data. For 128K bytes APROM device, the Data Flash is shared with original 128K program memory and its start address is configurable in CONFIG1. For 64K/32K bytes APROM device, the Data Flash is fixed at 4KB.

### 6.4.2 Features

- Runs up to 50 MHz with zero wait cycle for continuous address read access and runs up to 72MHz with one wait cycle for continuous address read.

- All embedded flash memory supports 512 bytes page erase

- 128/64/32 KB application program memory (APROM)

- 8KB In-System-Programming (ISP) loader program memory (LDROM)

- 4KB Data Flash for 64/32 KB APROM device

- Configurable Data Flash size for 128KB APROM device

- Configurable or fixed 4 KB Data Flash with 512 bytes page erase unit

- Supports In-Application-Programming (IAP) to switch code between APROM and LDROM without reset

- In-System-Programming (ISP) to update on-chip Flash

### 6.9 PWM Generator and Capture Timer (PWM)

#### 6.9.1 Overview

The NuMicro<sup>™</sup> NUC230/240 series has 2 sets of PWM group supporting a total of 4 sets of PWM generators that can be configured as 8 independent PWM outputs, PWM0~PWM7, or as 4 complementary PWM pairs, (PWM0, PWM1), (PWM2, PWM3), (PWM4, PWM5) and (PWM6, PWM7) with 4 programmable Dead-zone generators.

Each PWM generator has one 8-bit prescaler, one clock divider with 5 divided frequencies (1, 1/2, 1/4, 1/8, 1/16), two PWM Timers including two clock selectors, two 16-bit PWM counters for PWM period control, two 16-bit comparators for PWM duty control and one Dead-zone generator. The 4 sets of PWM generators provide eight independent PWM interrupt flags set by hardware when the corresponding PWM period down counter reaches 0. Each PWM interrupt source with its corresponding enable bit can cause CPU to request PWM interrupt. The PWM generators can be configured as one-shot mode to produce only one PWM cycle signal or auto-reload mode to output PWM waveform continuously.

When DZEN01 (PCR[4]) is set, PWM0 and PWM1 perform complementary PWM paired function; the paired PWM period, duty and Dead-time are determined by PWM0 timer and Dead-zone generator 0. Similarly, the complementary PWM pairs of (PWM2, PWM3), (PWM4, PWM5) and (PWM6, PWM7) are controlled by PWM2, PWM4 and PWM6 timers and Dead-zone generator 2, 4 and 6, respectively. Refer to 錯誤! 找不到參照來源。 and 錯誤! 找不到參照來源。 for the architecture of PWM Timers.

To prevent PWM driving output pin with unsteady waveform, the 16-bit period down counter and 16-bit comparator are implemented with double buffer. When user writes data to counter/comparator buffer registers the updated value will be load into the 16-bit down counter/ comparator at the time down counter reaching 0. The double buffering feature avoids glitch at PWM outputs.

When the 16-bit period down counter reaches 0, the interrupt request is generated. If PWM-timer is set as auto-reload mode, when the down counter reaches 0, it is reloaded with PWM Counter Register (CNRx) automatically then start decreasing, repeatedly. If the PWM-timer is set as one-shot mode, the down counter will stop and generate one interrupt request when it reaches 0.

The value of PWM counter comparator is used for pulse high width modulation. The counter control logic changes the output to high level when down-counter value matches the value of compare register.

The alternate feature of the PWM-timer is digital input Capture function. If Capture function is enabled the PWM output pin is switched as capture input mode. The Capture0 and PWM0 share one timer which is included in PWM0 and the Capture1 and PWM1 share PWM1 timer, and etc. Therefore user must setup the PWM-timer before enable Capture feature. After capture feature is enabled, the capture always latched PWM-counter to Capture Rising Latch Register (CRLR) when input channel has a rising transition and latched PWM-counter to Capture Falling Latch Register (CFLR) when input channel has a falling transition. Capture channel 0 interrupt is programmable by setting CRL\_IE0 (CCR0[1]) (Rising latch Interrupt enable) and CFL\_IE0 (CCR0[2]) (Falling latch Interrupt enable) to decide the condition of interrupt occur. Capture channel 1 has the same feature by setting CRL\_IE1 (CCR0[17]) and CFL\_IE1 (CCR0[18]). And capture channel 2 to channel 3 on each group have the same feature by setting the corresponding control bits in CCR2. For each group, whenever Capture issues Interrupt 0/1/2/3, the PWM counter 0/1/2/3 will be reload at this moment.

The maximum captured frequency that PWM can capture is confined by the capture interrupt latency. When capture interrupt occurred, software will do at least three steps, including: Read PIIR to get interrupt source and Read CRLRx/CFLRx(x=0~3) to get capture value and finally write 1 to clear PIIR to 0. If interrupt latency will take time T0 to finish, the capture signal mustn't transition during this interval (T0). In this case, the maximum capture frequency will be 1/T0. For

### 6.13 UART Interface Controller (UART)

### 6.13.1 Overview

The NuMicro NUC230/240 series provides up to three channels of Universal Asynchronous Receiver/Transmitters (UART). UARTO supports High Speed UART and UART1~2 perform Normal Speed UART. Besides, only UARTO and UART1 support the flow control function. The UART Controller performs a serial-to-parallel conversion on data received from the peripheral, and a parallel-to-serial conversion on data transmitted from the CPU. The UART controller also supports IrDA SIR Function, LIN master/slave function and RS-485 function mode. Each UART Controller channel supports seven types of interrupts.

### 6.13.2 Features

- Full duplex, asynchronous communications

- Separates receive / transmit 64/16/16 bytes (UART0/UART1/UART2) entry FIFO for data payloads

- Supports hardware auto flow control/flow control function (CTS, RTS) and programmable RTS flow control trigger level (UART0 and UART1 support)

- Programmable receiver buffer trigger level

- Supports programmable baud-rate generator for each channel individually

- Supports CTS wake-up function (UART0 and UART1 support)

- Supports 7-bit receiver buffer time-out detection function

- UART0/UART1 can through DMA channels to receive/transmit data

- Programmable transmitting data delay time between the last stop and the next start bit by setting UA\_TOR [DLY] register

- Supports break error, frame error, parity error and receive / transmit buffer overflow detect function

- Fully programmable serial-interface characteristics

- Programmable data bit length, 5-, 6-, 7-, 8-bit character

- Programmable parity bit, even, odd, no parity or stick parity bit generation and detection

- Programmable stop bit length, 1, 1.5, or 2 stop bit generation

- IrDA SIR function mode

- Supports 3-/16-bit duration for normal mode

- LIN function mode

- Supports LIN master/slave mode

- Supports programmable break generation function for transmitter

- Supports break detect function for receiver

- RS-485 function mode.

- Supports RS-485 9-bit mode

- Supports hardware or software direct enable control provided by RTS pin (UART0 and UART1 support)

### 6.15 PS/2 Device Controller (PS2D)

#### 6.15.1 Overview

PS/2 device controller provides a basic timing control for PS/2 communication. All communication between the device and the host is managed through the PS2\_CLK and PS2\_DATA pins. Unlike PS/2 keyboard or mouse device controller, the receive/transmit code needs to be translated as meaningful code by firmware. The device controller generates the PS2\_CLK signal after receiving a "Request to Send" state, but host has ultimate control over communication. Data of PS2\_DATA line sent from the host to the device is read on the rising edge and sent from the device to the host is change after rising edge. A 16 bytes FIFO is used to reduce CPU intervention. Software can select 1 to 16 bytes for a continuous transmission.

### 6.15.2 Features

- Host communication inhibit and "Request-to-Send" state detection

- Reception frame error detection

- Programmable 1 to 16 bytes transmit buffer to reduce CPU intervention

- Double buffer for data reception

- Software override bus

### 6.16 I<sup>2</sup>C Serial Interface Controller (I<sup>2</sup>C)

#### 6.16.1 Overview

I<sup>2</sup>C is a two-wire, bi-directional serial bus that provides a simple and efficient method of data exchange between devices. The I<sup>2</sup>C standard is a true multi-master bus including collision detection and arbitration that prevents data corruption if two or more masters attempt to control the bus simultaneously.

#### 6.16.2 Features

The I<sup>2</sup>C bus uses two wires (I2Cn\_SDA and I2Cn\_SCL) to transfer information between devices connected to the bus. The main features of the I<sup>2</sup>C bus include:

- Supports up to two I<sup>2</sup>C serial interface controller

- Master/Slave mode

- Bidirectional data transfer between masters and slaves

- Multi-master bus (no central master)

- Arbitration between simultaneously transmitting masters without corruption of serial data on the bus

- Serial clock synchronization allow devices with different bit rates to communicate via one serial bus

- Built-in a 14-bit time-out counter requesting the I<sup>2</sup>C interrupt if the I<sup>2</sup>C bus hangs up and timer-out counter overflows.

- Programmable clocks allow for versatile rate control

- Supports 7-bit addressing mode

- Supports multiple address recognition (four slave address with mask option)

- Supports Power-down wake-up function

### 6.17 Serial Peripheral Interface (SPI)

#### 6.17.1 Overview

The Serial Peripheral Interface (SPI) is a synchronous serial data communication protocol that operates in full duplex mode. Devices communicate in Master/Slave mode with the 4-wire bidirection interface. The NuMicro<sup>™</sup> NUC230/240 series contains up to four sets of SPI controllers performing a serial-to-parallel conversion on data received from a peripheral device, and a parallel-to-serial conversion on data transmitted to a peripheral device. Each set of SPI controller can be configured as a master or a slave device.

The SPI controller supports the variable bus clock function for special applications and 2-bit Transfer mode to connect 2 off-chip slave devices at the same time. This controller also supports the PDMA function to access the data buffer and also supports Dual I/O Transfer mode.

- Up to 1 MSPS conversion rate (chip working at 5V)

- Three operating modes

- Single mode: A/D conversion is performed one time on a specified channel

- Single-cycle scan mode: A/D conversion is performed one cycle on all specified channels with the sequence from the smallest numbered channel to the largest numbered channel

- Continuous scan mode: A/D converter continuously performs Single-cycle scan mode until software stops A/D conversion

- An A/D conversion can be started by:

- Writing 1 to ADST bit (ADCR[11])through software

- PWM Center-aligned trigger

- External pin STADC

- Conversion results are held in data registers for each channel with valid and overrun indicators

- Supports two set digital comparators. The conversion result can be compared with specify value and user can select whether to generate an interrupt when conversion result matches the compare register setting

- Channel 7 supports 3 input sources: external analog voltage, internal Band-gap voltage, and internal temperature sensor output

### 6.22 Analog Comparator (ACMP)

#### 6.22.1 Overview

The NuMicro<sup>™</sup> NUC230/240 series contains two comparators which can be used in a number of different configurations. The comparator output is logic 1 when positive input voltage is greater than negative input voltage; otherwise the output is logic 0. Each comparator can be configured to generate interrupt request when the comparator output value changes. The block diagram is shown in 錯誤! 找不到參照來源。.

#### 6.22.2 Features

- Analog input voltage range: 0~ V<sub>DDA</sub> (Voltage of AV<sub>DD</sub> pin)

- Supports Hysteresis function

- Optional internal reference voltage source for each comparator negative input

### 8.4.3 Low Voltage Reset Specification

| PARAMETER             | CONDITION               | MIN. | TYP. | MAX. | UNIT |

|-----------------------|-------------------------|------|------|------|------|

| Operation Voltage     |                         | 0    | -    | 5.5  | V    |

| Quiescent Current     | AV <sub>DD</sub> =5.5 V | -    | 1    | 5    | μΑ   |

| Operation Temperature |                         | -40  | 25   | 105  | °C   |

| Threshold Voltage     | - 80                    | 1.6  | 2.0  | 2.4  | V    |

| Hysteresis            | - <i>Y</i>              | 0    | 0    | 0    | V    |

### 8.4.4 Brown-out Detector Specification

| PARAMETER         | CONDITION               | MIN. | TYP. | MAX. | UNIT |

|-------------------|-------------------------|------|------|------|------|

| Operation Voltage | -                       | 0    | - 9  | 5.5  | V    |

| Temperature       | -                       | -40  | 25   | 105  | °C   |

| Quiescent Current | AV <sub>DD</sub> =5.5 V | -    | -    | 125  | μA   |

|                   | BOD_VL[1:0]=11          | 4.2  | 4.4  | 4.6  | V    |

|                   | BOD_VL [1:0]=10         | 3.5  | 3.7  | 3.9  | V    |

| Brown-out Voltage | BOD_VL [1:0]=01         | 2.6  | 2.7  | 2.8  | V    |

|                   | BOD_VL [1:0]=00         | 2.1  | 2.2  | 2.3  | V    |

| Hysteresis        | -                       | 30   | -    | 150  | mV   |

### 8.4.5 Power-on Reset Specification

| PARAMETER             | CONDITION           | MIN. | TYP. | MAX. | UNIT |

|-----------------------|---------------------|------|------|------|------|

| Operation Temperature | -                   | -40  | 25   | 105  | °C   |

| Reset Voltage         | V+                  | -    | 2    | -    | V    |

| Quiescent Current     | Vin > reset voltage | -    | 1    | -    | nA   |

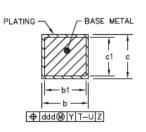

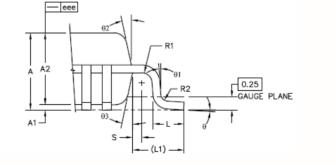

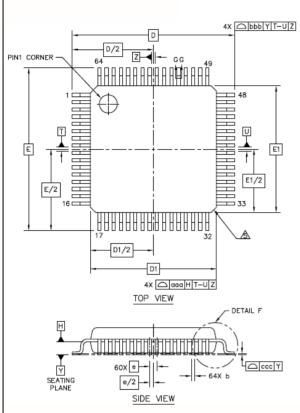

### 9.2 64-pin LQFP (7x7x1.4 mm footprint 2.0 mm)

|                      |     | SYMBOL | MIN     | NOM   | MAX  |  |

|----------------------|-----|--------|---------|-------|------|--|

| TOTAL THICKNESS      | Α   |        |         | 1.6   |      |  |

| STAND OFF            | A1  | 0.05   |         | 0.15  |      |  |

| MOLD THICKNESS       |     | A2     | 1.35    | 1.4   | 1.45 |  |

| LEAD WIDTH(PLATING)  |     | đ      | 0.13    | 0.18  | 0.23 |  |

| LEAD WIDTH           |     | b1     | 0.13    | 0.16  | 0.19 |  |

| L/F THICKNESS(PLATIN | ۹G) | с      | 0.09    |       | 0.2  |  |

| L/F THICKNESS        |     | c1     | 0.09    |       | 0.16 |  |

|                      | Х   | D      |         | 9 BSC |      |  |

|                      | Y   | E      | 9 BSC   |       |      |  |

| BODY SIZE            | Х   | D1     | 7 BSC   |       |      |  |

| BODT SIZE            | Y   | E1     | 7 BSC   |       |      |  |

| LEAD PITCH           |     | e      | 0.4 BSC |       |      |  |

|                      |     | L      | 0.45    | 0.6   | 0.75 |  |

| FOOTPRINT            |     | L1     | 1 REF   |       |      |  |

|                      |     | θ      | 0.      | 3.5*  | 7.   |  |

|                      |     | 01     | 0.      |       |      |  |

|                      |     | θ2     | 11.     | 12*   | 13   |  |

|                      |     | 03     | 11'     | 12*   | 13   |  |

|                      |     | R1     | 0.08    |       |      |  |

|                      |     | R2     | 0.08    |       | 0.2  |  |

|                      |     | S      | 0.2     |       |      |  |

| PACKAGE EDGE TOLER   | aaa | 0.2    |         |       |      |  |

| LEAD EDGE TOLERANC   | bbb |        | 0.2     |       |      |  |

| COPLANARITY          | ccc | 0.08   |         |       |      |  |

| LEAD OFFSET          |     | ddd    | 0.07    |       |      |  |

| MOLD FLATNESS        | eee |        | 0.05    |       |      |  |