Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Details                    |                                                                                         |

|----------------------------|-----------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                  |

| Core Processor             | ARM® Cortex®-M0                                                                         |

| Core Size                  | 32-Bit Single-Core                                                                      |

| Speed                      | 72MHz                                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART, USB                 |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LVD, POR, PS2, PWM, WDT                  |

| Number of I/O              | 45                                                                                      |

| Program Memory Size        | 64KB (64K x 8)                                                                          |

| Program Memory Type        | FLASH                                                                                   |

| EEPROM Size                | 4K x 8                                                                                  |

| RAM Size                   | 8K x 8                                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                             |

| Data Converters            | A/D 7x12b                                                                               |

| Oscillator Type            | Internal                                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                      |

| Mounting Type              | Surface Mount                                                                           |

| Package / Case             | 64-LQFP                                                                                 |

| Supplier Device Package    | 64-LQFP (7x7)                                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/nuc240sd2ae |

|                            |                                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 8.4.1 12-bit SARADC Specification                | 89 |

|--------------------------------------------------|----|

| 8.4.2 LDO and Power Management Specification     | 89 |

| 8.4.3 Low Voltage Reset Specification            | 90 |

| 8.4.4 Brown-out Detector Specification           | 90 |

| 8.4.5 Power-on Reset Specification               | 90 |

| 8.4.6 Temperature Sensor Specification           | 91 |

| 8.4.7 Comparator Specification                   | 91 |

| 8.4.8 USB PHY Specification                      | 92 |

| 8.5 Flash DC Electrical Characteristics          | 93 |

| 9 PACKAGE DIMENSIONS                             | 94 |

| 9.1 100-pin LQFP (14x14x1.4 mm footprint 2.0 mm) | 94 |

| 9.2 64-pin LQFP (7x7x1.4 mm footprint 2.0 mm)    | 95 |

| 9.3 48-pin LQFP (7x7x1.4 mm footprint 2.0 mm)    | 96 |

| 10REVISION HISTORY                               |    |

|                                                  |    |

| LIST OF FIGURES                                       |

|-------------------------------------------------------|

| Figure 4-1 NuMicro™ NUC230/240 Series Selection Code  |

| Figure 4-2 NuMicro™ NUC230VxxAE LQFP 100-pin Diagram  |

| Figure 4-3 NuMicro™ NUC230SxxAE LQFP 64-pin Diagram   |

| Figure 4-4 NuMicro™ NUC230LxxAE LQFP 48-pin Diagram   |

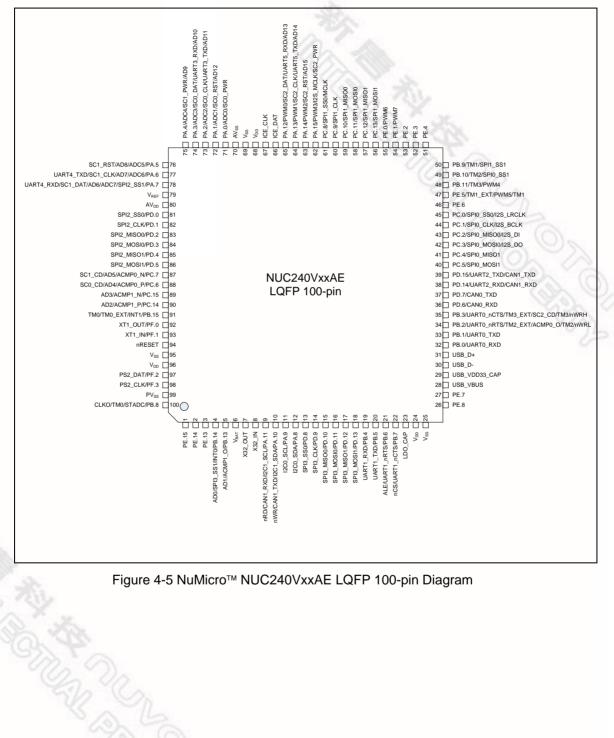

| Figure 4-5 NuMicro™ NUC240VxxAE LQFP 100-pin Diagram  |

| Figure 4-6 NuMicro™ NUC240SxxAE LQFP 64-pin Diagram   |

| Figure 4-7 NuMicro™ NUC240LxxAE LQFP 48-pin Diagram   |

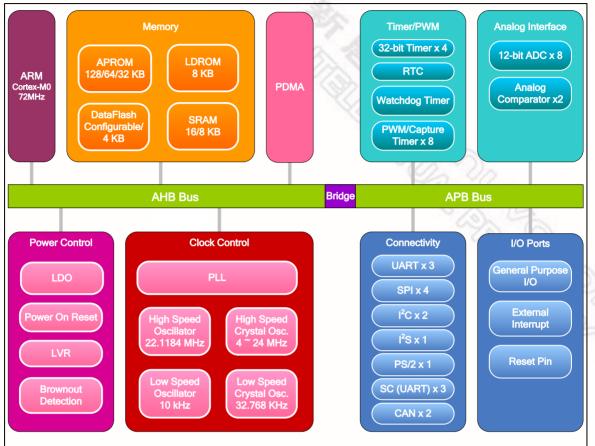

| Figure 5-1 NuMicro™ NUC230 Block Diagram              |

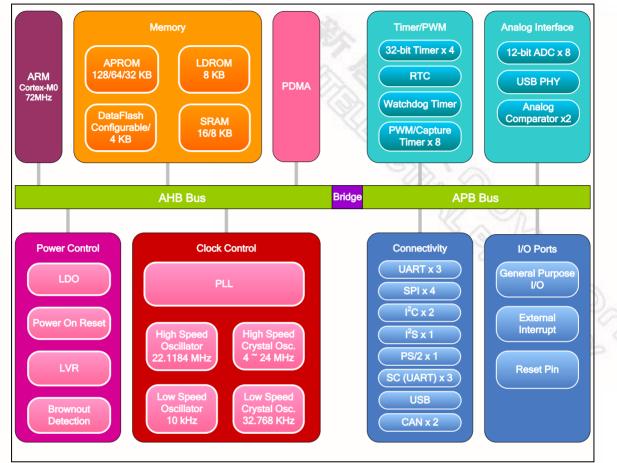

| Figure 5-2 NuMicro™ NUC240 Block Diagram              |

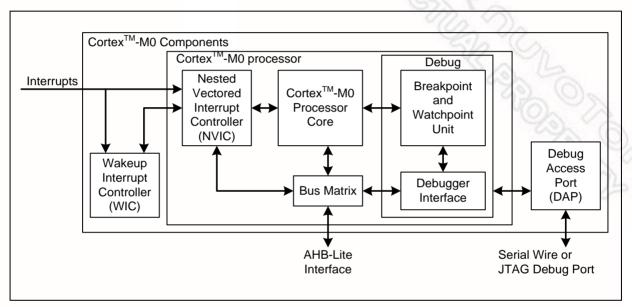

| Figure 6-1 Functional Controller Diagram45            |

| Figure 6-2 NuMicro™ NUC230 Power Distribution Diagram |

| Figure 6-3 NuMicro™ NUC240 Power Distribution Diagram |

| Figure 6-4 Clock Generator Block Diagram              |

| Figure 6-5 Clock Generator Global View Diagram        |

| Figure 6-6 System Clock Block Diagram 60              |

| Figure 6-7 SysTick Clock Control Block Diagram 60     |

| Figure 6-8 Clock Source of Frequency Divider 62       |

| Figure 6-9 Frequency Divider Block Diagram 62         |

| Figure 8-1 Typical Crystal Application Circuit        |

### 2.2 NuMicro™ NUC240 Features - Connectivity Line

- ARM® Cortex<sup>™</sup>-M0 core

- Runs up to 72 MHz

- One 24-bit system timer

- Supports low power sleep mode

- Single-cycle 32-bit hardware multiplier

- NVIC for the 32 interrupt inputs, each with 4-levels of priority

- Serial Wire Debug supports with 2 watchpoints/4 breakpoints

- Built-in LDO for wide operating voltage ranges from 2.5 V to 5.5 V

- Flash Memory

- 32K/64K/128K bytes Flash for program code

- 8 KB flash for ISP loader

- Supports In-System-Program (ISP) and In-Application-Program (IAP) application code update

- 512 byte page erase for flash

- Configurable Data Flash address and size for 128 KB system, fixed 4 KB Data Flash for the 32 KB and 64 KB system

- Supports 2-wired ICP update through SWD/ICE interface

- SRAM Memory

- 8K/16K bytes embedded SRAM

- Supports PDMA mode

- PDMA (Peripheral DMA)

- Supports 9 channels PDMA for automatic data transfer between SRAM and peripherals

- Supports CRC calculation with four common polynomials, CRC-CCITT, CRC-8, CRC-16 and CRC-32

- Clock Control

- Flexible selection for different applications

- Built-in 22.1184 MHz high speed oscillator for system operation

- Trimmed to  $\pm 1$  % at +25 °C and V<sub>DD</sub> = 5 V

- Trimmed to  $\pm 3$  % at -40  $^\circ$ C ~ +105  $^\circ$ C and V<sub>DD</sub> = 2.5 V ~ 5.5 V

- Built-in 10 kHz low speed oscillator for Watchdog Timer and Wake-up operation

- Supports one PLL, up to 72 MHz, for high performance system operation

- External 4~24 MHz high speed crystal input for USB and precise timing operation

- External 32.768 kHz low speed crystal input for RTC function and low power system operation

- GPIÓ

- Four I/O modes:

- Quasi-bidirectional

- Push-pull output

- Open-drain output

- Input only with high impendence

- TTL/Schmitt trigger input selectable

- I/O pin configured as interrupt source with edge/level setting

- Timer

- Supports 4 sets of 32-bit timers with 24-bit up-timer and one 8-bit prescale counter

- Independent clock source for each timer

- Provides one-shot, periodic, toggle and continuous counting operation modes

- Supports event counting function

- Supports input capture function

- Watchdog Timer

- Multiple clock sources

- 8 selectable time-out period from 1.6 ms ~ 26.0 sec (depending on clock source)

- Wake-up from Power-down or Idle mode

- Interrupt or reset selectable on watchdog time-out

- Supports 4 selectable Watchdog Timer reset delay period(1026, 130, 18 or 3 WDT\_CLK)

- Supports SPI Master/Slave mode

- Full duplex synchronous serial data transfer

- Variable length of transfer data from 8 to 32 bits

- MSB or LSB first data transfer

- Rx and Tx on both rising or falling edge of serial clock independently

- Two slave/device select lines in Master mode, and one slave/device select line in Slave mode

- Supports Byte Suspend mode in 32-bit transmission

- Supports PDMA mode

- Supports three wire, no slave select signal, bi-direction interface

- $I^2C$

- Up to two sets of I<sup>2</sup>C devices

- Master/Slave mode

- Bidirectional data transfer between masters and slaves

- Multi-master bus (no central master)

- Arbitration between simultaneously transmitting masters without corruption of serial data on the bus

- Serial clock synchronization allowing devices with different bit rates to communicate via one serial bus

- Serial clock synchronization used as a handshake mechanism to suspend and resume serial transfer

- Programmable clocks allowing for versatile rate control

- Supports multiple address recognition (four slave address with mask option)

- Supports wake-up function

- I<sup>2</sup>S

- Interface with external audio CODEC

- Operate as either Master or Slave mode

- Capable of handling 8-, 16-, 24- and 32-bit word sizes

- Supports mono and stereo audio data

- Supports I<sup>2</sup>S and MSB justified data format

- Provides two 8 word FIFO data buffers, one for transmitting and the other for receiving

- Generates interrupt requests when buffer levels cross a programmable boundary

- Supports two DMA requests, one for transmitting and the other for receiving

- PS/2 Device

- Host communication inhibit and request to send detection

- Reception frame error detection

- Programmable 1 to 16 bytes transmit buffer to reduce CPU intervention

- Double buffer for data reception

- Software override bus

- CAN 2.0

- Supports CAN protocol version 2.0 part A and B

- Bit rates up to 1M bit/s

- 32 Message Objects

- Each Message Object has its own identifier mask

- Programmable FIFO mode (concatenation of Message Object)

- Maskable interrupt

- Disabled Automatic Re-transmission mode for Time Triggered CAN applications

- Supports Power-down wake-up function

- USB 2.0 Full-Speed Device

- One set of USB 2.0 FS Device 12 Mbps

- On-chip USB Transceiver

- Provides 1 interrupt source with 4 interrupt events

- Supports Control, Bulk In/Out, Interrupt and Isochronous transfers

- Auto suspend function when no bus signaling for 3 ms

- Provides 8 programmable endpoints

- Includes 512 Bytes internal SRAM as USB buffer

### NuMicro<sup>™</sup> NUC230/240 Datasheet

# nuvoTon

| SPS  | Samples per Second                          |

|------|---------------------------------------------|

| TDES | Triple Data Encryption Standard             |

| TMR  | Timer Controller                            |

| UART | Universal Asynchronous Receiver/Transmitter |

| UCID | Unique Customer ID                          |

| USB  | Universal Serial Bus                        |

| WDT  | Watchdog Timer                              |

| WWDT | Window Watchdog Timer                       |

Table 3-1 List of Abbreviations

Dec. 30, 2014

### 4.2.2 NuMicro™ NUC240 Pin Diagram

4.2.2.1 NuMicro™NUC240VxxAE LQFP 100 pin

### NuMicro<sup>™</sup> NUC230/240 Datasheet

| Pin No.         |                |                |                            |             |                                                                                 |

|-----------------|----------------|----------------|----------------------------|-------------|---------------------------------------------------------------------------------|

| LQFP<br>100-pin | LQFP<br>64-pin | LQFP<br>48-pin | Pin Name                   | Pin<br>Type | Description                                                                     |

| 10              |                |                | PD.11                      | I/O         | General purpose digital I/O pin.                                                |

| 16              |                |                | SPI3_MOSI0                 | I/O         | 1 <sup>st</sup> SPI3 MOSI (Master Out, Slave In) pin.                           |

| 47              |                |                | PD.12                      | I/O         | General purpose digital I/O pin.                                                |

| 17              |                |                | SPI3_MISO1                 | I/O         | 2 <sup>nd</sup> SPI3 MISO (Master In, Slave Out) pin.                           |

| 10              |                |                | PD.13                      | I/O         | General purpose digital I/O pin.                                                |

| 18              |                |                | SPI3_MOSI1                 | I/O         | 2 <sup>nd</sup> SPI3 MOSI (Master Out, Slave In) pin.                           |

| 40              | 40             | _              | PB.4                       | I/O         | General purpose digital I/O pin.                                                |

| 19              | 10             | 8              | UART1_RXD                  | I           | Data receiver input pin for UART1.                                              |

| 00              |                | <u>_</u>       | PB.5                       | I/O         | General purpose digital I/O pin.                                                |

| 20              | 11             | 9              | UART1_TXD                  | 0           | Data transmitter output pin for UART1.                                          |

|                 |                |                | PB.6                       | I/O         | General purpose digital I/O pin.                                                |

| 21              | 12             |                | ALE                        | 0           | EBI address latch enable output pin                                             |

|                 |                |                | UART1_nRTS                 | 0           | Request to Send output pin for UART1.                                           |

|                 |                |                | PB.7                       | I/O         | General purpose digital I/O pin.                                                |

| 22              | 13             |                | nCS                        | 0           | EBI chip select enable output pin                                               |

|                 |                |                | UART1_nCTS                 | I           | Clear to Send input pin for UART1.                                              |

| 23              | 14             | 10             | LDO_CAP                    | Р           | LDO output pin.                                                                 |

| 24              | 15             | 11             | V <sub>DD</sub>            | Ρ           | Power supply for I/O ports and LDO source for internal PLL and digital circuit. |

| 25              | 16             | 12             | V <sub>SS</sub>            | Р           | Ground pin for digital circuit.                                                 |

| 26              |                |                | PE.8                       | I/O         | General purpose digital I/O pin.                                                |

| 27              |                |                | PE.7                       | I/O         | General purpose digital I/O pin.                                                |

| 28              | 17             | 13             | USB_VBUS                   | USB         | Power supply from USB host or HUB.                                              |

| 29              | 18             | 14             | USB_V <sub>DD</sub> 33_CAP | USB         | Internal power regulator output 3.3V decoupling pin.                            |

| 30              | 19             | 15             | USB_D-                     | USB         | USB differential signal D                                                       |

| 31              | 20             | 16             | USB_D+                     | USB         | USB differential signal D+.                                                     |

| 20              | 21             | 17             | PB.0                       | I/O         | General purpose digital I/O pin.                                                |

| 32              | 21             | 17             | UART0_RXD                  | Ι           | Data receiver input pin for UART0.                                              |

| 22              | 22             | 10             | PB.1                       | I/O         | General purpose digital I/O pin.                                                |

| 33              | 22             | 18             | UART0_TXD                  | 0           | Data transmitter output pin for UART0.                                          |

|                 |                | NP.            | PB.2                       | I/O         | General purpose digital I/O pin.                                                |

| 34              | 23             | C              | nWRL                       | 0           | EBI low byte write enable output pin                                            |

|                 |                |                | UART0_nRTS                 | 0           | Request to Send output pin for UART0.                                           |

### NuMicro<sup>™</sup> NUC230/240 Datasheet

|                 | Pin No.        |                |            |             |                                                       |    |

|-----------------|----------------|----------------|------------|-------------|-------------------------------------------------------|----|

| LQFP<br>100-pin | LQFP<br>64-pin | LQFP<br>48-pin | Pin Name   | Pin<br>Type | Description                                           |    |

|                 |                |                | PC.0       | I/O         | General purpose digital I/O pin.                      |    |

| 45              | 32             | 24             | SPI0_SS0   | I/O         | 1 <sup>st</sup> SPI0 slave select pin.                |    |

|                 |                |                | I2S_LRCLK  | I/O         | I <sup>2</sup> S left right channel clock.            |    |

| 46              |                |                | PE.6       | I/O         | General purpose digital I/O pin.                      |    |

|                 |                |                | PE.5       | I/O         | General purpose digital I/O pin.                      |    |

| 47              |                |                | PWM5       | I/O         | PWM5 output/Capture input.                            |    |

| -11             |                |                | TM1_EXT    | I           | Timer1 external capture input pin.                    |    |

|                 |                |                | TM1        | 0           | Timer1 toggle output pin.                             |    |

|                 |                |                | PB.11      | I/O         | General purpose digital I/O pin.                      |    |

| 48              |                |                | тмз        | I/O         | Timer3 event counter input / toggle output.           |    |

|                 |                |                | PWM4       | I/O         | PWM4 output/Capture input.                            | D. |

|                 |                |                | PB.10      | I/O         | General purpose digital I/O pin.                      | 1  |

| 49              |                |                | TM2        | I/O         | Timer2 event counter input / toggle output.           | 0  |

|                 |                |                | SPI0_SS1   | I/O         | 2 <sup>nd</sup> SPI0 slave select pin.                |    |

|                 |                |                | PB.9       | I/O         | General purpose digital I/O pin.                      |    |

| 50              |                |                | TM1        | I/O         | Timer1 event counter input / toggle output.           |    |

|                 |                |                | SPI1_SS1   | I/O         | 2 <sup>nd</sup> SPI1 slave select pin.                |    |

| 51              |                |                | PE.4       | I/O         | General purpose digital I/O pin.                      |    |

| 52              |                |                | PE.3       | I/O         | General purpose digital I/O pin.                      |    |

| 53              |                |                | PE.2       | I/O         | General purpose digital I/O pin.                      |    |

| 54              |                |                | PE.1       | I/O         | General purpose digital I/O pin.                      |    |

|                 |                |                | PWM7       | I/O         | PWM7 output/Capture input.                            |    |

| 55              |                |                | PE.0       | I/O         | General purpose digital I/O pin.                      |    |

| 235             | 1.             |                | PWM6       | I/O         | PWM6 output/Capture input.                            |    |

| 56              | S.             |                | PC.13      | I/O         | General purpose digital I/O pin.                      |    |

| 30              | 3.             | 2              | SPI1_MOSI1 | I/O         | 2 <sup>nd</sup> SPI1MOSI (Master Out, Slave In) pin.  |    |

| 57              | Zz,            | 20             | PC.12      | I/O         | General purpose digital I/O pin.                      |    |

| 51              | K              | ~              | SPI1_MISO1 | I/O         | 2 <sup>nd</sup> SPI1 MISO (Master In, Slave Out) pin. |    |

| 58              | 33             | 20             | PC.11      | I/O         | General purpose digital I/O pin.                      |    |

| 00              |                | - UR           | SPI1_MOSI0 | I/O         | 1 <sup>st</sup> SPI1 MOSI (Master Out, Slave In) pin. |    |

| 59              | 34             |                | PC.10      | 1/0         | General purpose digital I/O pin.                      |    |

| 55              | 04             |                | SPI1_MISO0 | 1/0         | 1 <sup>st</sup> SPI1 MISO (Master In, Slave Out) pin. |    |

#### 5 **BLOCK DIAGRAM**

### 5.1 NuMicro™ NUC230 Block Diagram

Figure 5-1 NuMicro™ NUC230 Block Diagram

### 5.2 NuMicro™ NUC240 Block Diagram

Figure 5-2 NuMicro™ NUC240 Block Diagram

### 6 FUNCTIONAL DESCRIPTION

### 6.1 ARM® Cortex<sup>™</sup>-M0 Core

The Cortex<sup>™</sup>-M0 processor is a configurable, multistage, 32-bit RISC processor, which has an AMBA AHB-Lite interface and includes an NVIC component. It also has optional hardware debug functionality. The processor can execute Thumb code and is compatible with other Cortex<sup>™</sup>-M profile processor. The profile supports two modes -Thread mode and Handler mode. Handler mode is entered as a result of an exception. An exception return can only be issued in Handler mode. Thread mode is entered on Reset, and can be entered as a result of an exception return.

Figure 6-1 shows the functional controller of processor.

Figure 6-1 Functional Controller Diagram

The implemented device provides the following components and features:

- A low gate count processor:

- ARMv6-M Thumb<sup>®</sup> instruction set

- Thumb-2 technology

- ARMv6-M compliant 24-bit SysTick timer

- A 32-bit hardware multiplier

- System interface supported with little-endian data accesses

- Ability to have deterministic, fixed-latency, interrupt handling

- Load/store-multiples and multicycle-multiplies that can be abandoned and restarted to facilitate rapid interrupt handling

- C Application Binary Interface compliant exception model. This is the ARMv6-M, C Application Binary Interface (C-ABI) compliant exception model that enables the use of pure C functions as interrupt handlers

- Low Power Sleep mode entry using Wait For Interrupt (WFI), Wait For Event (WFE) instructions, or the return from interrupt sleep-on-exit feature

#### 6.2.6.2 Vector Table

When an interrupt is accepted, the processor will automatically fetch the starting address of the interrupt service routine (ISR) from a vector table in memory. For ARMv6-M, the vector table base address is fixed at 0x00000000. The vector table contains the initialization value for the stack pointer on reset, and the entry point addresses for all exception handlers. The vector number on previous page defines the order of entries in the vector table associated with exception handler entry as illustrated in previous section.

| Vector Table Word Offset | Description                                      |

|--------------------------|--------------------------------------------------|

| 0                        | SP_main – The Main stack pointer                 |

| Vector Number            | Exception Entry Pointer using that Vector Number |

Table 6-4 Vector Table Format

#### 6.2.6.3 Operation Description

NVIC interrupts can be enabled and disabled by writing to their corresponding Interrupt Set-Enable or Interrupt Clear-Enable register bit-field. The registers use a write-1-to-enable and write-1-to-clear policy, both registers reading back the current enabled state of the corresponding interrupts. When an interrupt is disabled, interrupt assertion will cause the interrupt to become Pending, however, the interrupt will not activate. If an interrupt is Active when it is disabled, it remains in its Active state until cleared by reset or an exception return. Clearing the enable bit prevents new activations of the associated interrupt.

NVIC interrupts can be pended/un-pended using a complementary pair of registers to those used to enable/disable the interrupts, named the Set-Pending Register and Clear-Pending Register respectively. The registers use a write-1-to-enable and write-1-to-clear policy, both registers reading back the current pended state of the corresponding interrupts. The Clear-Pending Register has no effect on the execution status of an Active interrupt.

NVIC interrupts are prioritized by updating an 8-bit field within a 32-bit register (each register supporting four interrupts).

The general registers associated with the NVIC are all accessible from a block of memory in the System Control Space and will be described in next section.

#### 6.2.7 System Control

The Cortex<sup>™</sup>-M0 status and operating mode control are managed by System Control Registers. Including CPUID, Cortex<sup>™</sup>-M0 interrupt priority and Cortex<sup>™</sup>-M0 power management can be controlled through these system control registers.

For more detailed information, please refer to the "ARM<sup>®</sup> Cortex<sup>™</sup>-M0 Technical Reference Manual" and "ARM<sup>®</sup> v6-M Architecture Reference Manual".

### 6.4 Flash Memory Controller (FMC)

#### 6.4.1 Overview

The NuMicro<sup>™</sup> NUC230/240 series has 128/64/32K bytes on-chip embedded Flash for application program memory (APROM) that can be updated through ISP procedure. The In-System-Programming (ISP) function enables user to update program memory when chip is soldered on PCB. After chip is powered on, Cortex<sup>™</sup>-M0 CPU fetches code from APROM or LDROM decided by boot select (CBS) in CONFIG0. By the way, the NuMicro<sup>™</sup> NUC230/240 series also provides additional Data Flash for user to store some application dependent data. For 128K bytes APROM device, the Data Flash is shared with original 128K program memory and its start address is configurable in CONFIG1. For 64K/32K bytes APROM device, the Data Flash is fixed at 4KB.

#### 6.4.2 Features

- Runs up to 50 MHz with zero wait cycle for continuous address read access and runs up to 72MHz with one wait cycle for continuous address read.

- All embedded flash memory supports 512 bytes page erase

- 128/64/32 KB application program memory (APROM)

- 8KB In-System-Programming (ISP) loader program memory (LDROM)

- 4KB Data Flash for 64/32 KB APROM device

- Configurable Data Flash size for 128KB APROM device

- Configurable or fixed 4 KB Data Flash with 512 bytes page erase unit

- Supports In-Application-Programming (IAP) to switch code between APROM and LDROM without reset

- In-System-Programming (ISP) to update on-chip Flash

### 6.5 External Bus Interface (EBI)

#### 6.5.1 Overview

The NuMicro™ NUC100 series LQFP-64 and LQFP-100 package equips an external bus interface (EBI) for access external device.

To save the connections between external device and this chip, EBI supports address bus and data bus multiplex mode. And, address latch enable (ALE) signal is used to differentiate the address and data cycle.

#### 6.5.2 Features

External Bus Interface has the following functions:

- Supports external devices with max. 64 KB size (8-bit data width)/128 KB (16-bit data width)

- Supports variable external bus base clock (MCLK) which based on HCLK

- Supports 8-bit or 16-bit data width

- Supports variable data access time (tACC), address latch enable time (tALE) and address hold time (tAHD)

- Supports address bus and data bus multiplex mode to save the address pins

- Supports configurable idle cycle for different access condition: Write command finish (W2X), Read-to-Read (R2R)

### 6.6 General Purpose I/O (GPIO)

#### 6.6.1 Overview

The NuMicro<sup>™</sup> NUC230/240 series has up to 84 General Purpose I/O pins to be shared with other function pins depending on the chip configuration. These 84 pins are arranged in 6 ports named as GPIOA, GPIOB, GPIOC, GPIOD, GPIOE and GPIOF. The GPIOA/B/C/D/E port has the maximum of 16 pins and GPIOF port has the maximum of 4 pins. Each of the 84 pins is independent and has the corresponding register bits to control the pin mode function and data.

The I/O type of each of I/O pins can be configured by software individually as input, output, opendrain or Quasi-bidirectional mode. After reset, the I/O mode of all pins are depending on Config0[10] setting. In Quasi-bidirectional mode, I/O pin has a very weak individual pull-up resistor which is about 110~300 K $\Omega$  for V<sub>DD</sub> is from 5.0 V to 2.5 V.

#### 6.6.2 Features

- Four I/O modes:

- Quasi-bidirectional

- Push-Pull output

- Open-Drain output

- Input only with high impendence

- TTL/Schmitt trigger input selectable by GPx\_TYPE[15:0] in GPx\_MFP[31:16]

- I/O pin configured as interrupt source with edge/level setting

- Configurable default I/O mode of all pins after reset by Config0[10] setting

- If Config[10] is 0, all GPIO pins in input tri-state mode after chip reset

- If Config[10] is 1, all GPIO pins in Quasi-bidirectional mode after chip reset

- I/O pin internal pull-up resistor enabled only in Quasi-bidirectional I/O mode

- Enabling the pin interrupt function will also enable the pin wake-up function.

### 6.7 PDMA Controller (PDMA)

#### 6.7.1 Overview

The NuMicro<sup>™</sup> NUC230/240 series DMA contains nine-channel peripheral direct memory access (PDMA) controller and a cyclic redundancy check (CRC) generator.

The PDMA that transfers data to and from memory or transfer data to and from APB devices. For PDMA channel (PDMA CH0~CH8), there is one-word buffer as transfer buffer between the Peripherals APB devices and Memory. Software can stop the PDMA operation by disable PDMA PDMACEN (PDMA\_CSRx[0]). The CPU can recognize the completion of a PDMA operation by software polling or when it receives an internal PDMA interrupt. The PDMA controller can increase source or destination address or fixed them as well.

The DMA controller contains a cyclic redundancy check (CRC) generator that can perform CRC calculation with programmable polynomial settings. The CRC engine supports CPU PIO mode and DMA transfer mode.

### nuvoton

#### 6.7.2 Features

- Supports nine PDMA channels and one CRC channel. Each PDMA channel can support a unidirectional transfer

- AMBA AHB master/slave interface compatible, for data transfer and register read/write

- Hardware round robin priority scheme. DMA channel 0 has the highest priority and channel 8 has the lowest priority

- PDMA operation

- Peripheral-to-memory, memory-to-peripheral, and memory-to-memory transfer

- Supports word/half-word/byte transfer data width from/to peripheral

- Supports address direction: increment, fixed.

- Cyclic Redundancy Check (CRC)

- Supports four common polynomials CRC-CCITT, CRC-8, CRC-16, and CRC-32

- CRC-CCITT:  $X^{16} + X^{12} + X^5 + 1$

- **CRC-8**:  $X^8 + X^2 + X + 1$

- CRC-16:  $X^{16} + X^{15} + X^2 + 1$

- CRC-32:  $X^{32} + X^{26} + X^{23} + X^{22} + X^{16} + X^{12} + X^{11} + X^{10} + X^8 + X^7 + X^5 + X^4 + X^2 + X + 1$

- Supports programmable CRC seed value.

- Supports programmable order reverse setting for input data and CRC checksum.

- Supports programmable 1's complement setting for input data and CRC checksum.

- Supports CPU PIO mode or DMA transfer mode.

- Supports the follows write data length in CPU PIO mode

- 8-bit write mode (byte): 1-AHB clock cycle operation.

- 16-bit write mode (half-word): 2-AHB clock cycle operation.

- 32-bit write mode (word): 4-AHB clock cycle operation.

- Supports byte alignment transfer data length and word alignment transfer source address in CRC DMA mode.

### 6.8 Timer Controller (TIMER)

#### 6.8.1 Overview

The timer controller includes four 32-bit timers, TIMER0 ~ TIMER3, allowing user to easily implement a timer control for applications. The timer can perform functions, such as frequency measurement, delay timing, clock generation, and event counting by external input pins, and interval measurement by external capture pins.

### 6.10 Watchdog Timer (WDT)

#### 6.10.1 Overview

The purpose of Watchdog Timer is to perform a system reset when system runs into an unknown state. This prevents system from hanging for an infinite period of time. Besides, this Watchdog Timer supports the function to wake-up system from Idle/Power-down mode.

#### 6.10.2 Features

- 18-bit free running up counter for Watchdog Timer time-out interval.

- Selectable time-out interval (2<sup>4</sup> ~ 2<sup>18</sup>) WDT\_CLK cycle and the time-out interval period is 104 ms ~ 26.3168 s if WDT\_CLK = 10 kHz.

- System kept in reset state for a period of (1 / WDT\_CLK) \* 63

- Supports Watchdog Timer reset delay period

- Selectable it includes (1026 \ 130 \ 18 or 3) \* WDT\_CLK reset delay period.

- Supports to force Watchdog Timer enabled after chip powered on or reset while CWDTEN (CONFIG0[31] Watchdog Enable) bit is set to 0.

- Supports Watchdog Timer time-out wake-up function only if WDT clock source is selected as 10 kHz

- Up to 1 MSPS conversion rate (chip working at 5V)

- Three operating modes

- Single mode: A/D conversion is performed one time on a specified channel

- Single-cycle scan mode: A/D conversion is performed one cycle on all specified channels with the sequence from the smallest numbered channel to the largest numbered channel

- Continuous scan mode: A/D converter continuously performs Single-cycle scan mode until software stops A/D conversion

- An A/D conversion can be started by:

- Writing 1 to ADST bit (ADCR[11])through software

- PWM Center-aligned trigger

- External pin STADC

- Conversion results are held in data registers for each channel with valid and overrun indicators

- Supports two set digital comparators. The conversion result can be compared with specify value and user can select whether to generate an interrupt when conversion result matches the compare register setting

- Channel 7 supports 3 input sources: external analog voltage, internal Band-gap voltage, and internal temperature sensor output

### 6.22 Analog Comparator (ACMP)

#### 6.22.1 Overview

The NuMicro<sup>™</sup> NUC230/240 series contains two comparators which can be used in a number of different configurations. The comparator output is logic 1 when positive input voltage is greater than negative input voltage; otherwise the output is logic 0. Each comparator can be configured to generate interrupt request when the comparator output value changes. The block diagram is shown in 錯誤! 找不到參照來源。.

#### 6.22.2 Features

- Analog input voltage range: 0~ V<sub>DDA</sub> (Voltage of AV<sub>DD</sub> pin)

- Supports Hysteresis function

- Optional internal reference voltage source for each comparator negative input

### NuMicro<sup>™</sup> NUC230/240 Datasheet

|                                                                            |                                | SPECIFICATION |      |                         |      |                                                          |                                         |            |     |                       |  |

|----------------------------------------------------------------------------|--------------------------------|---------------|------|-------------------------|------|----------------------------------------------------------|-----------------------------------------|------------|-----|-----------------------|--|

| PARAMETER                                                                  | SYM.                           | MIN.          | TYP. | MAX.                    | UNIT | TEST CONDITIONS                                          |                                         |            |     |                       |  |

|                                                                            | I <sub>IDLE19</sub>            |               | 133  |                         | μA   | 3.3V                                                     | 32.768                                  | Х          | х   | V                     |  |

|                                                                            | I <sub>IDLE20</sub>            |               | 120  |                         | μА   | 3.3V                                                     | 32.768                                  | х          | х   | х                     |  |

|                                                                            |                                |               | 100  |                         |      | V <sub>DD</sub>                                          | HXT/LXT                                 | LIRC (kHz) | PLL | All digital<br>module |  |

| Operating Current                                                          | I <sub>IDLE21</sub>            |               | 122  |                         | μA   | 5.5V                                                     | x                                       | 10         | Х   | V                     |  |

| Idle Mode<br>at 10 kHz                                                     | I <sub>IDLE22</sub>            |               | 118  |                         | μA   | 5.5V                                                     | х                                       | 10         | х   | х                     |  |

|                                                                            | I <sub>IDLE23</sub>            |               | 122  |                         | μΑ   | 3.3V                                                     | x                                       | 10         | x   | V                     |  |

|                                                                            | I <sub>IDLE24</sub>            |               | 118  |                         | μA   | 3.3V                                                     | Х                                       | 10         | x   | х                     |  |

|                                                                            | I <sub>PWD1</sub>              |               | 15   |                         | μA   | V <sub>DD</sub>                                          | HXT/HIRC<br>PLL                         | LXT (kHz)  | RTC | RAM<br>retension      |  |

| Standby Current<br>Power-down Mode                                         | FWDI                           |               |      |                         | pu ( | 5.5V                                                     | Х                                       | х          | x   | V                     |  |

| (Deep Sleep Mode)                                                          | I <sub>PWD2</sub>              |               | 15   |                         | μΑ   | 5.5V                                                     | х                                       | х          | х   | V                     |  |

| V <sub>LDO</sub> =1.6 V                                                    | I <sub>PWD3</sub>              |               | 17   |                         | μΑ   | 3.3V                                                     | х                                       | 32.768     | V   | V                     |  |

|                                                                            | I <sub>PWD4</sub>              |               | 17   |                         | μA   | 3.3V                                                     | Х                                       | 32.768     | V   | v                     |  |

| RTC Operating<br>Current                                                   | I <sub>VBAT</sub>              |               | 1.6  |                         | μA   | V <sub>BAT</sub> = 3.0∖                                  | , RTC enable                            | ed         |     | •                     |  |

| Input Current PA,<br>PB, PC, PD, PE, PF<br>(Quasi-bidirectional<br>mode)   | I <sub>IN1</sub>               |               | -50  | -60                     | μΑ   | $V_{DD} = 5.5V, V_{IN} = 0V \text{ or } V_{IN} = V_{DD}$ |                                         |            |     |                       |  |

| Input Current at<br>/RESET <sup>[1]</sup>                                  | I <sub>IN2</sub>               | -55           | -45  | -30                     | μΑ   | V <sub>DD</sub> = 3.3V                                   | /, V <sub>IN</sub> = 0.45V              |            |     |                       |  |

| Input Leakage<br>Current PA, PB, PC,<br>PD, PE, PF                         | I <sub>LK</sub>                | -2            | -    | +2                      | μA   | V <sub>DD</sub> = 5.5V                                   | V, 0 <v<sub>IN<v<sub>DD</v<sub></v<sub> |            |     |                       |  |

| Logic 1 to 0<br>Transition Current<br>PA~PF (Quasi-<br>bidirectional mode) | I <sub>TL</sub> <sup>[3]</sup> | -650          | -    | -200                    | μΑ   | V <sub>DD</sub> = 5.5V                                   | ∕, V <sub>IN</sub> <2.0V                |            |     |                       |  |

| Input Low Voltage                                                          | M                              | -0.3          | -    | 0.8                     |      | V <sub>DD</sub> = 4.5V                                   | /                                       |            |     |                       |  |

| PA, PB, PC, PD, PE,<br>PF (TTL input)                                      | V <sub>IL1</sub>               | -0.3          | -    | 0.6                     | V    | $V_{DD} = 2.5 V$                                         | /                                       |            |     |                       |  |

| Input High Voltage                                                         | 2                              | 2.0           | -    | V <sub>DD</sub><br>+0.2 | V    | $V_{DD} = 5.5 V$                                         | 1                                       |            |     |                       |  |

| PÁ, PB, PC, PD, PE,<br>PF (TTL input)                                      | V <sub>IH1</sub>               | 1.5           | -    | V <sub>DD</sub><br>+0.2 | v    | V <sub>DD</sub> =3.0V                                    |                                         |            |     |                       |  |

| Input Low Voltage<br>PA, PB, PC, PD, PE,<br>PF (Schmitt input)             | $V_{\text{IL2}}$               | -0.3          | 2    | $0.3V_{DD}$             | V    |                                                          |                                         |            |     |                       |  |

| Input High Voltage<br>PA, PB, PC, PD, PE,<br>PF (Schmitt input)            | V <sub>IH2</sub>               | $0.7V_{DD}$   | 0    | V <sub>DD</sub><br>+0.2 | v    |                                                          |                                         |            |     |                       |  |

### 8.4.6 Temperature Sensor Specification

| PARAMETER                        | CONDITIONS | MIN.  | TYP.  | MAX.  | UNIT  |

|----------------------------------|------------|-------|-------|-------|-------|

| Operation Voltage <sup>[1]</sup> | The second | 2.5   | -     | 5.5   | V     |

| Operation Temperature            | Ser al     | -40   | -     | 105   | °C    |

| Current Consumption              | E.         | う     | 16    |       | μA    |

| Gain                             | K          | -1.55 | -1.65 | -1.75 | mV/°C |

| Offset Voltage                   | Temp=0 ℃   | 735   | 745   | 755   | mV    |

Note: Internal operation voltage comes from internal LDO.

### 8.4.7 Comparator Specification

| -                                                                                                       | 2.5                                                                                                                                                                                                |                                                                                                                                                                                                                 |                                                        | UNI                                                    |

|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|

|                                                                                                         |                                                                                                                                                                                                    |                                                                                                                                                                                                                 | 5.5                                                    | V                                                      |

|                                                                                                         | -40                                                                                                                                                                                                | 25                                                                                                                                                                                                              | 105                                                    | °C                                                     |

| V <sub>DD</sub> =3.0 V                                                                                  | -                                                                                                                                                                                                  | 20                                                                                                                                                                                                              | 40                                                     | μA                                                     |

| -                                                                                                       | -                                                                                                                                                                                                  | 10                                                                                                                                                                                                              | 20                                                     | m۷                                                     |

| -                                                                                                       | 0.1                                                                                                                                                                                                | -                                                                                                                                                                                                               | V <sub>DD</sub> -0.1                                   | V                                                      |

| -                                                                                                       | 0.1                                                                                                                                                                                                | -                                                                                                                                                                                                               | V <sub>DD</sub> -1.2                                   | V                                                      |

| -                                                                                                       | -                                                                                                                                                                                                  | 70                                                                                                                                                                                                              | -                                                      | dB                                                     |

| VCM=1.2 V and VDIFF=0.1 V                                                                               | -                                                                                                                                                                                                  | 200                                                                                                                                                                                                             | -                                                      | ns                                                     |

| 20 mV at VCM=1 V<br>50 mV at VCM=0.1 V<br>50 mV at VCM=V <sub>DD</sub> -1.2<br>10 mV for non-hysteresis | 10                                                                                                                                                                                                 | 20                                                                                                                                                                                                              | -                                                      | m\                                                     |

| VCM=0.4 V ~ V <sub>DD</sub> -1.2 V                                                                      | -                                                                                                                                                                                                  | ±10                                                                                                                                                                                                             | -                                                      | m\                                                     |

| CINP=1.3 V<br>CINN=1.2 V                                                                                | -                                                                                                                                                                                                  | -                                                                                                                                                                                                               | 2                                                      | μs                                                     |

|                                                                                                         | -<br>-<br>VCM=1.2 V and VDIFF=0.1 V<br>20 mV at VCM=1 V<br>50 mV at VCM=0.1 V<br>50 mV at VCM=V <sub>DD</sub> -1.2<br>10 mV for non-hysteresis<br>VCM=0.4 V ~ V <sub>DD</sub> -1.2 V<br>CINP=1.3 V | - 0.1   - -   VCM=1.2 V and VDIFF=0.1 V -   20 mV at VCM=1 V -   20 mV at VCM=0.1 V 10   50 mV at VCM=0.1 V 10   50 mV at VCM=VDD-1.2 10   10 mV for non-hysteresis 10   VCM=0.4 V ~ VDD-1.2 V -   CINP=1.3 V - | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ |