Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                           |

|--------------------------------|-----------------------------------------------------------|

| Product Status                 | Obsolete                                                  |

| Number of LABs/CLBs            | 480                                                       |

| Number of Logic Elements/Cells | 4800                                                      |

| Total RAM Bits                 | 49152                                                     |

| Number of I/O                  | 303                                                       |

| Number of Gates                | 120000                                                    |

| Voltage - Supply               | 1.71V ~ 1.89V                                             |

| Mounting Type                  | Surface Mount                                             |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                           |

| Package / Case                 | 484-BBGA, FCBGA                                           |

| Supplier Device Package        | 484-FBGA (23x23)                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1m120f484c7a |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## ...and More Features

- Advanced high-speed I/O features

- Robust I/O standard support, including LVTTL, PCI up to 66 MHz, 3.3-V AGP in 1× and 2× modes, 3.3-V SSTL-3 and 2.5-V SSTL-2, GTL+, HSTL, CTT, LVDS, LVPECL, and 3.3-V PCML

- High-speed differential interface (HSDI) with dedicated circuitry for CDR at up to 1.25 Gbps for LVDS, LVPECL, and 3.3-V PCML

- Support for source-synchronous True-LVDS™ circuitry up to 840 megabits per second (Mbps) for LVDS, LVPECL, and 3.3-V PCML

- Up to 18 input and 18 output dedicated differential channels of high-speed LVDS, LVPECL, or 3.3-V PCML

- Built-in  $100-\Omega$  termination resistor on HSDI data and clock differential pairs

- Flexible-LVDS<sup>TM</sup> circuitry provides 624-Mbps support on up to 100 channels with the EP1M350 device

- Versatile three-register I/O element (IOE) supporting double data rate I/O (DDRIO), double data-rate (DDR) SDRAM, zero bus turnaround (ZBT) SRAM, and quad data rate (QDR) SRAM

- Designed for low-power operation

- 1.8-V internal supply voltage (V<sub>CCINT</sub>)

- MultiVolt<sup>TM</sup> I/O interface voltage levels (V<sub>CCIO</sub>) compatible with 1.5-V, 1.8-V, 2.5-V, and 3.3-V devices

- 5.0-V tolerant with external resistor

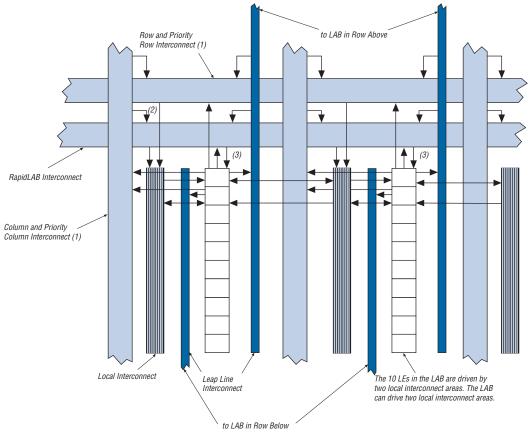

- Advanced interconnect structure

- Multi-level FastTrack<sup>®</sup> Interconnect structure providing fast, predictable interconnect delays

- Optimized high-speed Priority FastTrack Interconnect for routing critical paths in a design

- Dedicated carry chain that implements arithmetic functions such as fast adders, counters, and comparators (automatically used by software tools and megafunctions)

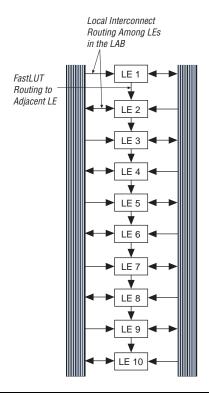

- FastLUT<sup>TM</sup> connection allowing high speed direct connection between LEs in the same logic array block (LAB)

- Leap lines allowing a single LAB to directly drive LEs in adjacent rows

- The RapidLAB interconnect providing a high-speed connection to a 10-LAB-wide region

- Dedicated clock and control signal resources, including four dedicated clocks, six dedicated fast global signals, and additional row-global signals

Mercury devices provide four dedicated clock input pins and six dedicated fast I/O pins that globally drive register control inputs, including clocks. These signals ensure efficient distribution of high-speed, low-skew control signals. The control signals use dedicated routing channels to provide short delays and low skew. The dedicated fast signals can also be driven by internal logic, providing an ideal solution for a clock divider or internally generated asynchronous control signal with high fan-out. The dedicated clock and fast I/O pins on Mercury devices can also feed logic. Dedicated clocks can also be used with the Mercury general purpose PLLs for clock management.

Each I/O row band also provides two additional I/O pins that can drive two row-global signals. Row-global signals can drive register control inputs for the LAB row associated with that particular I/O row band.

## High-Speed Differential Interface

The top I/O or HSDI band in Mercury devices contains dedicated circuitry for supporting differential standards at speeds up to 1.25 Gbps. Mercury devices have dedicated differential buffers and circuitry to support LVDS, LVPECL, and 3.3-V PCML I/O standards. Two dedicated high-speed PLLs (separate from the general purpose PLLs) multiply reference clocks and drive high-speed differential serializer/deserializer channels. In addition, clock recovery units (CRUs) at each receiver channel enable CDR. EP1M120 devices support eight input channels, eight output channels, and two dedicated clock inputs for feeding the receiver and/or transmitter PLLs. EP1M350 devices support 18 input channels, 18 output channels, and two dedicated clock inputs.

Mercury devices have optional built-in 100- $\Omega$  termination resistors on HSDI differential receiver data pins and the <code>HSDI\_CLK1</code> and <code>HSDI\_CLK2</code> pins.

Designers can use the HSDI circuitry for the following applications:

- Gigabit Ethernet backplanes

- ATM, SONET

- RapidIO

- POS-PHY Level 4

- Fibre Channel

- SDTV

The HSDI band supports one of two possible modes:

- Source-synchronous mode

- Clock data recovery (CDR) mode

Table 6 defines the support for source-synchronous mode applications.

| Table 6. Source-Synchronous Mode |              |        |            |  |  |  |  |

|----------------------------------|--------------|--------|------------|--|--|--|--|

| Data Rate                        | I/O Standard |        |            |  |  |  |  |

|                                  | LVDS         | LVPECL | 3.3-V PCML |  |  |  |  |

| ≤ 840 Mbps                       | (1)          | ✓      | ✓          |  |  |  |  |

#### Note to Table 6:

(1) You can use the CDR circuit to achieve data rates for DC coupled LVDS applications. You must AC-couple the clock to a 2.2-V common mode voltage ( $V_{\rm CM}$ ) using the AC-coupling schemes in AN 134: Using Programmable I/O Standards in Mercury Devices. The data channels should be DC-coupled. The byte alignment relative to the clock is lost when using the CDR circuit. Therefore, a byte-alignment circuit is required. Most Mercury source-synchronous designs already include byte-alignment logic since they usually use DDR or SDR clocks. The CDR run length requirement is waived if the reference clock and the receiver data come from the same source and have the same frequency.

In CDR mode, serial data is supported up to 1.25 Gbps per channel. The system provides a reference clock which is multiplied by the receiver or transmitter PLL to the same rate as the data is provided. For the receiver, this multiplied reference clock is used by a CRU on each receiver channel to generate a recovered clock in-phase with the received data. That recovered clock drives the programmable deserializer and synchronizer. The synchronizer is a FIFO for data transfer between the recovered clock domain and the global clock domain. The dedicated synchronizers can be bypassed if necessary. For every receiver channel in the EP1M350 and EP1M120 devices, the  $\div J$  recovered clock can drive a priority column line for use as a clock. See Figure 4.

Figure 5. Mercury LAB Structure

### Notes to Figure 5:

- (1) Priority column lines drive priority row lines, but not other row lines.

- (2) The RapidLAB interconnect can be driven by priority column lines, but not other column lines.

- (3) In multiplier mode, the RapidLAB interconnect drives LEs directly.

Mercury devices use an interleaved LAB structure, which allows each LAB to drive two local interconnect areas. Every other LE drives to either the left or right local interconnect area, alternating by LE. The local interconnect can drive LEs within the same LAB or adjacent LABs. This feature minimizes use of the row and column interconnects, providing higher performance and flexibility. Each LAB structure can drive 30 LEs through fast local interconnects.

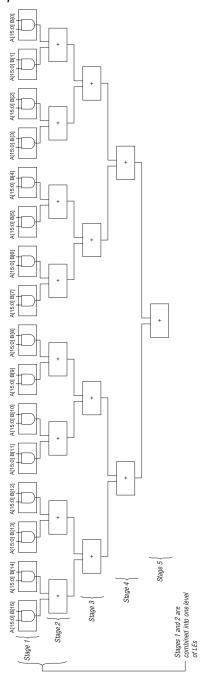

Figure 13. Mercury Binary Tree Implementation

The RapidLAB interconnect provides a specialized high-speed structure to allow a central LAB to drive other LABs within a 10-LAB-wide region. The RapidLAB lines drive alternating local LAB interconnect regions, allowing communication to all LABs in the 10-LAB-wide region. Even numbered LEs in a LAB directly drive a RapidLAB line that drives one set of alternating local interconnect regions, while odd-numbered LEs drive a RapidLAB line that drives the opposite set of alternating local interconnect regions. Figure 14 shows RapidLAB interconnect connections. This 10-LAB wide region of the RapidLAB interconnect is repeated for every LAB in the row. The region covered by the RapidLAB interconnect is smaller than 10 for source LABs that are four or five LABs in from either edge of the LAB row. The RapidLAB row interconnect is used for LAB-to-LAB routing; it is only used by I/O bands or ESBs indirectly through other interconnects. The RapidLAB interconnect drives an LE directly when that LE is in multiplier mode.

Figure 16. FastLUT Interconnect

ESB rows also have their own interconnect resources to communicate horizontally and vertically with LAB rows. The ESB rows at the top and bottom of the device have their own set of row and priority row interconnect resources. For vertical communication, all LAB column interconnect lines traverse to the ESBs. This includes leap lines, which allow the adjacent LAB rows to communicate with the ESBs.

The row interconnect resources can be driven directly by LEs or ESBs in that row. Further, the column interconnect resources can drive a row line, allowing LEs, IOEs, and ESBs to drive elements in a different row via the column and row resources.

The column interconnect resources can be directly driven by LEs, IOEs, or ESBs within that column. The priority column and leap line resources can be driven directly by LEs. These lines enable high-speed vertical communication in the device for timing-critical paths. The column resources route signals between rows. A column resource can drive row resources directly, allowing fast connections between rows.

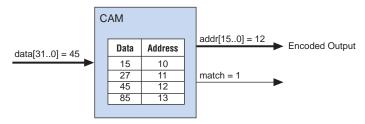

Figure 23. Encoded CAM Address Outputs

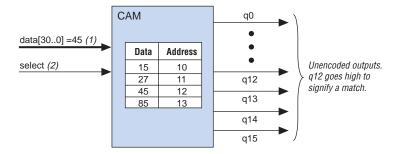

Figure 24. Unencoded CAM Address Outputs

#### Notes to Figure 24:

- (1) For an unencoded output, the ESB only supports 31 input data bits. One input bit is used by the select line to choose one of the two banks of 16 outputs.

- (2) If the select input is a 1, then CAM outputs odd words between 1 through 15. If the select input is a 0, CAM outputs words even words between 0 through 14.

In single-match mode, it takes two clock cycles to write into CAM, but only one clock cycle to read from CAM. In this mode, both encoded and unencoded outputs are available without external logic. Single-match mode is better suited for designs without duplicate data in the memory.

Dedicated Clocks

Fast Global Signals

Local Interconnect

Local Interconnect

Local Interconnect

Local Interconnect

INCLOCKEN

Figure 25. ESB Control Signal Generation

Interconnect

Interconnect

Local

The ESB can drive row interconnects within its own ESB row and can directly drive all the column interconnects: column, priority column, and leap lines.

OUTCLOCKEN

RDEN

WREN

**INCLR**

OUTCLR

OUTCLOCK

## Implementing Logic in ROM

**INCLOCK**

In addition to implementing RAM functions, the ESB can implement logic functions when it is programmed with a read-only pattern during configuration, creating a large LUT. With LUTs, combinatorial functions are implemented by looking up the results, rather than by computing them. This implementation of combinatorial functions can be faster than using algorithms implemented in general logic, a performance advantage further enhanced by the fast access times of ESBs. The large capacity of ESBs enables designers to implement complex functions in one logic level without the routing delays associated with linked LEs or distributed RAM blocks. Parameterized functions such as LPM functions can take advantage of the ESB automatically. Further, the Quartus II software can implement portions of a design with ESBs where appropriate.

|                      | T                                                            |

|----------------------|--------------------------------------------------------------|

| I/O Standard         | I <sub>OH</sub> /I <sub>OL</sub> Current Strength<br>Setting |

| VTTL (3.3 V)         | 4 mA                                                         |

|                      | 8 mA                                                         |

|                      | 12 mA                                                        |

|                      | 16 mA                                                        |

|                      | 24 mA (default)                                              |

| /TTL (2.5 V)         | 4 mA                                                         |

|                      | 8 mA                                                         |

|                      | 12 mA                                                        |

|                      | 16 mA (default)                                              |

| VTTL (1.8 V)         | 2 mA                                                         |

|                      | 4 mA (default)                                               |

| STL-3 class I and II | Minimum                                                      |

| STL-2 class I and II | Maximum (default)                                            |

| STL class I and II   |                                                              |

| GTL+ (3.3 V)         |                                                              |

## **Open-Drain Output**

Mercury devices provide an optional open-drain (equivalent to an open-collector) output for each I/O pin. This open-drain output enables the device to provide system-level control signals (e.g., interrupt and write enable signals) that can be asserted by any of several devices.

#### Slew-Rate Control

The output buffer for each Mercury device I/O pin has a programmable output slew rate control that can be configured for low-noise or high-speed performance. A faster slew rate provides high-speed transitions for high-performance systems. However, these fast transitions may introduce noise transients into the system. A slow slew rate reduces system noise, but adds a nominal delay to rising and falling edges. Each I/O pin has an individual slew rate control, allowing the designer to specify the slew rate on a pin-by-pin basis. The slew rate control affects both the rising and falling edges.

#### Dedicated Fast Lines & I/O Pins

Mercury devices incorporate dedicated bidirectional pins for signals with high internal fanout, such as PCI control signals. These pins are called dedicated fast I/O pins (FAST1, FAST2, FAST3, FAST4, FAST5, and FAST6) and can drive the six global fast lines throughout the device, ideal for fast clock, clock enable, clear, preset, or high fanout logic signal distribution. The dedicated fast I/O pins have the same IOE as a regular I/O pin. The dedicated fast lines can also be driven by a LE local interconnect to generate internal global signals.

In addition to the device global fast lines, each LAB row has two dedicated fast lines local to the row. This is ideal for high fanout control signals for a section of a design that may fit into a single LAB row. Each I/O band (with the exception of the top I/O band) has two dedicated row-global fast I/O pins to drive the row-global fast resources for the associated LAB. The dedicated local fast I/O pins have the same IOE as a regular I/O pin. The LE local interconnect can drive dedicated row-global fast lines to generate internal global signals specific to a row. There are no pin connections for buried LAB rows; LE local interconnects drive the row-global signals in those rows.

## I/O Standard Support

Mercury device IOEs support the following I/O standards:

- LVTTL

- LVCMOS

- 1.8-V

- 2.5-V

- 3.3-V PCI

- 3.3-V PCI-X

- 3.3-V AGP (1×, 2×)

- LVDS

- LVPECL

- 3.3-V PCML

- GTL+

- HSTL class I and II

- SSTL-3 class I and II

- SSTL-2 class I and II

- CTT

Normal Mode: The external clock output pin will have phase delay relative to the clock input pin. If an internal clock is used in this mode, the IOE register clock will be phase aligned to the input clock pin. Multiplication is allowed with the normal mode.

## Advanced ClockShift Circuitry

General purpose PLLs in Mercury devices have advanced ClockShift<sup>TM</sup> circuitry that provides programmable phase shift and fine tune time delay shift. For phase shifting, users can enter a phase shift (in degrees or time units) that affects all PLL outputs. Phase shifts of 90, 180, and 270 can be implemented exactly. Other values of phase shifting, or delay shifting in time units, are allowed with a resolution range of 0.3 ns to 1.0 ns. This resolution varies with frequency input and the user-entered multiplication and division factors. The phase shift ability is only possible on a multiplied or divided clock if the input and output frequency have an integer multiple relationship (i.e.,  $f_{\rm IN}/f_{\rm OUT}$  or  $f_{\rm OUT}/f_{\rm IN}$  must be an integer).

In addition to the phase shift feature that affects all outputs, there is an advanced fine time delay shift control on each of the four PLL outputs. Each PLL output can be shifted in 250-ps increments for a range of –2.0 ns to +2.0 ns. This ability can be used in conjunction with the phase shifting ability that affects all outputs.  $f_{\rm IN}/f_{\rm OUT}$  does not need to have an integer relationship for the advanced fine time delay shift control.

## Clock Enable Signal

Mercury PLLs have a CLKLK\_ENA pin for enabling/disabling all of the device PLLs. When the CLKLK\_ENA pin is high, the PLL drives a clock to all its output ports. When the CLKLK\_ENA pin is low, the clock0, clock1, clock2 and extclock ports are driven by GND and all of the PLLs go out of lock. When the CLKLK\_ENA pin goes high again, the PLL must relock.

The individual enable port for each general purpose PLL is programmable. If more than one general-purpose PLL is instantiated, each one does not have to use the clock enable. To enable/disable the device PLLs with the CLKLK\_ENA pin, the inclocken port on the altclklock instance must be connected to the CLKLK\_ENA input pin.

| Table 26. 1.8-V I/O Specifications Note (10) |                           |                                            |                          |                        |       |  |  |  |  |  |

|----------------------------------------------|---------------------------|--------------------------------------------|--------------------------|------------------------|-------|--|--|--|--|--|

| Symbol                                       | Parameter                 | Conditions                                 | Minimum                  | Maximum                | Units |  |  |  |  |  |

| V <sub>CCIO</sub>                            | Output supply voltage     |                                            | 1.71                     | 1.89                   | V     |  |  |  |  |  |

| V <sub>IH</sub>                              | High-level input voltage  |                                            | $0.65 \times V_{CCIO}$   | 4.1                    | V     |  |  |  |  |  |

| V <sub>IL</sub>                              | Low-level input voltage   |                                            | -0.5                     | $0.35 \times V_{CCIO}$ | V     |  |  |  |  |  |

| I <sub>I</sub>                               | Input pin leakage current | V <sub>IN</sub> = 0 V or V <sub>CCIO</sub> | -10                      | 10                     | μΑ    |  |  |  |  |  |

| V <sub>OH</sub>                              | High-level output voltage | $I_{OH} = -2 \text{ mA}$                   | V <sub>CCIO</sub> - 0.45 |                        | V     |  |  |  |  |  |

| $V_{OL}$                                     | Low-level output voltage  | $I_{OL} = 2 \text{ mA}$                    |                          | 0.45                   | V     |  |  |  |  |  |

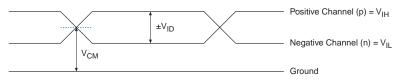

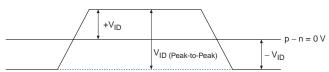

Figures 34 and 35 show receiver input and transmitter output waveforms, respectively, for all differential I/O standards (LVPECL, 3.3-V PCML, LVDS, and HyperTransport technology).

Figure 34. Receiver Input Waveforms for Differential I/O Standards

Single-Ended Waveform

#### **Differential Waveform**

| Symbol            | Parameter                 | Conditions                              | Minimum                    | Typical | Maximum                    | Units |

|-------------------|---------------------------|-----------------------------------------|----------------------------|---------|----------------------------|-------|

| V <sub>CCIO</sub> | I/O supply voltage        |                                         | 3.0                        | 3.3     | 3.6                        | V     |

| V <sub>IH</sub>   | High-level input voltage  |                                         | 0.5 ×<br>V <sub>CCIO</sub> |         | V <sub>CCIO</sub> + 0.5    | V     |

| V <sub>IL</sub>   | Low-level input voltage   |                                         | -0.5                       |         | 0.3 ×<br>V <sub>CCIO</sub> | V     |

| I <sub>I</sub>    | Input pin leakage current | 0 < V <sub>IN</sub> < V <sub>CCIO</sub> | -10                        |         | 10                         | μΑ    |

| V <sub>OH</sub>   | High-level output voltage | I <sub>OUT</sub> = -500 μA              | 0.9 ×<br>V <sub>CCIO</sub> |         |                            | V     |

| V <sub>OL</sub>   | Low-level output voltage  | I <sub>OUT</sub> = 1,500 μA             |                            |         | 0.1 ×<br>V <sub>CCIO</sub> | V     |

| Symbol            | Parameter                 | Conditions                  | Minimum           | Typical | Maximum             | Units |

|-------------------|---------------------------|-----------------------------|-------------------|---------|---------------------|-------|

| V <sub>CCIO</sub> | I/O supply voltage        |                             | 3.0               |         | 3.6                 | V     |

| V <sub>IH</sub>   | High-level input voltage  |                             | 0.5 ×             |         | V <sub>CCIO</sub> + | V     |

|                   |                           |                             | V <sub>CCIO</sub> |         | 0.5                 |       |

| V <sub>IL</sub>   | Low-level input voltage   |                             | -0.5              |         | 0.35×               | V     |

|                   |                           |                             |                   |         | V <sub>CCIO</sub>   |       |

| V <sub>IPU</sub>  | Input pull-up voltage     |                             | 0.7 ×             |         |                     | V     |

|                   |                           |                             | V <sub>CCIO</sub> |         |                     |       |

| I <sub>IL</sub>   | Input leakage current     | $0 < V_{IN} < V_{CCIO}$     | -10               |         | 10                  | μΑ    |

| V <sub>OH</sub>   | High-level output voltage | $I_{OUT} = -500 \mu A$      | 0.9 ×             |         |                     | V     |

|                   |                           |                             | V <sub>CCIO</sub> |         |                     |       |

| V <sub>OL</sub>   | Low-level output voltage  | I <sub>OUT</sub> = 1,500 μA |                   |         | 0.1 ×               | V     |

| -                 |                           |                             |                   |         | $V_{CCIO}$          |       |

| L <sub>PIN</sub>  | Pin inductance            |                             |                   |         | 15                  | nH    |

| Table 32. GTL+ I/O Specifications Note (10) |                          |                         |                        |         |                        |       |  |  |  |

|---------------------------------------------|--------------------------|-------------------------|------------------------|---------|------------------------|-------|--|--|--|

| Symbol                                      | Parameter                | Conditions              | Minimum                | Typical | Maximum                | Units |  |  |  |

| V <sub>TT</sub>                             | Termination voltage      |                         | 1.35                   | 1.5     | 1.65                   | V     |  |  |  |

| $V_{REF}$                                   | Reference voltage        |                         | 0.88                   | 1.0     | 1.12                   | V     |  |  |  |

| $V_{IH}$                                    | High-level input voltage |                         | V <sub>REF</sub> + 0.1 |         |                        | V     |  |  |  |

| $V_{IL}$                                    | Low-level input voltage  |                         |                        |         | V <sub>REF</sub> - 0.1 | V     |  |  |  |

| $V_{OL}$                                    | Low-level output voltage | I <sub>OL</sub> = 34 mA |                        |         | 0.65                   | V     |  |  |  |

| Table 36. SSTL-3 Class II Specifications Note (10) |                           |                           |                        |           |                         |       |  |  |  |

|----------------------------------------------------|---------------------------|---------------------------|------------------------|-----------|-------------------------|-------|--|--|--|

| Symbol                                             | Parameter                 | Conditions                | Minimum                | Typical   | Maximum                 | Units |  |  |  |

| V <sub>CCIO</sub>                                  | I/O supply voltage        |                           | 3.0                    | 3.3       | 3.6                     | V     |  |  |  |

| $V_{TT}$                                           | Termination voltage       |                           | $V_{REF} - 0.05$       | $V_{REF}$ | V <sub>REF</sub> + 0.05 | V     |  |  |  |

| $V_{REF}$                                          | Reference voltage         |                           | 1.3                    | 1.5       | 1.7                     | V     |  |  |  |

| $V_{IH}$                                           | High-level input voltage  |                           | V <sub>REF</sub> + 0.2 |           | V <sub>CCIO</sub> + 0.3 | V     |  |  |  |

| $V_{IL}$                                           | Low-level input voltage   |                           | -0.3                   |           | V <sub>REF</sub> – 0.2  | V     |  |  |  |

| V <sub>OH</sub>                                    | High-level output voltage | $I_{OH} = -16 \text{ mA}$ | V <sub>TT</sub> + 0.8  |           |                         | V     |  |  |  |

| $V_{OL}$                                           | Low-level output voltage  | I <sub>OL</sub> = 16 mA   |                        |           | V <sub>TT</sub> – 0.8   | V     |  |  |  |

| Table 37. 3.3-V AGP -2X Specifications |                               |                          |                         |         |                         |       |  |  |  |  |

|----------------------------------------|-------------------------------|--------------------------|-------------------------|---------|-------------------------|-------|--|--|--|--|

| Symbol                                 | Parameter                     | Conditions               | Minimum                 | Typical | Maximum                 | Units |  |  |  |  |

| V <sub>CCIO</sub>                      | I/O supply voltage            |                          | 3.15                    | 3.3     | 3.45                    | V     |  |  |  |  |

| $V_{REF}$                              | Reference voltage             |                          | $0.39 \times V_{CCIO}$  |         | $0.41 \times V_{CCIO}$  | V     |  |  |  |  |

| V <sub>IH</sub>                        | High-level input voltage (12) |                          | $0.5 \times V_{CCIO}$   |         | V <sub>CCIO</sub> + 0.5 | V     |  |  |  |  |

| V <sub>IL</sub>                        | Low-level input voltage (12)  |                          |                         |         | 0.3 × V <sub>CCIO</sub> | V     |  |  |  |  |

| V <sub>OH</sub>                        | High-level output voltage     | $I_{OUT} = -20 \mu A$    | 0.9 × V <sub>CCIO</sub> |         | 3.6                     | V     |  |  |  |  |

| V <sub>OL</sub>                        | Low-level output voltage      | I <sub>OUT</sub> = 20 μA |                         |         | $0.1 \times V_{CCIO}$   | V     |  |  |  |  |

| I <sub>I</sub>                         | Input pin leakage current     | $0 < V_{IN} < V_{CCIO}$  |                         |         | ±10                     | μΑ    |  |  |  |  |

| Table 38. 3.3-V AGP -1X Specifications |                               |                          |                         |         |                         |       |  |  |  |  |

|----------------------------------------|-------------------------------|--------------------------|-------------------------|---------|-------------------------|-------|--|--|--|--|

| Symbol                                 | Parameter                     | Conditions               | Minimum                 | Typical | Maximum                 | Units |  |  |  |  |

| V <sub>CCIO</sub>                      | I/O supply voltage            |                          | 3.15                    | 3.3     | 3.45                    | V     |  |  |  |  |

| V <sub>IH</sub>                        | High-level input voltage (12) |                          | 0.5 × V <sub>CCIO</sub> |         | V <sub>CCIO</sub> + 0.5 | V     |  |  |  |  |

| V <sub>IL</sub>                        | Low-level input voltage (12)  |                          |                         |         | $0.3 \times V_{CCIO}$   | V     |  |  |  |  |

| V <sub>OH</sub>                        | High-level output voltage     | $I_{OUT} = -20 \mu A$    | $0.9 \times V_{CCIO}$   |         | 3.6                     | V     |  |  |  |  |

| V <sub>OL</sub>                        | Low-level output voltage      | I <sub>OUT</sub> = 20 μA |                         |         | $0.1 \times V_{CCIO}$   | V     |  |  |  |  |

| I                                      | Input pin leakage current     | $0 < V_{IN} < V_{CCIO}$  |                         |         | ±10                     | μΑ    |  |  |  |  |

| Table 42. Bus Hold Parameters |                                                |             |                   |         |         |         |         |       |  |

|-------------------------------|------------------------------------------------|-------------|-------------------|---------|---------|---------|---------|-------|--|

| Parameter                     | Conditions                                     | VCCIO Level |                   |         |         |         |         | Units |  |

|                               |                                                | 1.8         | 1.8 V 2.5 V 3.3 V |         |         | 3 V     |         |       |  |

|                               |                                                | Minimum     | Maximum           | Minimum | Maximum | Minimum | Maximum |       |  |

| Low sustaining current        | V <sub>IN</sub> > V <sub>IL</sub><br>(maximum) | 30          |                   | 50      |         | 70      |         | μА    |  |

| High sustaining current       | V <sub>IN</sub> < V <sub>IH</sub><br>(minimum) | -30         |                   | -50     |         | -70     |         | μΑ    |  |

| Low overdrive current         | 0 V < V <sub>IN</sub> < V <sub>CCIO</sub>      |             | 200               |         | 300     |         | 500     | μА    |  |

| High overdrive current        | 0 V < V <sub>IN</sub> < V <sub>CCIO</sub>      |             | -200              |         | -300    |         | -500    | μΑ    |  |

| Table 43. Mercury Device Capacitance   Note (13) |                                                     |         |         |         |      |  |  |  |  |  |

|--------------------------------------------------|-----------------------------------------------------|---------|---------|---------|------|--|--|--|--|--|

| Symbol                                           | Parameter                                           | Minimum | Typical | Maximum | Unit |  |  |  |  |  |

| C <sub>IO</sub>                                  | I/O pin capacitance                                 |         | 13.5    |         | pF   |  |  |  |  |  |

| C <sub>CLK</sub>                                 | Input capacitance on CLK[41] pins                   |         | 16.9    |         | pF   |  |  |  |  |  |

| C <sub>RXHSDI</sub>                              | Input capacitance on HSDI receiver pins             |         | 8.0     |         | pF   |  |  |  |  |  |

| C <sub>TXHSDI</sub>                              | Input capacitance on HSDI transmitter pins          |         | 18.0    |         | pF   |  |  |  |  |  |

| C <sub>CLKHSDI</sub>                             | Input capacitance on HSDI clock pins                |         | 7.5     |         | pF   |  |  |  |  |  |

| C <sub>FLEXLVDSRX</sub>                          | Input capacitance on flexible LVDS receiver pins    |         | 13.4    |         | pF   |  |  |  |  |  |

| C <sub>FLEXLVDSTX</sub>                          | Input capacitance on flexible LVDS transmitter pins |         | 13.4    |         | pF   |  |  |  |  |  |

#### Notes to Tables 20 – 43.:

- (1) See the Operating Requirements for Altera Devices Data Sheet.

- (2) Minimum DC input is -0.5 V. During transitions, the inputs may undershoot to -0.5 V or overshoot to 4.1 V for input currents less than 100 mA and periods shorter than 20 ns.

- (3) Maximum  $V_{CC}$  rise time is 100 ms, and  $V_{CC}$  must rise monotonically.

- (4) V<sub>CCIO</sub> maximum and minimum conditions for LVPECL, LVDS, RapidIO, and 3.3-V PCML are shown in parentheses.

- (5) All pins, including dedicated inputs, clock, I/O, and JTAG pins, may be driven before V<sub>CCINT</sub> and V<sub>CCIO</sub> are powered.

- (6) Typical values are for  $T_A = 25^{\circ}$  C,  $V_{CCINT} = 1.8$  V, and  $V_{CCIO} = 1.8$  V, 2.5 V, and 3.3 V.

- (7) These values are specified under the Mercury Device Recommended Operating Conditions shown in Table 3 on page 3.

- (8) Input pins are grounded. In the test design, internal logic does not toggle. The test design does not use PLL or HSDI circuitry. All ESBs are in power-down mode.

- (9) Pin pull-up resistance values will lower if an external source drives the pin higher than V<sub>CCIO</sub>.

- (10) Drive strength is programmable according to values in Table 11 on page 53.

- (11) For more information on termination, see AN 134: Using Programmable I/O Standards in Mercury Devices or AN 159: Using HSDI in Source-Synchronous Mode in Mercury Devices.

- (12) V<sub>REF</sub> specifies the center point of the switching range.

- (13) Capacitance is sample-tested only. Capacitance is measured using time-domain reflections (TDR). Measurement accuracy is within ±5%.

## Timing Model

The high-performance multi-level FastTrack Interconnect routing resources ensure predictable performance, accurate simulation, and accurate timing analysis. The predictable performance of Mercury devices offer an advantage over FPGAs, which use a segmented connection scheme and therefore have unpredictable performance.

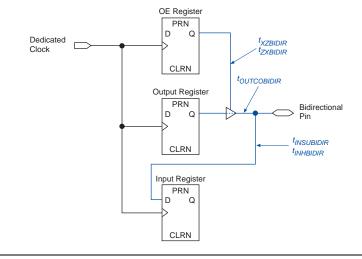

Figure 36 shows the timing model for bidirectional IOE pin timing. All registers are within the IOE.

Figure 36. Synchronous Bidirectional Pin External Timing Model

| Table 48. EP1M120 External Timing Parameters Note (1) |                 |      |          |          |      |  |  |

|-------------------------------------------------------|-----------------|------|----------|----------|------|--|--|

| Symbol                                                | -7A Speed Grade |      | -8A Spee | ed Grade | Unit |  |  |

|                                                       | Min             | Max  | Min      | Max      |      |  |  |

| t <sub>INSU</sub>                                     | 0.74            |      | 0.79     |          | ns   |  |  |

| t <sub>INH</sub>                                      | 0.00            |      | 0.00     |          | ns   |  |  |

| tоитсо                                                | 2.00            | 3.50 | 2.00     | 4.10     | ns   |  |  |

| t <sub>INSUPLL</sub>                                  | 0.62            |      | 0.75     |          | ns   |  |  |

| t <sub>INHPLL</sub>                                   | 0.00            |      | 0.00     |          | ns   |  |  |

| toutcopll                                             | 0.50            | 2.15 | 0.50     | 2.43     | ns   |  |  |

| Table 49. EP1M120 External Bidirectional Timing Parameters Note (1) |                 |      |         |      |    |  |  |

|---------------------------------------------------------------------|-----------------|------|---------|------|----|--|--|

| Symbol                                                              | -7A Speed Grade |      | -8A Spe | Unit |    |  |  |

|                                                                     | Min             | Max  | Min     | Max  |    |  |  |

| t <sub>INSUBIDIR</sub>                                              | 0.74            |      | 0.79    |      | ns |  |  |

| t <sub>INHBIDIR</sub>                                               | 0.00            |      | 0.00    |      | ns |  |  |

| toutcobidir                                                         | 2.00            | 3.50 | 2.00    | 4.10 | ns |  |  |

| t <sub>XZBIDIR</sub>                                                |                 | 3.75 |         | 4.30 | ns |  |  |

| t <sub>ZXBIDIR</sub> (2)                                            |                 | 3.75 |         | 4.30 | ns |  |  |

| t <sub>ZXBIDIR</sub> (3)                                            |                 | 4.00 |         | 4.58 | ns |  |  |

| tINSUBIDIRPLL                                                       | 0.62            |      | 0.75    |      | ns |  |  |

| t <sub>INHBIDIRPLL</sub>                                            | 0.00            |      | 0.00    |      | ns |  |  |

| tOUTCOBIDIRPLL                                                      | 0.50            | 2.15 | 0.50    | 2.43 | ns |  |  |

| t <sub>XZBIDIRPLL</sub>                                             |                 | 2.39 |         | 2.67 | ns |  |  |

| t <sub>ZXBIDIRPLL</sub> (2)                                         |                 | 2.39 |         | 2.67 | ns |  |  |

| t <sub>ZXBIDIRPLL</sub> (3)                                         |                 | 2.64 |         | 2.95 | ns |  |  |

| Table 50. EP1M350 External Timing Parameters Note (1) |                |      |                |      |                |      |      |

|-------------------------------------------------------|----------------|------|----------------|------|----------------|------|------|

| Symbol                                                | -5 Speed Grade |      | -6 Speed Grade |      | -7 Speed Grade |      | Unit |

|                                                       | Min            | Max  | Min            | Max  | Min            | Max  |      |

| t <sub>INSU</sub>                                     | 0.60           |      | 0.57           |      | 0.71           |      | ns   |

| t <sub>INH</sub>                                      | 0.00           |      | 0.00           |      | 0.00           |      | ns   |

| t <sub>outco</sub>                                    | 2.00           | 3.95 | 2.00           | 3.97 | 2.00           | 4.75 | ns   |

| t <sub>INSUPLL</sub>                                  | 0.69           |      | 0.70           |      | 0.82           |      | ns   |

| t <sub>INHPLL</sub>                                   | 0.00           |      | 0.00           |      | 0.00           |      | ns   |

| tOUTCOPLL                                             | 0.50           | 2.23 | 0.50           | 2.23 | 0.50           | 2.69 | ns   |

## Revision History

The information contained in the *Mercury Programmable Logic Device Family Data Sheet* version 2.2 supersedes information published in previous versions.

### Version 2.2

The following changes were made to the *Mercury Programmable Logic Device Family Data Sheet* version 2.2:

Updated the condition values (symbols I<sub>I</sub> and I<sub>OZ</sub>) in Table 22.

### Version 2.1

The following changes were made to the *Mercury Programmable Logic Device Family Data Sheet* version 2.1:

- Updated Table 8.

- Updated EP1M350 regular I/O banks in Table 13.

- Updated *Note (6)* in Table 14.

#### Version 2.0

The following changes were made to the *Mercury Programmable Logic Device Family Data Sheet* version 2.0:

- Changed all references to PCML to 3.3-V PCML.

- Updated Table 4.

- Updated "High-Speed Differential Interface" on page 8.

- Added Tables 6 through 8.

- Added Figures 34 and 35.

- Updated I/O specifications in Tables 28 and 29.

- Updated Mercury device capacitance in Table 43.

- Updated EP1M120 device timing in Tables 46 through 49.

- Added EP1M350 device timing in Tables 50 and 51.

101 Innovation Drive San Jose, CA 95134 (408) 544-7000 http://www.altera.com Applications Hotline: (800) 800-EPLD Customer Marketing: (408) 544-7104 Literature Services: lit\_req@altera.com

Copyright © 2003 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, mask work rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes

to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.