Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                           |

|--------------------------------|-----------------------------------------------------------|

| Product Status                 | Obsolete                                                  |

| Number of LABs/CLBs            | 480                                                       |

| Number of Logic Elements/Cells | 4800                                                      |

| Total RAM Bits                 | 49152                                                     |

| Number of I/O                  | 303                                                       |

| Number of Gates                | 120000                                                    |

| Voltage - Supply               | 1.71V ~ 1.89V                                             |

| Mounting Type                  | Surface Mount                                             |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                           |

| Package / Case                 | 484-BBGA, FCBGA                                           |

| Supplier Device Package        | 484-FBGA (23x23)                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1m120f484c8a |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# ...and More Features

- Advanced high-speed I/O features

- Robust I/O standard support, including LVTTL, PCI up to 66 MHz, 3.3-V AGP in 1× and 2× modes, 3.3-V SSTL-3 and 2.5-V SSTL-2, GTL+, HSTL, CTT, LVDS, LVPECL, and 3.3-V PCML

- High-speed differential interface (HSDI) with dedicated circuitry for CDR at up to 1.25 Gbps for LVDS, LVPECL, and 3.3-V PCML

- Support for source-synchronous True-LVDS™ circuitry up to 840 megabits per second (Mbps) for LVDS, LVPECL, and 3.3-V PCML

- Up to 18 input and 18 output dedicated differential channels of high-speed LVDS, LVPECL, or 3.3-V PCML

- Built-in  $100-\Omega$  termination resistor on HSDI data and clock differential pairs

- Flexible-LVDS<sup>TM</sup> circuitry provides 624-Mbps support on up to 100 channels with the EP1M350 device

- Versatile three-register I/O element (IOE) supporting double data rate I/O (DDRIO), double data-rate (DDR) SDRAM, zero bus turnaround (ZBT) SRAM, and quad data rate (QDR) SRAM

- Designed for low-power operation

- 1.8-V internal supply voltage (V<sub>CCINT</sub>)

- MultiVolt<sup>TM</sup> I/O interface voltage levels (V<sub>CCIO</sub>) compatible with 1.5-V, 1.8-V, 2.5-V, and 3.3-V devices

- 5.0-V tolerant with external resistor

- Advanced interconnect structure

- Multi-level FastTrack<sup>®</sup> Interconnect structure providing fast, predictable interconnect delays

- Optimized high-speed Priority FastTrack Interconnect for routing critical paths in a design

- Dedicated carry chain that implements arithmetic functions such as fast adders, counters, and comparators (automatically used by software tools and megafunctions)

- FastLUT<sup>TM</sup> connection allowing high speed direct connection between LEs in the same logic array block (LAB)

- Leap lines allowing a single LAB to directly drive LEs in adjacent rows

- The RapidLAB interconnect providing a high-speed connection to a 10-LAB-wide region

- Dedicated clock and control signal resources, including four dedicated clocks, six dedicated fast global signals, and additional row-global signals

4 Dedicated Clocks

Figure 4. Receiver & Transmitter Diagrams for CDR Mode Notes (1), (2)

The RapidLAB interconnect provides a specialized high-speed structure to allow a central LAB to drive other LABs within a 10-LAB-wide region. The RapidLAB lines drive alternating local LAB interconnect regions, allowing communication to all LABs in the 10-LAB-wide region. Even numbered LEs in a LAB directly drive a RapidLAB line that drives one set of alternating local interconnect regions, while odd-numbered LEs drive a RapidLAB line that drives the opposite set of alternating local interconnect regions. Figure 14 shows RapidLAB interconnect connections. This 10-LAB wide region of the RapidLAB interconnect is repeated for every LAB in the row. The region covered by the RapidLAB interconnect is smaller than 10 for source LABs that are four or five LABs in from either edge of the LAB row. The RapidLAB row interconnect is used for LAB-to-LAB routing; it is only used by I/O bands or ESBs indirectly through other interconnects. The RapidLAB interconnect drives an LE directly when that LE is in multiplier mode.

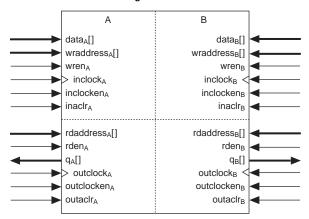

Figure 17. ESB Quad-Port Block Diagram

In addition to quad port memory, the ESB also supports true dual-port, dual-port, and single-port RAM. True dual-port RAM supports any combination of two port operations: two reads, two writes, or one read and one write. Dual-port memory supports a simultaneous read and write. For single-port memory, independent read and write is supported. Figure 18 shows these different RAM memory port configurations for an ESB.

ESBs can implement synchronous RAM, which is easier to use than asynchronous RAM. A circuit using asynchronous RAM must generate the RAM write enable (WE) signal while ensuring that its data and address signals meet setup and hold time specifications relative to the WE signal. In contrast, the ESB's synchronous RAM generates its own WE signal and is self-timed with respect to the global clock. Circuits using the ESB's self-timed RAM must only meet the setup and hold time specifications relative to the global clock.

ESBs are grouped together in rows at the top and bottom of the device for fast horizontal communication. The ESB row interconnect can be driven by any ESB in the row. The row interconnect drives the ESB local interconnect, which in turn drives the ESB ports. ESB outputs drive the ESB local interconnect, which can drive row interconnect as well as all types of column interconnect, including leap lines. The leap lines allow fast access between ESBs and the adjacent LAB row.

When implementing memory, each ESB can be configured in any of the following sizes for quad port and true dual-port memory modes:  $256 \times 16$ ;  $512 \times 8$ ;  $1,024 \times 4$ ;  $2,048 \times 2$ ; or  $4,096 \times 1$ . For dual-port and single-port modes, the ESB can be configured for  $128 \times 32$  in addition to the list above. For variable port width RAMs, any port width ratio combination must be 1, 2, 4, 8, or 16. For example, a RAM with data ports of width 1 and 16 or 2 and 32 will work, but not 1 and 32.

The ESB can also be split in half and used for two independent 2,048-bit single-port or dual-port RAM blocks. For example, one half of the ESB can be used as a  $128 \times 16$  memory single-port memory while the other half can be used for a  $1,024 \times 2$  dual-port memory. This effectively doubles the number of RAMs a Mercury device can implement for its given number of ESBs. The Quartus II software automatically merges two logical memory functions in a design into an ESB; the designer does not need to merge the functions manually.

By combining multiple ESBs, the Quartus II software implements larger memory blocks automatically. For example, two  $256 \times 16$  RAM blocks can be combined to form a  $256 \times 32$  RAM block, and two  $512 \times 8$  RAM blocks can be combined to form a  $512 \times 16$  RAM block. Memory performance does not degrade for memory blocks up to 4,096 words deep. Each ESB can implement a 4,096-word-deep memory; the ESBs are used in parallel, eliminating the need for any external control logic and its associated delays. To create a high-speed memory block more than 4,096 words deep, the Quartus II software will automatically combine ESBs with LE control logic.

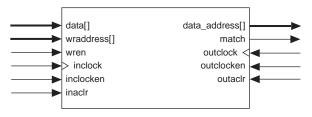

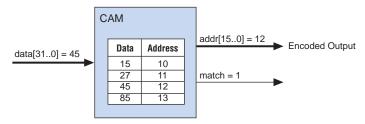

CAM is used for high-speed search operations. When searching for data within a RAM block, the search is performed serially. Thus, finding a particular data word can take many cycles. CAM searches all addresses in parallel and outputs the address storing a particular word. When a match is found, a match flag is set high. CAM is ideally suited for applications such as Ethernet address lookup, data compression, pattern recognition, cache tags, fast routing table lookup, and high-bandwidth address filtering. Figure 22 shows the CAM block diagram.

Figure 22. CAM Block Diagram

The Mercury on-chip CAM provides faster system performance than traditional discrete CAM. Integrating CAM and logic into the Mercury device eliminates off-chip and on-chip delays, improving system performance.

When in CAM mode, the ESB implements a 32-word, 32-bit CAM. Wider or deeper CAM, such as a 32-word, 64-bit or 128-word, 32-bit block, can be implemented by combining multiple CAM blocks with some ancillary logic implemented in LEs. The Quartus II software automatically combines ESBs and LEs to create larger CAM blocks.

CAM supports writing "don't care" bits into words of the memory. The don't-care bit can be used as a mask for CAM comparisons; any bit set to don't-care has no effect on matches.

CAM can generate outputs in three different modes: single-match mode, multiple-match mode, and fast multiple-match mode. In each mode, the ESB outputs the matched data's location as an encoded or unencoded address. When encoded, the ESB outputs an encoded address of the data's location. For instance, if the data is located in address 12, the ESB output is 12. When unencoded, each ESB port uses its 16 outputs to show the location of the data over two clock cycles. In this case, if the data is located in address 12, the 12th output line goes high. Figures 22 and 23 show the encoded CAM outputs and unencoded CAM outputs, respectively.

Figure 23. Encoded CAM Address Outputs

Figure 24. Unencoded CAM Address Outputs

#### Notes to Figure 24:

- (1) For an unencoded output, the ESB only supports 31 input data bits. One input bit is used by the select line to choose one of the two banks of 16 outputs.

- (2) If the select input is a 1, then CAM outputs odd words between 1 through 15. If the select input is a 0, CAM outputs words even words between 0 through 14.

In single-match mode, it takes two clock cycles to write into CAM, but only one clock cycle to read from CAM. In this mode, both encoded and unencoded outputs are available without external logic. Single-match mode is better suited for designs without duplicate data in the memory.

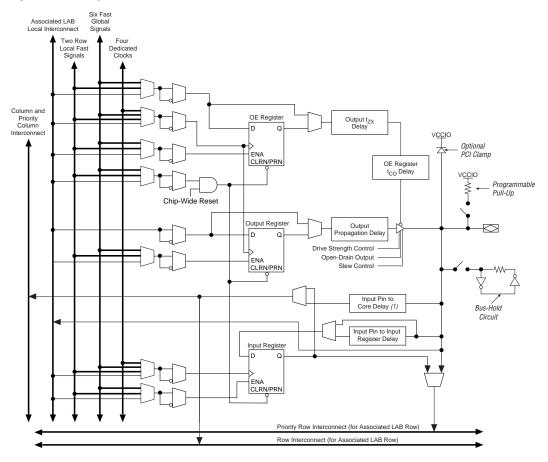

The Mercury IOE includes programmable delays that can be activated to ensure zero hold times, minimum clock-to-output times, input IOE register-to-core register transfers, or core-to-output IOE register transfers. A path in which a pin directly drives a register may require the delay to ensure zero hold time, whereas a path in which a pin drives a register through combinatorial logic may not require the delay. Programmable delays exist for decreasing input pin to core and IOE input register delays. The Quartus II Compiler can program these delays automatically to minimize setup time while providing a zero hold time. Delays are also programmable for increasing the register to pin delays for output and/or output enable registers. A programmable delay exists for increasing the  $t_{\rm ZX}$  delay to the output pin, which is required for ZBT interfaces. Table 10 shows the programmable delays for Mercury devices.

| Table 10. Mercury Programmable Delay Chain   |                                              |  |  |  |  |  |  |

|----------------------------------------------|----------------------------------------------|--|--|--|--|--|--|

| Programmable Delays                          | Quartus II Logic Option                      |  |  |  |  |  |  |

| Input pin to core delay (1)                  | Decrease input delay to internal cells       |  |  |  |  |  |  |

| Input pin to input register delay            | Decrease input delay to input register       |  |  |  |  |  |  |

| Output propagation delay                     | Increase delay to output pin                 |  |  |  |  |  |  |

| Output enable register t <sub>CO</sub> delay | Increase delay to OE pin                     |  |  |  |  |  |  |

| Output t <sub>ZX</sub> delay                 | Increase t <sub>ZX</sub> delay to output pin |  |  |  |  |  |  |

#### Note to Table 10:

(1) This delay has four settings: off and three levels of delay.

The IOE registers in Mercury devices share the same source for clear or preset. Use of the preset/clear is programmable for each individual IOE. The register(s) can be programmed to power up high or low after configuration is complete. If programmed to power up low, an asynchronous clear can control the register(s). If programmed to power up high, an asynchronous preset can control the register(s). This feature prevents the inadvertent activation of another device's active-low input upon power-up. Figure 26 shows the IOE for Mercury devices.

Figure 26. Mercury IOE

Note to Figure 26:

(1) This programmable delay has four settings: off and three levels of delay.

## Double Data Rate I/O

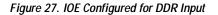

Mercury device's have three register IOEs to support the DDRIO feature, which makes double data rate interfaces possible by clocking data on both positive and negative clock edges. The IOE in Mercury devices supports double data rate input and double data rate output modes.

In Mercury device IOEs, the OE register is a multi-purpose register available as a second input or output register. When using the IOE for double data rate inputs, the input register and OE register are automatically configured as input registers to clock input double rate data on alternating edges. An input latch is also used within the IOE for DDR input acquisition. The latch holds the data that is present during the clock high times, driving it to the OE register. This allows the OE register and input register to clock both bits of data into LEs, synchronous to the same clock edge (either rising or falling). Figure 27 shows an IOE configured for DDR input.

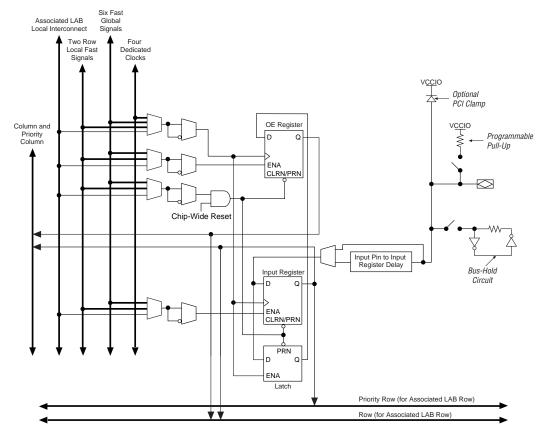

Figure 30. I/O Bank Layout

#### **Notes to Figure 30:**

- (1) If HSDI I/O channels are not used, the HSDI banks can be used as regular I/O banks.

- (2) When used as regular I/O banks, these banks must be set to the same V<sub>CCIO</sub> level, but can have separate V<sub>REF</sub> bank settings.

For more information on I/O standards, see *Application Note 117 (Using Selectable I/O Standards in Altera Devices)*.

## MultiVolt I/O Interface

The Mercury architecture supports the MultiVolt I/O interface feature, which allows Mercury devices in all packages to interface with devices with different supply voltages. The devices have one set of VCC pins for internal operation and input buffers (VCCINT), and another set for I/O output drivers (VCCIO).

Normal Mode: The external clock output pin will have phase delay relative to the clock input pin. If an internal clock is used in this mode, the IOE register clock will be phase aligned to the input clock pin. Multiplication is allowed with the normal mode.

# Advanced ClockShift Circuitry

General purpose PLLs in Mercury devices have advanced ClockShift<sup>TM</sup> circuitry that provides programmable phase shift and fine tune time delay shift. For phase shifting, users can enter a phase shift (in degrees or time units) that affects all PLL outputs. Phase shifts of 90, 180, and 270 can be implemented exactly. Other values of phase shifting, or delay shifting in time units, are allowed with a resolution range of 0.3 ns to 1.0 ns. This resolution varies with frequency input and the user-entered multiplication and division factors. The phase shift ability is only possible on a multiplied or divided clock if the input and output frequency have an integer multiple relationship (i.e.,  $f_{\rm IN}/f_{\rm OUT}$  or  $f_{\rm OUT}/f_{\rm IN}$  must be an integer).

In addition to the phase shift feature that affects all outputs, there is an advanced fine time delay shift control on each of the four PLL outputs. Each PLL output can be shifted in 250-ps increments for a range of –2.0 ns to +2.0 ns. This ability can be used in conjunction with the phase shifting ability that affects all outputs.  $f_{\rm IN}/f_{\rm OUT}$  does not need to have an integer relationship for the advanced fine time delay shift control.

# Clock Enable Signal

Mercury PLLs have a CLKLK\_ENA pin for enabling/disabling all of the device PLLs. When the CLKLK\_ENA pin is high, the PLL drives a clock to all its output ports. When the CLKLK\_ENA pin is low, the clock0, clock1, clock2 and extclock ports are driven by GND and all of the PLLs go out of lock. When the CLKLK\_ENA pin goes high again, the PLL must relock.

The individual enable port for each general purpose PLL is programmable. If more than one general-purpose PLL is instantiated, each one does not have to use the clock enable. To enable/disable the device PLLs with the CLKLK\_ENA pin, the inclocken port on the altclklock instance must be connected to the CLKLK\_ENA input pin.

| Table 23. LVTTL Specifications Note (10) |                           |                                            |         |         |       |  |  |  |  |  |

|------------------------------------------|---------------------------|--------------------------------------------|---------|---------|-------|--|--|--|--|--|

| Symbol                                   | Parameter                 | Conditions                                 | Minimum | Maximum | Units |  |  |  |  |  |

| V <sub>CCIO</sub>                        | Output supply voltage     |                                            | 3.0     | 3.6     | V     |  |  |  |  |  |

| V <sub>IH</sub>                          | High-level input voltage  |                                            | 1.7     | 4.1     | V     |  |  |  |  |  |

| $V_{IL}$                                 | Low-level input voltage   |                                            | -0.5    | 0.7     | V     |  |  |  |  |  |

| I                                        | Input pin leakage current | V <sub>IN</sub> = 0 V or V <sub>CCIO</sub> | -10     | 10      | μΑ    |  |  |  |  |  |

| V <sub>OH</sub>                          | High-level output voltage | $I_{OH} = -4 \text{ mA}$                   | 2.4     |         | V     |  |  |  |  |  |

| V <sub>OL</sub>                          | Low-level output voltage  | I <sub>OL</sub> = 4 mA                     |         | 0.45    | V     |  |  |  |  |  |

| Table 24. LVCMOS Specifications |                            |                                                      |                         |         |       |  |  |  |  |

|---------------------------------|----------------------------|------------------------------------------------------|-------------------------|---------|-------|--|--|--|--|

| Symbol                          | Parameter                  | Conditions                                           | Minimum                 | Maximum | Units |  |  |  |  |

| V <sub>CCIO</sub>               | Power supply voltage range |                                                      | 3.0                     | 3.6     | V     |  |  |  |  |

| $V_{IH}$                        | High-level input voltage   |                                                      | 1.7                     | 4.1     | V     |  |  |  |  |

| $V_{IL}$                        | Low-level input voltage    |                                                      | -0.5                    | 0.7     | V     |  |  |  |  |

| I                               | Input pin leakage current  | V <sub>IN</sub> = 0 V or V <sub>CCIO</sub>           | -10                     | 10      | μΑ    |  |  |  |  |

| V <sub>OH</sub>                 | High-level output voltage  | $V_{CCIO} = 3.0,$<br>$I_{OH} = -0.1 \text{ mA}$      | V <sub>CCIO</sub> - 0.2 |         | V     |  |  |  |  |

| V <sub>OL</sub>                 | Low-level output voltage   | V <sub>CCIO</sub> = 3.0,<br>I <sub>OL</sub> = 0.1 mA |                         | 0.2     | V     |  |  |  |  |

| Table 25. 2.5-V I/O Specifications Note (10) |                           |                                     |         |         |       |  |  |  |  |

|----------------------------------------------|---------------------------|-------------------------------------|---------|---------|-------|--|--|--|--|

| Symbol                                       | Parameter                 | Conditions                          | Minimum | Maximum | Units |  |  |  |  |

| V <sub>CCIO</sub>                            | Output supply voltage     |                                     | 2.375   | 2.625   | V     |  |  |  |  |

| $V_{IH}$                                     | High-level input voltage  |                                     | 1.7     | 4.1     | V     |  |  |  |  |

| $V_{IL}$                                     | Low-level input voltage   |                                     | -0.5    | 0.7     | V     |  |  |  |  |

| I <sub>I</sub>                               | Input pin leakage current | $V_{IN} = 0 \text{ V or } V_{CCIO}$ | 10      | 10      | μΑ    |  |  |  |  |

| $V_{OH}$                                     | High-level output voltage | $I_{OH} = -0.1 \text{ mA}$          | 2.1     |         | V     |  |  |  |  |

|                                              |                           | $I_{OH} = -1 \text{ mA}$            | 2.0     |         | V     |  |  |  |  |

|                                              |                           | $I_{OH} = -2 \text{ mA}$            | 1.7     |         | V     |  |  |  |  |

| $V_{OL}$                                     | Low-level output voltage  | $I_{OL} = 0.1 \text{ mA}$           |         | 0.2     | V     |  |  |  |  |

|                                              |                           | $I_{OH} = 1 \text{ mA}$             |         | 0.4     | V     |  |  |  |  |

|                                              |                           | $I_{OH} = 2 \text{ mA}$             |         | 0.7     | V     |  |  |  |  |

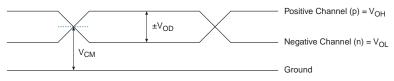

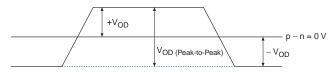

Figure 35. Transmitter Output Waveforms for Differential I/O Standards

#### Single-Ended Waveform

#### **Differential Waveform**

| Table 27. 3.3-V LVDS I/O Specifications |                                                                    |                         |         |         |         |       |  |  |  |

|-----------------------------------------|--------------------------------------------------------------------|-------------------------|---------|---------|---------|-------|--|--|--|

| Symbol                                  | Parameter                                                          | Conditions              | Minimum | Typical | Maximum | Units |  |  |  |

| V <sub>CCIO</sub>                       | I/O supply voltage                                                 |                         | 3.135   | 3.3     | 3.465   | V     |  |  |  |

| $V_{OD}$                                | Differential output voltage                                        | $R_L = 100 \Omega$      | 250     | 510     | 600     | mV    |  |  |  |

| ΔV <sub>OD</sub>                        | Change in V <sub>OD</sub> between high and low                     | R <sub>L</sub> = 100 Ω  |         |         | 50      | mV    |  |  |  |

| Vos                                     | Output offset voltage                                              | $R_L = 100 \Omega$      | 1.125   | 1.25    | 1.375   | V     |  |  |  |

| ΔV <sub>OS</sub>                        | Change in V <sub>OS</sub> between high and low                     | R <sub>L</sub> = 100 Ω  |         |         | 50      | mV    |  |  |  |

| $V_{TH}$                                | Differential input threshold                                       | V <sub>CM</sub> = 1.2 V | -100    |         | 100     | mV    |  |  |  |

| V <sub>IN</sub>                         | Receiver input voltage range                                       |                         | 0.0     |         | 2.4     | V     |  |  |  |

| R <sub>L</sub>                          | Receiver differential input resistor (external to Mercury devices) |                         | 90      | 100     | 110     | Ω     |  |  |  |

| Table 33. SSTL-2 Class I Specifications Note (10) |                           |                            |                         |                  |                         |       |  |  |

|---------------------------------------------------|---------------------------|----------------------------|-------------------------|------------------|-------------------------|-------|--|--|

| Symbol                                            | Parameter                 | Conditions                 | Minimum                 | Typical          | Maximum                 | Units |  |  |

| V <sub>CCIO</sub>                                 | I/O supply voltage        |                            | 2.375                   | 2.5              | 2.625                   | V     |  |  |

| V <sub>TT</sub>                                   | Termination voltage       |                            | V <sub>REF</sub> - 0.04 | V <sub>REF</sub> | V <sub>REF</sub> + 0.04 | V     |  |  |

| $V_{REF}$                                         | Reference voltage         |                            | 1.15                    | 1.25             | 1.35                    | V     |  |  |

| V <sub>IH</sub>                                   | High-level input voltage  |                            | V <sub>REF</sub> + 0.18 |                  | 3.0                     | V     |  |  |

| V <sub>IL</sub>                                   | Low-level input voltage   |                            | -0.3                    |                  | V <sub>REF</sub> – 0.18 | V     |  |  |

| V <sub>OH</sub>                                   | High-level output voltage | $I_{OH} = -7.6 \text{ mA}$ | V <sub>TT</sub> + 0.57  |                  |                         | V     |  |  |

| V <sub>OL</sub>                                   | Low-level output voltage  | I <sub>OL</sub> = 7.6 mA   |                         |                  | V <sub>TT</sub> – 0.57  | V     |  |  |

| Table 34. S       | Table 34. SSTL-2 Class II Specifications Note (10) |                             |                         |           |                         |       |  |  |  |

|-------------------|----------------------------------------------------|-----------------------------|-------------------------|-----------|-------------------------|-------|--|--|--|

| Symbol            | Parameter                                          | Conditions                  | Minimum                 | Typical   | Maximum                 | Units |  |  |  |

| V <sub>CCIO</sub> | I/O supply voltage                                 |                             | 2.3                     | 2.5       | 2.7                     | V     |  |  |  |

| $V_{TT}$          | Termination voltage                                |                             | V <sub>REF</sub> – 0.04 | $V_{REF}$ | V <sub>REF</sub> + 0.04 | V     |  |  |  |

| $V_{REF}$         | Reference voltage                                  |                             | 1.15                    | 1.25      | 1.35                    | V     |  |  |  |

| $V_{IH}$          | High-level input voltage                           |                             | V <sub>REF</sub> + 0.18 |           | $V_{CCIO} + 0.3$        | V     |  |  |  |

| $V_{IL}$          | Low-level input voltage                            |                             | -0.3                    |           | V <sub>REF</sub> – 0.18 | V     |  |  |  |

| V <sub>OH</sub>   | High-level output voltage                          | $I_{OH} = -15.2 \text{ mA}$ | V <sub>TT</sub> + 0.76  |           |                         | V     |  |  |  |

| V <sub>OL</sub>   | Low-level output voltage                           | I <sub>OL</sub> = 15.2 mA   |                         |           | V <sub>TT</sub> – 0.76  | V     |  |  |  |

| Table 35. SSTL-3 Class I Specifications Note (10) |                           |                          |                         |           |                         |       |  |  |

|---------------------------------------------------|---------------------------|--------------------------|-------------------------|-----------|-------------------------|-------|--|--|

| Symbol                                            | Parameter                 | Conditions               | Minimum                 | Typical   | Maximum                 | Units |  |  |

| V <sub>CCIO</sub>                                 | I/O supply voltage        |                          | 3.0                     | 3.3       | 3.6                     | V     |  |  |

| $V_{TT}$                                          | Termination voltage       |                          | V <sub>REF</sub> – 0.05 | $V_{REF}$ | V <sub>REF</sub> + 0.05 | V     |  |  |

| $V_{REF}$                                         | Reference voltage         |                          | 1.3                     | 1.5       | 1.7                     | V     |  |  |

| $V_{IH}$                                          | High-level input voltage  |                          | V <sub>REF</sub> + 0.2  |           | $V_{CCIO} + 0.3$        | V     |  |  |

| V <sub>IL</sub>                                   | Low-level input voltage   |                          | -0.3                    |           | V <sub>REF</sub> - 0.2  | V     |  |  |

| V <sub>OH</sub>                                   | High-level output voltage | $I_{OH} = -8 \text{ mA}$ | V <sub>TT</sub> + 0.6   |           |                         | V     |  |  |

| $V_{OL}$                                          | Low-level output voltage  | $I_{OL} = 8 \text{ mA}$  |                         |           | V <sub>TT</sub> – 0.6   | V     |  |  |

| Table 39. 1.5-V HSTL Class I Specifications Note (10) |                             |                          |                         |         |                        |       |  |  |  |

|-------------------------------------------------------|-----------------------------|--------------------------|-------------------------|---------|------------------------|-------|--|--|--|

| Symbol                                                | Parameter                   | Conditions               | Minimum                 | Typical | Maximum                | Units |  |  |  |

| V <sub>CCIO</sub>                                     | I/O supply voltage          |                          | 1.4                     | 1.5     | 1.6                    | V     |  |  |  |

| $V_{REF}$                                             | Input reference voltage     |                          | 0.68                    | 0.75    | 0.9                    | V     |  |  |  |

| V <sub>TT</sub>                                       | Termination voltage         |                          | 0.7                     | 0.75    | 0.8                    | V     |  |  |  |

| V <sub>IH</sub> (DC)                                  | DC high-level input voltage |                          | V <sub>REF</sub> + 0.1  |         |                        | V     |  |  |  |

| V <sub>IL</sub> (DC)                                  | DC low-level input voltage  |                          | -0.3                    |         | V <sub>REF</sub> – 0.1 | V     |  |  |  |

| V <sub>IH</sub> (AC)                                  | AC high-level input voltage |                          | V <sub>REF</sub> + 0.2  |         |                        | V     |  |  |  |

| V <sub>IL</sub> (AC)                                  | AC low-level input voltage  |                          |                         |         | V <sub>REF</sub> - 0.2 | V     |  |  |  |

| V <sub>OH</sub>                                       | High-level output voltage   | I <sub>OH</sub> = 8 mA   | V <sub>CCIO</sub> - 0.4 |         |                        | V     |  |  |  |

| V <sub>OL</sub>                                       | Low-level output voltage    | $I_{OH} = -8 \text{ mA}$ |                         |         | 0.4                    | V     |  |  |  |

| Table 40. 1.5-V HSTL Class II Specifications Note (10) |                             |                           |                         |         |                        |       |  |  |

|--------------------------------------------------------|-----------------------------|---------------------------|-------------------------|---------|------------------------|-------|--|--|

| Symbol                                                 | Parameter                   | Conditions                | Minimum                 | Typical | Maximum                | Units |  |  |

| V <sub>CCIO</sub>                                      | I/O supply voltage          |                           | 1.4                     | 1.5     | 1.6                    | V     |  |  |

| $V_{REF}$                                              | Input reference voltage     |                           | 0.68                    | 0.75    | 0.9                    | V     |  |  |

| $V_{TT}$                                               | Termination voltage         |                           | 0.7                     | 0.75    | 0.8                    | V     |  |  |

| V <sub>IH</sub> (DC)                                   | DC high-level input voltage |                           | V <sub>REF</sub> + 0.1  |         |                        | V     |  |  |

| V <sub>IL</sub> (DC)                                   | DC low-level input voltage  |                           | -0.3                    |         | V <sub>REF</sub> - 0.1 | V     |  |  |

| V <sub>IH</sub> (AC)                                   | AC high-level input voltage |                           | V <sub>REF</sub> + 0.2  |         |                        | V     |  |  |

| V <sub>IL</sub> (AC)                                   | AC low-level input voltage  |                           |                         |         | V <sub>REF</sub> - 0.2 | V     |  |  |

| V <sub>OH</sub>                                        | High-level output voltage   | I <sub>OH</sub> = 16 mA   | V <sub>CCIO</sub> - 0.4 |         |                        | V     |  |  |

| V <sub>OL</sub>                                        | Low-level output voltage    | $I_{OH} = -16 \text{ mA}$ |                         |         | 0.4                    | V     |  |  |

| Table 41. CTT I/O Specifications  |                                                |                                               |                        |         |                        |       |  |  |  |

|-----------------------------------|------------------------------------------------|-----------------------------------------------|------------------------|---------|------------------------|-------|--|--|--|

| Symbol                            | Parameter                                      | Conditions                                    | Minimum                | Typical | Maximum                | Units |  |  |  |

| V <sub>CCIO</sub>                 | I/O supply voltage                             |                                               | 3.0                    | 3.3     | 3.6                    | V     |  |  |  |

| V <sub>TT</sub> /V <sub>REF</sub> | Termination and input reference voltage        |                                               | 1.35                   | 1.5     | 1.65                   | V     |  |  |  |

| $V_{IH}$                          | High-level input voltage                       |                                               | V <sub>REF</sub> + 0.2 |         |                        | V     |  |  |  |

| $V_{IL}$                          | Low-level input voltage                        |                                               |                        |         | V <sub>REF</sub> - 0.2 | V     |  |  |  |

| I <sub>I</sub>                    | Input pin leakage current                      | 0 < V <sub>IN</sub> < V <sub>CCIO</sub>       |                        |         | ±10                    | μΑ    |  |  |  |

| V <sub>OH</sub>                   | High-level output voltage                      | $I_{OH} = -8 \text{ mA}$                      | V <sub>REF</sub> + 0.4 |         |                        | V     |  |  |  |

| V <sub>OL</sub>                   | Low-level output voltage                       | I <sub>OL</sub> = 8 mA                        |                        |         | V <sub>REF</sub> - 0.4 | V     |  |  |  |

| I <sub>O</sub>                    | Output leakage current (when output is high Z) | GND ở V <sub>OUT</sub> ở<br>V <sub>CCIO</sub> |                        |         | ±10                    | μΑ    |  |  |  |

Tables 44 and 45 describe the Mercury device's external timing parameters.

| Table 44. Mercury External Timing Parameters Notes (1), (2) |                                                             |            |  |  |  |  |

|-------------------------------------------------------------|-------------------------------------------------------------|------------|--|--|--|--|

| Symbol                                                      | Parameter                                                   | Conditions |  |  |  |  |

| t <sub>INSU</sub>                                           | Setup time with global clock at IOE register                |            |  |  |  |  |

| t <sub>INH</sub>                                            | Hold time with global clock at IOE register                 |            |  |  |  |  |

| t <sub>оитсо</sub>                                          | Clock-to-output delay with global clock at IOE register     | C1 = 35 pF |  |  |  |  |

| t <sub>INSUPLL</sub>                                        | Setup time with PLL clock at IOE input register             |            |  |  |  |  |

| t <sub>INHPLL</sub>                                         | Hold time with PLL clock at IOE input register              |            |  |  |  |  |

| t <sub>OUTCOPLL</sub>                                       | Clock-to-output delay with PLL clock at IOE output register | C1 = 35 pF |  |  |  |  |

| Table 45. Mercury External Bidirectional Timing Parameters Notes (1), (2) |                                                                                       |            |  |  |  |  |

|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------|--|--|--|--|

| Symbol                                                                    | Parameter                                                                             | Conditions |  |  |  |  |

| t <sub>INSUBIDIR</sub>                                                    | Setup time for bidirectional pins with gobal clock at IOE input register              |            |  |  |  |  |

| t <sub>INHBIDIR</sub>                                                     | Hold time for bidirectional pins with global clock at IOE input register              |            |  |  |  |  |

| toutcobidir                                                               | Clock-to-output delay for bidirectional pins with global clock at IOE output register | C1 = 35 pF |  |  |  |  |

| t <sub>XZBIDIR</sub>                                                      | Synchronous IOE output enable register to output buffer disable delay                 | C1 = 35 pF |  |  |  |  |

| t <sub>ZXBIDIR</sub>                                                      | Synchronous IOE output enable register output buffer enable delay                     | C1 = 35 pF |  |  |  |  |

| t <sub>INSUBIDIRPLL</sub>                                                 | Setup time for bidirectional pins with PLL clock at IOE input register                |            |  |  |  |  |

| t <sub>INHBIDIRPLL</sub>                                                  | Hold time for bidirectional pins with PLL clock at IOE input register                 |            |  |  |  |  |

| toutcobidirpll                                                            | Clock-to-output delay for bidirectional pins with PLL clock at IOE output register    | C1 = 35 pF |  |  |  |  |

| <sup>t</sup> XZBIDIRPLL                                                   | Synchronous IOE output enable register to output buffer disable delay with PLL        | C1 = 35 pF |  |  |  |  |

| t <sub>ZXBIDIRPLL</sub>                                                   | Synchronous IOE output enable register output buffer enable delay with PLL            | C1 = 35 pF |  |  |  |  |

## Notes to Tables 44 and 45:

- (1) These timing parameters are sample-tested only.

- (2) All timing parameters are either to and/or from pins, including global clock pins.

Tables 46 through 51 show external timing parameters for Mercury devices.

| Table 46. EP1M120 External Timing Parameters Note (1) |                |      |                |      |                |      |      |  |

|-------------------------------------------------------|----------------|------|----------------|------|----------------|------|------|--|

| Symbol                                                | -5 Speed Grade |      | -6 Speed Grade |      | -7 Speed Grade |      | Unit |  |

|                                                       | Min            | Max  | Min            | Max  | Min            | Max  |      |  |

| t <sub>INSU</sub>                                     | 0.67           |      | 0.70           |      | 0.73           |      | ns   |  |

| t <sub>INH</sub>                                      | 0.00           |      | 0.00           |      | 0.00           |      | ns   |  |

| tоитсо                                                | 2.00           | 3.30 | 2.00           | 3.32 | 2.00           | 3.49 | ns   |  |

| t <sub>INSUPLL</sub>                                  | 0.59           |      | 0.64           |      | 0.62           |      | ns   |  |

| t <sub>INHPLL</sub>                                   | 0.00           |      | 0.00           |      | 0.00           |      | ns   |  |

| tOUTCOPLL                                             | 0.50           | 2.08 | 0.50           | 2.08 | 0.50           | 2.15 | ns   |  |

| Symbol                      | -5 Speed Grade |      | -6 Speed Grade |      | -7 Speed Grade |      | Unit |

|-----------------------------|----------------|------|----------------|------|----------------|------|------|

|                             | Min            | Max  | Min            | Max  | Min            | Max  | 7    |

| t <sub>INSUBIDIR</sub>      | 0.67           |      | 0.70           |      | 0.73           |      | ns   |

| t <sub>INHBIDIR</sub>       | 0.00           |      | 0.00           |      | 0.00           |      | ns   |

| t <sub>OUTCOBIDIR</sub>     | 2.00           | 3.30 | 2.00           | 3.32 | 2.00           | 3.49 | ns   |

| t <sub>XZBIDIR</sub>        |                | 3.52 |                | 3.53 |                | 3.74 | ns   |

| t <sub>ZXBIDIR</sub> (2)    |                | 3.52 |                | 3.53 |                | 3.74 | ns   |

| t <sub>ZXBIDIR</sub> (3)    |                | 3.72 |                | 3.73 |                | 3.99 | ns   |

| t <sub>INSUBIDIRPLL</sub>   | 0.59           |      | 0.64           |      | 0.62           |      | ns   |

| t <sub>INHBIDIRPLL</sub>    | 0.00           |      | 0.00           |      | 0.00           |      | ns   |

| t <sub>OUTCOBIDIRPLL</sub>  | 0.50           | 2.08 | 0.50           | 2.08 | 0.50           | 2.15 | ns   |

| t <sub>XZBIDIRPLL</sub>     |                | 2.29 |                | 2.29 |                | 2.39 | ns   |

| t <sub>ZXBIDIRPLL</sub> (2) |                | 2.29 |                | 2.29 |                | 2.39 | ns   |

| t <sub>ZXBIDIRPLL</sub> (3) |                | 2.49 |                | 2.49 |                | 2.64 | ns   |

| Table 48. EP1M120 External Timing Parameters Note (1) |          |          |          |          |      |  |  |

|-------------------------------------------------------|----------|----------|----------|----------|------|--|--|

| Symbol                                                | -7A Spec | ed Grade | -8A Spee | ed Grade | Unit |  |  |

|                                                       | Min      | Max      | Min      | Max      |      |  |  |

| t <sub>INSU</sub>                                     | 0.74     |          | 0.79     |          | ns   |  |  |

| t <sub>INH</sub>                                      | 0.00     |          | 0.00     |          | ns   |  |  |

| tоитсо                                                | 2.00     | 3.50     | 2.00     | 4.10     | ns   |  |  |

| t <sub>INSUPLL</sub>                                  | 0.62     |          | 0.75     |          | ns   |  |  |

| t <sub>INHPLL</sub>                                   | 0.00     |          | 0.00     |          | ns   |  |  |

| toutcopll                                             | 0.50     | 2.15     | 0.50     | 2.43     | ns   |  |  |

| Table 49. EP1M              | 120 External Bidired | ctional Timing Param | eters Note (1) |      |    |

|-----------------------------|----------------------|----------------------|----------------|------|----|

| Symbol                      | -7A Spe              | eed Grade            | -8A Spe        | Unit |    |

|                             | Min                  | Max                  | Min            | Max  |    |

| t <sub>INSUBIDIR</sub>      | 0.74                 |                      | 0.79           |      | ns |

| t <sub>INHBIDIR</sub>       | 0.00                 |                      | 0.00           |      | ns |

| toutcobidir                 | 2.00                 | 3.50                 | 2.00           | 4.10 | ns |

| t <sub>XZBIDIR</sub>        |                      | 3.75                 |                | 4.30 | ns |

| t <sub>ZXBIDIR</sub> (2)    |                      | 3.75                 |                | 4.30 | ns |

| t <sub>ZXBIDIR</sub> (3)    |                      | 4.00                 |                | 4.58 | ns |

| tINSUBIDIRPLL               | 0.62                 |                      | 0.75           |      | ns |

| t <sub>INHBIDIRPLL</sub>    | 0.00                 |                      | 0.00           |      | ns |

| tOUTCOBIDIRPLL              | 0.50                 | 2.15                 | 0.50           | 2.43 | ns |

| t <sub>XZBIDIRPLL</sub>     |                      | 2.39                 |                | 2.67 | ns |

| t <sub>ZXBIDIRPLL</sub> (2) |                      | 2.39                 |                | 2.67 | ns |

| t <sub>ZXBIDIRPLL</sub> (3) |                      | 2.64                 |                | 2.95 | ns |

| Table 50. EP1M350 External Timing Parameters Note (1) |                |      |                |      |                |      |      |  |

|-------------------------------------------------------|----------------|------|----------------|------|----------------|------|------|--|

| Symbol                                                | -5 Speed Grade |      | -6 Speed Grade |      | -7 Speed Grade |      | Unit |  |

|                                                       | Min            | Max  | Min            | Max  | Min            | Max  |      |  |

| t <sub>INSU</sub>                                     | 0.60           |      | 0.57           |      | 0.71           |      | ns   |  |

| t <sub>INH</sub>                                      | 0.00           |      | 0.00           |      | 0.00           |      | ns   |  |

| t <sub>outco</sub>                                    | 2.00           | 3.95 | 2.00           | 3.97 | 2.00           | 4.75 | ns   |  |

| t <sub>INSUPLL</sub>                                  | 0.69           |      | 0.70           |      | 0.82           |      | ns   |  |

| t <sub>INHPLL</sub>                                   | 0.00           |      | 0.00           |      | 0.00           |      | ns   |  |

| tOUTCOPLL                                             | 0.50           | 2.23 | 0.50           | 2.23 | 0.50           | 2.69 | ns   |  |

101 Innovation Drive San Jose, CA 95134 (408) 544-7000 http://www.altera.com Applications Hotline: (800) 800-EPLD Customer Marketing: (408) 544-7104 Literature Services: lit\_req@altera.com

Copyright © 2003 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, mask work rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes

to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.