Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 1440                                                       |

| Number of Logic Elements/Cells | 14400                                                      |

| Total RAM Bits                 | 114688                                                     |

| Number of I/O                  | 486                                                        |

| Number of Gates                | 350000                                                     |

| Voltage - Supply               | 1.71V ~ 1.89V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 780-BBGA, FCBGA                                            |

| Supplier Device Package        | 780-FBGA (29x29)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1m350f780c7es |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Mercury devices provide four dedicated clock input pins and six dedicated fast I/O pins that globally drive register control inputs, including clocks. These signals ensure efficient distribution of high-speed, low-skew control signals. The control signals use dedicated routing channels to provide short delays and low skew. The dedicated fast signals can also be driven by internal logic, providing an ideal solution for a clock divider or internally generated asynchronous control signal with high fan-out. The dedicated clock and fast I/O pins on Mercury devices can also feed logic. Dedicated clocks can also be used with the Mercury general purpose PLLs for clock management.

Each I/O row band also provides two additional I/O pins that can drive two row-global signals. Row-global signals can drive register control inputs for the LAB row associated with that particular I/O row band.

# High-Speed Differential Interface

The top I/O or HSDI band in Mercury devices contains dedicated circuitry for supporting differential standards at speeds up to 1.25 Gbps. Mercury devices have dedicated differential buffers and circuitry to support LVDS, LVPECL, and 3.3-V PCML I/O standards. Two dedicated high-speed PLLs (separate from the general purpose PLLs) multiply reference clocks and drive high-speed differential serializer/deserializer channels. In addition, clock recovery units (CRUs) at each receiver channel enable CDR. EP1M120 devices support eight input channels, eight output channels, and two dedicated clock inputs for feeding the receiver and/or transmitter PLLs. EP1M350 devices support 18 input channels, 18 output channels, and two dedicated clock inputs.

Mercury devices have optional built-in 100- $\Omega$  termination resistors on HSDI differential receiver data pins and the <code>HSDI\_CLK1</code> and <code>HSDI\_CLK2</code> pins.

Designers can use the HSDI circuitry for the following applications:

- Gigabit Ethernet backplanes

- ATM, SONET

- RapidIO

- POS-PHY Level 4

- Fibre Channel

- SDTV

The HSDI band supports one of two possible modes:

- Source-synchronous mode

- Clock data recovery (CDR) mode

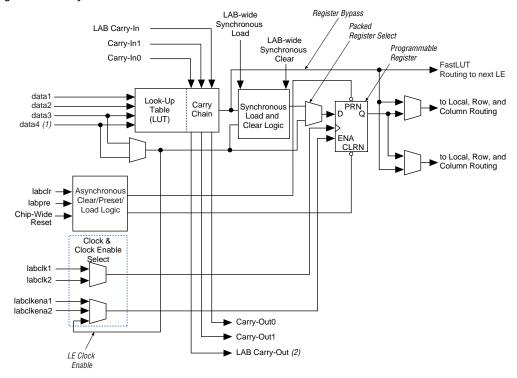

Figure 7. Mercury LE

#### Notes to Figure 7:

- FastLUT interconnect uses the data4 input.

- (2) LAB carry-out can only be generated by LE 4 and/or LE 10.

Each LE's programmable register can be configured for D, T, JK, or SR operation. The register's clock, clock enable, and clear control signals can be driven by global signals, general-purpose I/O pins, or any internal logic. For combinatorial functions, the register is bypassed and the output of the LUT drives directly to the outputs of the LE.

Each LE has four data inputs that can drive the internal LUT. One of these inputs has a shorter delay than the others, improving overall LE performance. This input is chosen automatically by the Quartus II software as appropriate.

The CSLA chain's speed advantage results from the parallel precomputation of carry chains. Instead of including every LUT in the critical path, only the propagation delays between LAB carry-in generation circuits (LE 4 and LE 10) make up the critical path. This feature allows the Mercury architecture to implement high-speed counters, adders, multipliers, parity functions, and comparators of arbitrary width.

Figure 10 shows the CSLA circuitry in a LAB for a 10-bit full adder. One portion of the LUT generates the sum of two bits using the input signals and the appropriate carry-in bit; the sum is routed to the output of the LE. The register can be bypassed for simple adders or used for accumulator functions. Another portion of the LUT generates carry-out bits. A labwide carry-in bit selects which chain is used for the addition of given inputs. The actual carry-in signal for that selected chain,  ${\tt carry-in0}$  or  ${\tt carry-in1}$ , selects the carry-out to carry forward, which is routed to the carry-in signal of the next-higher-order bit. The final carry-out signal is routed to an LE, where it is driven to local, row, or column interconnects.

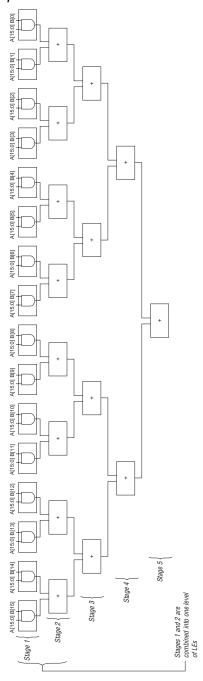

Figure 13. Mercury Binary Tree Implementation

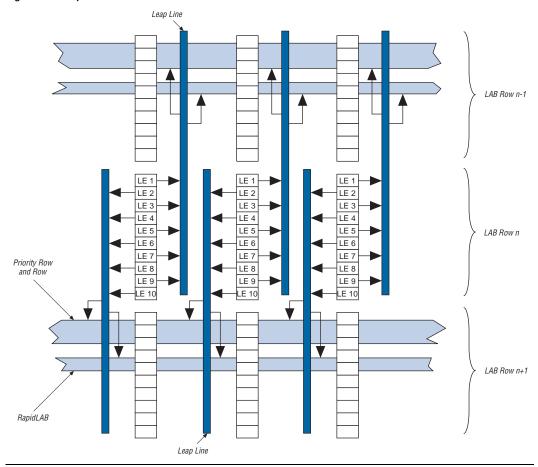

The RapidLAB interconnect provides a specialized high-speed structure to allow a central LAB to drive other LABs within a 10-LAB-wide region. The RapidLAB lines drive alternating local LAB interconnect regions, allowing communication to all LABs in the 10-LAB-wide region. Even numbered LEs in a LAB directly drive a RapidLAB line that drives one set of alternating local interconnect regions, while odd-numbered LEs drive a RapidLAB line that drives the opposite set of alternating local interconnect regions. Figure 14 shows RapidLAB interconnect connections. This 10-LAB wide region of the RapidLAB interconnect is repeated for every LAB in the row. The region covered by the RapidLAB interconnect is smaller than 10 for source LABs that are four or five LABs in from either edge of the LAB row. The RapidLAB row interconnect is used for LAB-to-LAB routing; it is only used by I/O bands or ESBs indirectly through other interconnects. The RapidLAB interconnect drives an LE directly when that LE is in multiplier mode.

RapidLAB interconnects driven by odd-numbered

LEs on drive out to the four LEs to the left and five

LES to the right through local interconnects.

LES and drive out to the four LEs to the left and five

LES to the right through local interconnects.

RapidLAB interconnects driven by even-numbered

LEs on the few out to the four LEs to the right and five

LEs to the left morphial interconnects.

Figure 14. RapidLAB Interconnect Connections

The column interconnect vertically routes signals to and from LABs, ESBs, and I/O bands. Each column of LABs is served by a dedicated column interconnect. These column resources include:

- Column interconnect traversing the entire device from top to bottom

- Priority column interconnect for high speed access across the device vertically

- Leap line interconnect for vertical routing between adjacent LAB rows and between adjacent ESP rows and LAB rows.

Leap lines are driven directly by LEs for fast access to adjacent row interconnects. LABs can drive a leap line to the row above and/or below (including ESB rows). The even-numbered LEs in a LAB drive leap lines down, while odd-numbered LEs drive leap lines up. This allows a single LAB to access row and RapidLAB interconnects within a three-row region. Figure 15 shows the leap line interconnect.

Figure 15. Leap Line Interconnect

# FastLUT Interconnect

Mercury devices include an enhanced interconnect structure within LABs for faster routing of LE output to LE input connections. The FastLUT connection allows the combinatorial output of an LE to directly drive the fast input of the LE directly below it, bypassing the local interconnect. This resource can be used as a high speed connection for wide fan-in functions from LE 1 to LE 10 in the same LAB. Figure 16 shows a FastLUT interconnect.

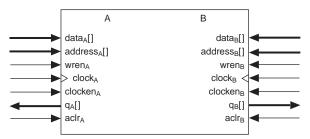

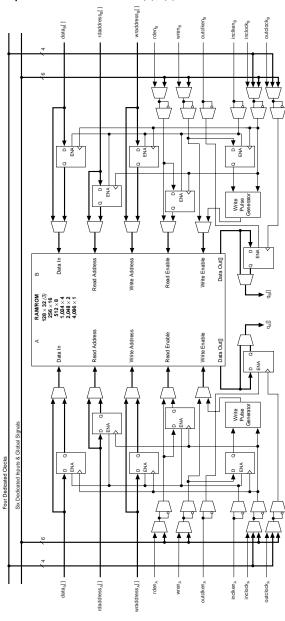

Figure 18. RAM Memory Port Configurations

#### **True Dual-Port Memory**

### **Dual-Port Memory** (1)

### Single-Port Memory (1)

### Note to Figure 18:

(1) Two dual- or single-port memory blocks can be implemented in a single ESB.

The ESB also allows variable width data ports for reading and writing to any of the RAM ports in any RAM configuration. For example, the ESB in quad port configuration can be written in  $\times 1$  mode at port A, read in  $\times 16$  from port A, written in  $\times 4$  mode at port B, and read in  $\times 2$  mode from port B.

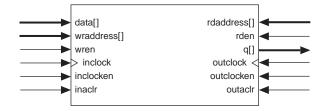

Figure 20. ESB in Input/Output Clock Mode Notes (1), (2)

### Notes to Figure 20:

- (1) Only half of the ESB, either A or B, is used for dual-port configuration.

- (2) All registers can be asynchronously cleared by ESB local interconnect signals, global signals, or the chip-wide reset.

(3) This configuration is supported for dual-port configuration.

Dedicated Clocks

Fast Global Signals

Local Interconnect

Local Interconnect

Local Interconnect

Local Interconnect

INCLOCKEN

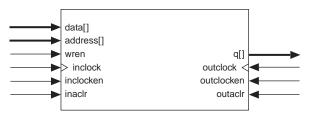

Figure 25. ESB Control Signal Generation

Interconnect

Interconnect

Local

The ESB can drive row interconnects within its own ESB row and can directly drive all the column interconnects: column, priority column, and leap lines.

OUTCLOCKEN

RDEN

WREN

**INCLR**

OUTCLR

OUTCLOCK

# Implementing Logic in ROM

**INCLOCK**

In addition to implementing RAM functions, the ESB can implement logic functions when it is programmed with a read-only pattern during configuration, creating a large LUT. With LUTs, combinatorial functions are implemented by looking up the results, rather than by computing them. This implementation of combinatorial functions can be faster than using algorithms implemented in general logic, a performance advantage further enhanced by the fast access times of ESBs. The large capacity of ESBs enables designers to implement complex functions in one logic level without the routing delays associated with linked LEs or distributed RAM blocks. Parameterized functions such as LPM functions can take advantage of the ESB automatically. Further, the Quartus II software can implement portions of a design with ESBs where appropriate.

When using the IOE for double data rate outputs, the output register and OE register are automatically configured to clock two data paths from LEs on rising clock edges. These register outputs are multiplexed by the clock to drive the output pin at a  $\times 2$  rate. The output register clocks the first bit out on the clock high time, while the OE register clocks the second bit out on the clock low time. Figure 28 shows the IOE configured for DDR output.

Six Fast Associated LAB Global Local Interconnect Signals Two Row Four Dedicated Local Fast Clocks Signals OE Register VCCIO Optional FΝΔ PCI Clamp CLRN/PRN Programmable Pull-Up Chip-Wide Reset Output Register Output D Propagation Delay Drive Strength Control Open-Drain Output ENA Slew Control Bus-Hold Circuit

Figure 28. IOE Configured for DDR Output

Bidirectional DDR on an I/O pin is possible by using the IOE for DDR output and using LEs to acquire the double data rate input. Bidirectional DDR I/O pins support double data rate synchronous DRAM (DDR SDRAM) at 166 MHz (334 Mbps), which transfer data on a double data rate bidirectional bus. QDR SRAMs are also supported with DDR I/O pins on separate read and write ports.

# Zero Bus Turnaround SRAM Interface Support

In addition to DDR SDRAM support, Mercury device I/O pins also support interfacing with ZBT SRAM blocks at up to 200 MHz. ZBT SRAM blocks are designed to eliminate dead bus cycles when turning a bidirectional bus around between reads and writes, or writes and reads. ZBT allows for 100% bus utilization because ZBT SRAM can read or write on every clock cycle.

To avoid bus contention, the output  $t_{ZX}$  delay ensures that the clock-to-low-impedance time ( $t_{ZX}$ ) is greater than the clock-to-high-impedance time ( $t_{XZ}$ ). Time delay control of clocks to the OE/output and input register, using a single general purpose PLL, enable the Mercury device to meet ZBT  $t_{CO}$  and  $t_{SU}$  times.

# **Programmable Drive Strength**

The output buffer for each Mercury device I/O pin has a programmable drive strength control for certain I/O standards. The LVTTL standard has several levels of drive strength that can be controlled by the user. SSTL-3 class I and II, SSTL-2 class I and II, HSTL class I and II, and 3.3-V GTL+ support a minimum or maximum setting. The minimum setting is the lowest drive strength that guarantees the  $\rm I_{OH}/\rm I_{OL}$  of the standard. The maximum setting provides higher drive strength that allows for faster switching and is the default setting. Using settings below the maximum provides signal slew-rate control to reduce system noise and signal overshoot. Table 11 shows the possible settings for the I/O standards with drive strength control.

Table 12 describes the I/O standards supported by Mercury devices.

| Table 12. Mercury Supporte | ed I/O Standards   |                                                          |                                                         |                                                           |

|----------------------------|--------------------|----------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------|

| I/O Standard               | Туре               | Input<br>Reference<br>Voltage (V <sub>REF</sub> )<br>(V) | Output<br>Supply<br>Voltage<br>(V <sub>CCIO</sub> ) (V) | Board<br>Termination<br>Voltage<br>(V <sub>TT</sub> ) (V) |

| LVTTL                      | Single-ended       | N/A                                                      | 3.3                                                     | N/A                                                       |

| LVCMOS                     | Single-ended       | N/A                                                      | 3.3                                                     | N/A                                                       |

| 2.5 V                      | Single-ended       | N/A                                                      | 2.5                                                     | N/A                                                       |

| 1.8 V                      | Single-ended       | N/A                                                      | 1.8                                                     | N/A                                                       |

| 3.3-V PCI                  | Single-ended       | N/A                                                      | 3.3                                                     | N/A                                                       |

| 3.3-V PCI-X                | Single-ended       | N/A                                                      | 3.3                                                     | N/A                                                       |

| LVDS                       | Differential       | N/A                                                      | 3.3                                                     | N/A                                                       |

| LVPECL                     | Differential       | N/A                                                      | 3.3                                                     | N/A                                                       |

| 3.3-V PCML                 | Differential       | N/A                                                      | 3.3                                                     | 3.3                                                       |

| GTL+                       | Voltage referenced | 1.0                                                      | N/A                                                     | 1.5                                                       |

| HSTL class I and II        | Voltage referenced | 0.75                                                     | 1.5                                                     | 0.75                                                      |

| SSTL-2 class I and II      | Voltage referenced | 1.25                                                     | 2.5                                                     | 1.25                                                      |

| SSTL-3 class I and II      | Voltage referenced | 1.5                                                      | 3.3                                                     | 1.5                                                       |

| AGP                        | Voltage referenced | 1.32                                                     | 3.3                                                     | N/A                                                       |

| CTT                        | Voltage referenced | 1.5                                                      | 3.3                                                     | 1.5                                                       |

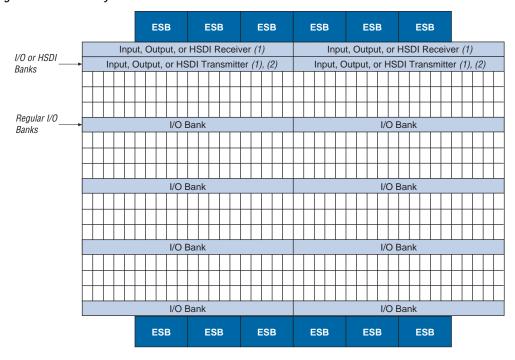

Each regular I/O band row contains two I/O banks. The number of I/O banks in a Mercury device depends on the number of I/O band rows. The top I/O band contains four regular I/O banks specifically designed for HSDI. The top I/O band banks and dedicated clock inputs support LVDS, LVPECL, and 3.3-V PCML. 3.3-V PCML is an open-drain standard and therefore requires external termination to 3.3 V. All other standards are supported by all I/O banks. The top I/O banks 1, 2, 3, and 4 only support non-HSDI I/O pins if the design does not use HSDI circuitry. If the design uses any HSDI channel, banks 1, 2, 3, and 4 all do not support regular I/O pins.

Additionally, the EP1M350 device includes the Flexible-LVDS feature, providing support for up to 100 LVDS channels on all regular I/O banks. Regular I/O banks in EP1M350 devices include dedicated LVDS input and output buffers that do not require any external components except for 100- $\Omega$  termination resistors on receiver channels.

Figure 30. I/O Bank Layout

#### Notes to Figure 30:

- (1) If HSDI I/O channels are not used, the HSDI banks can be used as regular I/O banks.

- (2) When used as regular I/O banks, these banks must be set to the same V<sub>CCIO</sub> level, but can have separate V<sub>REF</sub> bank settings.

For more information on I/O standards, see *Application Note 117 (Using Selectable I/O Standards in Altera Devices)*.

# MultiVolt I/O Interface

The Mercury architecture supports the MultiVolt I/O interface feature, which allows Mercury devices in all packages to interface with devices with different supply voltages. The devices have one set of VCC pins for internal operation and input buffers (VCCINT), and another set for I/O output drivers (VCCIO).

# Lock Signals

The Mercury device general purpose PLL circuits support individual LOCK signals. The LOCK signal drives high when the PLL has locked onto the input clock. Lock remains high as long as the input remains within specification. It will go low if the input is out of specification. A LOCK pin is optional for each PLL used in the Mercury devices; when not used, they are I/O pins. This signal is not available internally; if it is used in the core, it must be fed back in with an input pin.

# SignalTap Embedded Logic Analyzer

Mercury devices include device enhancements to support the SignalTap embedded logic analyzer. By including this circuitry, the Mercury device provides the ability to monitor design operation over a period of time through the IEEE Std. 1149.1 JTAG circuitry; a designer can analyze internal logic at speed without bringing internal signals to the I/O pins. This feature is particularly important for advanced packages such as FineLine BGA packages, because it can be difficult to add a connection to a pin during the debugging process after a board is designed and manufactured.

# IEEE Std. 1149.1 (JTAG) Boundary-Scan Support

All Mercury devices provide JTAG BST circuitry that complies with the IEEE Std. 1149.1-1990 specification. JTAG boundary-scan testing can be performed before or after configuration, but not during configuration. Mercury devices can also use the JTAG port for configuration with the Quartus II software or with hardware using either Jam Standard Test and Programming Language (STAPL) Files (,jam) or Jam STAPL Byte-Code Files (,jbc). Mercury devices also use the JTAG port to monitor the logic operation of the device with the SignalTap embedded logic analyzer. Mercury devices support the JTAG instructions shown in Table 16.

For more information, see the following documents:

- Application Note 39 (IEEE Std. 1149.1 (JTAG) Boundary-Scan Testing in Altera Devices)

- Jam Programming & Test Language Specification

# **Generic Testing**

Each Mercury device is functionally tested. Complete testing of each configurable static random access memory (SRAM) bit and all logic functionality ensures 100% yield. AC test measurements for Mercury devices are made under conditions equivalent to those shown in Figure 33. Multiple test patterns can be used to configure devices during all stages of the production flow.

| Table 26. 1.8-V I/O Specifications Note (10) |                           |                                            |                          |                        |       |  |  |

|----------------------------------------------|---------------------------|--------------------------------------------|--------------------------|------------------------|-------|--|--|

| Symbol                                       | Parameter                 | Conditions                                 | Minimum                  | Maximum                | Units |  |  |

| V <sub>CCIO</sub>                            | Output supply voltage     |                                            | 1.71                     | 1.89                   | V     |  |  |

| V <sub>IH</sub>                              | High-level input voltage  |                                            | $0.65 \times V_{CCIO}$   | 4.1                    | V     |  |  |

| V <sub>IL</sub>                              | Low-level input voltage   |                                            | -0.5                     | $0.35 \times V_{CCIO}$ | V     |  |  |

| I <sub>I</sub>                               | Input pin leakage current | V <sub>IN</sub> = 0 V or V <sub>CCIO</sub> | -10                      | 10                     | μΑ    |  |  |

| V <sub>OH</sub>                              | High-level output voltage | $I_{OH} = -2 \text{ mA}$                   | V <sub>CCIO</sub> - 0.45 |                        | V     |  |  |

| $V_{OL}$                                     | Low-level output voltage  | $I_{OL} = 2 \text{ mA}$                    |                          | 0.45                   | V     |  |  |

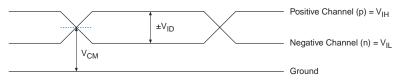

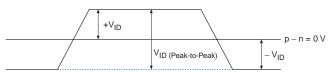

Figures 34 and 35 show receiver input and transmitter output waveforms, respectively, for all differential I/O standards (LVPECL, 3.3-V PCML, LVDS, and HyperTransport technology).

Figure 34. Receiver Input Waveforms for Differential I/O Standards

Single-Ended Waveform

#### **Differential Waveform**

| Symbol              | Parameter                            | Conditions | Minimum           | Typical           | Maximum                 | Units |

|---------------------|--------------------------------------|------------|-------------------|-------------------|-------------------------|-------|

| V <sub>CCIO</sub>   | I/O supply voltage                   |            | 3.135             | 3.3               | 3.465                   | V     |

| V <sub>IL</sub>     | Low-level input voltage              |            |                   |                   | V <sub>CCIO</sub> – 0.4 | V     |

| V <sub>IH</sub>     | High-level input voltage             |            | V <sub>CCIO</sub> |                   |                         | V     |

| V <sub>OL</sub>     | Low-level output voltage             |            |                   |                   | V <sub>CCIO</sub> – 0.4 | V     |

| V <sub>OH</sub>     | High-level output voltage            |            | V <sub>CCIO</sub> |                   |                         | V     |

| V <sub>T</sub>      | Output termination voltage           |            |                   | V <sub>CCIO</sub> |                         | V     |

| V <sub>ID</sub>     | Differential input voltage           |            | 400               |                   | 800                     | mV    |

| V <sub>OD</sub>     | Differential output voltage          |            | 400               | 700               | 800                     | mV    |

| t <sub>R</sub>      | Rise time (20 to 80%)                |            |                   |                   | 200                     | ps    |

| t <sub>F</sub>      | Fall time (20 to 80%)                |            |                   |                   | 200                     | ps    |

| t <sub>DSKEW</sub>  | Differential skew                    |            |                   |                   | 25                      | ps    |

| R <sub>1</sub> (11) | Output load                          |            | 90                | 100               | 110                     | Ω     |

| R <sub>2</sub> (11) | Receiver differential input resistor |            | 45                | 50                | 55                      | Ω     |

| Symbol             | Parameter                            | Conditions | Minimum | Typical | Maximum | Units |

|--------------------|--------------------------------------|------------|---------|---------|---------|-------|

| V <sub>CCIO</sub>  | I/O supply voltage                   |            | 3.135   | 3.3     | 3.465   | V     |

| V <sub>IL</sub>    | Low-level input voltage              |            | 0       |         | 2,000   | mV    |

| V <sub>IH</sub>    | High-level input voltage             |            | 400     |         | 2,470   | mV    |

| V <sub>OL</sub>    | Low-level output voltage             |            | 1,400   |         | 1,650   | mV    |

| V <sub>OH</sub>    | High-level output voltage            |            | 2,275   |         | 2,470   | mV    |

| V <sub>ID</sub>    | Differential input voltage           |            | 400     | 600     | 1,200   | mV    |

| V <sub>OD</sub>    | Differential output voltage          |            | 525     | 1,050   | 1,200   | mV    |

| t <sub>R</sub>     | Rise time (20 to 80%)                |            | 85      |         | 325     | ps    |

| t <sub>F</sub>     | Fall time (20 to 80%)                |            | 85      |         | 325     | ps    |

| t <sub>DSKEW</sub> | Differential skew                    |            |         |         | 25      | ps    |

| R <sub>L</sub>     | Receiver differential input resistor |            |         | 100     |         | Ω     |

| Table 36. SSTL-3 Class II Specifications Note (10) |                           |                           |                        |           |                         |       |

|----------------------------------------------------|---------------------------|---------------------------|------------------------|-----------|-------------------------|-------|

| Symbol                                             | Parameter                 | Conditions                | Minimum                | Typical   | Maximum                 | Units |

| V <sub>CCIO</sub>                                  | I/O supply voltage        |                           | 3.0                    | 3.3       | 3.6                     | V     |

| $V_{TT}$                                           | Termination voltage       |                           | $V_{REF} - 0.05$       | $V_{REF}$ | V <sub>REF</sub> + 0.05 | V     |

| $V_{REF}$                                          | Reference voltage         |                           | 1.3                    | 1.5       | 1.7                     | V     |

| $V_{IH}$                                           | High-level input voltage  |                           | V <sub>REF</sub> + 0.2 |           | V <sub>CCIO</sub> + 0.3 | V     |

| $V_{IL}$                                           | Low-level input voltage   |                           | -0.3                   |           | V <sub>REF</sub> – 0.2  | V     |

| V <sub>OH</sub>                                    | High-level output voltage | $I_{OH} = -16 \text{ mA}$ | V <sub>TT</sub> + 0.8  |           |                         | V     |

| $V_{OL}$                                           | Low-level output voltage  | I <sub>OL</sub> = 16 mA   |                        |           | V <sub>TT</sub> – 0.8   | V     |

| Table 37. 3.3-V AGP -2X Specifications |                               |                          |                        |         |                         |       |

|----------------------------------------|-------------------------------|--------------------------|------------------------|---------|-------------------------|-------|

| Symbol                                 | Parameter                     | Conditions               | Minimum                | Typical | Maximum                 | Units |

| V <sub>CCIO</sub>                      | I/O supply voltage            |                          | 3.15                   | 3.3     | 3.45                    | V     |

| $V_{REF}$                              | Reference voltage             |                          | $0.39 \times V_{CCIO}$ |         | $0.41 \times V_{CCIO}$  | V     |

| V <sub>IH</sub>                        | High-level input voltage (12) |                          | $0.5 \times V_{CCIO}$  |         | V <sub>CCIO</sub> + 0.5 | V     |

| V <sub>IL</sub>                        | Low-level input voltage (12)  |                          |                        |         | 0.3 × V <sub>CCIO</sub> | V     |

| V <sub>OH</sub>                        | High-level output voltage     | $I_{OUT} = -20 \mu A$    | $0.9 \times V_{CCIO}$  |         | 3.6                     | V     |

| V <sub>OL</sub>                        | Low-level output voltage      | I <sub>OUT</sub> = 20 μA |                        |         | $0.1 \times V_{CCIO}$   | V     |

| I <sub>I</sub>                         | Input pin leakage current     | $0 < V_{IN} < V_{CCIO}$  |                        |         | ±10                     | μΑ    |

| Table 38. 3.3-V AGP -1X Specifications |                               |                          |                         |         |                         |       |  |

|----------------------------------------|-------------------------------|--------------------------|-------------------------|---------|-------------------------|-------|--|

| Symbol                                 | Parameter                     | Conditions               | Minimum                 | Typical | Maximum                 | Units |  |

| V <sub>CCIO</sub>                      | I/O supply voltage            |                          | 3.15                    | 3.3     | 3.45                    | V     |  |

| V <sub>IH</sub>                        | High-level input voltage (12) |                          | 0.5 × V <sub>CCIO</sub> |         | V <sub>CCIO</sub> + 0.5 | V     |  |

| V <sub>IL</sub>                        | Low-level input voltage (12)  |                          |                         |         | $0.3 \times V_{CCIO}$   | V     |  |

| V <sub>OH</sub>                        | High-level output voltage     | $I_{OUT} = -20 \mu A$    | $0.9 \times V_{CCIO}$   |         | 3.6                     | V     |  |

| V <sub>OL</sub>                        | Low-level output voltage      | I <sub>OUT</sub> = 20 μA |                         |         | $0.1 \times V_{CCIO}$   | V     |  |

| I                                      | Input pin leakage current     | $0 < V_{IN} < V_{CCIO}$  |                         |         | ±10                     | μΑ    |  |

Tables 44 and 45 describe the Mercury device's external timing parameters.

| Table 44. Mercury External Timing Parameters Notes (1), (2) |                                                             |            |  |  |  |

|-------------------------------------------------------------|-------------------------------------------------------------|------------|--|--|--|

| Symbol                                                      | Parameter                                                   | Conditions |  |  |  |

| t <sub>INSU</sub>                                           | Setup time with global clock at IOE register                |            |  |  |  |

| t <sub>INH</sub>                                            | Hold time with global clock at IOE register                 |            |  |  |  |

| t <sub>оитсо</sub>                                          | Clock-to-output delay with global clock at IOE register     | C1 = 35 pF |  |  |  |

| t <sub>INSUPLL</sub>                                        | Setup time with PLL clock at IOE input register             |            |  |  |  |

| t <sub>INHPLL</sub>                                         | Hold time with PLL clock at IOE input register              |            |  |  |  |

| t <sub>OUTCOPLL</sub>                                       | Clock-to-output delay with PLL clock at IOE output register | C1 = 35 pF |  |  |  |

| Table 45. Mercury External Bidirectional Timing Parameters Notes (1), (2) |                                                                                       |            |  |  |  |

|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------|--|--|--|

| Symbol                                                                    | Parameter                                                                             | Conditions |  |  |  |

| t <sub>INSUBIDIR</sub>                                                    | Setup time for bidirectional pins with gobal clock at IOE input register              |            |  |  |  |

| t <sub>INHBIDIR</sub>                                                     | Hold time for bidirectional pins with global clock at IOE input register              |            |  |  |  |

| toutcobidir                                                               | Clock-to-output delay for bidirectional pins with global clock at IOE output register | C1 = 35 pF |  |  |  |

| t <sub>XZBIDIR</sub>                                                      | Synchronous IOE output enable register to output buffer disable delay                 | C1 = 35 pF |  |  |  |

| t <sub>ZXBIDIR</sub>                                                      | Synchronous IOE output enable register output buffer enable delay                     | C1 = 35 pF |  |  |  |

| t <sub>INSUBIDIRPLL</sub>                                                 | Setup time for bidirectional pins with PLL clock at IOE input register                |            |  |  |  |

| t <sub>INHBIDIRPLL</sub>                                                  | Hold time for bidirectional pins with PLL clock at IOE input register                 |            |  |  |  |

| toutcobidirpll                                                            | Clock-to-output delay for bidirectional pins with PLL clock at IOE output register    | C1 = 35 pF |  |  |  |

| <sup>t</sup> XZBIDIRPLL                                                   | Synchronous IOE output enable register to output buffer disable delay with PLL        | C1 = 35 pF |  |  |  |

| t <sub>ZXBIDIRPLL</sub>                                                   | Synchronous IOE output enable register output buffer enable delay with PLL            | C1 = 35 pF |  |  |  |

# Notes to Tables 44 and 45:

- (1) These timing parameters are sample-tested only.

- (2) All timing parameters are either to and/or from pins, including global clock pins.