# Intel - EP1M350F780I6 Datasheet

Welcome to <u>E-XFL.COM</u>

### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

## Details

| Product Status                 | Obsolete                                                 |

|--------------------------------|----------------------------------------------------------|

| Number of LABs/CLBs            | 1440                                                     |

| Number of Logic Elements/Cells | 14400                                                    |

| Total RAM Bits                 | 114688                                                   |

| Number of I/O                  | 486                                                      |

| Number of Gates                | 350000                                                   |

| Voltage - Supply               | 1.71V ~ 1.89V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                       |

| Package / Case                 | 780-BBGA, FCBGA                                          |

| Supplier Device Package        | 780-FBGA (29x29)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1m350f780i6 |

|                                |                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Tables 2 and 3 show the Mercury  $^{\rm TM}$  FineLine BGA  $^{\rm TM}$  device package sizes, options, and I/O pin counts.

| Table 2. Mercury Package Sizes         |                         |                         |  |  |  |  |  |  |

|----------------------------------------|-------------------------|-------------------------|--|--|--|--|--|--|

| Feature                                | 484-Pin<br>FineLine BGA | 780-Pin<br>FineLine BGA |  |  |  |  |  |  |

| Pitch (mm)                             | 1.00                    | 1.00                    |  |  |  |  |  |  |

| Area (mm <sup>2</sup> )                | 529                     | 841                     |  |  |  |  |  |  |

| Length $\times$ width (mm $\times$ mm) | $23 \times 23$          | 29 × 29                 |  |  |  |  |  |  |

| Table 3. Mercury Package Options & I/O Count |                         |                         |  |  |  |  |  |

|----------------------------------------------|-------------------------|-------------------------|--|--|--|--|--|

| Device                                       | 484-Pin<br>FineLine BGA | 780-Pin<br>FineLine BGA |  |  |  |  |  |

| EP1M120                                      | 303                     |                         |  |  |  |  |  |

| EP1M350                                      |                         | 486                     |  |  |  |  |  |

# General Description

Mercury devices integrate high-speed differential transceivers and support for CDR with a speed-optimized PLD architecture. These transceivers are implemented through the dedicated serializer, deserializer, and clock recovery circuitry in the HSDI and incorporate support for the LVDS, LVPECL, and 3.3-V PCML I/O standards. This circuitry, together with enhanced I/O elements (IOEs) and support for numerous I/O standards, allows Mercury devices to meet high-speed interface requirements.

Mercury devices are the first PLDs optimized for core performance. These LUT-based, enhanced memory devices use a network of fast routing resources to achieve optimal performance. These resources are ideal for data-path, register-intensive, mathematical, digital signal processing (DSP), or communications designs.

Mercury devices include other features for performance such as quadport RAM, CAM, general purpose PLLs, and dedicated circuitry for implementing multiplier circuits. Table 4 shows Mercury performance.

| Table 4. Mercury Performance     |         |         |                   |                   |                   |       |  |  |  |  |  |

|----------------------------------|---------|---------|-------------------|-------------------|-------------------|-------|--|--|--|--|--|

| Application                      | Resourc | es Used |                   | Perform           | ance              |       |  |  |  |  |  |

|                                  | LEs     | ESBs    | -5 Speed<br>Grade | -6 Speed<br>Grade | -7 Speed<br>Grade | Units |  |  |  |  |  |

| 16-bit loadable counter (1)      | 16      | 0       | 400               | 400               | 400               | MHz   |  |  |  |  |  |

| 32-bit loadable counter (1)      | 32      | 0       | 400               | 400               | 400               | MHz   |  |  |  |  |  |

| 32-bit accumulator (1)           | 32      | 0       | 400               | 400               | 400               | MHz   |  |  |  |  |  |

| 32-to-1 multiplexer              | 27      | 0       | 1.864             | 2.466             | 2.723             | ns    |  |  |  |  |  |

| $32 \times 64$ asynchronous FIFO | 103     | 2       | 290               | 258               | 242               | MHz   |  |  |  |  |  |

| 8-bit, 37-tap FIR filter         | 251     | 1       | 290               | 240               | 205               | MSPS  |  |  |  |  |  |

#### Note to Table 4:

The clock tree supports up to 400 MHz. Although the registered performance for these designs exceed 400 MHz, they are limited by the clock tree limit.

## Configuration

The logic, circuitry, and interconnects in the Mercury architecture are configured with CMOS SRAM elements. Mercury devices are reconfigurable and are 100% tested prior to shipment. As a result, test vectors do not have to be generated for fault coverage purposes. Instead, the designer can focus on simulation and design verification. In addition, the designer does not need to manage inventories of different ASIC designs; Mercury devices can be configured on the board for the specific functionality required.

Mercury devices are configured at system power-up with data stored in an Altera<sup>®</sup> serial configuration device or provided by a system controller. Altera offers in-system programmability (ISP)-capable configuration devices, which configure Mercury devices via a serial data stream. Mercury devices can be configured in under 70 ms. Moreover, Mercury devices contain an optimized interface that permits microprocessors to configure Mercury devices serially or in parallel, synchronously or asynchronously. This interface also enables microprocessors to treat Mercury devices as memory and to configure the device by writing to a virtual memory location, simplifying reconfiguration.

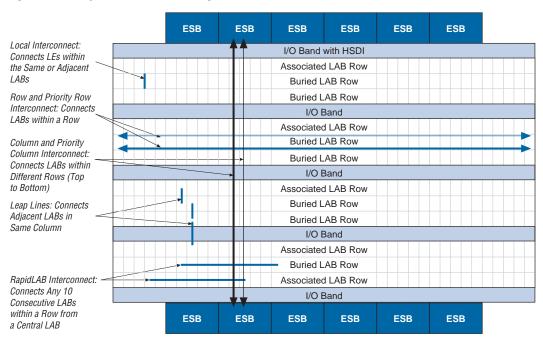

## Figure 1. Mercury Architecture Block Diagram Note (1)

#### Note to Figure 1:

(1) Figure 1 shows an EP1M120 device. Mercury devices have a varying number of rows, columns, and ESBs, as shown in Table 5.

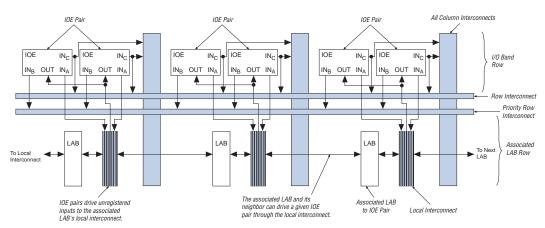

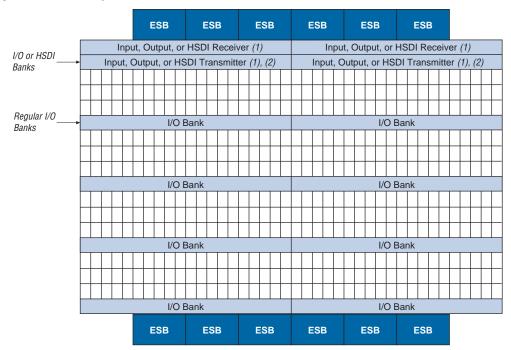

## Table 5 lists the resources available in Mercury devices.

| Table 5. Mercury Device Resources |          |             |               |      |  |  |  |  |  |

|-----------------------------------|----------|-------------|---------------|------|--|--|--|--|--|

| Device                            | LAB Rows | LAB Columns | I/O Row Bands | ESBs |  |  |  |  |  |

| EP1M120                           | 12       | 40          | 5             | 12   |  |  |  |  |  |

| EP1M350                           | 18       | 80          | 4             | 28   |  |  |  |  |  |

F

Mercury device HSDI performance is finalized for certain speed grades. Also, the industrial-grade CDR specification is the same as the -6 speed grade for commercial-grade CDR specification. See Table 8.

| Table 8. CDR & Se | Table 8. CDR & Source-Synchronous Data Rates |                    |                                 |                                                    |  |  |  |  |  |  |  |

|-------------------|----------------------------------------------|--------------------|---------------------------------|----------------------------------------------------|--|--|--|--|--|--|--|

| Device            | Speed Grade                                  | Number of Channels | Maximum CDR Data<br>Rate (Gbps) | Maximum Source-<br>Synchronous Data<br>Rate (Mbps) |  |  |  |  |  |  |  |

| EP1M120           | -5                                           | 8                  | 1.25                            | 840                                                |  |  |  |  |  |  |  |

|                   | -6 (1)                                       | 8                  | 1.25                            | 840                                                |  |  |  |  |  |  |  |

|                   | -7                                           | 8                  | 1.0                             | 840                                                |  |  |  |  |  |  |  |

| EP1M350           | -5                                           | 18                 | 1.25                            | 840                                                |  |  |  |  |  |  |  |

|                   | -6 (1)                                       | 8 (2)              | 1.25                            | 840                                                |  |  |  |  |  |  |  |

|                   |                                              | 10 (2)             | 1.0                             | 840                                                |  |  |  |  |  |  |  |

|                   | -7                                           | 18                 | 1.0                             | 840                                                |  |  |  |  |  |  |  |

#### Notes to Table 8:

(1) The -6 speed grade specifications apply for both commercial and industrial devices.

(2) EP1M350 devices can support any 8 channels at 1.25 Gbps. The other 10 channels must run at 1.0 Gbps or less.

# Logic & Interconnect

Mercury device logic is implemented in LEs. LE resources are used differently according to specific operating modes and the type of logic function being implemented. LEs are grouped into LABs in a row-based architecture. The multi-level FastTrack Interconnect structure provides the routing connection between LEs, ESBs, and IOEs.

## Logic Array Block

Each LAB consists of 10 LEs, LE carry chains, multiplier circuitry, LAB control signals, local interconnect, and FastLUT connection lines. The local interconnect transfers signals between LEs within the same or adjacent LABs. FastLUT connections transfer the output of one LE to the adjacent LE for ultra-fast sequential LE connections within the same LAB. The Quartus II Compiler places associated logic within a LAB or adjacent LABs, allowing the use of fast local and FastLUT connections for high performance. Figure 5 shows the Mercury LAB structure.

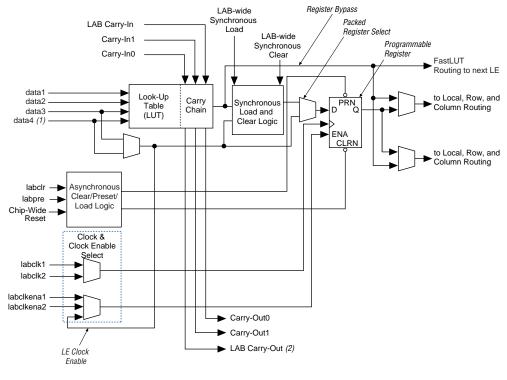

### Figure 7. Mercury LE

#### Notes to Figure 7:

- (1) FastLUT interconnect uses the data4 input.

- (2) LAB carry-out can only be generated by LE 4 and/or LE 10.

Each LE's programmable register can be configured for D, T, JK, or SR operation. The register's clock, clock enable, and clear control signals can be driven by global signals, general-purpose I/O pins, or any internal logic. For combinatorial functions, the register is bypassed and the output of the LUT drives directly to the outputs of the LE.

Each LE has four data inputs that can drive the internal LUT. One of these inputs has a shorter delay than the others, improving overall LE performance. This input is chosen automatically by the Quartus II software as appropriate.

Each LE has two outputs that drive the local, row, and column routing resources. Each output can be driven independently by the LUT's or register's output. For example, the LUT can drive one output, while the register drives the other output. This feature, called register packing, improves device utilization because the register and the LUT can be used for unrelated functions. The LE can also drive out registered and unregistered versions of the LUT output.

#### LE Operating Modes

The Mercury LE can operate in one of the following modes:

- Normal

- Arithmetic

- Multiplier

Each operating mode uses LE resources differently. In each operating mode, eight available inputs to the LE—the four data inputs from the LAB local interconnect; carry-in0, carry-in1 from the previous LE; the LAB carry-in from the previous carry-chain generation; and the FastLUT Connection input from the previous LE—are directed to different destinations to implement the desired logic function. LAB-wide signals provide clock, asynchronous clear, asynchronous preset, asynchronous load, synchronous clear, synchronous load, and clock enable control for the register. These LAB-wide signals are available in all normal and arithmetic LE modes.

The Quartus II software, in conjunction with parameterized functions such as LPM and DesignWare functions, automatically chooses the appropriate mode for common functions, such as counters, adders, and multipliers. If required, the designer can also create special-purpose functions that specify which LE operating mode to use for optimal performance.

#### Normal Mode

The normal mode is suitable for general logic applications and combinatorial functions. In normal mode, four data inputs from the LAB local interconnect and a single carry-in are inputs to a four-input LUT. The Quartus II Compiler automatically selects the carry-in or the data3 signal as one of the inputs to the LUT. The LUT (combinatorial) output can be driven to the FastLUT connection to the next LE in the LAB. LEs in normal mode support packed registers. Figure 8 shows an LE in normal mode.

The Quartus II Compiler creates carry chains longer than ten LEs by linking LABs together automatically. For enhanced fitting, a long carry chain skips intermediate LABs in a row structure. A carry chain longer than one LAB skips either from an even-numbered LAB to the next evennumbered LAB, or from an odd-numbered LAB to the next oddnumbered LAB. For example, the last LE of the first LAB in a LAB row carries to the first LE of the third LAB in the same LAB row.

## **Multiplier Mode**

Multiplier mode is used for implementing high-speed multipliers up to  $16 \times 16$  in size. The LUT implements the partial product formation and summation in a single stage for a  $N \times M$ -bit multiply operation. A single LE can implement the summation of  $A_N B_{M+1} + A_{N+1} B_M$  for the multiplier and multiplicand inputs. To increase the speed of the multiplication, LAB wide signals are used to control the partial product sum generation. These multiplier LAB-wide signals use the LABCLKENA1 and PRESET/ASYNCLOAD resources. The multiplier mode takes advantage of the CSLA circuitry for optimized sum and carry generation in the partial product sum. There is a special CSLA circuitry mode used for the multiplier where the carry chain runs vertically between LABs in the same column. The Quartus II Compiler automatically uses this special mode for dedicated multiplier implementation only. The summation of the multiplier and multiplicand bits is driven out along with the carryout 0 and carry-out 1 bits. The combinatorial or registered versions of the sum can be driven out, allowing the multiplier to be pipelined.

The RapidLAB interconnect has dedicated fast connections to the LE inputs in multiplier mode, further increasing the speed of the multiplier. These dedicated connections allow RapidLAB lines to avoid delay incurred by driving onto local interconnects and then into the LE.

The Quartus II software implements parameterized functions that use the multiplier mode automatically when multiply operators are used.

Figure 11 shows a Mercury device LE in multiplier mode.

|     |                 |                                                                                                                                                                                                                                   |                                                                                       |                                                                                            |                                                                                       |                                                                                       |                                                                                       |                                                                   | Sixteen 16-Bit                                                         | Partial Products                                                                      |                                                                                        |                                                                                                  |                                                                                                       |                                                                                                       |                                                                                                   |                                                                                                       |                                                                                                             |

|-----|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| 04  | Bo              | 0B0                                                                                                                                                                                                                               |                                                                                       |                                                                                            |                                                                                       |                                                                                       |                                                                                       |                                                                   |                                                                        |                                                                                       |                                                                                        |                                                                                                  |                                                                                                       |                                                                                                       |                                                                                                   |                                                                                                       |                                                                                                             |

| 4   | <u>B</u>        | A1B0 /                                                                                                                                                                                                                            | ^0B1                                                                                  |                                                                                            |                                                                                       |                                                                                       |                                                                                       |                                                                   |                                                                        |                                                                                       |                                                                                        |                                                                                                  |                                                                                                       |                                                                                                       |                                                                                                   |                                                                                                       |                                                                                                             |

| 2   | B2              | A2B0                                                                                                                                                                                                                              | A1B1                                                                                  | A <sub>0</sub> B <sub>2</sub>                                                              |                                                                                       |                                                                                       |                                                                                       |                                                                   |                                                                        |                                                                                       |                                                                                        |                                                                                                  |                                                                                                       |                                                                                                       |                                                                                                   |                                                                                                       |                                                                                                             |

| 2   | B3              | ан алаан алаан<br>Аңево Аңево Аңе | Ai5B1 Ai4B1 Ai3B1 Ai2B1 Ai1B1 Ai0B1 A9B1 A6B1 A7B1 A6B1 A5B1 A4B1 A3B1 A2B1 A1B1 A0B1 | A15B2 A14B2 A13B2 A12B2 A11B2 A10B2 A6B2 A6B2 A5B2 A5B2 A6B2 A5B2 A4B2 A3B2 A2B2 A1B2 A0B2 | A <sub>0</sub> B <sub>3</sub>                                                         |                                                                                       |                                                                                       |                                                                   |                                                                        |                                                                                       |                                                                                        |                                                                                                  |                                                                                                       |                                                                                                       |                                                                                                   |                                                                                                       |                                                                                                             |

| ŧ   | B4              | = == ==<br>A₄B₀                                                                                                                                                                                                                   | A <sub>3</sub> B <sub>1</sub>                                                         | $A_2B_2$                                                                                   | A15B3 A14B3 A13B3 A12B3 A11B3 A10B3 A9B3 A8B3 A7B3 A6B3 A5B3 A4B3 A3B3 A2B3 A1B3 A0B3 | A <sub>0</sub> B <sub>4</sub>                                                         |                                                                                       |                                                                   |                                                                        |                                                                                       |                                                                                        |                                                                                                  |                                                                                                       |                                                                                                       |                                                                                                   |                                                                                                       |                                                                                                             |

| 2   | B5              | A5B0                                                                                                                                                                                                                              | A4B1                                                                                  | $A_3B_2$                                                                                   | $A_2B_3$                                                                              | A15B4 A14B4 A13B4 A12B4 A11B4 A10B4 A9B4 A8B4 A7B4 A6B4 A5B4 A4B4 A3B4 A2B4 A1B4 A0B4 | A <sub>0</sub> B <sub>5</sub>                                                         |                                                                   |                                                                        |                                                                                       |                                                                                        |                                                                                                  |                                                                                                       |                                                                                                       |                                                                                                   |                                                                                                       |                                                                                                             |

| P   | $^{\rm B_6}$    | A6B0                                                                                                                                                                                                                              | A5B1                                                                                  | A4B2                                                                                       | $A_3B_3$                                                                              | $A_2B_4$                                                                              | A15B5 A14B5 A13B5 A12B5 A11B5 A10B5 A3B5 A8B5 A7B5 A6B5 A5B5 A4B5 A3B5 A2B5 A1B5 A0B5 | $A_0B_6$                                                          |                                                                        |                                                                                       |                                                                                        |                                                                                                  |                                                                                                       |                                                                                                       |                                                                                                   |                                                                                                       |                                                                                                             |

|     | B <sub>7</sub>  | = == =<br>A7B0                                                                                                                                                                                                                    | A <sub>6</sub> B <sub>1</sub>                                                         | A5B2                                                                                       | A4B3                                                                                  | A <sub>3</sub> B <sub>4</sub>                                                         | A2B5                                                                                  | A1B6                                                              | $A_0B_7$                                                               |                                                                                       |                                                                                        |                                                                                                  |                                                                                                       |                                                                                                       |                                                                                                   |                                                                                                       |                                                                                                             |

| 2   | B <sub>8</sub>  | == == =<br>A <sub>8</sub> B <sub>0</sub>                                                                                                                                                                                          | A7B1                                                                                  | $A_6B_2$                                                                                   | A5B3                                                                                  | A4B4                                                                                  | A <sub>3</sub> B <sub>5</sub>                                                         | A3B6 A2B6 A1B6 A0B6                                               | A2B7 A1B7                                                              | A <sub>0</sub> B <sub>8</sub>                                                         |                                                                                        |                                                                                                  |                                                                                                       |                                                                                                       |                                                                                                   |                                                                                                       |                                                                                                             |

| P   | å               | A9B0                                                                                                                                                                                                                              | A <sub>8</sub> B <sub>1</sub>                                                         | A7B2                                                                                       | $A_6B_3$                                                                              | A5B4                                                                                  | A4B5                                                                                  | A <sub>3</sub> B <sub>6</sub>                                     |                                                                        | A <sub>1</sub> B <sub>8</sub>                                                         | A <sub>0</sub> B <sub>9</sub>                                                          |                                                                                                  |                                                                                                       |                                                                                                       |                                                                                                   |                                                                                                       |                                                                                                             |

|     | B <sub>10</sub> | = == =<br>A <sub>10</sub> B <sub>0</sub>                                                                                                                                                                                          | A <sub>9</sub> B <sub>1</sub>                                                         | $A_8B_2$                                                                                   | A7B3                                                                                  | A <sub>6</sub> B <sub>4</sub>                                                         | A5B5                                                                                  | A4B6                                                              | A <sub>3</sub> B <sub>7</sub>                                          | $A_2B_8$                                                                              | A <sub>1</sub> B <sub>9</sub>                                                          | A0B10                                                                                            |                                                                                                       |                                                                                                       |                                                                                                   |                                                                                                       |                                                                                                             |

|     | B11             | =====<br>A <sub>11</sub> B <sub>0</sub>                                                                                                                                                                                           | A10B1                                                                                 | A <sub>9</sub> B <sub>2</sub>                                                              | $A_8B_3$                                                                              | $A_7B_4$                                                                              | A <sub>6</sub> B <sub>5</sub>                                                         | A <sub>5</sub> B <sub>6</sub>                                     | A4B7                                                                   | A <sub>3</sub> B <sub>8</sub>                                                         | $A_2B_9$                                                                               | A1B10                                                                                            | A0B11                                                                                                 |                                                                                                       |                                                                                                   |                                                                                                       |                                                                                                             |

| 71. | B <sub>12</sub> | A12B0                                                                                                                                                                                                                             | A11B1                                                                                 | A10B2                                                                                      | A9B3                                                                                  | A <sub>8</sub> B <sub>4</sub>                                                         | A7B5                                                                                  | $A_6B_6$                                                          | A <sub>5</sub> B <sub>7</sub>                                          | A4B8                                                                                  | A <sub>3</sub> B <sub>9</sub>                                                          | A2B10                                                                                            | A1B11                                                                                                 | A0B12                                                                                                 |                                                                                                   |                                                                                                       |                                                                                                             |

| 212 | B <sub>13</sub> | = == ==<br>A13B0                                                                                                                                                                                                                  | A12B1                                                                                 | A11B2                                                                                      | A10B3                                                                                 | A9B4                                                                                  | A <sub>8</sub> B <sub>5</sub>                                                         | $A_7B_6$                                                          | A <sub>6</sub> B <sub>7</sub>                                          | A5B8                                                                                  | A4B9                                                                                   | 1 A3B10                                                                                          | A2B11                                                                                                 | A1B12                                                                                                 | A0B13                                                                                             |                                                                                                       |                                                                                                             |

| *   | B <sub>14</sub> | == == =<br>A14Bc                                                                                                                                                                                                                  | A13B1                                                                                 | A12B2                                                                                      | A11B3                                                                                 | A10B4                                                                                 | AgB5                                                                                  | A15B6 A14B6 A13B6 A12B6 A11B6 A10B6 A9B6 A6B6 A7B6 A6B6 A5B6 A4B6 | A15B7 A14B7 A13B7 A12B7 A11B7 A10B7 A9B7 A9B7 A7B7 A6B7 A5B7 A4B7 A3B7 | Å15B8 Å14B8 Å13B8 Å12B8 Å11B8 Å10B8 Å9B8 Å6B8 Å7B8 Å6B8 Å5B8 Å4B8 Å3B8 Å2B8 Å1B8 Å0B8 | ArsB9 AraB9 ArsB9 ArsB9 ArsB9 ArsB9 ArsB9 A8B9 A7B9 A6B9 A5B9 A4B9 A3B9 A2B9 ArB9 A0B9 | A15B10A14B10A13B10A12B10A11B10A10B10A9B10A9B10A8B10A7B10A6B10A6B10A6B10A4B10A3B10A2B10A1B10A0B10 | A15B11A14B11A13B11A12B11A11B11A10B11A9B11 A8B11 A7B11 A6B11 A6B11 A4B11 A4B11 A3B11 A2B11 A1B11 A0B11 | A15B12A14B12A13B12A12B12A11B12A10B12A9B12 A8B12 A7B12 A6B12 A6B12 A4B12 A5B12 A3B12 A2B12 A1B12 A0B12 | ÅisBi3Åi4Bi3Åi3Bi3Åi2Bi3Åi1Bi3Åi0Bi3ÅgBi3ÅgBi3Å9Bi3Å7Bi3Å6Bi3Å5Bi3Å5Bi3Å4Bi3Å3Bi3Å2Bi3Å18Bi3Å0Bi3 | A15B14A14B14A13B14A12B14A11B14A10B14A9B14 A8B14 A5B14 A5B14 A6B14 A5B14 A4B14 A3B14 A2B14 A1B14 A0B14 |                                                                                                             |

| 01. | B <sub>15</sub> | A15Bc                                                                                                                                                                                                                             | 1 A14B1                                                                               | 2 A13B2                                                                                    | 3 A12B3                                                                               | 4 A11B4                                                                               | 5 A10BE                                                                               | 5 AgB6                                                            | A <sub>8</sub> B <sub>7</sub>                                          | A7B8                                                                                  | A6B9                                                                                   | ) A5B10                                                                                          | 1 A4B11                                                                                               | 2 A3B12                                                                                               | 3 A2B13                                                                                           | 4 A1B14                                                                                               | AısBısAı4BısAı3BısAı2BısAı1BısAı0BısAşBıs AşBıs AşBıs AşBıs AşBıs AsBıs A4Bıs A3Bıs A2Bıs A2Bıs A1Bıs A0Bıs |

|     | ×               |                                                                                                                                                                                                                                   | A <sub>15</sub> B <sub>1</sub>                                                        | 2 A14B2                                                                                    | 3 A13B3                                                                               | t A12B4                                                                               | 5 A11B5                                                                               | 3 A10B6                                                           | AgB7                                                                   | A <sub>8</sub> B <sub>8</sub>                                                         | A7B9                                                                                   | ) A6B10                                                                                          | A5B11                                                                                                 | 2 A4B12                                                                                               | 3 A3B13                                                                                           | 1 A2B14                                                                                               | 5 A1B16                                                                                                     |

|     |                 |                                                                                                                                                                                                                                   |                                                                                       | A15B3                                                                                      | 3 A14B                                                                                | t A <sub>13</sub> B,                                                                  | 5 A12B                                                                                | 5 A11B                                                            | A10B                                                                   | 3 A9B8                                                                                | A <sub>8</sub> B <sub>9</sub>                                                          | ) A7B1(                                                                                          | A6B1                                                                                                  | 2 A5B1                                                                                                | 3 A4B1                                                                                            | 1 A3B1                                                                                                | 5 A2B1                                                                                                      |

|     |                 |                                                                                                                                                                                                                                   |                                                                                       |                                                                                            | A <sub>15</sub> B <sub>3</sub>                                                        | 1 A14B                                                                                | 5 A13B                                                                                | 3 A12B6                                                           | r A <sub>11</sub> B <sub>7</sub>                                       | 3 A10B                                                                                | A9B9                                                                                   | ) A8B1(                                                                                          | A7B1                                                                                                  | e A6B12                                                                                               | 3 A5B13                                                                                           | 1 A4B1                                                                                                | 5 A3B1£                                                                                                     |

|     |                 |                                                                                                                                                                                                                                   |                                                                                       |                                                                                            |                                                                                       | A15B4                                                                                 | A14B5                                                                                 | A13B6                                                             | A12B7                                                                  | A11B8                                                                                 | A <sub>10</sub> B <sub>6</sub>                                                         | AgB10                                                                                            | A <sub>8</sub> B <sub>11</sub>                                                                        | A7B12                                                                                                 | A6B13                                                                                             | A5B14                                                                                                 | A4B16                                                                                                       |

|     |                 |                                                                                                                                                                                                                                   |                                                                                       |                                                                                            |                                                                                       |                                                                                       | A15B5                                                                                 | A14B6                                                             | A13B7                                                                  | A12B8                                                                                 | A11B9                                                                                  | A10B10                                                                                           | A9B11                                                                                                 | A <sub>8</sub> B <sub>12</sub>                                                                        | A7B13                                                                                             | A6B14                                                                                                 | A5B15                                                                                                       |

|     |                 |                                                                                                                                                                                                                                   |                                                                                       |                                                                                            |                                                                                       |                                                                                       |                                                                                       | A15B6                                                             | A14B7                                                                  | A13B8                                                                                 | A12B9                                                                                  | A11B10                                                                                           | A10B11                                                                                                | A9B12                                                                                                 | A8B13                                                                                             | A7B14                                                                                                 | A6B15                                                                                                       |

|     |                 |                                                                                                                                                                                                                                   |                                                                                       |                                                                                            |                                                                                       |                                                                                       |                                                                                       |                                                                   | A15B7                                                                  | A14B8                                                                                 | A13B9                                                                                  | A12B10.                                                                                          | V11B11.                                                                                               | A10B12.                                                                                               | A9B13                                                                                             | \8B14                                                                                                 | V7B15                                                                                                       |

|     |                 |                                                                                                                                                                                                                                   |                                                                                       |                                                                                            |                                                                                       |                                                                                       |                                                                                       |                                                                   | 1                                                                      | 45B8 /                                                                                | 14B9 /                                                                                 | 43B10/                                                                                           | 42B11/                                                                                                | 41B12/                                                                                                | 40B13/                                                                                            | 9B14 /                                                                                                | 6B15 /                                                                                                      |

|     |                 |                                                                                                                                                                                                                                   |                                                                                       |                                                                                            |                                                                                       |                                                                                       |                                                                                       |                                                                   |                                                                        | ٩                                                                                     | 15B9 A                                                                                 | 14B10A                                                                                           | 13B11A                                                                                                | 12B12A                                                                                                | 11B13A                                                                                            | 10B14A                                                                                                | B15 A                                                                                                       |

|     |                 |                                                                                                                                                                                                                                   |                                                                                       |                                                                                            |                                                                                       |                                                                                       |                                                                                       |                                                                   |                                                                        |                                                                                       | Ŕ                                                                                      | 5B10 A                                                                                           | 4B11 A                                                                                                | 3B12 A                                                                                                | 2B13 A                                                                                            | 1B14 A                                                                                                | 0B15A                                                                                                       |

|     |                 |                                                                                                                                                                                                                                   |                                                                                       |                                                                                            |                                                                                       |                                                                                       |                                                                                       |                                                                   |                                                                        |                                                                                       |                                                                                        | Ą                                                                                                | 5B11A1                                                                                                | 4B12A1                                                                                                | 3B13A1                                                                                            | 2B14A1                                                                                                | 1B15A1                                                                                                      |

|     |                 |                                                                                                                                                                                                                                   |                                                                                       |                                                                                            |                                                                                       |                                                                                       |                                                                                       |                                                                   |                                                                        |                                                                                       |                                                                                        |                                                                                                  | A                                                                                                     | 5B12A1                                                                                                | tB13A1;                                                                                           | 8B14A1                                                                                                | B15A1                                                                                                       |

|     |                 |                                                                                                                                                                                                                                   |                                                                                       |                                                                                            |                                                                                       |                                                                                       |                                                                                       |                                                                   |                                                                        |                                                                                       |                                                                                        |                                                                                                  |                                                                                                       | A <sub>15</sub>                                                                                       | B13A14                                                                                            | B14A13                                                                                                | B15A12                                                                                                      |

|     |                 |                                                                                                                                                                                                                                   |                                                                                       |                                                                                            |                                                                                       |                                                                                       |                                                                                       |                                                                   |                                                                        |                                                                                       |                                                                                        |                                                                                                  |                                                                                                       |                                                                                                       | A15                                                                                               | 314A14                                                                                                | 315A13                                                                                                      |

|     |                 |                                                                                                                                                                                                                                   |                                                                                       |                                                                                            |                                                                                       |                                                                                       |                                                                                       |                                                                   |                                                                        |                                                                                       |                                                                                        |                                                                                                  |                                                                                                       |                                                                                                       |                                                                                                   | A <sub>15</sub> t                                                                                     | 15 A 1 4 l                                                                                                  |

Figure 12. Partial Product Formation

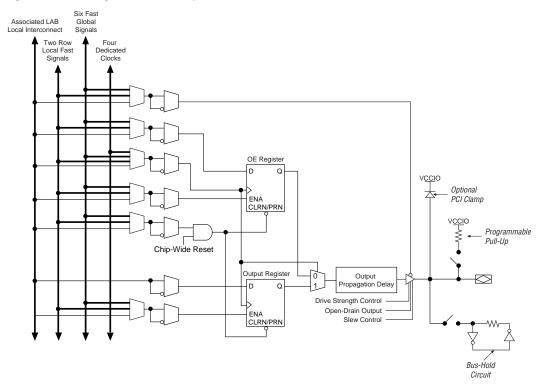

The Mercury IOE includes programmable delays that can be activated to ensure zero hold times, minimum clock-to-output times, input IOE register-to-core register transfers, or core-to-output IOE register transfers. A path in which a pin directly drives a register may require the delay to ensure zero hold time, whereas a path in which a pin drives a register through combinatorial logic may not require the delay. Programmable delays exist for decreasing input pin to core and IOE input register delays. The Quartus II Compiler can program these delays automatically to minimize setup time while providing a zero hold time. Delays are also programmable for increasing the register to pin delays for output and/or output enable registers. A programmable delay exists for increasing the t<sub>ZX</sub> delay to the output pin, which is required for ZBT interfaces. Table 10 shows the programmable delays for Mercury devices.

| Table 10. Mercury Programmable Delay Chain   |                                              |  |  |  |  |  |  |  |

|----------------------------------------------|----------------------------------------------|--|--|--|--|--|--|--|

| Programmable Delays                          | Quartus II Logic Option                      |  |  |  |  |  |  |  |

| Input pin to core delay (1)                  | Decrease input delay to internal cells       |  |  |  |  |  |  |  |

| Input pin to input register delay            | Decrease input delay to input register       |  |  |  |  |  |  |  |

| Output propagation delay                     | Increase delay to output pin                 |  |  |  |  |  |  |  |

| Output enable register t <sub>CO</sub> delay | Increase delay to OE pin                     |  |  |  |  |  |  |  |

| Output t <sub>ZX</sub> delay                 | Increase t <sub>ZX</sub> delay to output pin |  |  |  |  |  |  |  |

#### Note to Table 10:

(1) This delay has four settings: off and three levels of delay.

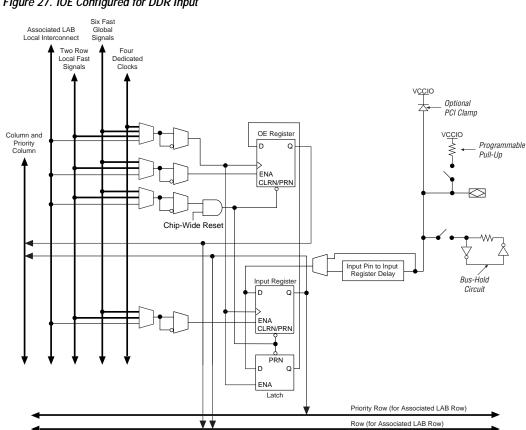

The IOE registers in Mercury devices share the same source for clear or preset. Use of the preset/clear is programmable for each individual IOE. The register(s) can be programmed to power up high or low after configuration is complete. If programmed to power up low, an asynchronous clear can control the register(s). If programmed to power up high, an asynchronous preset can control the register(s). This feature prevents the inadvertent activation of another device's active-low input upon power-up. Figure 26 shows the IOE for Mercury devices.

In Mercury device IOEs, the OE register is a multi-purpose register available as a second input or output register. When using the IOE for double data rate inputs, the input register and OE register are automatically configured as input registers to clock input double rate data on alternating edges. An input latch is also used within the IOE for DDR input acquisition. The latch holds the data that is present during the clock high times, driving it to the OE register. This allows the OE register and input register to clock both bits of data into LEs, synchronous to the same clock edge (either rising or falling). Figure 27 shows an IOE configured for DDR input.

Figure 27. IOE Configured for DDR Input

When using the IOE for double data rate outputs, the output register and OE register are automatically configured to clock two data paths from LEs on rising clock edges. These register outputs are multiplexed by the clock to drive the output pin at a  $\times$ 2 rate. The output register clocks the first bit out on the clock high time, while the OE register clocks the second bit out on the clock low time. Figure 28 shows the IOE configured for DDR output.

Figure 28. IOE Configured for DDR Output

Bidirectional DDR on an I/O pin is possible by using the IOE for DDR output and using LEs to acquire the double data rate input. Bidirectional DDR I/O pins support double data rate synchronous DRAM (DDR SDRAM) at 166 MHz (334 Mbps), which transfer data on a double data rate bidirectional bus. QDR SRAMs are also supported with DDR I/O pins on separate read and write ports.

## **Bus Hold**

Each Mercury device I/O pin provides an optional bus-hold feature. When this feature is enabled for an I/O pin, the bus-hold circuitry weakly holds the signal at its last driven state. By holding the last driven state of the pin until the next input signal is present, the bus-hold feature eliminates the need to add external pull-up or pull-down resistors to hold a signal level when the bus is tri-stated. The bus-hold circuitry also pulls undriven pins away from the input threshold voltage where noise can cause unintended high-frequency switching. This feature can be selected individually for each I/O pin. The bus-hold output will drive no higher than  $V_{CCIO}$  to prevent overdriving signals. If the bus-hold feature is enabled, the programmable pull-up option cannot be used. The bus-hold feature should also be disabled if open-drain outputs are used with the GTL+ I/O standard.

The bus-hold circuitry weakly pulls the signal level to the last driven state through a resistor with a nominal resistance (R<sub>BH</sub>) of approximately 8 kΩ. Table 42 gives specific sustaining current that will be driven through this resistor and overdrive current that will identify the next driven input level. This information is provided for each V<sub>CCIO</sub> voltage level.

The bus-hold circuitry is active only after configuration. When going into user mode, the bus-hold circuit captures the value on the pin present at the end of configuration.

# Programmable Pull-Up Resistor

Each Mercury device I/O pin provides an optional programmable pullup resistor during user mode. When this feature is enabled for an I/O pin, the pull-up resistor (50 kΩ) weakly holds the output to the  $V_{CCIO}$  level of the bank that the output pin resides in.

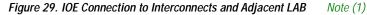

## I/O Row Bands

The I/O row bands are one of the advanced features of the Mercury architecture. All IOEs are grouped in I/O row bands across the device. The number of I/O row bands depends on the Mercury device size. The I/O row bands are designed for flip-chip technology, allowing I/O pins to be distributed across the entire chip, not only in the periphery. This array driver technology allows higher I/O pin density (I/O pins per device area) than peripheral I/O pins.

Each row of I/O pins has an associated LAB row for driving to and from the core of the Mercury device. For a given I/O band row, its associated LAB row is located below it with the exception of the bottom I/O band row. The bottom I/O band is located at the bottom periphery of the device, hence its associated LAB row is located above it. Figure 29 shows an example of an I/O band to associated LAB row interconnect in a Mercury device.

There is a maximum of two IOEs associated with each LAB in the associated LAB row. The local interconnect of the associated LAB drives the IOEs. Since local interconnect is shared with the LAB neighbor, any given LAB can directly drive up to four IOEs. The local interconnect drives the data and OE signals when the IOE is used as an output or bidirectional pin.

#### Note to Figure 29:

(1)  $IN_A$ : unregistered input;  $IN_B$ : registered/unregistered input;  $IN_C$ : registered/unregistered input or OE register output in DDR mode.

The IOEs drive registered or combinatorial versions of input data into the device. The unregistered input data can be driven to the local interconnect (for fast input setup), row and priority row interconnect, and column and priority column interconnects. The registered data can also be driven to the same row and column resources. The OE register output can be fed back through column and row interconnects to implement DDR I/O pins.

## Dedicated Fast Lines & I/O Pins

Mercury devices incorporate dedicated bidirectional pins for signals with high internal fanout, such as PCI control signals. These pins are called dedicated fast I/O pins (FAST1, FAST2, FAST3, FAST4, FAST5, and FAST6) and can drive the six global fast lines throughout the device, ideal for fast clock, clock enable, clear, preset, or high fanout logic signal distribution. The dedicated fast I/O pins have the same IOE as a regular I/O pin. The dedicated fast lines can also be driven by a LE local interconnect to generate internal global signals.