### Welcome to <u>E-XFL.COM</u>

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | 12V1                                                                    |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 25MHz                                                                   |

| Connectivity               | IrDA, LINbus, SCI, SPI                                                  |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 16                                                                      |

| Program Memory Size        | 32KB (32K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 128 × 8                                                                 |

| RAM Size                   | 2K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 5.5V                                                            |

| Data Converters            | A/D 2x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 32-LQFP                                                                 |

| Supplier Device Package    | 32-LQFP (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12vr32f0clcr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 8.4 | Function | nal Description   |  |

|-----|----------|-------------------|--|

|     |          | Analog Sub-Block  |  |

|     | 8.4.2    | Digital Sub-Block |  |

| 8.5 | Resets   | ~                 |  |

| 8.6 | Interrup | ts                |  |

# Chapter 9

# Pulse-Width Modulator (S12PWM8B8CV2)

| 9.1 | Introduc | tion                            | . 295 |

|-----|----------|---------------------------------|-------|

|     | 9.1.1    | Features                        | . 295 |

|     | 9.1.2    | Modes of Operation              | . 295 |

|     | 9.1.3    | Block Diagram                   | . 296 |

| 9.2 | External | Signal Description              | . 296 |

|     | 9.2.1    | PWM7 - PWM0 — PWM Channel 7 - 0 | . 297 |

| 9.3 | Memory   | Map and Register Definition     | . 297 |

|     | 9.3.1    | Module Memory Map               | . 297 |

|     | 9.3.2    | Register Descriptions           | . 297 |

| 9.4 | Function | nal Description                 | . 311 |

|     | 9.4.1    | PWM Clock Select                | . 311 |

|     | 9.4.2    | PWM Channel Timers              | . 315 |

| 9.5 | Resets . |                                 | . 323 |

| 9.6 | Interrup | ts                              | . 324 |

# Chapter 10

# Serial Communication Interface (S12SCIV6)

| 10.1 | Introduction                                     | . 325 |

|------|--------------------------------------------------|-------|

|      | 10.1.1 Glossary                                  | . 325 |

|      | 10.1.2 Features                                  | . 326 |

|      | 10.1.3 Modes of Operation                        | . 326 |

|      | 10.1.4 Block Diagram                             | . 327 |

| 10.2 | External Signal Description                      | . 328 |

|      | 10.2.1 TXD — Transmit Pin                        | . 328 |

|      | 10.2.2 RXD — Receive Pin                         | . 328 |

| 10.3 | Memory Map and Register Definition               | . 328 |

|      | 10.3.1 Module Memory Map and Register Definition | . 328 |

|      | 10.3.2 Register Descriptions                     | . 329 |

| 10.4 | Functional Description                           | . 341 |

|      | 10.4.1 Infrared Interface Submodule              | . 342 |

|      | 10.4.2 LIN Support                               | . 342 |

|      | 10.4.3 Data Format                               | . 343 |

|      | 10.4.4 Baud Rate Generation                      | . 344 |

|      | 10.4.5 Transmitter                               | . 345 |

|      | 10.4.6 Receiver                                  | . 350 |

|      | 10.4.7 Single-Wire Operation                     | . 358 |

|      |                                                  |       |

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2<br>DDRS | <b>Data Direction Register port S</b> —<br>This bit determines whether the associated pin is an input or output. The enabled API_EXTCLK function forces the I/O state to output. Depending on the configuration of the enabled SPI the I/O state will be forced to be input or output. The routed SCI1 function forces the I/O state to input if enabled. The routed PWM function forces the I/O state to output if enabled. In these cases the data direction bit will not change. The routed ETRIG function has no effect on the I/O state.<br>1 Associated pin is configured as output<br>0 Associated pin is configured as input |

| 1<br>DDRS | Data Direction Register port S —         This bit determines whether the associated pin is an input or output.         Depending on the configuration of the enabled SCI the I/O state will be forced to be input or output. The enabled routed LINPHY forces the I/O state to be an output (LPDR[LPDR1]). In these cases the data direction bit will not change.         1 Associated pin is configured as output         0 Associated pin is configured as input                                                                                                                                                                   |

| 0<br>DDRS | Data Direction Register port S —         This bit determines whether the associated pin is an input or output.         Depending on the configuration of the enabled SCI the I/O state will be forced to be input or output. In this case the data direction bit will not change.         1 Associated pin is configured as output         0 Associated pin is configured as input                                                                                                                                                                                                                                                   |

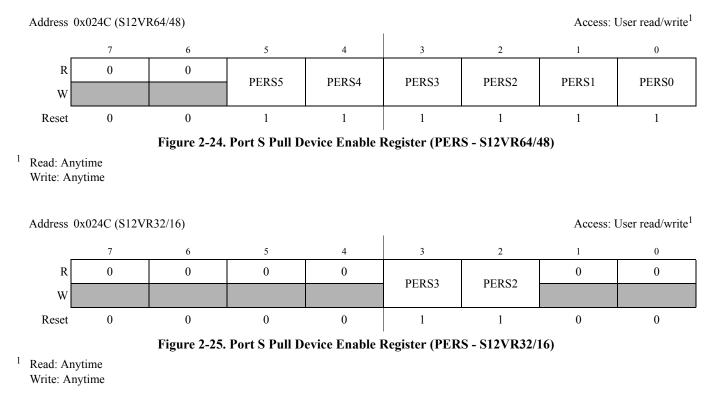

## 2.3.22 Port S Pull Device Enable Register (PERS)

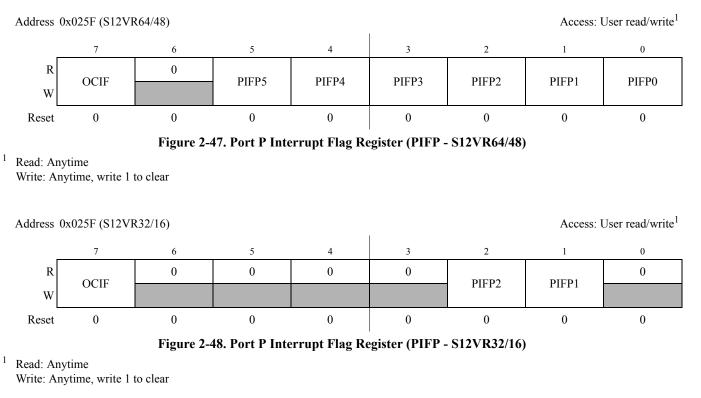

## 2.3.33 Port P Interrupt Flag Register (PIFP)

#### Table 2-32. PIFP Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>OCIF   | Over-Current Interrupt Flag register port P —<br>This flag asserts if an over-current condition is detected on PP2 (Section 2.4.4.3, "Over-Current Interrupt and Protection").<br>1 PP2 Over-current event occurred<br>0 No PP2 over-current event occurred                                                                                                                                                  |

| 5-0<br>PIFP | <b>Pin Interrupt Flag</b> register port P —<br>This flag asserts after a valid active edge was detected on the related pin (Section 2.4.4, "Interrupts"). This can be a rising or a falling edge based on the state of the polarity select register. An interrupt will occur if the associated interrupt enable bit is set.<br>1 Active edge on the associated bit has occurred<br>0 No active edge occurred |

#### Port Integration Module (S12VRPIMV3)

voltage divider can be bypassed (PTAL[PTADIRL]=1). Additionally in latter case the impedance converter in the ADC signal path can be configured to be used or bypassed in direct input mode (PTAL[PTABYPL]).

Out of reset the digital input buffer of the selected pin is disabled to avoid shoot-through current. Pin interrupts can only be generated if DIENL[x]=1.

In stop mode the digital input buffer is enabled if DIENL[x]=1 or if the PTAL[PTTEL] bit is set to support wakeup functionality.

Table 2-49 shows the HVI input configuration depending on register bits and operation mode.

| Mode     | DIENL | PTAENL | Digital Input    | Analog Input | Resulting Function                                                                                                                                    |

|----------|-------|--------|------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Run/Wait | 0     | 0      | off              | off          | Input disabled (Reset)                                                                                                                                |

|          | 0     | 1      | off <sup>1</sup> | enabled      | Analog input, interrupt not supported                                                                                                                 |

|          | 1     | 0      | enabled          | off          | Digital input, interrupt supported                                                                                                                    |

|          | 1     | 1      | off <sup>1</sup> | enabled      | Analog input, interrupt not supported                                                                                                                 |

| Stop     | 0     | Х      | off              | off          | If PTAL[PTTEL] is set:<br>input enabled, wakeup from stop supported.<br>If PTAL[PTTEL] is cleared:<br>input disabled, wakeup from stop not supported. |

|          | 1     | X      | enabled          | off          | Digital input, wakeup from stop supported                                                                                                             |

Table 2-49. HVI Input Configurations

Enabled if (PTAL[PTTEL]=1 & PTAL[PTADIRL]=0)

### NOTE

An external resistor  $R_{EXT_HVI}$  must always be connected to the high-voltage inputs to protect the device pins from fast transients and to achieve the specified pin input divider ratios when using the HVI in analog mode.

### 2.4.3.7 **Port AD**

1

This port is associated with the ADC.

Port AD pins can be used for either general-purpose I/O, or with the ADC subsystem.

### 2.4.4 Interrupts

This section describes the interrupts generated by the PIM and their individual sources. Vector addresses and interrupt priorities are defined at MCU level.

| Module Interrupt Sources | Local Enable<br>(S12VR64/48) | Local Enable<br>(S12VR32/16) |  |

|--------------------------|------------------------------|------------------------------|--|

| XIRQ                     | None                         | None                         |  |

### Table 2-50. PIM Interrupt Sources

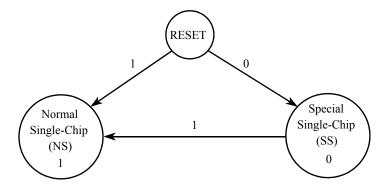

### Read: Anytime.

Write: Only if a transition is allowed (see Figure 3-4).

The MODC bit of the MODE register is used to select the MCU's operating mode.

Table 3-4. MODE Field Descriptions

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>MODC | <b>Mode Select Bit</b> — This bit controls the current operating mode during RESET high (inactive). The external mode pin MODC determines the operating mode during RESET low (active). The state of the pin is registered into the respective register bit after the RESET signal goes inactive (see Figure 3-4). Write restrictions exist to disallow transitions between certain modes. Figure 3-4 illustrates all allowed mode changes. Attempting non authorized transitions will not change the MODE bit, but it will block further writes to the register bit except in special modes. Write accesses to the MODE register are blocked when the device is secured. |

Figure 3-4. Mode Transition Diagram when MCU is Unsecured

## **3.3.2.2** Direct Page Register (DIRECT)

Address: 0x0011

|        | 7    | 6    | 5    | 4    | 3    | 2    | 1   | 0   |

|--------|------|------|------|------|------|------|-----|-----|

| R<br>W | DP15 | DP14 | DP13 | DP12 | DP11 | DP10 | DP9 | DP8 |

| Reset  | 0    | 0    | 0    | 0    | 0    | 0    | 0   | 0   |

Figure 3-5. Direct Register (DIRECT)

Read: Anytime

Write: anytime in special SS, write-once in NS.

This register determines the position of the 256 Byte direct page within the memory map. It is valid for both global and local mapping scheme.

MC9S12VR Family Reference Manual, Rev. 4.2

| TCTRIM[4:0]  | IRC1M Indicative relative TC variation | IRC1M indicative frequency drift for<br>relative TC variation |  |  |

|--------------|----------------------------------------|---------------------------------------------------------------|--|--|

| 00000        | 0 (nominal TC of the IRC)              | 0%                                                            |  |  |

| 00001        | -0.27%                                 | -0.5%                                                         |  |  |

| 00010        | -0.54%                                 | -0.9%                                                         |  |  |

| 00011        | -0.81%                                 | -1.3%                                                         |  |  |

| 00100        | -1.08%                                 | -1.7%                                                         |  |  |

| 00101        | -1.35%                                 | -2.0%                                                         |  |  |

| 00110        | -1.63%                                 | -2.2%                                                         |  |  |

| 00111        | -1.9%                                  | -2.5%                                                         |  |  |

| 01000        | -2.20%                                 | -3.0%                                                         |  |  |

| 01001        | -2.47%                                 | -3.4%                                                         |  |  |

| 01010        | -2.77%                                 | -3.9%                                                         |  |  |

| 01011        | -3.04                                  | -4.3%                                                         |  |  |

| 01100        | -3.33%                                 | -4.7%                                                         |  |  |

| 01101        | -3.6%                                  | -5.1%                                                         |  |  |

| 01110        | -3.91%                                 | -5.6%                                                         |  |  |

| 01111        | -4.18%                                 | -5.9%                                                         |  |  |

| 10000        | 0 (nominal TC of the IRC)              | 0%                                                            |  |  |

| 10001        | +0.27%                                 | +0.5%                                                         |  |  |

| 10010        | +0.54%                                 | +0.9%                                                         |  |  |

| 10011        | +0.81%                                 | +1.3%                                                         |  |  |

| 10100        | +1.07%                                 | +1.7%                                                         |  |  |

| 10101        | +1.34%                                 | +2.0%                                                         |  |  |

| 10110        | +1.59%                                 | +2.2%                                                         |  |  |

| 10111        | +1.86%                                 | +2.5%                                                         |  |  |

| 11000        | +2.11%                                 | +3.0%                                                         |  |  |

| 11001        | +2.38%                                 | +3.4%                                                         |  |  |

| 11010 +2.62% |                                        | +3.9%                                                         |  |  |

| 11011        | +2.89%                                 | +4.3%                                                         |  |  |

| 11100        | +3.12%                                 | +4.7%                                                         |  |  |

| 11101        | +3.39%                                 | +5.1%                                                         |  |  |

| 11110        | +3.62%                                 | +5.6%                                                         |  |  |

| 11111        | +3.89%                                 | +5.9%                                                         |  |  |

| Table 4-27. TC trimmin | g of the frequency | y of the IRC1M at ambient temperature |

|------------------------|--------------------|---------------------------------------|

|                        |                    |                                       |

### NOTE

Since the IRC1M frequency is not a linear function of the temperature, but more like a parabola, the above relative variation is only an indication and should be considered with care.

### NOTE

The ACK pulse does not provide a time out. This means for the GO\_UNTIL command that it can not be distinguished if a stop or wait has been executed (command discarded and ACK not issued) or if the "UNTIL" condition (BDM active) is just not reached yet. Hence in any case where the ACK pulse of a command is not issued the possible pending command should be aborted before issuing a new command. See the handshake abort procedure described in Section 5.4.8, "Hardware Handshake Abort Procedure".

### 5.4.8 Hardware Handshake Abort Procedure

The abort procedure is based on the SYNC command. In order to abort a command, which had not issued the corresponding ACK pulse, the host controller should generate a low pulse in the BKGD pin by driving it low for at least 128 serial clock cycles and then driving it high for one serial clock cycle, providing a speedup pulse. By detecting this long low pulse in the BKGD pin, the target executes the SYNC protocol, see Section 5.4.9, "SYNC — Request Timed Reference Pulse", and assumes that the pending command and therefore the related ACK pulse, are being aborted. Therefore, after the SYNC protocol has been completed the host is free to issue new BDM commands. For BDM firmware READ or WRITE commands it can not be guaranteed that the pending command is aborted when issuing a SYNC before the corresponding ACK pulse. There is a short latency time from the time the READ or WRITE access begins until it is finished and the corresponding ACK pulse is issued. The latency time depends on the firmware READ or WRITE command that is issued and on the selected bus clock rate. When the SYNC command starts during this latency time the READ or WRITE command will not be aborted, but the corresponding ACK pulse will be aborted. A pending GO, TRACE1 or GO\_UNTIL command can not be aborted. Only the corresponding ACK pulse can be aborted by the SYNC command.

Although it is not recommended, the host could abort a pending BDM command by issuing a low pulse in the BKGD pin shorter than 128 serial clock cycles, which will not be interpreted as the SYNC command. The ACK is actually aborted when a negative edge is perceived by the target in the BKGD pin. The short abort pulse should have at least 4 clock cycles keeping the BKGD pin low, in order to allow the negative edge to be detected by the target. In this case, the target will not execute the SYNC protocol but the pending command will be aborted along with the ACK pulse. The potential problem with this abort procedure is when there is a conflict between the ACK pulse and the short abort pulse. In this case, the target may not perceive the abort pulse. The worst case is when the pending command is a read command (i.e., READ\_BYTE). If the abort pulse is not perceived by the target the host to retrieve the accessed memory byte. In this case, host and target will run out of synchronism. However, if the command to be aborted is not a read command the short abort pulse could be used. After a command is aborted the target assumes the next negative edge, after the abort pulse, is the first bit of a new BDM command.

### NOTE

The details about the short abort pulse are being provided only as a reference for the reader to better understand the BDM internal behavior. It is not recommended that this procedure be used in a real application.

Analog-to-Digital Converter (ADC12B6CV2)

## 8.3.2.7 ATD Status Register 0 (ATDSTAT0)

This register contains the Sequence Complete Flag, overrun flags for external trigger and FIFO mode, and the conversion counter.

Module Base + 0x0006

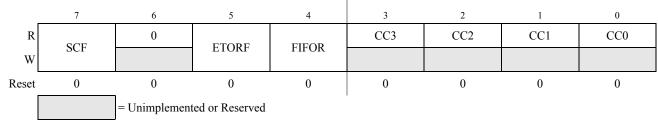

Figure 8-9. ATD Status Register 0 (ATDSTAT0)

Read: Anytime

Write: Anytime (No effect on (CC3, CC2, CC1, CC0))

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7<br>SCF   | Sequence Complete Flag — This flag is set upon completion of a conversion sequence. If conversion sequences are continuously performed (SCAN=1), the flag is set after each one is completed. This flag is cleared when one of the following occurs: <ul> <li>A) Write "1" to SCF</li> <li>B) Write to ATDCTL5 (a new conversion sequence is started)</li> <li>C) If AFFC=1 and a result register is read</li> <li>0 Conversion sequence not completed</li> <li>1 Conversion sequence has completed</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 5<br>ETORF | <ul> <li>External Trigger Overrun Flag — While in edge sensitive mode (ETRIGLE=0), if additional active edges are detected while a conversion sequence is in process the overrun flag is set. This flag is cleared when one of the following occurs:         <ul> <li>A) Write "1" to ETORF</li> <li>B) Write to ATDCTL0,1,2,3,4, ATDCMPE or ATDCMPHT (a conversion sequence is aborted)</li> <li>C) Write to ATDCTL5 (a new conversion sequence is started)</li> <li>No External trigger overrun error has occurred</li> <li>External trigger overrun error has occurred</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                    |  |

| 4<br>FIFOR | Result Register Overrun Flag — This bit indicates that a result register has been written to before its associated conversion complete flag (CCF) has been cleared. This flag is most useful when using the FIFO mode because the flag potentially indicates that result registers are out of sync with the input channels. However, it is also practical for non-FIFO modes, and indicates that a result register has been overwritten before it has been read (i.e. the old data has been lost). This flag is cleared when one of the following occurs: <ul> <li>A) Write "1" to FIFOR</li> <li>B) Write to ATDCTL0,1,2,3,4, ATDCMPE or ATDCMPHT (a conversion sequence is aborted)</li> <li>C) Write to ATDCTL5 (a new conversion sequence is started)</li> <li>No overrun has occurred</li> <li>Overrun condition exists (result register has been written while associated CCFx flag was still set)</li> </ul> |  |

| Field          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3–0<br>CC[3:0] | <b>Conversion Counter</b> — These 4 read-only bits are the binary value of the conversion counter. The conversion counter points to the result register that will receive the result of the current conversion. E.g. CC3=0, CC2=1, CC1=1, CC0=0 indicates that the result of the current conversion will be in ATD Result Register 6. If in non-FIFO mode (FIFO=0) the conversion counter is initialized to zero at the beginning and end of the conversion sequence. If in FIFO mode (FIFO=1) the register counter is not initialized. The conversion counter wraps around when its maximum value is reached. Aborting a conversion or starting a new conversion clears the conversion counter even if FIFO=1. |

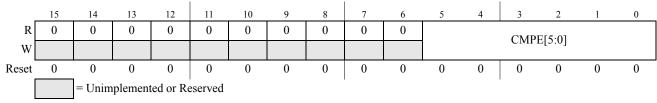

### 8.3.2.8 ATD Compare Enable Register (ATDCMPE)

Writes to this register will abort current conversion sequence.

Read: Anytime

Write: Anytime

Module Base + 0x0008

### Figure 8-10. ATD Compare Enable Register (ATDCMPE)

#### Table 8-17. ATDCMPE Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                              |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 5–0<br>CMPE[5:0] | Compare Enable for Conversion Number $n$ ( $n=5, 4, 3, 2, 1, 0$ ) of a Sequence ( <i>n conversion number, NOT channel number!</i> ) — These bits enable automatic compare of conversion results individually for conversions of a sequence. The sense of each comparison is determined by the CMPHT[ $n$ ] bit in the ATDCMPHT register. |  |

|                  | <ul> <li>For each conversion number with CMPE[n]=1 do the following:</li> <li>1) Write compare value to ATDDRn result register</li> <li>2) Write compare operator with CMPHT[n] in ATDCPMHT register</li> </ul>                                                                                                                          |  |

|                  | <ul> <li>CCF[n] in ATDSTAT2 register will flag individual success of any comparison.</li> <li>0 No automatic compare</li> <li>1 Automatic compare of results for conversion n of a sequence is enabled.</li> </ul>                                                                                                                       |  |

Timer Module (TIM16B4CV3)

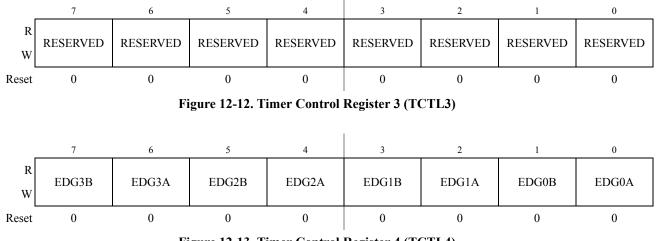

### 12.3.2.7 Timer Control Register 3/Timer Control Register 4 (TCTL3 and TCTL4)

Figure 12-13. Timer Control Register 4 (TCTL4)

### Read: Anytime

Write: Anytime.

### Table 12-8. TCTL3/TCTL4 Field Descriptions

Note: Writing to unavailable bits has no effect. Reading from unavailable bits return a zero.

| Field | Description                                                                                                       |

|-------|-------------------------------------------------------------------------------------------------------------------|

| 3:0   | Input Capture Edge Control — These four pairs of control bits configure the input capture edge detector circuits. |

| EDGnB |                                                                                                                   |

| EDGnA |                                                                                                                   |

#### Table 12-9. Edge Detector Circuit Configuration

| EDGnB | EDGnA | Configuration                           |

|-------|-------|-----------------------------------------|

| 0     | 0     | Capture disabled                        |

| 0     | 1     | Capture on rising edges only            |

| 1     | 0     | Capture on falling edges only           |

| 1     | 1     | Capture on any edge (rising or falling) |

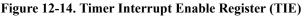

## **12.3.2.8** Timer Interrupt Enable Register (TIE)

Read: Anytime

MC9S12VR Family Reference Manual, Rev. 4.2

### Timer Module (TIM16B4CV3)

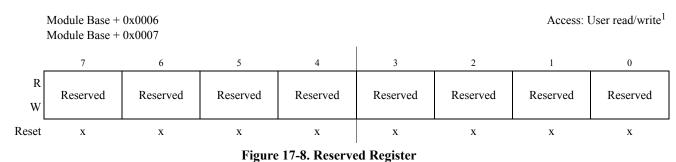

## 12.3.2.13 Output Compare Pin Disconnect Register(OCPD)

Figure 12-20. Output Compare Pin Disconnect Register (OCPD)

Read: Anytime

Write: Anytime

All bits reset to zero.

### Table 12-15. OCPD Field Description

Note: Writing to unavailable bits has no effect. Reading from unavailable bits return a zero.

| Field     | Description                                                                                                                               |  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------|--|

| 3:0       | Output Compare Pin Disconnect Bits                                                                                                        |  |

| OCPD[3:0] | 0 Enables the timer channel port. Output Compare action will occur on the channel pin. These bits do not affect the input capture .       |  |

|           | 1 Disables the timer channel port. Output Compare action will not occur on the channel pin, but the output compare flag still become set. |  |

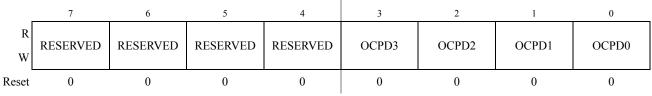

## 12.3.2.14 Precision Timer Prescaler Select Register (PTPSR)

Figure 12-21. Precision Timer Prescaler Select Register (PTPSR)

Read: Anytime

Write: Anytime

All bits reset to zero.

### Table 12-16. PTPSR Field Descriptions

| Field            | Description                                                                                                                                                                                                                                     |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTPS[7:0] | <b>Precision Timer Prescaler Select Bits</b> — These eight bits specify the division rate of the main Timer prescaler. These are effective only when the PRNT bit of TSCR1 is set to 1. Table 12-17 shows some selection examples in this case. |

|                  | The newly selected prescale factor will not take effect until the next synchronized edge where all prescale counter stages equal zero.                                                                                                          |

The Prescaler can be calculated as follows depending on logical value of the PTPS[7:0] and PRNT bit:

PRNT = 1: Prescaler = PTPS[7:0] + 1

MC9S12VR Family Reference Manual, Rev. 4.2

| Field      | Description                                                                                                                                                         |  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1<br>BVHIF | <b>BATS Interrupt Flag High Detect</b> — The flag is set to 1 when BVHC status bit changes.                                                                         |  |

|            | <ol> <li>No change of the BVHC status bit since the last clearing of the flag.</li> <li>BVHC status bit has changed since the last clearing of the flag.</li> </ol> |  |

| 0<br>BVLIF | <b>BATS Interrupt Flag Low Detect</b> — The flag is set to 1 when BVLC status bit changes.                                                                          |  |

|            | <ol> <li>No change of the BVLC status bit since the last clearing of the flag.</li> <li>BVLC status bit has changed since the last clearing of the flag.</li> </ol> |  |

### Table 17-5. BATIF Register Field Descriptions

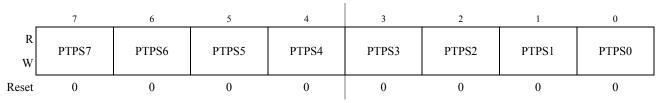

## 17.3.2.5 Reserved Register

Read: Anytime Write: Only in special mode

### NOTE

These reserved registers are designed for factory test purposes only and are not intended for general user access. Writing to these registers when in special mode can alter the module's functionality.

# 17.4 Functional Description

## 17.4.1 General

The BATS module allows measuring voltages on the VSENSE and VSUP pins. The VSENSE pin is implemented to allow measurement of the supply Line (Battery) Voltage  $V_{BAT}$  directly. By bypassing the device supply capacitor and the external reversed battery protection diode this pin allows to detect under/over voltage conditions without delay. A series resistor ( $R_{VSENSE_R}$ ) is required to protect the VSENSE pin from fast transients.

The voltage at the VSENSE or VSUP pin can be routed via an internal voltage divider to an internal Analog to Digital Converter Channel. Also the BATS module can be configured to generate a low and high voltage interrupt based on VSENSE or VSUP. The trigger level of the high and low interrupt are selectable.

In a typical application, the module could be used as follows: The voltage at VSENSE is observed via usage of the interrupt feature (BSESE=1, BVHIE=1), while the VSUP pin voltage is routed to the ADC to allow regular measurement (BSUAE=1).

### 18.4.4.4 P-Flash Commands

Table 18-28 summarizes the valid P-Flash commands along with the effects of the commands on the P-Flash block and other resources within the Flash module.

| FCMD | Command                         | Function on P-Flash Memory                                                                                                                                                                                                                     |  |

|------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0x01 | Erase Verify All<br>Blocks      | Verify that all P-Flash (and EEPROM) blocks are erased.                                                                                                                                                                                        |  |

| 0x02 | Erase Verify Block              | Verify that a P-Flash block is erased.                                                                                                                                                                                                         |  |

| 0x03 | Erase Verify P-Flash<br>Section | Verify that a given number of words starting at the address provided are erased.                                                                                                                                                               |  |

| 0x04 | Read Once                       | Read a dedicated 64 byte field in the nonvolatile information register in P-Flash block that was previously programmed using the Program Once command.                                                                                         |  |

| 0x06 | Program P-Flash                 | Program a phrase in a P-Flash block.                                                                                                                                                                                                           |  |

| 0x07 | Program Once                    | Program a dedicated 64 byte field in the nonvolatile information register in P-Flash block that is allowed to be programmed only once.                                                                                                         |  |

| 0x08 | Erase All Blocks                | Erase all P-Flash (and EEPROM) blocks.<br>An erase of all Flash blocks is only possible when the FPLDIS, FPHDIS, and FPOPEN bits in the<br>FPROT register and the DPOPEN bit in the EEPROT register are set prior to launching the<br>command. |  |

| 0x09 | Erase Flash Block               | Erase a P-Flash (or EEPROM) block.<br>An erase of the full P-Flash block is only possible when FPLDIS, FPHDIS and FPOPEN bits in<br>the FPROT register are set prior to launching the command.                                                 |  |

| 0x0A | Erase P-Flash Sector            | Erase all bytes in a P-Flash sector.                                                                                                                                                                                                           |  |

| 0x0B | Unsecure Flash                  | Supports a method of releasing MCU security by erasing all P-Flash (and EEPROM) blocks and verifying that all P-Flash (and EEPROM) blocks are erased.                                                                                          |  |

| 0x0C | Verify Backdoor<br>Access Key   | Supports a method of releasing MCU security by verifying a set of security keys.                                                                                                                                                               |  |

| 0x0D | Set User Margin<br>Level        | Specifies a user margin read level for all P-Flash blocks.                                                                                                                                                                                     |  |

| 0x0E | Set Field Margin<br>Level       | Specifies a field margin read level for all P-Flash blocks (special modes only).                                                                                                                                                               |  |

Table 18-28. P-Flash Commands

## 18.4.4.5 EEPROM Commands

Table 18-29 summarizes the valid EEPROM commands along with the effects of the commands on the EEPROM block.

| FCMD | Command                    | Function on EEPROM Memory                               |

|------|----------------------------|---------------------------------------------------------|

| 0x01 | Erase Verify All<br>Blocks | Verify that all EEPROM (and P-Flash) blocks are erased. |

| 0x02 | Erase Verify Block         | Verify that the EEPROM block is erased.                 |

#### Table 18-29. EEPROM Commands

#### 64 KByte Flash Module (S12FTMRG64K512V1) for S12VR64

| CCOBIX[2:0] | FCCOB Parameters                                  |                                                   |  |  |  |  |

|-------------|---------------------------------------------------|---------------------------------------------------|--|--|--|--|

| 000         | 0x09                                              | Global address [17:16] to identify<br>Flash block |  |  |  |  |

| 001         | Global address [15:0] in Flash block to be erased |                                                   |  |  |  |  |

Table 18-46. Erase Flash Block Command FCCOB Requirements

Upon clearing CCIF to launch the Erase Flash Block command, the Memory Controller will erase the selected Flash block and verify that it is erased. The CCIF flag will set after the Erase Flash Block operation has completed.

| Register | Error Bit | Error Condition                                                                                                                                                   |  |

|----------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|          |           | Set if CCOBIX[2:0] != 001 at command launch                                                                                                                       |  |

|          |           | Set if command not available in current mode (see Table 18-27)                                                                                                    |  |

|          | ACCERR    | Set if an invalid global address [17:16] is supplied<br>Set if the supplied P-Flash address is not phrase-aligned or if the EEPROM address is not<br>word-aligned |  |

| FSTAT    |           |                                                                                                                                                                   |  |

|          | FPVIOL    | Set if an area of the selected Flash block is protected                                                                                                           |  |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                                                                                               |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation                                                                               |  |

Table 18-47. Erase Flash Block Command Error Handling

### 18.4.6.9 Erase P-Flash Sector Command

The Erase P-Flash Sector operation will erase all addresses in a P-Flash sector.

Table 18-48. Erase P-Flash Sector Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters                                                                                                                          |                                                                  |  |  |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--|--|--|--|

| 000         | 0x0A                                                                                                                                      | Global address [17:16] to identify<br>P-Flash block to be erased |  |  |  |  |

| 001         | Global address [15:0] anywhere within the sector to be erased.<br>Refer to Section 18.1.2.1 P-Flash Features for the P-Flash sector size. |                                                                  |  |  |  |  |

Upon clearing CCIF to launch the Erase P-Flash Sector command, the Memory Controller will erase the selected Flash sector and then verify that it is erased. The CCIF flag will be set after the Erase P-Flash Sector operation has completed.

| Field            | Description                                                                                                                                                                                                                                                                                                                        |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6<br>FDIVLCK     | <ul> <li>Clock Divider Locked</li> <li>FDIV field is open for writing</li> <li>FDIV value is locked and cannot be changed. Once the lock bit is set high, only reset can clear this bit and restore writability to the FDIV field in normal mode.</li> </ul>                                                                       |

| 5–0<br>FDIV[5:0] | <b>Clock Divider Bits</b> — FDIV[5:0] must be set to effectively divide BUSCLK down to 1 MHz to control timed events during Flash program and erase algorithms. Table 19-8 shows recommended values for FDIV[5:0] based on the BUSCLK frequency. Please refer to Section 19.4.4, "Flash Command Operations," for more information. |

| BUSCLK Frequency (MHz) |                  | EDIV[5.0] | BUSCLK Fre       | BUSCLK Frequency (MHz) |           |  |

|------------------------|------------------|-----------|------------------|------------------------|-----------|--|

| MIN <sup>1</sup>       | MAX <sup>2</sup> | FDIV[5:0] | MIN <sup>1</sup> | MAX <sup>2</sup>       | FDIV[5:0] |  |

| 1.0                    | 1.6              | 0x00      | 16.6             | 17.6                   | 0x10      |  |

| 1.6                    | 2.6              | 0x01      | 17.6             | 18.6                   | 0x11      |  |

| 2.6                    | 3.6              | 0x02      | 18.6             | 19.6                   | 0x12      |  |

| 3.6                    | 4.6              | 0x03      | 19.6             | 20.6                   | 0x13      |  |

| 4.6                    | 5.6              | 0x04      | 20.6             | 21.6                   | 0x14      |  |

| 5.6                    | 6.6              | 0x05      | 21.6             | 22.6                   | 0x15      |  |

| 6.6                    | 7.6              | 0x06      | 22.6             | 23.6                   | 0x16      |  |

| 7.6                    | 8.6              | 0x07      | 23.6             | 24.6                   | 0x17      |  |

| 8.6                    | 9.6              | 0x08      | 24.6             | 25.6                   | 0x18      |  |

| 9.6                    | 10.6             | 0x09      |                  |                        |           |  |

| 10.6                   | 11.6             | 0x0A      |                  |                        |           |  |

| 11.6                   | 12.6             | 0x0B      |                  |                        |           |  |

| 12.6                   | 13.6             | 0x0C      |                  |                        |           |  |

| 13.6                   | 14.6             | 0x0D      |                  |                        |           |  |

| 14.6                   | 15.6             | 0x0E      |                  |                        |           |  |

| 15.6                   | 16.6             | 0x0F      |                  |                        |           |  |

Table 19-8. FDIV values for various BUSCLK Frequencies

$\overline{1}$  BUSCLK is Greater Than this value.

<sup>2</sup> BUSCLK is Less Than or Equal to this value.

## 19.3.2.2 Flash Security Register (FSEC)

The FSEC register holds all bits associated with the security of the MCU and Flash module.

#### 32 KByte Flash Module (S12FTMRG32K128V1) for S12VR32

Upon clearing CCIF to launch the Set Field Margin Level command, the Memory Controller will set the Table 19-57. Set Field Margin Level Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters      |                                                      |  |  |  |  |

|-------------|-----------------------|------------------------------------------------------|--|--|--|--|

| 000         | 0x0E                  | Flash block selection code [1:0]. See<br>Table 19-34 |  |  |  |  |

| 001         | Margin level setting. |                                                      |  |  |  |  |

field margin level for the targeted block and then set the CCIF flag.

### NOTE

When the EEPROM block is targeted, the EEPROM field margin levels are applied only to the EEPROM reads. However, when the P-Flash block is targeted, the P-Flash field margin levels are applied to both P-Flash and EEPROM reads. It is not possible to apply field margin levels to the P-Flash block only.

Valid margin level settings for the Set Field Margin Level command are defined in Table 19-58.

| CCOB<br>(CCOBIX=001) | Level Description                 |

|----------------------|-----------------------------------|

| 0x0000               | Return to Normal Level            |

| 0x0001               | User Margin-1 Level <sup>1</sup>  |

| 0x0002               | User Margin-0 Level <sup>2</sup>  |

| 0x0003               | Field Margin-1 Level <sup>1</sup> |

| 0x0004               | Field Margin-0 Level <sup>2</sup> |

### Table 19-58. Valid Set Field Margin Level Settings

<sup>1</sup> Read margin to the erased state

<sup>2</sup> Read margin to the programmed state

#### Table 19-59. Set Field Margin Level Command Error Handling

| Register | Error Bit | Error Condition                                                              |  |  |  |

|----------|-----------|------------------------------------------------------------------------------|--|--|--|

|          |           | Set if CCOBIX[2:0] != 001 at command launch                                  |  |  |  |

|          | ACCERR    | Set if command not available in current mode (see Table 19-27)               |  |  |  |

|          | ACCERR    | Set if an invalid FlashBlockSelectionCode[1:0] is supplied (See Table 19-34) |  |  |  |

| FSTAT    |           | Set if an invalid margin level setting is supplied                           |  |  |  |

|          | FPVIOL    | None                                                                         |  |  |  |

|          | MGSTAT1   | None                                                                         |  |  |  |

|          | MGSTAT0   | None                                                                         |  |  |  |

**IRC Electrical Specifications**

#### Table I-2. Static Electrical Characteristics - Supply Voltage Sense - (BATS).

Characteristics noted under conditions  $5.5V \le VSUP \le 18 \text{ V}$ ,  $-40^{\circ}C \le T_J \le 150^{\circ}C^1$  unless otherwise noted. Typical values noted reflect the approximate parameter mean at  $T_A = 25^{\circ}C^2$  under nominal conditions unless otherwise noted. All parameters in this table assume a in series connected  $R_{VSENSE_R}$  at VSENSE pin unless otherwise noted and are valid on input voltage of  $R_{VSENSE_R}$  and not on VSENSE pin.

| Num | Ratings                                                                        | Symbol                | Min | Тур | Max  | Unit |

|-----|--------------------------------------------------------------------------------|-----------------------|-----|-----|------|------|

| 9   | VSENSE Series Resistor                                                         | R <sub>VSENSE_R</sub> | 9.5 | 10  | 10.5 | kΩ   |

|     | Required to be placed externally at VSENSE pin.                                |                       |     |     |      |      |

| 10  | VSENSE Impedance                                                               | R <sub>VSEN_IMP</sub> | -   | 350 | -    | kΩ   |

|     | If path to ground is enabled. Value at VSENSE pin. $R_{VSENSE_R}$ is excluded. |                       |     |     |      |      |

| 11  | VSENSE Input Capacitance                                                       | C <sub>VSEN_IN</sub>  | -   | 8   | -    | pF   |

<sup>1</sup> T<sub>J</sub>: Junction Temperature

<sup>2</sup> T<sub>A</sub>: Ambient Temperature

$^{3}$  V<sub>ADC</sub>: Voltage accessible at the ATD input channel

## I.3 Dynamic Electrical Characteristics

#### Table I-3. Dynamic Electrical Characteristics - Supply Voltage Sense - (BATS).

|     | Characteristics noted under conditions $5.5V \le VSUP \le 18 \text{ V}$ , $-40^{\circ}C \le T_J \le 150^{\circ}C^1$ unless otherwise noted. Typical values noted reflect the approximate parameter mean at $T_A = 25^{\circ}C^2$ under nominal conditions unless otherwise noted. |                     |     |     |     |      |  |  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----|-----|-----|------|--|--|

| Num | Ratings                                                                                                                                                                                                                                                                           | Symbol              | Min | Тур | Max | Unit |  |  |

| 1   | Enable Stabilisation Time                                                                                                                                                                                                                                                         | T <sub>EN_UNC</sub> | _   | 1   | -   | μs   |  |  |

| 2   | Voltage Warning Low Pass Filter                                                                                                                                                                                                                                                   | $f_{VWLP_filter}$   | -   | 0.5 | Ι   | MHz  |  |  |

<sup>1</sup> T<sub>J</sub>: Junction Temperature

<sup>2</sup> T<sub>A</sub>: Ambient Temperature

#### **XOSCLCP Electrical Specifications**

## P.24 0x0150-0x0157 Reserved

| Address           | Name     |   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------------|----------|---|-------|-------|-------|-------|-------|-------|-------|-------|

| 0x0148-<br>0x014F | Reserved | R | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|                   |          | W |       |       |       |       |       |       |       |       |

# P.25 0x0150-0x0157 Low Side Drivers (LSDRV)

| Address | Name     |   | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1   | Bit 0   |

|---------|----------|---|--------|-------|-------|-------|--------|--------|---------|---------|

| Address | Name     |   | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1   | Bit 0   |

| 0x0150  | LSDR     | R | R 0    | 0     | 0     | 0     | 0      | 0      | LSDR1   | LSDR0   |

| 0x0150  | LSDK     | W |        |       |       |       |        |        |         |         |

| 0x0151  | LSCR     | R | 0      | 0     | 0     | 0     | LSOLE1 | LSOLE0 | LSE1    | LSE0    |

| 0X0151  | LISCK    | W |        |       |       |       | LSOLLI |        | LSEI    |         |

| 0x0152  | Reserved | R | 0      | 0     | 0     | 0     | 0      | 0      | 0       | 0       |

| 0X0132  | Reserved | W |        |       |       |       |        |        |         |         |

| 0x0153  | Reserved | R | 0      | 0     | 0     | 0     | 0      | 0      | 0       | 0       |

| 070133  |          | W |        |       |       |       |        |        |         |         |

| 0x0154  | Reserved | R | 0      | 0     | 0     | 0     | 0      | 0      | 0       | 0       |

| 0/0101  |          | W |        |       |       |       |        |        |         |         |

| 0x0155  | LSSR     | R | 0      | 0     | 0     | 0     | 0      | 0      | LSOL1   | LSOL0   |

| 0.0155  |          | W |        |       |       |       |        |        |         |         |

| 0x0156  | LSIE     | R | LSOCIE | 0     | 0     | 0     | 0      | 0      | 0       | 0       |

|         |          | W | W      |       |       |       |        |        |         |         |

| 0x0157  | LSIF     | R | R 0    | 0     | 0     | 0     | 0      | 0      | LSOCIF1 | LSOCIF0 |

|         |          | W |        |       |       |       |        |        | Looonii |         |

## P.26 0x0158-0x015F Reserved

| Address          | Name     |   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|------------------|----------|---|-------|-------|-------|-------|-------|-------|-------|-------|

| 0x058-<br>0x015F | Reserved | R | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|                  |          | W |       |       |       |       |       |       |       |       |

# P.27 0x0160-0x0167 LIN Physical Layer (LINPHY)

| Address | Name     |          | Bit 7   | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  |   |

|---------|----------|----------|---------|-------|-------|-------|-------|--------|--------|--------|---|

| 0x0160  | LPDR     | R R      | 0       | 0     | 0     | 0     | 0     | 0      | LPDR1  | LPDR0  |   |

|         |          | W        |         |       |       |       |       |        |        |        |   |

| 0x0161  | LPCR     | R        | 0       | 0     | 0     | 0     | LPE   | RXONLY | LPWUE  | LPPUE  |   |

|         |          | W        |         |       |       |       |       |        |        |        |   |

| 0x0162  | Reserved | Reserved | R       | 0     | 0     | 0     | 0     | 0      | 0      | 0      | 0 |

|         |          | W        |         |       |       |       |       |        |        |        |   |

| 0x0163  | LPSLRM   | R        | LPDTDIS | 0     | 0     | 0     | 0     | 0      | LPSLR1 | LPSLR0 |   |

|         |          | W        |         |       |       |       |       |        |        | LISLKU |   |