### Welcome to <u>E-XFL.COM</u>

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | 12V1                                                                     |

| Core Size                  | 16-Bit                                                                   |

| Speed                      | 25MHz                                                                    |

| Connectivity               | IrDA, LINbus, SCI, SPI                                                   |

| Peripherals                | LVD, POR, PWM, WDT                                                       |

| Number of I/O              | 16                                                                       |

| Program Memory Size        | 48KB (48K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 512 x 8                                                                  |

| RAM Size                   | 2K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 5.5V                                                             |

| Data Converters            | A/D 2x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 32-LQFP                                                                  |

| Supplier Device Package    | 32-LQFP (7x7)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12vr48af0mlcr |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|      | 12.4.1 Prescaler                         |  |

|------|------------------------------------------|--|

|      | 12.4.2 Input Capture                     |  |

|      | 12.4.3 Output Compare                    |  |

| 12.5 | Resets                                   |  |

| 12.6 | Interrupts                               |  |

|      | 12.6.1 Channel [3:0] Interrupt (C[3:0]F) |  |

|      | 12.6.2 Timer Overflow Interrupt (TOF)    |  |

# Chapter 13

# High-Side Drivers - HSDRV (S12HSDRVV2) for S12VR64

| 13.1 | Introduc | tion                                   | 409 |

|------|----------|----------------------------------------|-----|

|      | 13.1.1   | Features                               | 409 |

|      | 13.1.2   | Modes of Operation                     | 409 |

|      | 13.1.3   | Block Diagram                          | 410 |

| 13.2 | External | Signal Description                     | 411 |

|      | 13.2.1   | HS0, HS1— High Side Driver Pins        | 411 |

|      | 13.2.2   | VSUPHS — High Side Driver Power Pin    | 411 |

| 13.3 | Memory   | Map and Register Definition            | 411 |

|      | 13.3.1   | Module Memory Map                      | 411 |

|      | 13.3.2   | Register Definition                    | 413 |

|      | 13.3.3   | Port HS Data Register (HSDR)           | 413 |

|      | 13.3.4   | HSDRV Configuration Register (HSCR)    | 414 |

|      | 13.3.5   | Reserved Register                      | 415 |

|      | 13.3.6   | HSDRV Interrupt Enable Register (HSIE) | 416 |

|      | 13.3.7   | HSDRV Interrupt Flag Register (HSIF)   | 417 |

| 13.4 | Function | nal Description                        | 418 |

|      | 13.4.1   | General                                | 418 |

|      |          | Over-Current Shutdown                  |     |

|      | 13.4.3   | Interrupts                             | 418 |

|      |          |                                        |     |

# Chapter 14

# High-Side Driver - HSDRV1C (HSDRV1CV3) for S12VR32

| 14.1 | Introduction                                 |  |

|------|----------------------------------------------|--|

|      | 14.1.1 Features                              |  |

|      | 14.1.2 Modes of Operation                    |  |

|      | 14.1.3 Block Diagram                         |  |

| 14.2 | External Signal Description                  |  |

|      | 14.2.1 HS[0] — High Side Driver Pin          |  |

|      | 14.2.2 VSUPHS — High Side Driver Power Pin   |  |

| 14.3 | Memory Map and Register Definition           |  |

|      | 14.3.1 Module Memory Map                     |  |

|      | 14.3.2 Register Definition                   |  |

|      | 14.3.3 Port HS Data Register (HSDR)          |  |

|      | 14.3.4 HSDRV1C Configuration Register (HSCR) |  |

|      |                                              |  |

Port Integration Module (S12VRPIMV3)

| Port | Pin Name                | Pin Function<br>& Priority <sup>1</sup>                                               | I/O | Description                                                                            | Pin Function<br>after Reset |

|------|-------------------------|---------------------------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------|-----------------------------|

| Р    | <u>PP5</u>              | PP5         IRO         I         Maskable level- or falling edge-sensitive interrupt |     | GPIO                                                                                   |                             |

|      |                         | <u>PWM5</u>                                                                           | 0   | Pulse Width Modulator channel 5                                                        |                             |

|      |                         | ETRIG1                                                                                | Ι   | ADC external trigger input                                                             |                             |

|      |                         | <u>PTP[5]/</u><br>KWP[5]                                                              | I/O | General-purpose; with pin interrupt and wakeup                                         |                             |

|      | <u>PP4</u>              | <u>PWM4</u>                                                                           | 0   | Pulse Width Modulator channel 4                                                        |                             |

|      |                         | ETRIG0                                                                                | Ι   | ADC external trigger input                                                             |                             |

|      |                         | <u>PTP[4]/</u><br><u>KWP[4]</u>                                                       | I/O | General-purpose; with pin interrupt and wakeup                                         |                             |

|      | <u>PP3</u>              | <u>PWM3</u>                                                                           | 0   | Pulse Width Modulator channel 3                                                        |                             |

|      |                         | <u>PTP[3]/</u><br>KWP[3]                                                              | I/O | General-purpose; with pin interrupt and wakeup                                         |                             |

|      | PP2 <sup>3</sup>        | PWM2                                                                                  | 0   | Pulse Width Modulator channel 2                                                        |                             |

|      |                         | PTP[2]/<br>KWP[2]/<br>EVDD                                                            | I/O | General-purpose; with pin interrupt and wakeup                                         |                             |

|      | PP1 <sup>4</sup>        | XIRQ                                                                                  | Ι   | Non-maskable level-sensitive interrupt                                                 |                             |

|      |                         | PWM1                                                                                  | 0   | Pulse Width Modulator channel 1                                                        |                             |

|      |                         | PTP[1]/<br>KWP[1]                                                                     | I/O | General-purpose; with interrupt and wakeup                                             |                             |

|      | <u>PP0</u> <sup>4</sup> | <u>PWM0</u>                                                                           | 0   | Pulse Width Modulator channel 0                                                        |                             |

|      |                         | <u>PTP[0]/</u><br>KWP[0]                                                              | I/O | General-purpose; with interrupt and wakeup                                             |                             |

| L    | PL3-0                   | PTL[3:0]/<br>KWL[3:0]                                                                 | Ι   | General-purpose high-voltage input (HVI); with interrupt and wakeup; optional ADC link | GPI (HVI)                   |

| AD   | <u>PAD5-2</u>           | <u>AN[5:2]</u>                                                                        | Ι   | ADC analog                                                                             | GPIO                        |

|      |                         | <u>PTAD[5:2]/</u><br>KWAD[5:2]                                                        | I/O | General-purpose; with interrupt and wakeup                                             |                             |

|      | PAD1-0                  | AN[1:0]                                                                               | Ι   | ADC analog                                                                             |                             |

|      |                         | PTAD[1:0]/<br>KWAD[1:0]                                                               | I/O | General-purpose; with interrupt and wakeup                                             |                             |

<sup>1</sup> Signals in parentheses denote alternative module routing pins. Signals in **bold underlined** are only available on S12VR64/48.

<sup>2</sup> Function active when  $\overline{\text{RESET}}$  asserted

<sup>3</sup> High current capable high-side output (20mA) with over-current interrupt and protection for all sources (see 2.4.4.3/2-112)

<sup>4</sup> High-current capable output (10 mA)

# 2.3 Memory Map and Register Definition

This section provides a detailed description of all PIM registers.

### S12G Memory Map Controller (S12GMMCV1)

| Address           | Register<br>Name |        | Bit 7 | 6          | 5              | 4     | 3    | 2    | 1    | Bit 0  |

|-------------------|------------------|--------|-------|------------|----------------|-------|------|------|------|--------|

| 0x000A            | Reserved         | R      | 0     | 0          | 0              | 0     | 0    | 0    | 0    | 0      |

|                   |                  | W      |       |            |                |       |      |      |      |        |

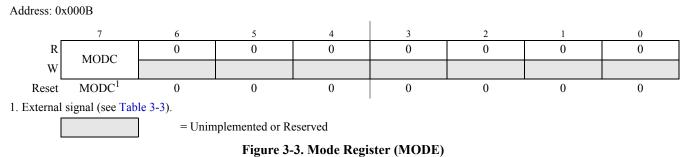

| 0x000B            | MODE             | R<br>W | MODC  | 0          | 0              | 0     | 0    | 0    | 0    | 0      |

| 0x0010            | Reserved         | R<br>W | 0     | 0          | 0              | 0     | 0    | 0    | 0    | 0      |

| 0x0011            | DIRECT           | R<br>W | DP15  | DP14       | DP13           | DP12  | DP11 | DP10 | DP9  | DP8    |

| 0x0012            | Reserved         | R<br>W | 0     | 0          | 0              | 0     | 0    | 0    | 0    | 0      |

| 0x0013            | MMCCTL1          | R<br>W | 0     | 0          | 0              | 0     | 0    | 0    | 0    | NVMRES |

| 0x0014            | Reserved         | R<br>W | 0     | 0          | 0              | 0     | 0    | 0    | 0    | 0      |

| 0x0015            | PPAGE            | R<br>W | 0     | 0          | 0              | 0     | PIX3 | PIX2 | PIX1 | PIX0   |

| 0x0016-<br>0x0017 | Reserved         | R<br>W | 0     | 0          | 0              | 0     | 0    | 0    | 0    | 0      |

|                   |                  | [      |       | = Unimplem | nented or Reso | erved |      |      |      |        |

Figure 3-2. MMC Register Summary

# **3.3.2** Register Descriptions

This section consists of the S12GMMC control register descriptions in address order.

## **3.3.2.1** Mode Register (MODE)

rigure 5-5. Mode Register (MODE)

MC9S12VR Family Reference Manual, Rev. 4.2

## 4.1.1 Features

The Pierce Oscillator (XOSCLCP) contains circuitry to dynamically control current gain in the output amplitude. This ensures a signal with low harmonic distortion, low power and good noise immunity.

- Supports crystals or resonators from 4MHz to 20MHz.

- High noise immunity due to input hysteresis and spike filtering.

- Low RF emissions with peak-to-peak swing limited dynamically

- Transconductance (gm) sized for optimum start-up margin for typical crystals

- Dynamic gain control eliminates the need for external current limiting resistor

- Integrated resistor eliminates the need for external bias resistor

- Low power consumption: Operates from internal 1.8V (nominal) supply, Amplitude control limits power

- Optional oscillator clock monitor reset

- Optional full swing mode for higher immunity against noise injection on the cost of higher power consumption and increased emission

The Voltage Regulator (VREGAUTO) has the following features:

- Input voltage range from 6 to 18V (nominal operating range)

- Low-voltage detect (LVD) with low-voltage interrupt (LVI)

- Power-on reset (POR)

- Low-voltage reset (LVR)

- On Chip Temperature Sensor and Bandgap Voltage measurement via internal ADC channel.

- High temperature interrupt

- Voltage Regulator providing Full Performance Mode (FPM) and Reduced Performance Mode (RPM)

The Phase Locked Loop (PLL) has the following features:

- Highly accurate and phase locked frequency multiplier

- Configurable internal filter for best stability and lock time

- Frequency modulation for defined jitter and reduced emission

- Automatic frequency lock detector

- Interrupt request on entry or exit from locked condition

- Reference clock either external (crystal) or internal square wave (1MHz IRC1M) based.

- PLL clock monitor reset

- PLL stability is sufficient for LIN communication in slave mode, even if using IRC1M as reference clock

The Internal Reference Clock (IRC1M) has the following features:

• Frequency trimming

(A factory trim value for 1MHz is loaded from Flash Memory into the IRCTRIM register after reset, which can be overwritten by application if required)

S12 Clock, Reset and Power Management Unit (S12CPMU\_UHV\_V8)

## 4.3.2.7 S12CPMU\_UHV\_V8 PLL Control Register (CPMUPLL)

This register controls the PLL functionality.

0x003A

|       | 7 | 6 | 5   | 4   | 3 | 2 | 1 | 0 |

|-------|---|---|-----|-----|---|---|---|---|

| R     | 0 | 0 | EM1 | EMO | 0 | 0 | 0 | 0 |

| W     |   |   | FM1 | FM0 |   |   |   |   |

| Reset | 0 | 0 | 0   | 0   | 0 | 0 | 0 | 0 |

## Figure 4-10. S12CPMU\_UHV\_V8 PLL Control Register (CPMUPLL)

Read: Anytime

Write: Anytime if PROT=0 (CPMUPROT register) and PLLSEL=1 (CPMUCLKS register). Else write has no effect.

## NOTE

Write to this register clears the LOCK and UPOSC status bits.

## NOTE

Care should be taken to ensure that the bus frequency does not exceed the specified maximum when frequency modulation is enabled.

### Table 4-8. CPMUPLL Field Descriptions

|   | Field | Description                                                                                                                                                                                                           |

|---|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F |       | PLL <b>Frequency Modulation Enable Bits</b> — FM1 and FM0 enable frequency modulation on the VCOCLK. This is to reduce noise emission. The modulation frequency is $f_{ref}$ divided by 16. See Table 4-9 for coding. |

### Table 4-9. FM Amplitude selection

| FM1 | FM0 | FM Amplitude /<br>f <sub>VCO</sub> Variation |

|-----|-----|----------------------------------------------|

| 0   | 0   | FM off                                       |

| 0   | 1   | ±1%                                          |

| 1   | 0   | ±2%                                          |

| 1   | 1   | ±4%                                          |

# 4.4.6 System Clock Configurations

## 4.4.6.1 PLL Engaged Internal Mode (PEI)

This mode is the default mode after System Reset or Power-On Reset.

The Bus Clock is based on the PLLCLK, the reference clock for the PLL is internally generated (IRC1M). The PLL is configured to 50 MHz VCOCLK with POSTDIV set to 0x03. If locked (LOCK=1) this results in a PLLCLK of 12.5 MHz and a Bus Clock of 6.25 MHz. The PLL can be re-configured to other bus frequencies.

The clock sources for COP and RTI can be based on the internal reference clock generator (IRC1M) or the RC-Oscillator (ACLK).

## 4.4.6.2 PLL Engaged External Mode (PEE)

In this mode, the Bus Clock is based on the PLLCLK as well (like PEI). The reference clock for the PLL is based on the external oscillator.

The clock sources for COP and RTI can be based on the internal reference clock generator or on the external oscillator clock or the RC-Oscillator (ACLK).

This mode can be entered from default mode PEI by performing the following steps:

- 1. Configure the PLL for desired bus frequency.

- 2. Enable the external Oscillator (OSCE bit).

- 3. Wait for oscillator to start-up and the PLL being locked (LOCK = 1) and (UPOSC = 1).

- 4. Clear all flags in the CPMUFLG register to be able to detect any future status bit change.

- 5. Optionally status interrupts can be enabled (CPMUINT register).

Loosing PLL lock status (LOCK=0) means loosing the oscillator status information as well (UPOSC=0).

The impact of loosing the oscillator status (UPOSC=0) in PEE mode is as follows:

• The PLLCLK is derived from the VCO clock (with its actual frequency) divided by four until the PLL locks again.

Application software needs to be prepared to deal with the impact of loosing the oscillator status at any time.

- Hardware handshake protocol to increase the performance of the serial communication

- Active out of reset in special single chip mode

- Nine hardware commands using free cycles, if available, for minimal CPU intervention

- Hardware commands not requiring active BDM

- 14 firmware commands execute from the standard BDM firmware lookup table

- Software control of BDM operation during wait mode

- When secured, hardware commands are allowed to access the register space in special single chip mode, if the Flash erase tests fail.

- Family ID readable from BDM ROM at global address 0x3\_FF0F in active BDM (value for devices with HCS12S core is 0xC2)

- BDM hardware commands are operational until system stop mode is entered

# 5.1.2 Modes of Operation

BDM is available in all operating modes but must be enabled before firmware commands are executed. Some systems may have a control bit that allows suspending the function during background debug mode.

## 5.1.2.1 Regular Run Modes

All of these operations refer to the part in run mode and not being secured. The BDM does not provide controls to conserve power during run mode.

Normal modes

General operation of the BDM is available and operates the same in all normal modes.

• Special single chip mode

In special single chip mode, background operation is enabled and active out of reset. This allows programming a system with blank memory.

## 5.1.2.2 Secure Mode Operation

If the device is in secure mode, the operation of the BDM is reduced to a small subset of its regular run mode operation. Secure operation prevents access to Flash other than allowing erasure. For more information please see Section 5.4.1, "Security".

## 5.1.2.3 Low-Power Modes

The BDM can be used until stop mode is entered. When CPU is in wait mode all BDM firmware commands as well as the hardware BACKGROUND command cannot be used and are ignored. In this case the CPU can not enter BDM active mode, and only hardware read and write commands are available. Also the CPU can not enter a low power mode (stop or wait) during BDM active mode.

In stop mode the BDM clocks are stopped. When BDM clocks are disabled and stop mode is exited, the BDM clocks will restart and BDM will have a soft reset (clearing the instruction register, any command in progress and disable the ACK function). The BDM is now ready to receive a new command.

### Table 9-11. PWMCLK Field Descriptions

Note: Bits related to available channels have functional significance. Writing to unavailable bits has no effect. Read from unavailable bits return a zero

| Field        | Description                                                                                                                                                                                                                          |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>PCLKAB7 | Pulse Width Channel 7 Clock A/B Select001Clock B or SB is the clock source for PWM channel 7, as shown in Table 9-6.11Clock A or SA is the clock source for PWM channel 7, as shown in Table 9-6.                                    |

| 6<br>PCLKAB6 | <ul> <li>Pulse Width Channel 6 Clock A/B Select</li> <li>Clock B or SB is the clock source for PWM channel 6, as shown in Table 9-6.</li> <li>Clock A or SA is the clock source for PWM channel 6, as shown in Table 9-6.</li> </ul> |

| 5<br>PCLKAB5 | <ul> <li>Pulse Width Channel 5 Clock A/B Select</li> <li>Clock A or SA is the clock source for PWM channel 5, as shown in Table 9-5.</li> <li>Clock B or SB is the clock source for PWM channel 5, as shown in Table 9-5.</li> </ul> |

| 4<br>PCLKAB4 | Pulse Width Channel 4 Clock A/B Select0Clock A or SA is the clock source for PWM channel 4, as shown in Table 9-5.1Clock B or SB is the clock source for PWM channel 4, as shown in Table 9-5.                                       |

| 3<br>PCLKAB3 | Pulse Width Channel 3 Clock A/B Select0Clock B or SB is the clock source for PWM channel 3, as shown in Table 9-6.1Clock A or SA is the clock source for PWM channel 3, as shown in Table 9-6.                                       |

| 2<br>PCLKAB2 | Pulse Width Channel 2 Clock A/B Select         0       Clock B or SB is the clock source for PWM channel 2, as shown in Table 9-6.         1       Clock A or SA is the clock source for PWM channel 2, as shown in Table 9-6.       |

| 1<br>PCLKAB1 | Pulse Width Channel 1 Clock A/B Select0Clock A or SA is the clock source for PWM channel 1, as shown in Table 9-5.1Clock B or SB is the clock source for PWM channel 1, as shown in Table 9-5.                                       |

| 0<br>PCLKAB0 | Pulse Width Channel 0 Clock A/B Select0Clock A or SA is the clock source for PWM channel 0, as shown in Table 9-5.1Clock B or SB is the clock source for PWM channel 0, as shown in Table 9-5.                                       |

The clock source of each PWM channel is determined by PCLKx bits in PWMCLK (see Section 9.3.2.3, "PWM Clock Select Register (PWMCLK)) and PCLKABx bits in PWMCLKAB as shown in Table 9-5 and Table 9-6.

## 9.3.2.8 PWM Scale A Register (PWMSCLA)

PWMSCLA is the programmable scale value used in scaling clock A to generate clock SA. Clock SA is generated by taking clock A, dividing it by the value in the PWMSCLA register and dividing that by two.

Clock SA = Clock A / (2 \* PWMSCLA)

## NOTE

When PWMSCLA =\$00, PWMSCLA value is considered a full scale value of 256. Clock A is thus divided by 512.

Any value written to this register will cause the scale counter to load the new scale value (PWMSCLA).

MC9S12VR Family Reference Manual, Rev. 4.2

### Serial Peripheral Interface (S12SPIV5) for S12VR64

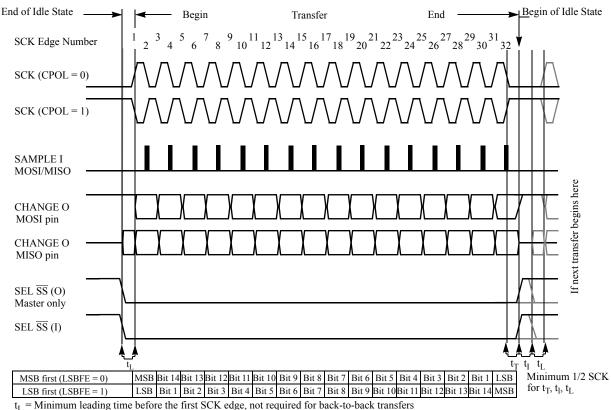

$t_{\rm T}$  = Minimum trailing time after the last SCK edge

$t_1$  = Minimum idling time between transfers (minimum  $\overline{SS}$  high time), not required for back-to-back transfers

Figure 11-15. SPI Clock Format 1 (CPHA = 1), with 16-Bit Transfer Width selected (XFRW = 1)

The  $\overline{SS}$  line can remain active low between successive transfers (can be tied low at all times). This format is sometimes preferred in systems having a single fixed master and a single slave that drive the MISO data line.

• Back-to-back transfers in master mode

In master mode, if a transmission has completed and new data is available in the SPI data register, this data is sent out immediately without a trailing and minimum idle time.

The SPI interrupt request flag (SPIF) is common to both the master and slave modes. SPIF gets set one half SCK cycle after the last SCK edge.

## 11.4.4 SPI Baud Rate Generation

Baud rate generation consists of a series of divider stages. Six bits in the SPI baud rate register (SPPR2, SPPR1, SPPR0, SPR2, SPR1, and SPR0) determine the divisor to the SPI module clock which results in the SPI baud rate.

The SPI clock rate is determined by the product of the value in the baud rate preselection bits (SPPR2–SPPR0) and the value in the baud rate selection bits (SPR2–SPR0). The module clock divisor equation is shown in Equation 11-3.

### High-Side Driver - HSDRV1C (HSDRV1CV3) for S12VR32

cleared automatically. After returning from stop mode the driver is re-enabled and the state of the HSCR[HSE0] bit is set automatically. If the data register bit (HSDR[HSDR0]) is chosen as source in the PIM module, then the high-side driver stays turned off until the software sets the associated bit in the data register (HSDR[HSDR0]). When the timer or PWM is chosen as source, the high-side driver is controlled by the timer or PWM without further handling. When it is required that the driver stays turned off after the stop mode for this case (PWM or timer), the software must take the appropriate action to turn off the driver before entering stop mode.

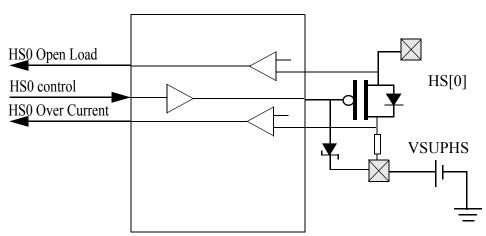

# 14.1.3 Block Diagram

Figure 14-1 shows a block diagram of the HSDRV1C module. The module consists of a control and an output stage. The high-side driver gate control can be routed. See PIM chapter for routing options.

## Figure 14-1. HSDRV1C Block Diagram

# 14.2 External Signal Description

Table 14-2 shows the external pins associated with the HSDRV1C module.

### Table 14-2. HSDRV1C Signal Properties

| Name   | Function                                       | Reset State    |

|--------|------------------------------------------------|----------------|

| HS[0]  | High-side driver output 0                      | disabled (off) |

| VSUPHS | High Voltage Power Supply for high side driver | disabled (off) |

# 14.2.1 HS[0] — High Side Driver Pin

Output of the high-side driver intended to drive LEDs or resistive loads.

# 14.2.2 VSUPHS — High Side Driver Power Pin

Power supply for the high-side driver.

# Chapter 15 Low-Side Drivers - LSDRV (S12LSDRV1)

| Rev. No.<br>(Item No.) | Date (Submitted<br>By) | Sections Affected                             | Substantial Change(s)                                                                                                                                                                                            |

|------------------------|------------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V1.01                  | 22 February<br>2011    | All                                           | - Added clarification to open-load mechanism in over-current conditions                                                                                                                                          |

| V1.02                  | 12 April<br>2011       | All                                           | <ul> <li>improved clarification to open-load mechanism in over-current conditions</li> <li>corrected typos</li> </ul>                                                                                            |

| V1.03                  | 3 April<br>2011        | Register<br>Descriptions for<br>LSDR and LSCR | <ul> <li>added Note on considering settling time t<sub>LS_settling</sub> to LSDR and LSCR register description</li> <li>added Note on how to disable the low-side driver to LSDR register description</li> </ul> |

| V1.04                  | 29 January 2013        | All                                           | - Cleaning                                                                                                                                                                                                       |

### Table 15-1. Revision History Table

## 15.1 Introduction

The LSDRV module provides two low-side drivers typically used to drive inductive loads (relays).

## 15.1.1 Features

The LSDRV module includes two independent low side drivers with common current sink. Each driver has the following features:

- Selectable driver control of low-side switches: LSDRx register bits, PWM or timer channels. See PIM chapter for routing options.

- Open-load detection while enabled

- While driver off: selectable high-load resistance open-load detection

- Over-current protection with shutdown and interrupt while enabled

- Active clamp to protect the device against over-voltage when the power transistor that is driving an inductive load (relay) is turned off.

## 15.1.2 Modes of Operation

The LSDRV module behaves as follows in the system operating modes:

1. MCU run mode

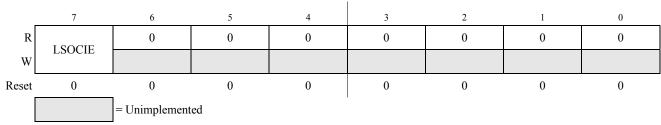

#### LSDRV Interrupt Enable Register (LSIE) 15.3.6

Module Base + 0x0006

Access: User read/write1

### Figure 15-5. LSDRV Interrupt Enable Register (LSIE)

Read: Anytime Write: Anytime

1

| Field       | Description                                                                                                                     |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------|--|

| 7<br>LSOCIE | LSDRV Error Interrupt Enable<br>0 Interrupt request is disabled<br>1 Interrupt will be requested whenever a LSOCIFx flag is set |  |

| Field            | Description                                                                                                                                                                                                                                                                                                |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2<br>FPLDIS      | Flash Protection Lower Address Range Disable — The FPLDIS bit determines whether there is a protected/unprotected area in a specific region of the P-Flash memory beginning with global address 0x3_8000.         0       Protection/Unprotection enabled         1       Protection/Unprotection disabled |

| 1–0<br>FPLS[1:0] | Flash Protection Lower Address Size — The FPLS bits determine the size of the protected/unprotected area in P-Flash memory as shown in Table 18-20. The FPLS bits can only be written to while the FPLDIS bit is set.                                                                                      |

| FPOPEN | FPHDIS | FPLDIS | Function <sup>1</sup>           |

|--------|--------|--------|---------------------------------|

| 1      | 1      | 1      | No P-Flash Protection           |

| 1      | 1      | 0      | Protected Low Range             |

| 1      | 0      | 1      | Protected High Range            |

| 1      | 0      | 0      | Protected High and Low Ranges   |

| 0      | 1      | 1      | Full P-Flash Memory Protected   |

| 0      | 1      | 0      | Unprotected Low Range           |

| 0      | 0      | 1      | Unprotected High Range          |

| 0      | 0      | 0      | Unprotected High and Low Ranges |

### Table 18-18. P-Flash Protection Function

<sup>1</sup> For range sizes, refer to Table 18-19 and Table 18-20.

### Table 18-19. P-Flash Protection Higher Address Range

| FPHS[1:0] | Global Address Range | Protected Size |

|-----------|----------------------|----------------|

| 00        | 0x3_F800-0x3_FFFF    | 2 Kbytes       |

| 01        | 0x3_F000-0x3_FFFF    | 4 Kbytes       |

| 10        | 0x3_E000-0x3_FFFF    | 8 Kbytes       |

| 11        | 0x3_C000-0x3_FFFF    | 16 Kbytes      |

### Table 18-20. P-Flash Protection Lower Address Range

| FPLS[1:0] | <b>Global Address Range</b> | Protected Size |

|-----------|-----------------------------|----------------|

| 00        | 0x3_8000-0x3_83FF           | 1 Kbyte        |

| 01        | 0x3_8000-0x3_87FF           | 2 Kbytes       |

| 10        | 0x3_8000-0x3_8FFF           | 4 Kbytes       |

| 11        | 0x3_8000-0x3_9FFF           | 8 Kbytes       |

All possible P-Flash protection scenarios are shown in Figure 18-13. Although the protection scheme is loaded from the Flash memory at global address 0x3\_FF0C during the reset sequence, it can be changed by the user. The P-Flash protection scheme can be used by applications requiring reprogramming in Normal Single Chip Mode while providing as much protection as possible if reprogramming is not required.

# **18.4** Functional Description

## **18.4.1** Modes of Operation

The FTMRG64K512 module provides the modes of operation normal and special . The operating mode is determined by module-level inputs and affects the FCLKDIV, FCNFG, FPROT and EEPROT registers (see Table 18-27).

## **18.4.2** IFR Version ID Word

The version ID word is stored in the IFR at address  $0x0_40B6$ . The contents of the word are defined in Table 18-26.

| [15:4]   | [3:0]  |

|----------|--------|

| Reserved | VERNUM |

Table 18-26. IFR Version ID Fields

• VERNUM: Version number. The first version is number 0b\_0001 with both 0b\_0000 and 0b\_1111 meaning 'none'.

# **18.4.3** Internal NVM resource (NVMRES)

IFR is an internal NVM resource readable by CPU , when NVMRES is active. The IFR fields are shown in Table 18-5.

The NVMRES global address map is shown in Table 18-6.

# 18.4.4 Flash Command Operations

Flash command operations are used to modify Flash memory contents.

The next sections describe:

- How to write the FCLKDIV register that is used to generate a time base (FCLK) derived from BUSCLK for Flash program and erase command operations

- The command write sequence used to set Flash command parameters and launch execution

- Valid Flash commands available for execution, according to MCU functional mode and MCU security state.

MC9S12VR Family Reference Manual, Rev. 4.2

64 KByte Flash Module (S12FTMRG64K512V1) for S12VR64

## 18.4.6.2 Erase Verify Block Command

The Erase Verify Block command allows the user to verify that an entire P-Flash or EEPROM block has been erased. The FCCOB FlashBlockSelectionCode[1:0]bits determine which block must be verified.

Table 18-33. Erase Verify Block Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters |                                                         |

|-------------|------------------|---------------------------------------------------------|

| 000         | 0x02             | Flash block<br>selection code [1:0]. See<br>Table 18-34 |

| Selection code[1:0] | Flash block to be verified |

|---------------------|----------------------------|

| 00                  | EEPROM                     |

| 01                  | Invalid (ACCERR)           |

| 10                  | Invalid (ACCERR)           |

| 11                  | P-Flash                    |

### Table 18-34. Flash block selection code description

Upon clearing CCIF to launch the Erase Verify Block command, the Memory Controller will verify that the selected P-Flash or EEPROM block is erased. The CCIF flag will set after the Erase Verify Block operation has completed. If the block is not erased, it means blank check failed, both MGSTAT bits will be set.

Table 18-35. Erase Verify Block Command Error Handling

| Register | Error Bit | Error Condition                                                                                   |

|----------|-----------|---------------------------------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] != 000 at command launch                                                       |

|          |           | Set if an invalid FlashBlockSelectionCode[1:0] is supplied                                        |

| FSTAT    | FPVIOL    | None                                                                                              |

|          | MGSTAT1   | Set if any errors have been encountered during the read or if blank check failed.                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the read or if blank check failed. |

## 18.4.6.3 Erase Verify P-Flash Section Command

The Erase Verify P-Flash Section command will verify that a section of code in the P-Flash memory is erased. The Erase Verify P-Flash Section command defines the starting point of the code to be verified and the number of phrases.

### 64 KByte Flash Module (S12FTMRG64K512V1) for S12VR64

Upon clearing CCIF to launch the Set Field Margin Level command, the Memory Controller will set the Table 18-57. Set Field Margin Level Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters      |                                                      |  |

|-------------|-----------------------|------------------------------------------------------|--|

| 000         | 0x0E                  | Flash block selection code [1:0]. See<br>Table 18-34 |  |

| 001         | Margin level setting. |                                                      |  |

field margin level for the targeted block and then set the CCIF flag.

## NOTE

When the EEPROM block is targeted, the EEPROM field margin levels are applied only to the EEPROM reads. However, when the P-Flash block is targeted, the P-Flash field margin levels are applied to both P-Flash and EEPROM reads. It is not possible to apply field margin levels to the P-Flash block only.

Valid margin level settings for the Set Field Margin Level command are defined in Table 18-58.

| CCOB<br>(CCOBIX=001) | Level Description                 |  |  |  |

|----------------------|-----------------------------------|--|--|--|

| 0x0000               | Return to Normal Level            |  |  |  |

| 0x0001               | User Margin-1 Level <sup>1</sup>  |  |  |  |

| 0x0002               | User Margin-0 Level <sup>2</sup>  |  |  |  |

| 0x0003               | Field Margin-1 Level <sup>1</sup> |  |  |  |

| 0x0004               | Field Margin-0 Level <sup>2</sup> |  |  |  |

## Table 18-58. Valid Set Field Margin Level Settings

<sup>1</sup> Read margin to the erased state

<sup>2</sup> Read margin to the programmed state

### Table 18-59. Set Field Margin Level Command Error Handling

| Register | Error Bit | Error Condition                                                              |  |  |

|----------|-----------|------------------------------------------------------------------------------|--|--|

|          |           | Set if CCOBIX[2:0] != 001 at command launch                                  |  |  |

|          | ACCERR    | Set if command not available in current mode (see Table 18-27)               |  |  |

|          |           | Set if an invalid FlashBlockSelectionCode[1:0] is supplied (See Table 18-34) |  |  |

| FSTAT    |           | Set if an invalid margin level setting is supplied                           |  |  |

|          | FPVIOL    | None                                                                         |  |  |

|          | MGSTAT1   | None                                                                         |  |  |

|          | MGSTAT0   | None                                                                         |  |  |

### 64 KByte Flash Module (S12FTMRG64K512V1) for S12VR64

| CCOBIX[2:0] | FCCOB Parameters                                                                                                               |                                                    |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|--|

| 000         | 0x12                                                                                                                           | Global address [17:16] to identify<br>EEPROM block |  |  |

| 001         | Global address [15:0] anywhere within the sector to be erased.<br>See Section 18.1.2.2 EEPROM Features for EEPROM sector size. |                                                    |  |  |

Upon clearing CCIF to launch the Erase EEPROM Sector command, the Memory Controller will erase the selected Flash sector and verify that it is erased. The CCIF flag will set after the Erase EEPROM Sector operation has completed.

| Register | Error Bit | Error Condition                                                                     |  |  |

|----------|-----------|-------------------------------------------------------------------------------------|--|--|

|          | ACCERR    | Set if CCOBIX[2:0] != 001 at command launch                                         |  |  |

|          |           | Set if command not available in current mode (see Table 18-27)                      |  |  |

|          |           | Set if an invalid global address [17:0] is suppliedsee )                            |  |  |

| FSTAT    |           | Set if a misaligned word address is supplied (global address [0] != 0)              |  |  |

|          | FPVIOL    | Set if the selected area of the EEPROM memory is protected                          |  |  |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |  |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |  |  |

Table 18-65. Erase EEPROM Sector Command Error Handling

## **18.4.7** Interrupts

The Flash module can generate an interrupt when a Flash command operation has completed or when a Flash command operation has detected an ECC fault.

| Table 18-66. | Flash | <b>Interrupt Sources</b> |

|--------------|-------|--------------------------|

|--------------|-------|--------------------------|

| Interrupt Source                   | Interrupt Flag Local Enable |                             | Global (CCR)<br>Mask |

|------------------------------------|-----------------------------|-----------------------------|----------------------|

| Flash Command Complete             | CCIF<br>(FSTAT register)    | CCIE<br>(FCNFG register)    | I Bit                |

| ECC Double Bit Fault on Flash Read | DFDIF<br>(FERSTAT register) | DFDIE<br>(FERCNFG register) | I Bit                |

| ECC Single Bit Fault on Flash Read | SFDIF<br>(FERSTAT register) | SFDIE<br>(FERCNFG register) | I Bit                |

## NOTE

Vector addresses and their relative interrupt priority are determined at the MCU level.

### MC9S12VR Family Reference Manual, Rev. 4.2

## 19.4.4.3 Valid Flash Module Commands

Table 19-27 present the valid Flash commands, as enabled by the combination of the functional MCU mode (Normal SingleChip NS, Special Singlechip SS) with the MCU security state (Unsecured, Secured).

Special Singlechip mode is selected by input mmc\_ss\_mode\_ts2 asserted. MCU Secured state is selected by input mmc\_secure input asserted.

| FCMD | Command                      | Unse            | cured           | Secured         |                 |  |

|------|------------------------------|-----------------|-----------------|-----------------|-----------------|--|

|      |                              | NS <sup>1</sup> | SS <sup>2</sup> | NS <sup>3</sup> | SS <sup>4</sup> |  |

| 0x01 | Erase Verify All Blocks      | *               | *               | *               | *               |  |

| 0x02 | Erase Verify Block           | *               | *               | *               | *               |  |

| 0x03 | Erase Verify P-Flash Section | *               | *               | *               |                 |  |

| 0x04 | Read Once                    | *               | *               | *               |                 |  |

| 0x06 | Program P-Flash              | *               | *               | *               |                 |  |

| 0x07 | Program Once                 | *               | *               | *               |                 |  |

| 0x08 | Erase All Blocks             |                 | *               |                 | *               |  |

| 0x09 | Erase Flash Block            | *               | *               | *               |                 |  |

| 0x0A | Erase P-Flash Sector         | *               | *               | *               |                 |  |

| 0x0B | Unsecure Flash               |                 | *               |                 | *               |  |

| 0x0C | Verify Backdoor Access Key   | *               |                 | *               |                 |  |

| 0x0D | Set User Margin Level        | *               | *               | *               |                 |  |

| 0x0E | Set Field Margin Level       |                 | *               |                 |                 |  |

| 0x10 | Erase Verify EEPROM Section  | *               | *               | *               |                 |  |

| 0x11 | Program EEPROM               | *               | *               | *               |                 |  |

| 0x12 | Erase EEPROM Sector          | *               | *               | *               |                 |  |

Table 19-27. Flash Commands by Mode and Security State

<sup>1</sup> Unsecured Normal Single Chip mode

<sup>2</sup> Unsecured Special Single Chip mode.

<sup>3</sup> Secured Normal Single Chip mode.

<sup>4</sup> Secured Special Single Chip mode.

**ATD Electrical Specifications**

# C.3 ATD Accuracy

**Table C-3.** and **Table C-4.** specifies the ATD conversion performance excluding any errors due to current injection, input capacitance and source resistance.

# C.3.1 ATD Accuracy Definitions

For the following definitions see also Figure C-1. Differential non-linearity (DNL) is defined as the difference between two adjacent switching steps.

$$DNL(i) = \frac{V_i - V_{i-1}}{1LSB} - 1$$

The integral non-linearity (INL) is defined as the sum of all DNLs:

$$INL(n) = \sum_{i=1}^{n} DNL(i) = \frac{V_n - V_0}{1LSB} - n$$

### Table I-2. Static Electrical Characteristics - Supply Voltage Sense - (BATS).

Characteristics noted under conditions  $5.5V \le VSUP \le 18 \text{ V}$ ,  $-40^{\circ}C \le T_J \le 150^{\circ}C^1$  unless otherwise noted. Typical values noted reflect the approximate parameter mean at  $T_A = 25^{\circ}C^2$  under nominal conditions unless otherwise noted. All parameters in this table assume a in series connected  $R_{VSENSE_R}$  at VSENSE pin unless otherwise noted and are valid on input voltage of  $R_{VSENSE_R}$  and not on VSENSE pin.

| Num | Ratings                                                                        | Symbol                | Min | Тур | Max  | Unit |

|-----|--------------------------------------------------------------------------------|-----------------------|-----|-----|------|------|

| 9   | VSENSE Series Resistor                                                         | R <sub>VSENSE_R</sub> | 9.5 | 10  | 10.5 | kΩ   |

|     | Required to be placed externally at VSENSE pin.                                |                       |     |     |      |      |

| 10  | VSENSE Impedance                                                               | R <sub>VSEN_IMP</sub> | -   | 350 | -    | kΩ   |

|     | If path to ground is enabled. Value at VSENSE pin. $R_{VSENSE_R}$ is excluded. |                       |     |     |      |      |

| 11  | VSENSE Input Capacitance                                                       | C <sub>VSEN_IN</sub>  | -   | 8   | -    | pF   |

<sup>1</sup> T<sub>J</sub>: Junction Temperature

<sup>2</sup> T<sub>A</sub>: Ambient Temperature

$^{3}$  V<sub>ADC</sub>: Voltage accessible at the ATD input channel

# I.3 Dynamic Electrical Characteristics

### Table I-3. Dynamic Electrical Characteristics - Supply Voltage Sense - (BATS).

|     | Characteristics noted under conditions $5.5V \le VSUP \le 18 \text{ V}$ , $-40^{\circ}C \le T_J \le 150^{\circ}C^1$ unless otherwise noted. Typical values noted reflect the approximate parameter mean at $T_A = 25^{\circ}C^2$ under nominal conditions unless otherwise noted. |                     |     |     |     |      |  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----|-----|-----|------|--|

| Num | Ratings                                                                                                                                                                                                                                                                           | Symbol              | Min | Тур | Max | Unit |  |

| 1   | Enable Stabilisation Time                                                                                                                                                                                                                                                         | T <sub>EN_UNC</sub> | -   | 1   | -   | μs   |  |

| 2   | Voltage Warning Low Pass Filter                                                                                                                                                                                                                                                   | $f_{VWLP_filter}$   | -   | 0.5 | Ι   | MHz  |  |

<sup>1</sup> T<sub>J</sub>: Junction Temperature

<sup>2</sup> T<sub>A</sub>: Ambient Temperature