#### Welcome to <u>E-XFL.COM</u>

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | 12V1                                                                     |

| Core Size                  | 16-Bit                                                                   |

| Speed                      | 25MHz                                                                    |

| Connectivity               | IrDA, LINbus, SCI, SPI                                                   |

| Peripherals                | LVD, POR, PWM, WDT                                                       |

| Number of I/O              | 16                                                                       |

| Program Memory Size        | 48KB (48K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 512 x 8                                                                  |

| RAM Size                   | 2K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 5.5V                                                             |

| Data Converters            | A/D 2x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 32-LQFP                                                                  |

| Supplier Device Package    | 32-LQFP (7x7)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12vr48af0vlcr |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Device Overview MC9S12VR-Family

### 1.7.2.15.4 MOSI Signal

This signal is associated with the MOSI functionality of the serial peripheral interface SPI. This signal acts as master output during master mode or as slave input during slave mode

### 1.7.2.16 LINPHY Signals

### 1.7.2.16.1 VLINSUP — Positive Power Supply

This is the power supply to the LINPHY. The VLINSUP is connected to VSUP.

#### 1.7.2.16.2 LPTXD Signal

This signal is the LINPHY transmit input. See Figure 2-22

#### 1.7.2.16.3 LPRXD Signal

This signal is the LINPHY receive output. See Figure 2-22

#### 1.7.2.17 SCI Signals

#### 1.7.2.17.1 RXD[1:0] Signals

Those signals are associated with the receive functionality of the serial communication interfaces SCI1-0.

#### 1.7.2.17.2 TXD[1:0] Signals

Those signals are associated with the transmit functionality of the serial communication interfaces SCI1-0.

#### 1.7.2.18 **PWM**[7:0] Signals

The signals PWM[7:0] are associated with the PWM module outputs.

#### **1.7.2.19** Internal Clock outputs

#### 1.7.2.19.1 ECLK

This signal is associated with the output of the divided bus clock (ECLK).

#### NOTE

This feature is only intended for debug purposes at room temperature. It must not be used for clocking external devices in an application.

#### 1.7.2.20 ETRIG[1:0]

These signals are inputs to the Analog-to-Digital Converter. Their purpose is to trigger ADC conversions.

#### Port Integration Module (S12VRPIMV3)

| Global<br>Address | Register<br>Name <sup>1</sup> | Bit 7    | 6          | 5       | 4       | 3       | 2              | 1       | Bit 0   |

|-------------------|-------------------------------|----------|------------|---------|---------|---------|----------------|---------|---------|

| 0x0272            | Reserved                      | R 0      | 0          | 0       | 0       | 0       | 0              | 0       | 0       |

|                   |                               | W        |            |         |         |         |                |         |         |

| 0x0273            | PTI1AD                        | R 0<br>W | 0          | PTI1AD5 | PTI1AD4 | PTI1AD3 | PTI1AD2        | PTI1AD1 | PTI1AD0 |

| 0x0274            | Reserved                      | R 0<br>W | 0          | 0       | 0       | 0       | 0              | 0       | 0       |

| 0x0275            | DDR1AD                        | R 0<br>W | 0          | DDR1AD5 | DDR1AD4 | DDR1AD3 | DDR1AD2        | DDR1AD1 | DDR1AD0 |

| 0x0276–<br>0x0278 | Reserved                      | R 0<br>W | 0          | 0       | 0       | 0       | 0              | 0       | 0       |

| 0x0279            | PER1AD                        | R 0<br>W | 0          | PER1AD5 | PER1AD4 | PER1AD3 | PER1AD2        | PER1AD1 | PER1AD0 |

| 0x027A            | Reserved                      | R 0<br>W | 0          | 0       | 0       | 0       | 0              | 0       | 0       |

| 0x027B            | PPS1AD                        | R 0<br>W | 0          | PPS1AD5 | PPS1AD4 | PPS1AD3 | PPS1AD2        | PPS1AD1 | PPS1AD0 |

| 0x027C            | Reserved                      | R 0<br>W | 0          | 0       | 0       | 0       | 0              | 0       | 0       |

| 0x027D            | PIE1AD                        | R 0<br>W | 0          | PIE1AD5 | PIE1AD4 | PIE1AD3 | <u>PIE1AD2</u> | PIE1AD1 | PIE1AD0 |

| 0x027E            | Reserved                      | R 0<br>W | 0          | 0       | 0       | 0       | 0              | 0       | 0       |

| 0x027F            | PIF1AD                        | R 0<br>W | 0          | PIF1AD5 | PIF1AD4 | PIF1AD3 | PIF1AD2        | PIF1AD1 | PIF1AD0 |

|                   |                               |          | = Unimplem | nented  |         |         |                |         |         |

<sup>1</sup> Registers in **bold underlinded** are only available in S12VR64/48. On S12VR32/16 these locations read 0 and write is unimplemented.

### 2.3.2 **Register Descriptions**

The following table summarizes the effect of the various configuration bits, that is data direction (DDR), output level (PORT/PT), pull enable (PER), pull select (PPS), interrupt enable (PIE) on the pin function, pull device and interrupt activity.

|                                       | conditions or                      | r r                          |                |                |              |                          |           |                 |

|---------------------------------------|------------------------------------|------------------------------|----------------|----------------|--------------|--------------------------|-----------|-----------------|

| 3.28                                  | Port P                             | Data Dir                     | ection Reg     | gister (DD     | RP)          |                          |           |                 |

| Address 07                            | x025A (S12V)                       | R64/48)                      |                |                |              |                          | Access:   | User read/write |

|                                       | 7                                  | 6                            | 5              | 4              | 3            | 2                        | 1         | 0               |

| R                                     | 0                                  | 0                            | DDDDC          | DDDD4          | DDDD         | DDDD                     | DDDD1     |                 |

| W                                     |                                    |                              | DDRP5          | DDRP4          | DDRP3        | DDRP2                    | DDRP1     | DDRP0           |

| Reset                                 | 0                                  | 0                            | 0              | 0              | 0            | 0                        | 0         | 0               |

|                                       |                                    |                              | 37. Port P Dat | a Direction Re | gister (DDRP | - S12VR64/48             | 3)        |                 |

| Read: Any<br>Write: Any               | time                               | Figure 2-3                   | 37. Port P Dat | a Direction Re | gister (DDRP | - S12VR64/48             |           | User read/write |

| Read: Any<br>Write: Any               | time<br>time                       | Figure 2-3                   | 37. Port P Dat | a Direction Re | gister (DDRP | - <b>S12VR64/48</b><br>2 |           | User read/write |

| Read: Any<br>Write: Any               | time<br>rtime<br>x025A (S12V)      | <b>Figure 2-3</b><br>R32/16) |                |                | I            | 2                        | Access: 1 |                 |

| Read: Any<br>Write: Any<br>Address 0: | time<br>/time<br>x025A (S12V)<br>7 | <b>Figure 2-3</b><br>R32/16) | 5              | 4              | 3            |                          | Access:   | 0               |

#### Table 2-26. PTIP Register Field Descriptions

Description

A read always returns the synchronized input state of the associated pin. It can be used to detect overload or short circuit

<sup>1</sup> Read: Anytime Write: Anytime

Field

5-0

PTIP

PorT Input data register port P —

#### Table 2-27. DDRP Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 5<br>DDRP   | Data Direction Register port P —         This bit determines whether the associated pin is an input or output.         The enabled IRQ function forces the I/O state to be an input if enabled. In this case the data direction bit will not change.         1 Associated pin is configured as output         0 Associated pin is configured as input |  |  |  |  |

| 4-2<br>DDRP | Data Direction Register port P —         This bit determines whether the associated pin is an input or output.         1 Associated pin is configured as output         0 Associated pin is configured as input                                                                                                                                       |  |  |  |  |

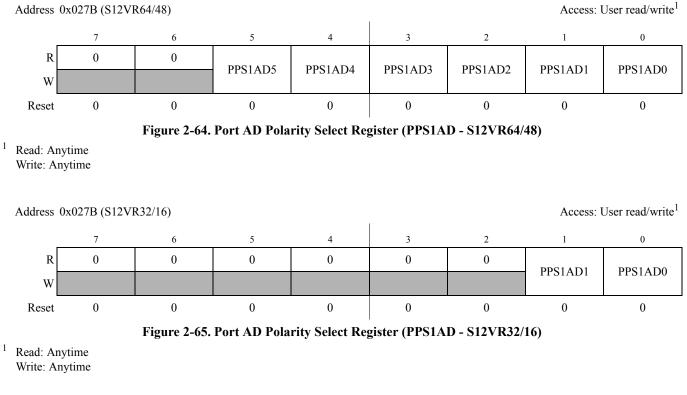

### 2.3.45 Port AD Polarity Select Register (PPS1AD)

#### Table 2-45. PPS1AD Register Field Descriptions

| Field  | Description                                                                                                                |  |  |  |

|--------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 5-0    | Pull device Polarity Select register 1 port AD — Configure pull device polarity and pin interrupt edge polarity on input p |  |  |  |

| PPS1AD | This bit selects a pullup or a pulldown device if enabled on the associated port input pin.                                |  |  |  |

|        | This bit also selects the polarity of the active pin interrupt edge.                                                       |  |  |  |

|        | 1 A pulldown device is selected; rising edge selected                                                                      |  |  |  |

|        | 0 A pullup device is selected; falling edge selected                                                                       |  |  |  |

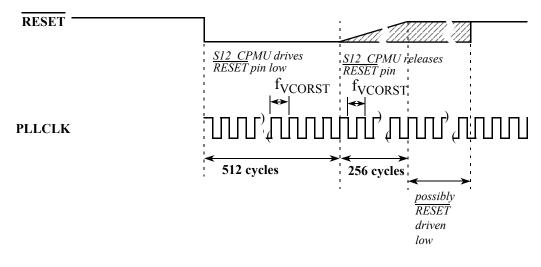

The internal reset of the MCU remains asserted while the reset generator completes the 768 PLLCLK cycles long reset sequence. In case the RESET pin is externally driven low for more than these 768 PLLCLK cycles (External Reset), the internal reset remains asserted longer.

Figure 4-39. RESET Timing

### 4.5.3 Oscillator Clock Monitor Reset

If the external oscillator is enabled (OSCE=1) and the oscillator clock monitor reset is enabled (OMRE=1), then in case of loss of oscillation or the oscillator frequency drops below the failure assert frequency  $f_{CMFA}$  (see device electrical characteristics for values), the S12CPMU\_UHV\_V8 generates an Oscillator Clock Monitor Reset. In Full Stop Mode the external oscillator and the oscillator clock monitor are disabled.

### 4.5.4 PLL Clock Monitor Reset

In case of loss of PLL clock oscillation or the PLL clock frequency is below the failure assert frequency  $f_{PMFA}$  (see device electrical characteristics for values), the S12CPMU\_UHV\_V8 generates a PLL Clock Monitor Reset. In Full Stop Mode the PLL and the PLL clock monitor are disabled.

### 4.5.4.1 Computer Operating Properly Watchdog (COP) Reset

The COP (free running watchdog timer) enables the user to check that a program is running and sequencing properly. When the COP is being used, software is responsible for keeping the COP from timing out. If the COP times out it is an indication that the software is no longer being executed in the intended sequence; thus COP reset is generated.

The clock source for the COP is either ACLK, IRCCLK or OSCCLK depending on the setting of the COPOSCSEL0 and COPOSCSEL1 bit.

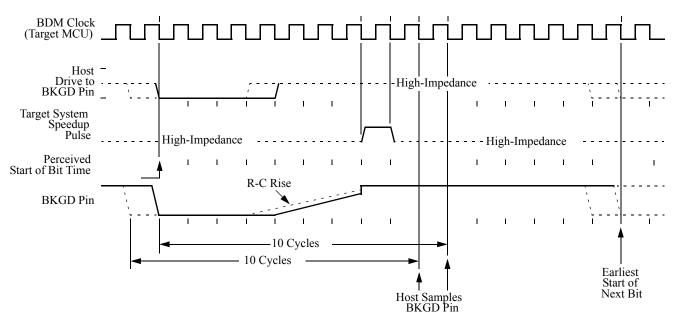

Figure 5-8. BDM Target-to-Host Serial Bit Timing (Logic 1)

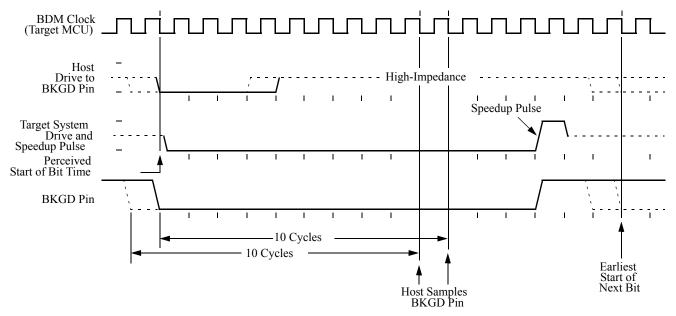

Figure 5-9 shows the host receiving a logic 0 from the target. Since the host is asynchronous to the target, there is up to a one clock-cycle delay from the host-generated falling edge on BKGD to the start of the bit time as perceived by the target. The host initiates the bit time but the target finishes it. Since the target wants the host to receive a logic 0, it drives the BKGD pin low for 13 target clock cycles then briefly drives it high to speed up the rising edge. The host samples the bit level about 10 target clock cycles after starting the bit time.

Figure 5-9. BDM Target-to-Host Serial Bit Timing (Logic 0)

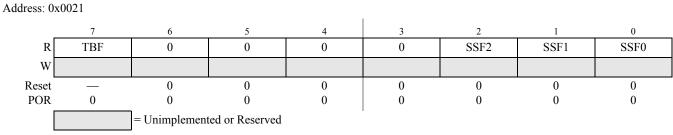

#### Figure 6-4. Debug Status Register (DBGSR)

#### Read: Anytime

Write: Never

#### Table 6-5. DBGSR Field Descriptions

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TBF        | <b>Trace Buffer Full</b> — The TBF bit indicates that the trace buffer has stored 64 or more lines of data since it was last armed. If this bit is set, then all 64 lines will be valid data, regardless of the value of DBGCNT bits. The TBF bit is cleared when ARM in DBGC1 is written to a one. The TBF is cleared by the power on reset initialization. Other system generated resets have no affect on this bit This bit is also visible at DBGCNT[7]                                                                                                                                                                                                               |

| 2–0<br>SSF[2:0] | <b>State Sequencer Flag Bits</b> — The SSF bits indicate in which state the State Sequencer is currently in. During a debug session on each transition to a new state these bits are updated. If the debug session is ended by software clearing the ARM bit, then these bits retain their value to reflect the last state of the state sequencer before disarming. If a debug session is ended by an internal event, then the state sequencer returns to state0 and these bits are cleared to indicate that state0 was entered during the session. On arming the module the state sequencer enters state1 and these bits are forced to $SSF[2:0] = 001$ . See Table 6-6. |

Table 6-6. SSF[2:0] — State Sequence Flag Bit Encoding

| SSF[2:0]    | Current State     |  |  |

|-------------|-------------------|--|--|

| 000         | State0 (disarmed) |  |  |

| 001         | State1            |  |  |

| 010         | State2            |  |  |

| 011         | State3            |  |  |

| 100         | Final State       |  |  |

| 101,110,111 | Reserved          |  |  |

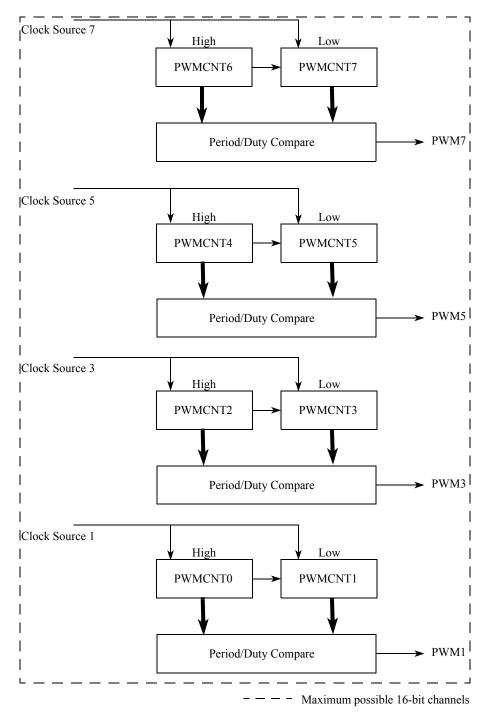

#### Pulse-Width Modulator (S12PWM8B8CV2)

To calculate the output duty cycle (high time as a% of period) for a particular channel:

- Polarity = 0 (PPOL x =0) Duty Cycle = [(PWMPERx-PWMDTYx)/PWMPERx] \* 100%

- Polarity = 1 (PPOLx = 1)

```

Duty Cycle = [PWMDTYx / PWMPERx] * 100%

```

For boundary case programming values, please refer to Section 9.4.2.8, "PWM Boundary Cases".

| _      | 7     | 6 | 5 | 4 | 3 | 2 | 1 | 0     |

|--------|-------|---|---|---|---|---|---|-------|

| R<br>W | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

| Reset  | 1     | 1 | 1 | 1 | 1 | 1 | 1 | 1     |

#### Figure 9-14. PWM Channel Duty Registers (PWMDTYx)

<sup>1</sup> This register is available only when the corresponding channel exists and is reserved if that channel does not exist. Writes to a reserved register have no functional effect. Reads from a reserved register return zeroes.

#### Read: Anytime

Write: Anytime

### 9.4 Functional Description

### 9.4.1 PWM Clock Select

There are four available clocks: clock A, clock B, clock SA (scaled A), and clock SB (scaled B). These four clocks are based on the bus clock.

Clock A and B can be software selected to be 1, 1/2, 1/4, 1/8,..., 1/64, 1/128 times the bus clock. Clock SA uses clock A as an input and divides it further with a reloadable counter. Similarly, clock SB uses clock B as an input and divides it further with a reloadable counter. The rates available for clock SA are software selectable to be clock A divided by 2, 4, 6, 8,..., or 512 in increments of divide by 2. Similar rates are available for clock SB. Each PWM channel has the capability of selecting one of four clocks, clock A, Clock B, clock SA or clock SB.

The block diagram in Figure 9-15 shows the four different clocks and how the scaled clocks are created.

### 9.4.1.1 Prescale

The input clock to the PWM prescaler is the bus clock. It can be disabled whenever the part is in freeze mode by setting the PFRZ bit in the PWMCTL register. If this bit is set, whenever the MCU is in freeze mode (freeze mode signal active) the input clock to the prescaler is disabled. This is useful for emulation in order to freeze the PWM. The input clock can also be disabled when all available PWM channels are disabled (PWMEx-0 = 0). This is useful for reducing power by disabling the prescale counter.

Clock A and clock B are scaled values of the input clock. The value is software selectable for both clock A and clock B and has options of 1, 1/2, 1/4, 1/8, 1/16, 1/32, 1/64, or 1/128 times the bus clock. The value selected for clock A is determined by the PCKA2, PCKA1, PCKA0 bits in the PWMPRCLK register. The

Figure 9-21. PWM 16-Bit Mode

Once concatenated mode is enabled (CONxx bits set in PWMCTL register), enabling/disabling the corresponding 16-bit PWM channel is controlled by the low order PWMEx bit. In this case, the high order bytes PWMEx bits have no effect and their corresponding PWM output is disabled.

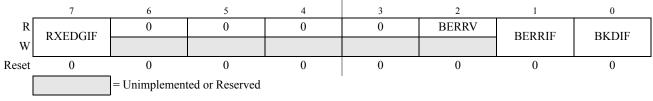

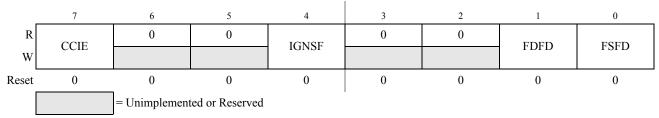

### **10.3.2.3** SCI Alternative Status Register 1 (SCIASR1)

Figure 10-6. SCI Alternative Status Register 1 (SCIASR1)

Read: Anytime, if AMAP = 1

#### Write: Anytime, if AMAP = 1

#### Table 10-5. SCIASR1 Field Descriptions

| Field        | Description                                                                                                                                                                                                                                                                                                                                                             |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>RXEDGIF | Receive Input Active Edge Interrupt Flag — RXEDGIF is asserted, if an active edge (falling if RXPOL = 0, rising if RXPOL = 1) on the RXD input occurs. RXEDGIF bit is cleared by writing a "1" to it.         0       No active receive on the receive input has occurred         1       An active edge on the receive input has occurred                              |

| 2<br>BERRV   | Bit Error Value — BERRV reflects the state of the RXD input when the bit error detect circuitry is enabled and a mismatch to the expected value happened. The value is only meaningful, if BERRIF = 1.         0       A low input was sampled, when a high was expected         1       A high input reassembled, when a low was expected                              |

| 1<br>BERRIF  | <b>Bit Error Interrupt Flag</b> — BERRIF is asserted, when the bit error detect circuitry is enabled and if the value sampled at the RXD input does not match the transmitted value. If the BERRIE interrupt enable bit is set an interrupt will be generated. The BERRIF bit is cleared by writing a "1" to it.<br>0 No mismatch detected<br>1 A mismatch has occurred |

| 0<br>BKDIF   | <ul> <li>Break Detect Interrupt Flag — BKDIF is asserted, if the break detect circuitry is enabled and a break signal is received.</li> <li>If the BKDIE interrupt enable bit is set an interrupt will be generated. The BKDIF bit is cleared by writing a "1" to it.</li> <li>0 No break signal was received</li> <li>1 A break signal was received</li> </ul>         |

| Field   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 3<br>OR | <ul> <li>Overrun Flag — OR is set when software fails to read the SCI data register before the receive shift register receives the next frame. The OR bit is set immediately after the stop bit has been completely received for the second frame. The data in the shift register is lost, but the data already in the SCI data registers is not affected. Clear OR by reading SCI status register 1 (SCISR1) with OR set and then reading SCI data register low (SCIDRL).</li> <li>0 No overrun</li> <li>1 Overrun</li> <li>Note: OR flag may read back as set when RDRF flag is clear. This may happen if the following sequence of events occurs: <ol> <li>After the first frame is received, read status register SCISR1 (returns RDRF set and OR flag clear);</li> <li>Receive second frame without reading the first frame in the data register (the second frame is not received and OR flag is set);</li> <li>Read data register SCIDRL (returns first frame and clears RDRF flag in the status register);</li> <li>Read status register SCISR1 (returns RDRF clear and OR set).</li> </ol> </li> <li>Event 3 may be at exactly the same time as event 2 or any time after. When this happens, a dummy SCIDRL read following event 4 will be required to clear the OR flag if further frames are to be received.</li> </ul> |  |  |  |  |  |

| 2<br>NF | Noise Flag — NF is set when the SCI detects noise on the receiver input. NF bit is set during the same cycle as the RDRF flag but does not get set in the case of an overrun. Clear NF by reading SCI status register 1(SCISR1), and then reading SCI data register low (SCIDRL).         0       No noise         1       Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| 1<br>FE | <ul> <li>Framing Error Flag — FE is set when a logic 0 is accepted as the stop bit. FE bit is set during the same cycle as the RDRF flag but does not get set in the case of an overrun. FE inhibits further data reception until it is cleared. Clear FE by reading SCI status register 1 (SCISR1) with FE set and then reading the SCI data register low (SCIDRL).</li> <li>0 No framing error</li> <li>1 Framing error</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 0<br>PF | <ul> <li>Parity Error Flag — PF is set when the parity enable bit (PE) is set and the parity of the received data does not match the parity type bit (PT). PF bit is set during the same cycle as the RDRF flag but does not get set in the case of an overrun. Clear PF by reading SCI status register 1 (SCISR1), and then reading SCI data register low (SCIDRL).</li> <li>0 No parity error</li> <li>1 Parity error</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

### Table 10-11. SCISR1 Field Descriptions (continued)

### **11.3.2** Register Descriptions

This section consists of register descriptions in address order. Each description includes a standard register diagram with an associated figure number. Details of register bit and field function follow the register diagrams, in bit order.

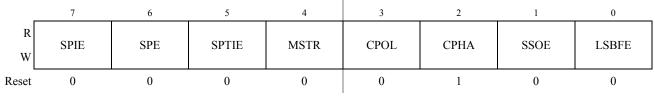

### 11.3.2.1 SPI Control Register 1 (SPICR1)

Figure 11-3. SPI Control Register 1 (SPICR1)

#### Read: Anytime

Write: Anytime

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>SPIE  | <ul> <li>SPI Interrupt Enable Bit — This bit enables SPI interrupt requests, if SPIF or MODF status flag is set.</li> <li>0 SPI interrupts disabled.</li> <li>1 SPI interrupts enabled.</li> </ul>                                                                                                                                                                                                                                                   |

| 6<br>SPE   | <ul> <li>SPI System Enable Bit — This bit enables the SPI system and dedicates the SPI port pins to SPI system functions. If SPE is cleared, SPI is disabled and forced into idle state, status bits in SPISR register are reset.</li> <li>O SPI disabled (lower power consumption).</li> <li>1 SPI enabled, port pins are dedicated to SPI functions.</li> </ul>                                                                                    |

| 5<br>SPTIE | <ul> <li>SPI Transmit Interrupt Enable — This bit enables SPI interrupt requests, if SPTEF flag is set.</li> <li>0 SPTEF interrupt disabled.</li> <li>1 SPTEF interrupt enabled.</li> </ul>                                                                                                                                                                                                                                                          |

| 4<br>MSTR  | <ul> <li>SPI Master/Slave Mode Select Bit — This bit selects whether the SPI operates in master or slave mode. Switching the SPI from master to slave or vice versa forces the SPI system into idle state.</li> <li>0 SPI is in slave mode.</li> <li>1 SPI is in master mode.</li> </ul>                                                                                                                                                             |

| 3<br>CPOL  | <ul> <li>SPI Clock Polarity Bit — This bit selects an inverted or non-inverted SPI clock. To transmit data between SPI modules, the SPI modules must have identical CPOL values. In master mode, a change of this bit will abort a transmission in progress and force the SPI system into idle state.</li> <li>0 Active-high clocks selected. In idle state SCK is low.</li> <li>1 Active-low clocks selected. In idle state SCK is high.</li> </ul> |

| 2<br>СРНА  | <ul> <li>SPI Clock Phase Bit — This bit is used to select the SPI clock format. In master mode, a change of this bit will abort a transmission in progress and force the SPI system into idle state.</li> <li>0 Sampling of data occurs at odd edges (1,3,5,) of the SCK clock.</li> <li>1 Sampling of data occurs at even edges (2,4,6,) of the SCK clock.</li> </ul>                                                                               |

#### Table 11-2. SPICR1 Field Descriptions

# Chapter 16 LIN Physical Layer (S12LINPHYV2)

| Rev. No.<br>(Item No.) | Date (Submitted<br>By) | Sections Affected | Substantial Change(s)                                                                                   |

|------------------------|------------------------|-------------------|---------------------------------------------------------------------------------------------------------|

| V02.11                 | 19 Sep 2013            | All               | <ul><li>Removed preliminary note.</li><li>Fixed grammar and spelling throughout the document.</li></ul> |

| V02.12                 | 20 Sep 2013            | Standby Mode      | - Clarified Standby mode behavior.                                                                      |

| V02.13                 | 8 Oct 2013             | All               | - More grammar, spelling, and formating fixes throughout the document.                                  |

Table 16-1. Revision History Table

### 16.1 Introduction

The LIN (Local Interconnect Network) bus pin provides a physical layer for single-wire communication in automotive applications. The LIN Physical Layer is designed to meet the LIN Physical Layer 2.2 specification from LIN consortium.

### 16.1.1 Features

The LIN Physical Layer module includes the following distinctive features:

- Compliant with LIN Physical Layer 2.2 specification.

- Compliant with the SAE J2602-2 LIN standard.

- Standby mode with glitch-filtered wake-up.

- Slew rate selection optimized for the baud rates: 10.4 kbit/s, 20 kbit/s and Fast Mode (up to 250 kbit/s).

- Switchable 34 k $\Omega$ /330 k $\Omega$  pullup resistors (in shutdown mode, 330 k $\Omega$  only)

- Current limitation for LIN Bus pin falling edge.

- Overcurrent protection.

- LIN TxD-dominant timeout feature monitoring the LPTxD signal.

- Automatic transmitter shutdown in case of an overcurrent or TxD-dominant timeout.

- Fulfills the OEM "Hardware Requirements for LIN (CAN and FlexRay) Interfaces in Automotive Applications" v1.3.

The LIN transmitter is a low-side MOSFET with current limitation and overcurrent transmitter shutdown. A selectable internal pullup resistor with a serial diode structure is integrated, so no external pullup components are required for the application in a slave node. To be used as a master node, an external

### 17.4.2 Interrupts

This section describes the interrupt generated by the BATS module. The interrupt is only available in CPU run mode. Entering and exiting CPU stop mode has no effect on the interrupt flags.

To make sure the interrupt generation works properly the bus clock frequency must be higher than the Voltage Warning Low Pass Filter frequency ( $f_{VWLP}$  filter).

The comparator outputs BVLC and BVHC are forced to zero if the comparator is disabled (configuration bits BSESE and BSUSE are cleared). If the software disables the comparator during a high or low Voltage condition (BVHC or BVLC active), then an additional interrupt is generated. To avoid this behavior the software must disable the interrupt generation before disabling the comparator.

The BATS interrupt vector is named in Table 17-6. Vector addresses and interrupt priorities are defined at MCU level.

The module internal interrupt sources are combined into one module interrupt signal.

**Table 17-6. BATS Interrupt Sources**

| Module Interrupt Source | Module Internal Interrupt Source             | Local Enable |

|-------------------------|----------------------------------------------|--------------|

| BATS Interrupt (BATI)   | BATS Voltage Low Condition Interrupt (BVLI)  | BVLIE = 1    |

|                         | BATS Voltage High Condition Interrupt (BVHI) | BVHIE = 1    |

### 17.4.2.1 BATS Voltage Low Condition Interrupt (BVLI)

To use the Voltage Low Interrupt the Level Sensing must be enabled (BSESE =1 or BSUSE =1).

If measured when

a) V<sub>LBI1</sub> selected with BVLS[1:0] = 0x0 at selected pin V<sub>measure</sub> < V<sub>LBI1</sub> A (falling edge) or V<sub>measure</sub> < V<sub>LBI1</sub> D (rising edge)

or when

b) V<sub>LBI2</sub> selected with BVLS[1:0] = 0x1 at selected pin V<sub>measure</sub> < V<sub>LBI2\_A</sub> (falling edge) or V<sub>measure</sub> < V<sub>LBI2\_D</sub> (rising edge)

or when

c) V<sub>LBI3</sub> selected with BVLS[1:0] = 0x2 at selected pin V<sub>measure</sub> < V<sub>LBI3\_A</sub> (falling edge) or V<sub>measure</sub> < V<sub>LBI3\_D</sub> (rising edge)

or when

d) V<sub>LBI4</sub> selected with BVLS[1:0] = 0x3 at selected pin V<sub>measure</sub> < V<sub>LBI4\_A</sub> (falling edge) or V<sub>measure</sub> < V<sub>LBI4\_D</sub> (rising edge)

then BVLC is set. BVLC status bit indicates that a low voltage at the selected pin is present. The Low Voltage Interrupt flag (BVLIF) is set to 1 when the Voltage Low Condition (BVLC) changes state . The

| F | ìield         | Description                                                                                                                          |

|---|---------------|--------------------------------------------------------------------------------------------------------------------------------------|

|   | 7–0<br>/[7:0] | Nonvolatile Bits — The NV[7:0] bits are available as nonvolatile bits. Refer to the device user guide for proper use of the NV bits. |

#### Table 18-25. FOPT Field Descriptions

### 18.3.2.17 Flash Reserved5 Register (FRSV5)

This Flash register is reserved for factory testing.

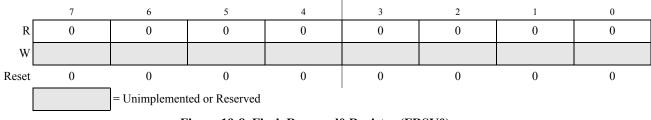

#### Figure 18-22. Flash Reserved5 Register (FRSV5)

All bits in the FRSV5 register read 0 and are not writable.

### 18.3.2.18 Flash Reserved6 Register (FRSV6)

This Flash register is reserved for factory testing.

#### Figure 18-23. Flash Reserved6 Register (FRSV6)

All bits in the FRSV6 register read 0 and are not writable.

### 18.3.2.19 Flash Reserved7 Register (FRSV7)

This Flash register is reserved for factory testing.

Figure 18-24. Flash Reserved7 Register (FRSV7)

All bits in the FRSV7 register read 0 and are not writable.

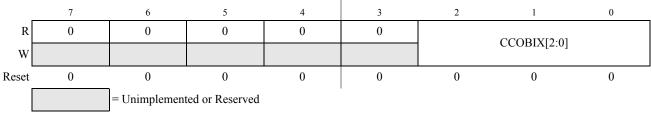

### 19.3.2.3 Flash CCOB Index Register (FCCOBIX)

The FCCOBIX register is used to index the FCCOB register for Flash memory operations.

Figure 19-7. FCCOB Index Register (FCCOBIX)

CCOBIX bits are readable and writable while remaining bits read 0 and are not writable.

#### Table 19-12. FCCOBIX Field Descriptions

| Field | Description                                                                                                                                                                                                                  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <b>Common Command Register Index</b> — The CCOBIX bits are used to select which word of the FCCOB register array is being read or written to. See 19.3.2.11 Flash Common Command Object Register (FCCOB)," for more details. |

### 19.3.2.4 Flash Reserved0 Register (FRSV0)

This Flash register is reserved for factory testing.

Figure 19-8. Flash Reserved0 Register (FRSV0)

All bits in the FRSV0 register read 0 and are not writable.

### **19.3.2.5** Flash Configuration Register (FCNFG)

The FCNFG register enables the Flash command complete interrupt and forces ECC faults on Flash array read access from the CPU.

Figure 19-9. Flash Configuration Register (FCNFG)

### 19.4.6.2 Erase Verify Block Command

The Erase Verify Block command allows the user to verify that an entire P-Flash or EEPROM block has been erased. The FCCOB FlashBlockSelectionCode[1:0]bits determine which block must be verified.

Table 19-33. Erase Verify Block Command FCCOB Requirements

| CCOBIX[2:0] | <b>FCCOB</b> P | arameters                                               |

|-------------|----------------|---------------------------------------------------------|

| 000         | 0x02           | Flash block<br>selection code [1:0]. See<br>Table 19-34 |

| Selection code[1:0] | Flash block to be verified |

|---------------------|----------------------------|

| 00                  | EEPROM                     |

| 01                  | Invalid (ACCERR)           |

| 10                  | Invalid (ACCERR)           |

| 11                  | P-Flash                    |

#### Table 19-34. Flash block selection code description

Upon clearing CCIF to launch the Erase Verify Block command, the Memory Controller will verify that the selected P-Flash or EEPROM block is erased. The CCIF flag will set after the Erase Verify Block operation has completed. If the block is not erased, it means blank check failed, both MGSTAT bits will be set.

Table 19-35. Erase Verify Block Command Error Handling

| Register | Error Bit | Error Condition                                                                                   |

|----------|-----------|---------------------------------------------------------------------------------------------------|

| FSTAT    | ACCERR    | Set if CCOBIX[2:0] != 000 at command launch                                                       |

|          |           | Set if an invalid FlashBlockSelectionCode[1:0] is supplied                                        |

|          | FPVIOL    | None                                                                                              |

|          | MGSTAT1   | Set if any errors have been encountered during the read or if blank check failed.                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the read or if blank check failed. |

### 19.4.6.3 Erase Verify P-Flash Section Command

The Erase Verify P-Flash Section command will verify that a section of code in the P-Flash memory is erased. The Erase Verify P-Flash Section command defines the starting point of the code to be verified and the number of phrases.

32 KByte Flash Module (S12FTMRG32K128V1) for S12VR32

### 19.4.6.15 Program EEPROM Command

The Program EEPROM operation programs one to four previously erased words in the EEPROM block. The Program EEPROM operation will confirm that the targeted location(s) were successfully programmed upon completion.

### CAUTION

A Flash word must be in the erased state before being programmed. Cumulative programming of bits within a Flash word is not allowed.

| CCOBIX[2:0] | FCCOB Parameters                 |                                                        |

|-------------|----------------------------------|--------------------------------------------------------|

| 000         | 0x11                             | Global address [17:16] to identify<br>the EEPROM block |

| 001         | Global address [15:0] of         | word to be programmed                                  |

| 010         | Word 0 pro                       | ogram value                                            |

| 011         | Word 1 program                   | value, if desired                                      |

| 100         | Word 2 program                   | value, if desired                                      |

| 101         | Word 3 program value, if desired |                                                        |

| Table 19-62. Program | <b>EEPROM</b> Command | FCCOB Requirements |

|----------------------|-----------------------|--------------------|

|                      |                       |                    |

Upon clearing CCIF to launch the Program EEPROM command, the user-supplied words will be transferred to the Memory Controller and be programmed if the area is unprotected. The CCOBIX index value at Program EEPROM command launch determines how many words will be programmed in the EEPROM block. The CCIF flag is set when the operation has completed.

| Register | Error Bit | Error Condition                                                                     |

|----------|-----------|-------------------------------------------------------------------------------------|

|          |           | Set if CCOBIX[2:0] < 010 at command launch                                          |

|          |           | Set if CCOBIX[2:0] > 101 at command launch                                          |

|          | ACCERR    | Set if command not available in current mode (see Table 19-27)                      |

|          | ACCERK    | Set if an invalid global address [17:0] is supplied                                 |

| FSTAT    |           | Set if a misaligned word address is supplied (global address [0] != 0)              |

|          |           | Set if the requested group of words breaches the end of the EEPROM block            |

|          | FPVIOL    | Set if the selected area of the EEPROM memory is protected                          |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |

### 19.4.6.16 Erase EEPROM Sector Command

The Erase EEPROM Sector operation will erase all addresses in a sector of the EEPROM block.

**IRC Electrical Specifications**

## **Appendix O Ordering Information**

The following figure provides an ordering partnumber example for the devices covered by this data book. There are two options when ordering a device. Customers must choose between ordering either the mask-specific partnumber or the generic / mask-independent partnumber. Ordering the mask-specific partnumber enables the customer to specify which particular maskset they will receive whereas ordering the generic maskset means that FSL will ship the currently preferred maskset (which may change over time).

In either case, the marking on the device will always show the generic / mask-independent partnumber and the mask set number.

#### NOTE

# The mask identifier suffix and the Tape & Reel suffix are always both omitted from the partnumber which is actually marked on the device.

For specific partnumbers to order, please contact your local sales office. The below figure illustrates the structure of a typical mask-specific ordering number for the MC9S12VR64 devices.