Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | 12V1                                                                     |

| Core Size                  | 16-Bit                                                                   |

| Speed                      | 25MHz                                                                    |

| Connectivity               | IrDA, LINbus, SCI, SPI                                                   |

| Peripherals                | LVD, POR, PWM, WDT                                                       |

| Number of I/O              | 28                                                                       |

| Program Memory Size        | 48KB (48K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 512 x 8                                                                  |

| RAM Size                   | 2K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 5.5V                                                             |

| Data Converters            | A/D 6x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 48-LQFP                                                                  |

| Supplier Device Package    | 48-LQFP (7x7)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12vr48af0vlfr |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| P.8         | 0x001C-0x001F Port Intergartion Module (PIM) Map 3 of 4              | 643 |

|-------------|----------------------------------------------------------------------|-----|

| P.9         | 0x0020-0x002F Debug Module (S12SDBG) Map                             | 643 |

| P.10        | 0x0030-0x0033 Reserved                                               |     |

| P.11        | 0x0034-0x003F Clock Reset and Power Management (CPMU) Map            | 644 |

| P.12        | 0x0040-0x006F Timer Module (TIM) Map                                 | 645 |

| P.13        | 0x0070-0x009F Analog to Digital Converter 10-Bit 6-Channel (ATD) Map | 646 |

| P.14        | 0x00A0-0x00C7 Pulse Width Modulator 6-Channels (PWM) Map.            | 648 |

| P.15        | 0x00C8-0x00CF Serial Communication Interface (SCI0) Map              | 650 |

| P.16        | 0x00D0-0x00D7 Serial Communication Interface (SCI1) Map              | 651 |

| P.17        | 0x00D8-0x00DF Serial Peripheral Interface (SPI) Map                  | 651 |

| P.18        | 0x00E0-0x00FF Reserved                                               | 652 |

| P.19        | 0x0100-0x0113 NVM Contol Register (FTMRG) Map                        | 652 |

| P.20        | 0x0114-0x011F Reserved                                               | 653 |

| <b>P.21</b> | 0x0120 Interrupt Vector Base Register                                | 653 |

|             | 0x0121-0x013F Reserved                                               |     |

| P.23        | 0x0140-0x0147 High Side Drivers                                      | 654 |

|             | P.23.1 S12HSDRVV2 on MC9S12VR64/48                                   |     |

|             | P.23.2 S12HSDRV1CV3 on MC9S12VR32/16                                 | 654 |

|             | 0x0150-0x0157 Reserved                                               |     |

| P.25        | 0x0150-0x0157 Low Side Drivers (LSDRV)                               | 655 |

| P.26        | 0x0158-0x015F Reserved                                               | 655 |

| P.27        | 0x0160-0x0167 LIN Physical Layer (LINPHY)                            | 655 |

| P.28        | 0x0168-0x016F Reserved                                               | 656 |

| P.29        | 0x0170-0x0177 Supply Voltage Sense (BATS)                            | 656 |

| P.30        | 0x0178-023F Reserved                                                 |     |

| P.31        | 0x0240 -0x027F Port Integration Module (PIM) Map 4 of 4              | 657 |

| P.32        | 0x0280-0x02EF Reserved                                               | 660 |

| P.33        | 0x02F0-0x02FF Clock and Power Management Unit (CPMU) Map 2 of 2      | 660 |

| P.34        | 0x0300-0x03FF Reserved                                               | 661 |

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 2<br>DDRS | <b>Data Direction Register port S</b> —<br>This bit determines whether the associated pin is an input or output. The enabled API_EXTCLK function forces the I/O state to output. Depending on the configuration of the enabled SPI the I/O state will be forced to be input or output. The routed SCI1 function forces the I/O state to input if enabled. The routed PWM function forces the I/O state to output if enabled. In these cases the data direction bit will not change. The routed ETRIG function has no effect on the I/O state.<br>1 Associated pin is configured as output<br>0 Associated pin is configured as input |  |

| 1<br>DDRS | Data Direction Register port S —         This bit determines whether the associated pin is an input or output.         Depending on the configuration of the enabled SCI the I/O state will be forced to be input or output. The enabled routed LINPHY forces the I/O state to be an output (LPDR[LPDR1]). In these cases the data direction bit will not change.         1 Associated pin is configured as output         0 Associated pin is configured as input                                                                                                                                                                   |  |

| 0<br>DDRS | Data Direction Register port S —         This bit determines whether the associated pin is an input or output.         Depending on the configuration of the enabled SCI the I/O state will be forced to be input or output. In this case the data direction bit will not change.         1 Associated pin is configured as output         0 Associated pin is configured as input                                                                                                                                                                                                                                                   |  |

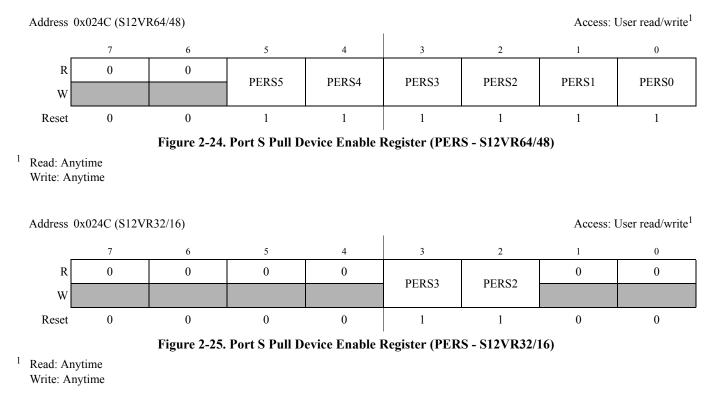

# 2.3.22 Port S Pull Device Enable Register (PERS)

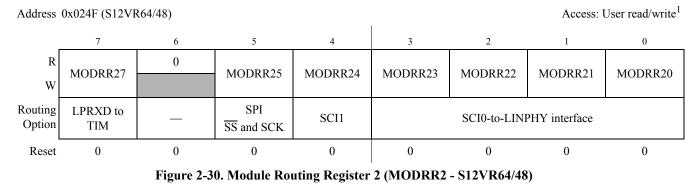

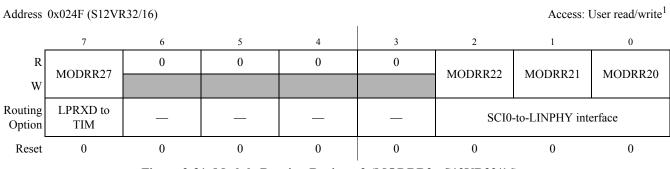

# 2.3.25 Module Routing Register 2 (MODRR2)

<sup>1</sup> Read: Anytime

Write: Once in normal, anytime in special mode

Figure 2-31. Module Routing Register 2 (MODRR2 - S12VR32/16)

<sup>1</sup> Read: Anytime

Write: Once in normal, anytime in special mode

#### Table 2-23. Module Routing Register 2 Field Descriptions

| Field         | Description                                                                                                                                         |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7<br>MODRR2   | MODule Routing Register 2 — TIM routing<br>1 TIM input capture channel 3 is connected to LPRXD<br>0 TIM input capture channel 3 is connected to PT3 |  |

| 5<br>MODRR2   |                                                                                                                                                     |  |

| 4<br>MODRR2   | MODule Routing Register 2 — SCI1 routing<br>1 TXD1 on PS3; RXD1 on PS2<br>0 TXD1 on PS1; RXD1 on PS0                                                |  |

| 3-0<br>MODRR2 |                                                                                                                                                     |  |

| Field    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5<br>PTP | <ul> <li>PorT data register port P — General-purpose input/output data, PWM output, ETRIG input, pin interrupt input/output, IRQ input</li> <li>The IRQ signal is mapped to this pin when used with the IRQ interrupt function. If enabled (IRQCR[IRQEN]=1) the I/O state of the pin is forced to be an input.</li> <li>When not used with the alternative function, the associated pin can be used as general-purpose I/O. In general-purpose output mode the register bit value is driven to the pin.</li> <li>If the associated data direction bit is set to 1, a read returns the value of the port register bit, otherwise the synchronized pin input state is read.</li> <li>The IRQ function takes precedence over the PWM and the general-purpose I/O function if enabled.</li> <li>The PWM function takes precedence over the general-purpose I/O function if the related channel is enabled.</li> <li>Pin interrupts can be generated if enabled in input or output mode.</li> <li>The ETRIG function has no effect on the I/O state.</li> </ul> |

| 4<br>PTP | <ul> <li>PorT data register port P — General-purpose input/output data, PWM output, ETRIG input, pin interrupt input/output The associated pin can be used as general-purpose I/O. In general-purpose output mode the register bit value is driven to the pin. If the associated data direction bit is set to 1, a read returns the value of the port register bit, otherwise the synchronized pin input state is read.</li> <li>The PWM function takes precedence over the general-purpose I/O function if the related channel is enabled.</li> <li>Pin interrupts can be generated if enabled in input or output mode.</li> <li>The ETRIG function has no effect on the I/O state.</li> </ul>                                                                                                                                                                                                                                                                                                                                                            |

| 3<br>PTP | <ul> <li>PorT data register port P — General-purpose input/output data, PWM output, pin interrupt input/output</li> <li>The associated pin can be used as general-purpose I/O. In general-purpose output mode the register bit value is driven to the pin. If the associated data direction bit is set to 1, a read returns the value of the port register bit, otherwise the synchronized pin input state is read.</li> <li>The PWM function takes precedence over the general-purpose I/O function if the related channel is enabled.</li> <li>Pin interrupts can be generated if enabled in input or output mode.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2<br>PTP | <ul> <li>PorT data register port P — General-purpose input/output data, PWM output, switchable high-current capable external supply with over-current protection (EVDD)</li> <li>The associated pin can be used as general-purpose I/O or as a supply for external devices such as Hall sensors (see Section 2.5.3, "Over-Current Protection on EVDD". In output mode the register bit value is driven to the pin. If the associated data direction bit is set to 1, a read returns the value of the port register bit, otherwise the synchronized pin input state is read.</li> <li>The PWM function takes precedence over the general-purpose I/O function if the related channel is enabled.</li> <li>Pin interrupts can be generated if enabled in input or output mode.</li> <li>An over-current interrupt can be generated if enabled. Refer to Section 2.4.4.3, "Over-Current Interrupt and Protection"</li> </ul>                                                                                                                                  |

### Table 2-25. PTP Register Field Descriptions

Be aware that the output frequency varies with the TC trimming. A frequency trimming correction is therefore necessary. The values provided in Table 4-27 are typical values at ambient temperature which can vary from device to device.

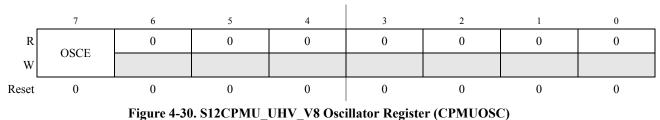

## 4.3.2.21 S12CPMU\_UHV\_V8 Oscillator Register (CPMUOSC)

This register configures the external oscillator (XOSCLCP).

0x02FA

Read: Anytime

Write: Anytime if PROT=0 (CPMUPROT register) and PLLSEL=1 (CPMUCLKS register). Else write has no effect.

#### NOTE.

Write to this register clears the LOCK and UPOSC status bits.

#### Table 4-28. CPMUOSC Field Descriptions

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7<br>OSCE | <ul> <li>Oscillator Enable Bit — This bit enables the external oscillator (XOSCLCP). The UPOSC status bit in the CPMUFLG register indicates when the oscillation is stable and OSCCLK can be selected as source of the Bus Clock or source of the COP or RTI.If the oscillator clock monitor reset is enabled (OMRE = 1 in CPMUOSC2 register), then a loss of oscillation will lead to an oscillator clock monitor reset.</li> <li>0 External oscillator is disabled. REFCLK for PLL is IRCCLK.</li> <li>1 External oscillator is enabled. External oscillator clock divided by REFDIV.</li> <li>If OSCE bit has been set (write "1") then the EXTAL and XTAL pins are exclusively reserved for the oscillator and</li> </ul> |  |

|           | they can not be used anymore as general purpose I/O until the next system reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|           | <b>Note:</b> When starting up the external oscillator (either by programming OSCE bit to 1 or on exit from Full Stop Mode with OSCE bit already 1) the software must wait for a minimum time equivalent to the startup-time of the external oscillator t <sub>UPOSC</sub> before entering Pseudo Stop Mode.                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

# 5.4.9 SYNC — Request Timed Reference Pulse

The SYNC command is unlike other BDM commands because the host does not necessarily know the correct communication speed to use for BDM communications until after it has analyzed the response to the SYNC command. To issue a SYNC command, the host should perform the following steps:

- 1. Drive the BKGD pin low for at least 128 cycles at the lowest possible BDM serial communication frequency (The lowest serial communication frequency is determined by the settings for the VCO clock (CPMUSYNR). The BDM clock frequency is always VCO clock frequency divided by 8.)

- 2. Drive BKGD high for a brief speedup pulse to get a fast rise time (this speedup pulse is typically one cycle of the host clock.)

- 3. Remove all drive to the BKGD pin so it reverts to high impedance.

- 4. Listen to the BKGD pin for the sync response pulse.

Upon detecting the SYNC request from the host, the target performs the following steps:

- 1. Discards any incomplete command received or bit retrieved.

- 2. Waits for BKGD to return to a logic one.

- 3. Delays 16 cycles to allow the host to stop driving the high speedup pulse.

- 4. Drives BKGD low for 128 cycles at the current BDM serial communication frequency.

- 5. Drives a one-cycle high speedup pulse to force a fast rise time on BKGD.

- 6. Removes all drive to the BKGD pin so it reverts to high impedance.

The host measures the low time of this 128 cycle SYNC response pulse and determines the correct speed for subsequent BDM communications. Typically, the host can determine the correct communication speed within a few percent of the actual target speed and the communication protocol can easily tolerate speed errors of several percent.

As soon as the SYNC request is detected by the target, any partially received command or bit retrieved is discarded. This is referred to as a soft-reset, equivalent to a time-out in the serial communication. After the SYNC response, the target will consider the next negative edge (issued by the host) as the start of a new BDM command or the start of new SYNC request.

Another use of the SYNC command pulse is to abort a pending ACK pulse. The behavior is exactly the same as in a regular SYNC command. Note that one of the possible causes for a command to not be acknowledged by the target is a host-target synchronization problem. In this case, the command may not have been understood by the target and so an ACK response pulse will not be issued.

# 5.4.10 Instruction Tracing

When a TRACE1 command is issued to the BDM in active BDM, the CPU exits the standard BDM firmware and executes a single instruction in the user code. Once this has occurred, the CPU is forced to return to the standard BDM firmware and the BDM is active and ready to receive a new command. If the TRACE1 command is issued again, the next user instruction will be executed. This facilitates stepping or tracing through the user code one instruction at a time.

match for both comparators happens on the same bus cycle. A match condition on only one comparator is not valid. An aligned word access which straddles the range boundary is valid only if the aligned address is inside the range.

## 6.4.2.2.2 Outside Range (address < CompA\_Addr or address > CompB\_Addr)

In the Outside Range comparator mode, comparator pair A and B can be configured for range comparisons. A single match condition on either of the comparators is recognized as valid. An aligned word access which straddles the range boundary is valid only if the aligned address is outside the range.

Outside range mode in combination with tagging can be used to detect if the opcode fetches are from an unexpected range. In forced match mode the outside range match would typically be activated at any interrupt vector fetch or register access. This can be avoided by setting the upper range limit to \$3FFFF or lower range limit to \$00000 respectively.

# 6.4.3 Match Modes (Forced or Tagged)

Match modes are used as qualifiers for a state sequencer change of state. The Comparator control register TAG bits select the match mode. The modes are described in the following sections.

# 6.4.3.1 Forced Match

When configured for forced matching, a comparator channel match can immediately initiate a transition to the next state sequencer state whereby the corresponding flags in DBGSR are set. The state control register for the current state determines the next state. Forced matches are typically generated 2-3 bus cycles after the final matching address bus cycle, independent of comparator RWE/RW settings. Furthermore since opcode fetches occur several cycles before the opcode execution a forced match of an opcode address typically precedes a tagged match at the same address.

## 6.4.3.2 Tagged Match

If a CPU taghit occurs a transition to another state sequencer state is initiated and the corresponding DBGSR flags are set. For a comparator related taghit to occur, the DBG must first attach tags to instructions as they are fetched from memory. When the tagged instruction reaches the execution stage of the instruction queue a taghit is generated by the CPU. This can initiate a state sequencer transition.

## 6.4.3.3 Immediate Trigger

Independent of comparator matches it is possible to initiate a tracing session and/or breakpoint by writing to the TRIG bit in DBGC1. If configured for begin aligned tracing, this triggers the state sequencer into the Final State, if configured for end alignment, setting the TRIG bit disarms the module, ending the session and issues a forced breakpoint request to the CPU.

It is possible to set both TRIG and ARM simultaneously to generate an immediate trigger, independent of the current state of ARM.

# 8.1.2 Modes of Operation

### 8.1.2.1 Conversion Modes

There is software programmable selection between performing **single** or **continuous conversion** on a **single channel** or **multiple channels**.

## 8.1.2.2 MCU Operating Modes

### • Stop Mode

Entering Stop Mode aborts any conversion sequence in progress and if a sequence was aborted restarts it after exiting stop mode. This has the same effect/consequences as starting a conversion sequence with write to ATDCTL5. So after exiting from stop mode with a previously aborted sequence all flags are cleared etc.

### • Wait Mode

ADC12B6CV2 behaves same in Run and Wait Mode. For reduced power consumption continuous conversions should be aborted before entering Wait mode.

### • Freeze Mode

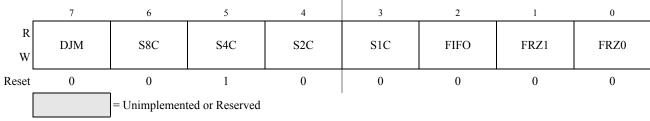

In Freeze Mode the ADC12B6CV2 will either continue or finish or stop converting according to the FRZ1 and FRZ0 bits. This is useful for debugging and emulation.

Analog-to-Digital Converter (ADC12B6CV2)

# 8.3.2.4 ATD Control Register 3 (ATDCTL3)

Writes to this register will abort current conversion sequence.

Module Base + 0x0003

#### Figure 8-6. ATD Control Register 3 (ATDCTL3)

Read: Anytime

Write: Anytime

| Field                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7<br>DJM                     | <ul> <li>Result Register Data Justification — Result data format is always unsigned. This bit controls justification of conversion data in the result registers.</li> <li>0 Left justified data in the result registers.</li> <li>1 Right justified data in the result registers.</li> <li>Table 8-9 gives example ATD results for an input signal range between 0 and 5.12 Volts.</li> </ul>                                                                                                               |  |

| 6–3<br>S8C, S4C,<br>S2C, S1C | <b>Conversion Sequence Length</b> — These bits control the number of conversions per sequence. Table 8-10 shows all combinations. At reset, S4C is set to 1 (sequence length is 4). This is to maintain software continuity to HC12 family.                                                                                                                                                                                                                                                                 |  |

| 2<br>FIFO                    | <b>Result Register FIFO Mode</b> — If this bit is zero (non-FIFO mode), the A/D conversion results map into the result registers based on the conversion sequence; the result of the first conversion appears in the first result register (ATDDR0), the second result in the second result register (ATDDR1), and so on.                                                                                                                                                                                   |  |

|                              | If this bit is one (FIFO mode) the conversion counter is not reset at the beginning or end of a conversion sequence; sequential conversion results are placed in consecutive result registers. In a continuously scanning conversion sequence, the result register counter will wrap around when it reaches the end of the result register file. The conversion counter value (CC3-0 in ATDSTAT0) can be used to determine where in the result register file, the current conversion result will be placed. |  |

|                              | Aborting a conversion or starting a new conversion clears the conversion counter even if FIFO=1. So the first result of a new conversion sequence, started by writing to ATDCTL5, will always be place in the first result register (ATDDDR0). Intended usage of FIFO mode is continuos conversion (SCAN=1) or triggered conversion (ETRIG=1).                                                                                                                                                              |  |

|                              | Which result registers hold valid data can be tracked using the conversion complete flags. Fast flag clear mode may be useful in a particular application to track valid data.                                                                                                                                                                                                                                                                                                                              |  |

|                              | <ul> <li>If this bit is one, automatic compare of result registers is always disabled, that is ADC12B6CV2 will behave as if ACMPIE and all CPME[n] were zero.</li> <li>0 Conversion results are placed in the corresponding result register up to the selected sequence length.</li> <li>1 Conversion results are placed in consecutive result registers (wrap around at end).</li> </ul>                                                                                                                   |  |

| 1–0<br>FRZ[1:0]              | <b>Background Debug Freeze Enable</b> — When debugging an application, it is useful in many cases to have the ATD pause when a breakpoint (Freeze Mode) is encountered. These 2 bits determine how the ATD will respond to a breakpoint as shown in Table 8-11. Leakage onto the storage node and comparator reference capacitors may compromise the accuracy of an immediately frozen conversion depending on the length of the freeze period.                                                             |  |

#### Table 8-8. ATDCTL3 Field Descriptions

Analog-to-Digital Converter (ADC12B6CV2)

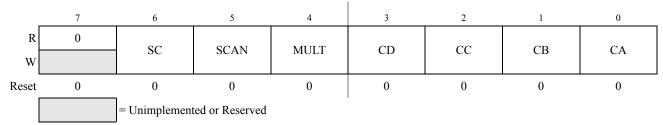

# 8.3.2.6 ATD Control Register 5 (ATDCTL5)

Writes to this register will abort current conversion sequence and start a new conversion sequence. If the external trigger function is enabled (ETRIGE=1) an initial write to ATDCTL5 is required to allow starting of a conversion sequence which will then occur on each trigger event. Start of conversion means the beginning of the sampling phase.

Module Base + 0x0005

Figure 8-8. ATD Control Register 5 (ATDCTL5)

## Read: Anytime

Write: Anytime

| Field                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 6<br>SC                  | <ul> <li>Special Channel Conversion Bit — If this bit is set, then special channel conversion can be selected using CD, CC, CB and CA of ATDCTL5. Table 8-15 lists the coding.</li> <li>O Special channel conversions disabled</li> <li>1 Special channel conversions enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 5<br>SCAN                | Continuous Conversion Sequence Mode — This bit selects whether conversion sequences are performed continuously or only once. If external trigger function is enabled (ETRIGE=1) setting this bit has no effect, thus the external trigger always starts a single conversion sequence.         0       Single conversion sequence         1       Continuous conversion sequences (scan mode)                                                                                                                                                                                                                                                                                                                                                                        |  |

| 4<br>MULT                | Multi-Channel Sample Mode — When MULT is 0, the ATD sequence controller samples only from the specified analog input channel for an entire conversion sequence. The analog channel is selected by channel selection code (control bits CD/CC/CB/CA located in ATDCTL5). When MULT is 1, the ATD sequence controller samples across channels. The number of channels sampled is determined by the sequence length value (S8C, S4C, S2C, S1C). The first analog channel examined is determined by channel selection code (CD, CC, CB, CA control bits); subsequent channels sampled in the sequence are determined by incrementing the channel selection code or wrapping around to AN0 (channel 0). 0 Sample only one channel 1 Sample across several channels       |  |

| 3–0<br>CD, CC,<br>CB, CA | Analog Input Channel Select Code — These bits select the analog input channel(s). Table 8-15 lists the coding used to select the various analog input channels.<br>In the case of single channel conversions (MULT=0), this selection code specifies the channel to be examined.<br>In the case of multiple channel conversions (MULT=1), this selection code specifies the first channel to be examined in the conversion sequence. Subsequent channels are determined by incrementing the channel selection code or wrapping around to AN0 (after converting the channel defined by the Wrap Around Channel Select Bits WRAP3-0 in ATDCTL0). When starting with a channel number higher than the one defined by WRAP3-0 the first wrap around will be AN5 to AN0. |  |

#### Table 8-14. ATDCTL5 Field Descriptions

Clock A is used as an input to an 8-bit down counter. This down counter loads a user programmable scale value from the scale register (PWMSCLA). When the down counter reaches one, a pulse is output and the 8-bit counter is re-loaded. The output signal from this circuit is further divided by two. This gives a greater range with only a slight reduction in granularity. Clock SA equals clock A divided by two times the value in the PWMSCLA register.

### NOTE

Clock SA = Clock A / (2 \* PWMSCLA)

When PWMSCLA =\$00, PWMSCLA value is considered a full scale value of 256. Clock A is thus divided by 512.

Similarly, clock B is used as an input to an 8-bit down counter followed by a divide by two producing clock SB. Thus, clock SB equals clock B divided by two times the value in the PWMSCLB register.

### NOTE

Clock SB = Clock B / (2 \* PWMSCLB)

When PWMSCLB =\$00, PWMSCLB value is considered a full scale value of 256. Clock B is thus divided by 512.

As an example, consider the case in which the user writes \$FF into the PWMSCLA register. Clock A for this case will be bus clock divided by 4. A pulse will occur at a rate of once every 255x4 bus cycles. Passing this through the divide by two circuit produces a clock signal at an bus clock divided by 2040 rate. Similarly, a value of \$01 in the PWMSCLA register when clock A is bus clock divided by 4 will produce a clock at an bus clock divided by 8 rate.

Writing to PWMSCLA or PWMSCLB causes the associated 8-bit down counter to be re-loaded. Otherwise, when changing rates the counter would have to count down to \$01 before counting at the proper rate. Forcing the associated counter to re-load the scale register value every time PWMSCLA or PWMSCLB is written prevents this.

### NOTE

Writing to the scale registers while channels are operating can cause irregularities in the PWM outputs.

# 9.4.1.3 Clock Select

Each PWM channel has the capability of selecting one of four clocks, clock A, clock SA, clock B or clock SB. The clock selection is done with the PCLKx control bits in the PWMCLK register and PCLKABx control bits in PWMCLKAB register. For backward compatibility consideration, the reset value of PWMCLK and PWMCLKAB configures following default clock selection.

For channels 0, 1, 4, and 5 the clock choices are clock A.

For channels 2, 3, 6, and 7 the clock choices are clock B.

## NOTE

Changing clock control bits while channels are operating can cause irregularities in the PWM outputs.

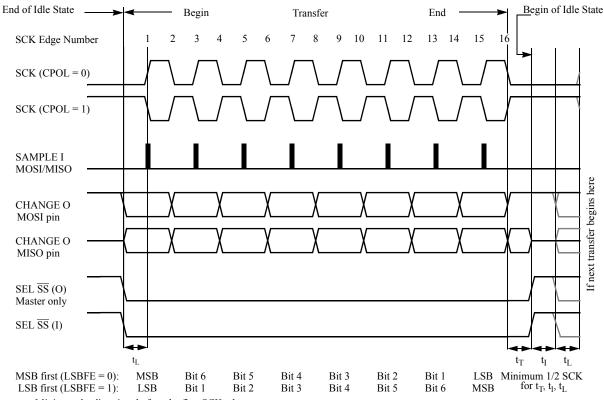

#### Serial Peripheral Interface (S12SPIV5) for S12VR64

$t_L$  = Minimum leading time before the first SCK edge

$t_T$  = Minimum trailing time after the last SCK edge

$t_{I}$  = Minimum idling time between transfers (minimum  $\overline{SS}$  high time)

$t_L$ ,  $t_T$ , and  $t_I$  are guaranteed for the master mode and required for the slave mode.

#### Figure 11-12. SPI Clock Format 0 (CPHA = 0), with 8-bit Transfer Width selected (XFRW = 0)

#### 64 KByte Flash Module (S12FTMRG64K512V1) for S12VR64

| CCOBIX[2:0] | FCCOB Parameters                                  |                                                   |

|-------------|---------------------------------------------------|---------------------------------------------------|

| 000 0x09    |                                                   | Global address [17:16] to identify<br>Flash block |

| 001         | Global address [15:0] in Flash block to be erased |                                                   |

Table 18-46. Erase Flash Block Command FCCOB Requirements

Upon clearing CCIF to launch the Erase Flash Block command, the Memory Controller will erase the selected Flash block and verify that it is erased. The CCIF flag will set after the Erase Flash Block operation has completed.

| Register | Error Bit | Error Condition                                                                                        |  |

|----------|-----------|--------------------------------------------------------------------------------------------------------|--|

|          | ACCERR    | Set if CCOBIX[2:0] != 001 at command launch                                                            |  |

|          |           | Set if command not available in current mode (see Table 18-27)                                         |  |

|          |           | Set if an invalid global address [17:16] is supplied                                                   |  |

| FSTAT    |           | Set if the supplied P-Flash address is not phrase-aligned or if the EEPROM address is not word-aligned |  |

|          | FPVIOL    | Set if an area of the selected Flash block is protected                                                |  |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                                    |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation                    |  |

Table 18-47. Erase Flash Block Command Error Handling

### 18.4.6.9 Erase P-Flash Sector Command

The Erase P-Flash Sector operation will erase all addresses in a P-Flash sector.

Table 18-48. Erase P-Flash Sector Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters                                                                                                                          |                                                                  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| 000         | 0x0A                                                                                                                                      | Global address [17:16] to identify<br>P-Flash block to be erased |

| 001         | Global address [15:0] anywhere within the sector to be erased.<br>Refer to Section 18.1.2.1 P-Flash Features for the P-Flash sector size. |                                                                  |

Upon clearing CCIF to launch the Erase P-Flash Sector command, the Memory Controller will erase the selected Flash sector and then verify that it is erased. The CCIF flag will be set after the Erase P-Flash Sector operation has completed.

#### 64 KByte Flash Module (S12FTMRG64K512V1) for S12VR64

Upon clearing CCIF to launch the Set Field Margin Level command, the Memory Controller will set the Table 18-57. Set Field Margin Level Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters      |                                                      |  |  |  |  |

|-------------|-----------------------|------------------------------------------------------|--|--|--|--|

| 000         | 0x0E                  | Flash block selection code [1:0]. See<br>Table 18-34 |  |  |  |  |

| 001         | Margin level setting. |                                                      |  |  |  |  |

field margin level for the targeted block and then set the CCIF flag.

### NOTE

When the EEPROM block is targeted, the EEPROM field margin levels are applied only to the EEPROM reads. However, when the P-Flash block is targeted, the P-Flash field margin levels are applied to both P-Flash and EEPROM reads. It is not possible to apply field margin levels to the P-Flash block only.

Valid margin level settings for the Set Field Margin Level command are defined in Table 18-58.

| CCOB<br>(CCOBIX=001) | Level Description                 |

|----------------------|-----------------------------------|

| 0x0000               | Return to Normal Level            |

| 0x0001               | User Margin-1 Level <sup>1</sup>  |

| 0x0002               | User Margin-0 Level <sup>2</sup>  |

| 0x0003               | Field Margin-1 Level <sup>1</sup> |

| 0x0004               | Field Margin-0 Level <sup>2</sup> |

### Table 18-58. Valid Set Field Margin Level Settings

<sup>1</sup> Read margin to the erased state

<sup>2</sup> Read margin to the programmed state

#### Table 18-59. Set Field Margin Level Command Error Handling

| Register | Error Bit | Error Condition                                                              |  |  |  |  |  |

|----------|-----------|------------------------------------------------------------------------------|--|--|--|--|--|

|          |           | Set if CCOBIX[2:0] != 001 at command launch                                  |  |  |  |  |  |

|          | ACCERR    | Set if command not available in current mode (see Table 18-27)               |  |  |  |  |  |

|          | ACCERK    | Set if an invalid FlashBlockSelectionCode[1:0] is supplied (See Table 18-34) |  |  |  |  |  |

| FSTAT    |           | Set if an invalid margin level setting is supplied                           |  |  |  |  |  |

|          | FPVIOL    | None                                                                         |  |  |  |  |  |

|          | MGSTAT1   | None                                                                         |  |  |  |  |  |

|          | MGSTAT0   | None                                                                         |  |  |  |  |  |

#### 32 KByte Flash Module (S12FTMRG32K128V1) for S12VR32

| Field              | Description                                                                                                                                                                                                                                                                                     |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3<br>MGBUSY        | Memory Controller Busy Flag — The MGBUSY flag reflects the active state of the Memory Controller.         0 Memory Controller is idle         1 Memory Controller is busy executing a Flash command (CCIF = 0)                                                                                  |

| 2<br>RSVD          | <b>Reserved Bit</b> — This bit is reserved and always reads 0.                                                                                                                                                                                                                                  |

| 1–0<br>MGSTAT[1:0] | <b>Memory Controller Command Completion Status Flag</b> — One or more MGSTAT flag bits are set if an error is detected during execution of a Flash command or during the Flash reset sequence. See Section 19.4.6, "Flash Command Description," and Section 19.6, "Initialization" for details. |

#### Table 19-15. FSTAT Field Descriptions (continued)

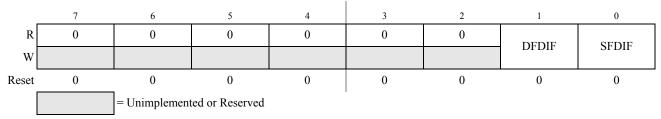

## **19.3.2.8** Flash Error Status Register (FERSTAT)

The FERSTAT register reflects the error status of internal Flash operations.

All flags in the FERSTAT register are readable and only writable to clear the flag.

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>DFDIF | <ul> <li>Double Bit Fault Detect Interrupt Flag — The setting of the DFDIF flag indicates that a double bit fault was detected in the stored parity and data bits during a Flash array read operation or that a Flash array read operation returning invalid data was attempted on a Flash block that was under a Flash command operation.<sup>1</sup> The DFDIF flag is cleared by writing a 1 to DFDIF. Writing a 0 to DFDIF has no effect on DFDIF.<sup>2</sup></li> <li>0 No double bit fault detected</li> <li>1 Double bit fault detected or a Flash array read operation returning invalid data was attempted while command running</li> </ul>                                                                                           |

| 0<br>SFDIF | <ul> <li>Single Bit Fault Detect Interrupt Flag — With the IGNSF bit in the FCNFG register clear, the SFDIF flag indicates that a single bit fault was detected in the stored parity and data bits during a Flash array read operation or that a Flash array read operation returning invalid data was attempted on a Flash block that was under a Flash command operation.<sup>1</sup> The SFDIF flag is cleared by writing a 1 to SFDIF. Writing a 0 to SFDIF has no effect on SFDIF.</li> <li>0 No single bit fault detected</li> <li>1 Single bit fault detected or a Flash array read operation returning invalid data was attempted or a Flash array read operation returning invalid data was attempted while command running</li> </ul> |

<sup>1</sup> The single bit fault and double bit fault flags are mutually exclusive for parity errors (an ECC fault occurrence can be either single fault or double fault but never both). A simultaneous access collision (Flash array read operation returning invalid data attempted while command running) is indicated when both SFDIF and DFDIF flags are high.

<sup>2</sup> There is a one cycle delay in storing the ECC DFDIF and SFDIF fault flags in this register. At least one NOP is required after a flash memory read before checking FERSTAT for the occurrence of ECC errors.

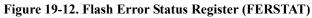

Figure 19-14. P-Flash Protection Scenarios

MC9S12VR Family Reference Manual, Rev. 4.2

#### 32 KByte Flash Module (S12FTMRG32K128V1) for S12VR32

## 19.3.2.12 Flash Reserved1 Register (FRSV1)

This Flash register is reserved for factory testing.

rigure 19-10. Flash Reserveur Register (F

All bits in the FRSV1 register read 0 and are not writable.

## 19.3.2.13 Flash Reserved2 Register (FRSV2)

This Flash register is reserved for factory testing.

Figure 19-19. Flash Reserved2 Register (FRSV2)

All bits in the FRSV2 register read 0 and are not writable.

# 19.3.2.14 Flash Reserved3 Register (FRSV3)

This Flash register is reserved for factory testing.

All bits in the FRSV3 register read 0 and are not writable.

## 19.3.2.15 Flash Reserved4 Register (FRSV4)

This Flash register is reserved for factory testing.

MC9S12VR Family Reference Manual, Rev. 4.2

#### 32 KByte Flash Module (S12FTMRG32K128V1) for S12VR32

| CCOBIX[2:0] | FCCOB Parameters                                  |                                                   |  |  |  |  |

|-------------|---------------------------------------------------|---------------------------------------------------|--|--|--|--|

| 000         | 0x09                                              | Global address [17:16] to identify<br>Flash block |  |  |  |  |

| 001         | Global address [15:0] in Flash block to be erased |                                                   |  |  |  |  |

Upon clearing CCIF to launch the Erase Flash Block command, the Memory Controller will erase the selected Flash block and verify that it is erased. The CCIF flag will set after the Erase Flash Block operation has completed.

| Register | Error Bit | Error Condition                                                                                        |  |  |  |  |  |

|----------|-----------|--------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|          |           | Set if CCOBIX[2:0] != 001 at command launch                                                            |  |  |  |  |  |

|          |           | Set if command not available in current mode (see Table 19-27)                                         |  |  |  |  |  |

| FSTAT    | ACCERR    | Set if an invalid global address [17:16] is supplied                                                   |  |  |  |  |  |

|          |           | Set if the supplied P-Flash address is not phrase-aligned or if the EEPROM address is not word-aligned |  |  |  |  |  |

|          | FPVIOL    | Set if an area of the selected Flash block is protected                                                |  |  |  |  |  |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                                    |  |  |  |  |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation                    |  |  |  |  |  |

Table 19-47. Erase Flash Block Command Error Handling

### 19.4.6.9 Erase P-Flash Sector Command

The Erase P-Flash Sector operation will erase all addresses in a P-Flash sector.

Table 19-48. Erase P-Flash Sector Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters                                                                                                                          |                                                                  |  |  |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--|--|--|--|

| 000         | 0x0A                                                                                                                                      | Global address [17:16] to identify<br>P-Flash block to be erased |  |  |  |  |

| 001         | Global address [15:0] anywhere within the sector to be erased.<br>Refer to Section 19.1.2.1 P-Flash Features for the P-Flash sector size. |                                                                  |  |  |  |  |

Upon clearing CCIF to launch the Erase P-Flash Sector command, the Memory Controller will erase the selected Flash sector and then verify that it is erased. The CCIF flag will be set after the Erase P-Flash Sector operation has completed.

| P.15 | 0x00C8-0x00CF | Serial Con | nmunication | Interface | (SCI0) Map |

|------|---------------|------------|-------------|-----------|------------|

|------|---------------|------------|-------------|-----------|------------|

| Address  | Name                  |                 | Bit 7      | Bit 6      | Bit 5        | Bit 4        | Bit 3 | Bit 2  | Bit 1  | Bit 0    |       |    |  |

|----------|-----------------------|-----------------|------------|------------|--------------|--------------|-------|--------|--------|----------|-------|----|--|

| 0x00C8   | SCI0BDH <sup>1</sup>  | R<br>W          | SBR15      | SBR14      | SBR13        | SBR12        | SBR11 | SBR10  | SBR9   | SBR8     |       |    |  |

| 0x00C9   | SCI0BDL <sup>1</sup>  | R<br>W          | SBR7       | SBR6       | SBR5         | SBR4         | SBR3  | SBR2   | SBR1   | SBR0     |       |    |  |

| 0x00CA   | SCI0CR1 <sup>1</sup>  | R<br>W          | LOOPS      | SCISWAI    | RSRC         | М            | WAKE  | ILT    | PE     | РТ       |       |    |  |

| 0x00C8   | SCI0ASR1 <sup>2</sup> | R<br>W          | RXEDGIF    | 0          | 0            | 0            | 0     | BERRV  | BERRIF | BKDIF    |       |    |  |

| 0x00C9   | SCI0ACR1 <sup>2</sup> | R               | RXEDGIE    | 0          | 0            | 0            | 0     | 0      | BERRIE | BKDIE    |       |    |  |

| 0110000  | Dentificiti           | W               |            |            |              |              |       |        | DEndel | DIIDIE   |       |    |  |

| 0x00CA   | SCI0ACR2 <sup>2</sup> | R               | IREN       | TNP1       | TNP0         | 0            | 0     | BERRM1 | BERRM0 | BKDFE    |       |    |  |

| 01100011 | V V                   | Service Service | W          |            |              | 11110        |       |        |        | DERIGINO | DIDIE |    |  |

| 0x00CB   | SCI0CR2               | R<br>W          | TIE        | TCIE       | RIE          | ILIE         | TE    | RE     | RWU    | SBK      |       |    |  |

| 000000   | SCIOSD 1              | R               | TDRE       | ТС         | RDRF         | IDLE         | OR    | NF     | FE     | PF       |       |    |  |

| 0x00CC   | SCI0SR1               | W               |            |            |              |              |       |        |        |          |       |    |  |

| 0.0000   | CLOCED 2              | SCI0SR2 R AMA   |            | 0          | 0            | TYDOI        | DUDOI | DBW12  | TYDD   | RAF      |       |    |  |

| 0x00CD   | SCI0SR2               |                 | W          | AMAP       |              |              | TXPOL | RXPOL  | BRK13  | TXDIR    |       |    |  |

| 0x00CE   | SCIADBU               | R               | R8 T       | Τ0         | 0            | 0            | 0     | 0      | 0      | 0        |       |    |  |

|          | SCIUDKH               | SCI0DRH         | LE SCIUDKH | VE SCIUDKI | UE SCIUDKI W | UUCE SCIUDKH |       | Т8     |        |          |       |    |  |

| 0x00CF   | SCI0DRL               | COMPRI          |            | R          | R7           | R6           | R5    | R4     | R3     | R2       | R1    | R0 |  |

|          |                       | W               | T7         | T6         | T5           | T4           | Т3    | T2     | T1     | Т0       |       |    |  |

<sup>1</sup> Those registers are accessible if the AMAP bit in the SCI0SR2 register is set to zero

<sup>2</sup> Those registers are accessible if the AMAP bit in the SCI0SR2 register is set to one

# P.32 0x0280-0x02EF Reserved

| Address | Name     |   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|----------|---|-------|-------|-------|-------|-------|-------|-------|-------|

| 0x0280- | Pasaruad | R | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0x02EF  | Reserved | W |       |       |       |       |       |       |       |       |

# P.33 0x02F0-0x02FF Clock and Power Management Unit (CPMU) Map 2 of 2

| Address | Name                  |             | Bit 7   | Bit 6             | Bit 5       | Bit 4   | Bit 3        | Bit 2   | Bit 1 | Bit 0  |  |  |

|---------|-----------------------|-------------|---------|-------------------|-------------|---------|--------------|---------|-------|--------|--|--|

| 0x02F0  | CPMUHTCL              | R<br>W      | 0       | 0                 | VSEL        | 0       | HTE          | HTDS    | HTIE  | HTIF   |  |  |

| 0x02F1  | CPMULVCTL             | R<br>W      | 0       | 0                 | 0           | 0       | 0            | LVDS    | LVIE  | LVIF   |  |  |

| 0x02F2  | CPMUAPICTL            | R<br>W      | APICLK  | 0                 | 0           | APIES   | APIEA        | APIFE   | APIE  | APIF   |  |  |

| 0x02F3  | CPMUACLKT<br>R        | R<br>W      | ACLKTR5 | ACLKTR4           | ACLKTR3     | ACLKTR2 | ACLKTR1      | ACLKTR0 | 0     | 0      |  |  |

| 0x02F4  | CPMUAPIRH             | R<br>W      | APIR15  | APIR14            | APIR13      | APIR12  | APIR11       | APIR10  | APIR9 | APIR8  |  |  |

| 0x02F5  | CPMUAPIRL             | R<br>W      | APIR7   | APIR6             | APIR5       | APIR4   | APIR3        | APIR2   | APIR1 | APIR0  |  |  |

| 0x02F6  | Reserved              | R           | 0       | 0                 | 0           | 0       | 0            | 0       | 0     | 0      |  |  |

| 0x02F7  | CPMUHTTR              | W<br>R<br>W | HTOE    | 0                 | 0           | 0       | HTTR3        | HTTR2   | HTTR1 | HTTR0  |  |  |

| 0x02F8  | CPMU<br>IRCTRIMH      | R<br>W      |         | -<br>-            | TCTRIM[3:0] | 0       | IRCTRIM[9:8] |         |       |        |  |  |

| 0x02F9  | CPMU<br>IRCTRIML      | R<br>W      |         | IRCTRIM[7:0]      |             |         |              |         |       |        |  |  |

| 0x02FA  | CPMUOSC               | R<br>W      | OSCE    | OSCE 0 0 Reserved |             |         |              |         |       |        |  |  |

| 0x02FB  | CPMUPROT              | R<br>W      | 0       | 0                 | 0           | 0       | 0            | 0       | 0     | PROT   |  |  |

| 0x02FC  | Reserved              | R<br>W      | 0       | 0                 | 0           | 0       | 0            | 0       | 0     | 0      |  |  |

| 0x02FD  | Reserved              | R<br>W      | 0       | 0                 | 0           | 0       | 0            | 0       | 0     | 0      |  |  |

| 0x02FE  | CPMUOSC2 <sup>1</sup> | R<br>W      | 0       | 0                 | 0           | 0       | 0            | 0       | OMRE  | OSCMOD |  |  |

| 0x02FF  | Reserved              | R<br>W      | 0       | 0                 | 0           | 0       | 0            | 0       | 0     | 0      |  |  |

<sup>1</sup> CPMUOSC2 Register is only available on S12VR32/16