Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | 12V1                                                                    |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 25MHz                                                                   |

| Connectivity               | IrDA, LINbus, SCI, SPI                                                  |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 28                                                                      |

| Program Memory Size        | 48KB (48K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 512 x 8                                                                 |

| RAM Size                   | 2K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 5.5V                                                            |

| Data Converters            | A/D 6x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 48-LQFP                                                                 |

| Supplier Device Package    | 48-LQFP (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12vr48f2clfr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.4.13 Serial Communication Interface Module (SCI)

- Full-duplex or single-wire operation

- Standard mark/space non-return-to-zero (NRZ) format

- Selectable IrDA 1.4 return-to-zero-inverted (RZI) format with programmable pulse widths

- 16-bit baud rate selection

- Programmable character length

- Programmable polarity for transmitter and receiver

- Active edge receive wake-up

- Break detect and transmit collision detect supporting LIN

# **1.4.14** Analog-to-Digital Converter Module (ATD)

- Up to 6-channel, 10-bit analog-to-digital converter

- 8-/10-bit resolution

- 3 us, 10-bit single conversion time

- Left or right justified result data

- Internal oscillator for conversion in stop modes

- Continuous conversion mode

- Multiple channel scans

- Pins can also be used as digital I/O

- Up to 6 pins can be used as keyboard wake-up interrupt (KWI)

- Internal voltages monitored with the ATD module

- V<sub>SUP</sub>, V<sub>SENSE</sub>, chip temperature sensor, high voltage inputs, V<sub>RH</sub>, V<sub>RL</sub>, V<sub>DDF</sub>

# 1.4.15 Supply Voltage Sense (BATS)

- VSENSE & VSUP pin low or a high voltage interrupt

- VSENSE & VSUP pin can be routed via an internal divider to the internal ADC

# 1.4.16 On-Chip Voltage Regulator system (VREG)

- Voltage regulator

- Linear voltage regulator directly supplied by VSUP (protected VBAT)

- Low-voltage detect with low-voltage interrupt on VSUP

- Capable of supplying both the MCU internally and providing additional external current (approximately 20mA) to supply other components within the electronic control unit.

- Over-temperature interrupt

- Internal Voltage regulator

- Linear voltage regulator with bandgap reference

- Low-voltage detect with low-voltage interrupt on VDDA

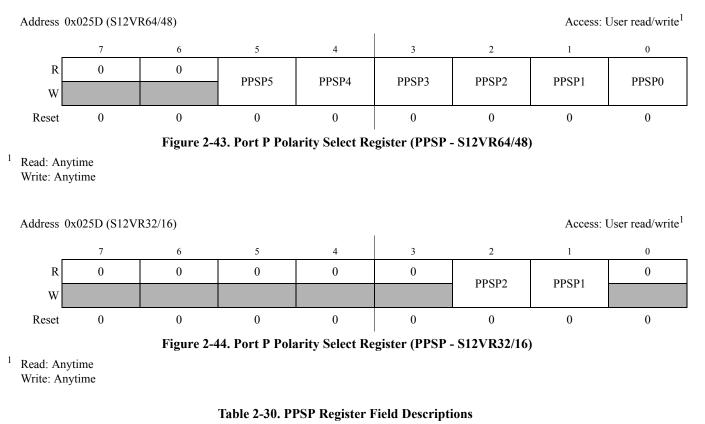

# 2.3.31 Port P Polarity Select Register (PPSP)

| Field | Description                                                                                                               |

|-------|---------------------------------------------------------------------------------------------------------------------------|

| 5-0   | Pull device Polarity Select register port P — Configure pull device polarity and pin interrupt edge polarity on input pin |

| PPSP  | This bit selects a pullup or a pulldown device if enabled on the associated port input pin.                               |

|       | This bit also selects the polarity of the active pin interrupt edge.                                                      |

|       | 1 A pulldown device is selected; rising edge selected                                                                     |

|       | 0 A pullup device is selected; falling edge selected                                                                      |

#### MC9S12VR Family Reference Manual, Rev. 4.2

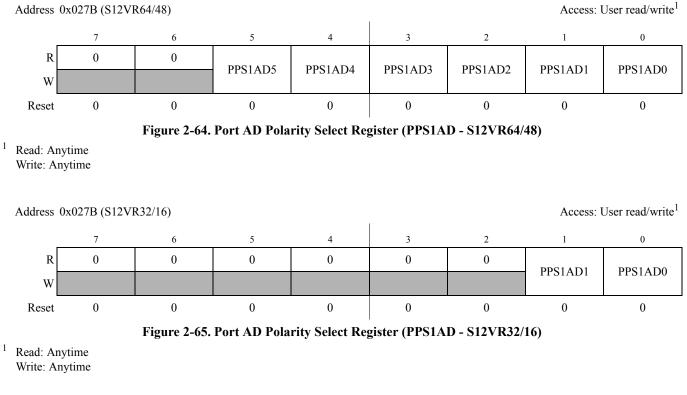

# 2.3.45 Port AD Polarity Select Register (PPS1AD)

#### Table 2-45. PPS1AD Register Field Descriptions

| Field  | Description                                                                                                                  |

|--------|------------------------------------------------------------------------------------------------------------------------------|

| 5-0    | Pull device Polarity Select register 1 port AD — Configure pull device polarity and pin interrupt edge polarity on input pin |

| PPS1AD | This bit selects a pullup or a pulldown device if enabled on the associated port input pin.                                  |

|        | This bit also selects the polarity of the active pin interrupt edge.                                                         |

|        | 1 A pulldown device is selected; rising edge selected                                                                        |

|        | 0 A pullup device is selected; falling edge selected                                                                         |

| Module Interrupt Sources | Local Enable<br>(S12VR64/48) | Local Enable<br>(S12VR32/16) |  |

|--------------------------|------------------------------|------------------------------|--|

| IRQ <sup>1</sup>         | IRQCR[IRQEN]                 | N/A                          |  |

| Port P pin interrupt     | PIEP[PIEP5-PIEP0]            | PIEP[PIEP2-PIEP1]            |  |

| Port L pin interrupt     | PIEL[PIEL3-PIEL0]            | PIEL[PIEL3-PIEL0]            |  |

| Port AD pin interrupt    | PIE1AD[PIE1AD5-PIE1AD0]      | PIE1AD[PIE1AD1-PIE1AD0]      |  |

| Port P over-current      | PIEP[OCIE]                   | PIEP[OCIE]                   |  |

| Table 2-50. | PIM | Interrupt | Sources |

|-------------|-----|-----------|---------|

|             |     |           | ~~~~~~  |

<sup>1</sup> S12VR64/48 only

## 2.4.4.1 XIRQ, IRQ Interrupts

The  $\overline{\text{XIRQ}}$  pin allows requesting non-maskable interrupts after reset initialization. During reset, the X bit in the condition code register is set and any interrupts are masked until software enables them.

The IRQ pin allows requesting asynchronous interrupts (S12VR64/48 only). The interrupt input is disabled out of reset. To enable the interrupt the IRQCR[IRQEN] bit must be set and the I bit cleared in the condition code register. The interrupt can be configured for level-sensitive or falling-edge-sensitive triggering. If IRQCR[IRQEN] is cleared while an interrupt is pending, the request will deassert.

Both interrupts are capable to wake-up the device from stop mode. Means for glitch filtering are not provided on these pins.

## 2.4.4.2 Pin Interrupts and Wakeup

Ports P, L and AD offer pin interrupt capability. The related interrupt enable (PIE) as well as the sensitivity to rising or falling edges (PPS) can be individually configured on per-pin basis. All bits/pins in a port share the same interrupt vector. Interrupts can be used with the pins configured as inputs or outputs.

An interrupt is generated when a bit in the port interrupt flag (PIF) and its corresponding port interrupt enable (PIE) are both set. The pin interrupt feature is also capable to wake up the CPU when it is in stop or wait mode.

A digital filter on each pin prevents short pulses from generating an interrupt. A valid edge on an input is detected if 4 consecutive samples of a passive level are followed by 4 consecutive samples of an active level. Else the sampling logic is restarted.

In run and wait mode the filters are continuously clocked by the bus clock. Pulses with a duration of  $t_{PULSE} < n_{P\_MASK}/f_{bus}$  are assuredly filtered out while pulses with a duration of  $t_{PULSE} > n_{P\_PASS}/f_{bus}$  guarantee a pin interrupt.

In stop mode the clock is generated by an RC-oscillator. The minimum pulse length varies over process conditions, temperature and voltage (Figure 2-72). Pulses with a duration of  $t_{PULSE} < t_{P\_MASK}$  are assuredly filtered out while pulses with a duration of  $t_{PULSE} > t_{P\_PASS}$  guarantee a wakeup event.

Please refer to the appendix table "Pin Interrupt Characteristics" for pulse length limits.

To maximize current saving the RC oscillator is active only if the following condition is true on any individual pin:

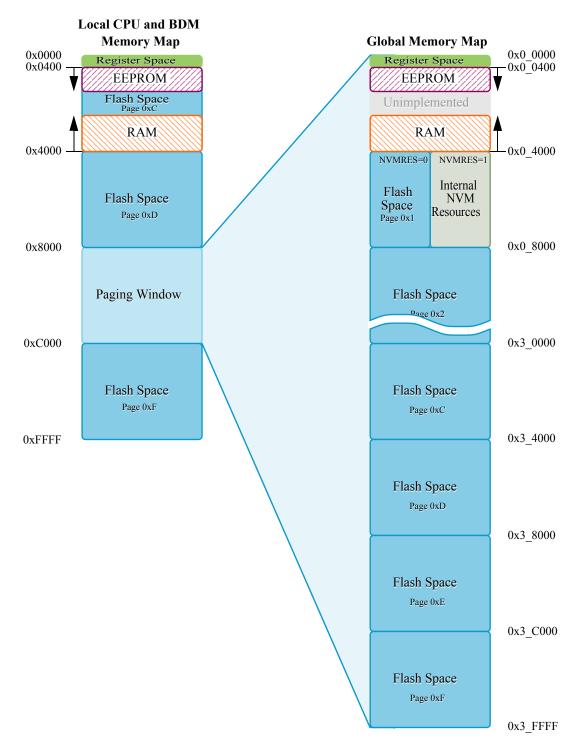

Figure 3-11. Local to Global Address Mapping

MC9S12VR Family Reference Manual, Rev. 4.2

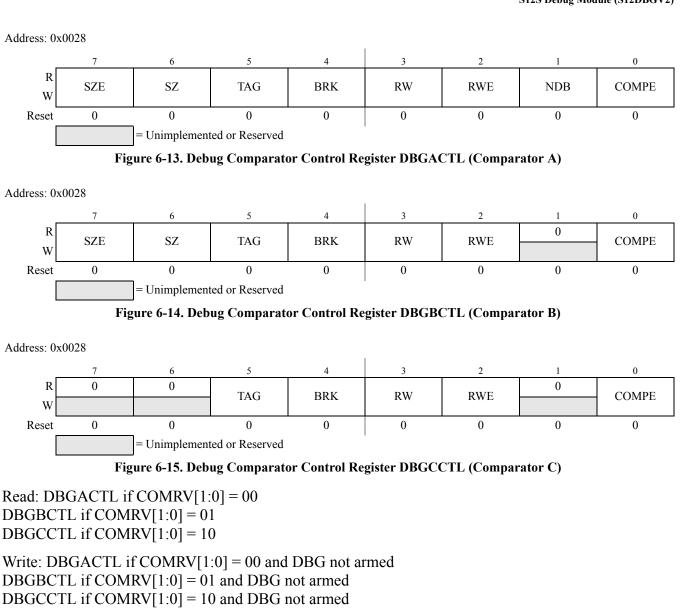

#### Table 6-22. DBGXCTL Field Descriptions

| Field | Description                                                                                                                                                                                                                                                                                                                      |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SZE   | <ul> <li>Size Comparator Enable Bit — The SZE bit controls whether access size comparison is enabled for the associated comparator. This bit is ignored if the TAG bit in the same register is set.</li> <li>0 Word/Byte access size is not used in comparison</li> <li>1 Word/Byte access size is used in comparison</li> </ul> |

| SZ    | <ul> <li>Size Comparator Value Bit — The SZ bit selects either word or byte access size in comparison for the associated comparator. This bit is ignored if the SZE bit is cleared or if the TAG bit in the same register is set.</li> <li>0 Word access size is compared</li> <li>1 Byte access size is compared</li> </ul>     |

Analog-to-Digital Converter (ADC12B6CV2)

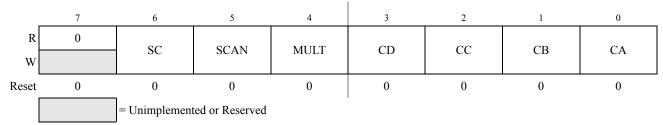

# 8.3.2.6 ATD Control Register 5 (ATDCTL5)

Writes to this register will abort current conversion sequence and start a new conversion sequence. If the external trigger function is enabled (ETRIGE=1) an initial write to ATDCTL5 is required to allow starting of a conversion sequence which will then occur on each trigger event. Start of conversion means the beginning of the sampling phase.

Module Base + 0x0005

Figure 8-8. ATD Control Register 5 (ATDCTL5)

### Read: Anytime

Write: Anytime

| Field                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 6<br>SC                  | <ul> <li>Special Channel Conversion Bit — If this bit is set, then special channel conversion can be selected using CD, CC, CB and CA of ATDCTL5. Table 8-15 lists the coding.</li> <li>O Special channel conversions disabled</li> <li>1 Special channel conversions enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| 5<br>SCAN                | Continuous Conversion Sequence Mode — This bit selects whether conversion sequences are performed continuously or only once. If external trigger function is enabled (ETRIGE=1) setting this bit has no effect, thus the external trigger always starts a single conversion sequence.         0       Single conversion sequence         1       Continuous conversion sequences (scan mode)                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| 4<br>MULT                | Multi-Channel Sample Mode — When MULT is 0, the ATD sequence controller samples only from the specified analog input channel for an entire conversion sequence. The analog channel is selected by channel selection code (control bits CD/CC/CB/CA located in ATDCTL5). When MULT is 1, the ATD sequence controller samples across channels. The number of channels sampled is determined by the sequence length value (S8C, S4C, S2C, S1C). The first analog channel examined is determined by channel selection code (CD, CC, CB, CA control bits); subsequent channels sampled in the sequence are determined by incrementing the channel selection code or wrapping around to AN0 (channel 0). 0 Sample only one channel 1 Sample across several channels       |  |  |  |  |  |

| 3–0<br>CD, CC,<br>CB, CA | Analog Input Channel Select Code — These bits select the analog input channel(s). Table 8-15 lists the coding used to select the various analog input channels.<br>In the case of single channel conversions (MULT=0), this selection code specifies the channel to be examined.<br>In the case of multiple channel conversions (MULT=1), this selection code specifies the first channel to be examined in the conversion sequence. Subsequent channels are determined by incrementing the channel selection code or wrapping around to AN0 (after converting the channel defined by the Wrap Around Channel Select Bits WRAP3-0 in ATDCTL0). When starting with a channel number higher than the one defined by WRAP3-0 the first wrap around will be AN5 to AN0. |  |  |  |  |  |

#### Table 8-14. ATDCTL5 Field Descriptions

<sup>1</sup> The address bit identifies the frame as an address character. See Section 10.4.6.6, "Receiver Wakeup".

### **10.4.4 Baud Rate Generation**

A 16-bit modulus counter in the two baud rate generator derives the baud rate for both the receiver and the transmitter. The value from 0 to 65535 written to the SBR15:SBR0 bits determines the baud rate. The value from 0 to 4095 written to the SBR15:SBR4 bits determines the baud rate clock with SBR3:SBR0 for fine adjust. The SBR bits are in the SCI baud rate registers (SCIBDH and SCIBDL) for both transmit and receive baud generator. The baud rate clock is synchronized with the bus clock and drives the receiver. The baud rate clock divided by 16 drives the transmitter. The receiver has an acquisition rate of 16 samples per bit time.

Baud rate generation is subject to one source of error:

• Integer division of the bus clock may not give the exact target frequency.

Table 10-16 lists some examples of achieving target baud rates with a bus clock frequency of 25 MHz.

#### When IREN = 0 then,

SCI baud rate = SCI bus clock / (SCIBR[15:0])

| Bits<br>SBR[15:0] | Receiver <sup>1</sup><br>Clock (Hz) | Transmitter <sup>2</sup><br>Clock (Hz) | Target<br>Baud Rate | Error<br>(%) |

|-------------------|-------------------------------------|----------------------------------------|---------------------|--------------|

| 109               | 3669724.8                           | 229,357.8                              | 230,400             | .452         |

| 217               | 1843318.0                           | 115,207.4                              | 115,200             | .006         |

| 651               | 614439.3                            | 38,402.5                               | 38,400              | .006         |

| 1302              | 307219.7                            | 19,201.2                               | 19,200              | .006         |

| 2604              | 153,609.8                           | 9600.6                                 | 9,600               | .006         |

| 5208              | 76,804.9                            | 4800.3                                 | 4,800               | .006         |

| 10417             | 38,398.8                            | 2399.9                                 | 2,400               | .003         |

| 20833             | 19,200.3                            | 1200.02                                | 1,200               | .00          |

| 41667             | 9599.9                              | 600.0                                  | 600                 | .00          |

| 65535             | 6103.6                              | 381.5                                  |                     |              |

Table 10-16. Baud Rates (Example: Bus Clock = 25 MHz)

<sup>1</sup> 16x faster then baud rate

<sup>2</sup> divide 1/16 form transmit baud generator

#### Serial Communication Interface (S12SCIV6)

The transmitting device can address messages to selected receivers by including addressing information in the initial frame or frames of each message.

The WAKE bit in SCI control register 1 (SCICR1) determines how the SCI is brought out of the standby state to process an incoming message. The WAKE bit enables either idle line wakeup or address mark wakeup.

### 10.4.6.6.1 Idle Input line Wakeup (WAKE = 0)

In this wakeup method, an idle condition on the RXD pin clears the RWU bit and wakes up the SCI. The initial frame or frames of every message contain addressing information. All receivers evaluate the addressing information, and receivers for which the message is addressed process the frames that follow. Any receiver for which a message is not addressed can set its RWU bit and return to the standby state. The RWU bit remains set and the receiver remains on standby until another idle character appears on the RXD pin.

Idle line wakeup requires that messages be separated by at least one idle character and that no message contains idle characters.

The idle character that wakes a receiver does not set the receiver idle bit, IDLE, or the receive data register full flag, RDRF.

The idle line type bit, ILT, determines whether the receiver begins counting logic 1s as idle character bits after the start bit or after the stop bit. ILT is in SCI control register 1 (SCICR1).

### 10.4.6.6.2 Address Mark Wakeup (WAKE = 1)

In this wakeup method, a logic 1 in the most significant bit (MSB) position of a frame clears the RWU bit and wakes up the SCI. The logic 1 in the MSB position marks a frame as an address frame that contains addressing information. All receivers evaluate the addressing information, and the receivers for which the message is addressed process the frames that follow. Any receiver for which a message is not addressed can set its RWU bit and return to the standby state. The RWU bit remains set and the receiver remains on standby until another address frame appears on the RXD pin.

The logic 1 MSB of an address frame clears the receiver's RWU bit before the stop bit is received and sets the RDRF flag.

Address mark wakeup allows messages to contain idle characters but requires that the MSB be reserved for use in address frames.

### NOTE

With the WAKE bit clear, setting the RWU bit after the RXD pin has been idle can cause the receiver to wake up immediately.

# **10.4.7** Single-Wire Operation

Normally, the SCI uses two pins for transmitting and receiving. In single-wire operation, the RXD pin is disconnected from the SCI. The SCI uses the TXD pin for both receiving and transmitting.

<sup>1</sup> The register is available only if corresponding channel exists.

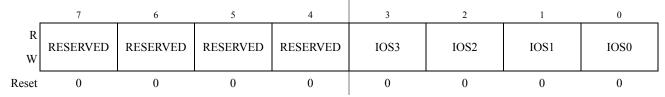

## 12.3.2.1 Timer Input Capture/Output Compare Select (TIOS)

Figure 12-4. Timer Input Capture/Output Compare Select (TIOS)

#### Read: Anytime

#### Write: Anytime

#### Table 12-2. TIOS Field Descriptions

Note: Writing to unavailable bits has no effect. Reading from unavailable bits return a zero.

| Fie        | eld | Description                                                                                                                                                                                                            |

|------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3:<br>IOS[ |     | Input Capture or Output Compare Channel Configuration         0       The corresponding implemented channel acts as an input capture.         1       The corresponding implemented channel acts as an output compare. |

## **12.3.2.2** Timer Compare Force Register (CFORC)

|       | 7        | 6        | 5        | 4        | 3    | 2    | 1    | 0    |

|-------|----------|----------|----------|----------|------|------|------|------|

| R     | 0        | 0        | 0        | 0        | 0    | 0    | 0    | 0    |

| W     | RESERVED | RESERVED | RESERVED | RESERVED | FOC3 | FOC2 | FOC1 | FOC0 |

| Reset | 0        | 0        | 0        | 0        | 0    | 0    | 0    | 0    |

#### Figure 12-5. Timer Compare Force Register (CFORC)

#### Read: Anytime but will always return 0x0000 (1 state is transient)

#### Write: Anytime

#### Table 12-3. CFORC Field Descriptions

Note: Writing to unavailable bits has no effect. Reading from unavailable bits return a zero.

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3:0<br>FOC[3:0] | <b>Note:</b> Force Output Compare Action for Channel 3:0 — A write to this register with the corresponding data bit(s) set causes the action which is programmed for output compare "x" to occur immediately. The action taken is the same as if a successful comparison had just taken place with the TCx register except the interrupt flag does not get set. If forced output compare on any channel occurs at the same time as the successful output compare then forced output compare then forced output compare then forced output compare action will take precedence and interrupt flag won't get set. |

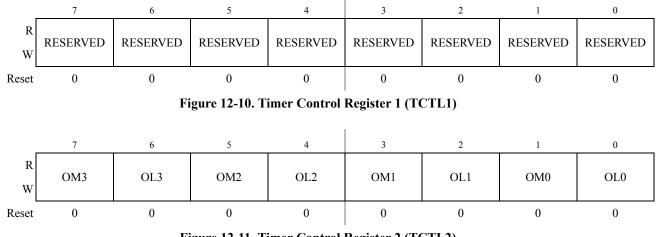

# 12.3.2.6 Timer Control Register 1/Timer Control Register 2 (TCTL1/TCTL2)

Figure 12-11. Timer Control Register 2 (TCTL2)

#### Read: Anytime

Write: Anytime

#### Table 12-6. TCTL1/TCTL2 Field Descriptions

Note: Writing to unavailable bits has no effect. Reading from unavailable bits return a zero

| Field      | Description                                                                                                                                                                                                                                                                                                                   |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3:0<br>OMx | <b>Output Mode</b> — These four pairs of control bits are encoded to specify the output action to be taken as a result of a successful OCx compare. When either OMx or OLx is 1, the pin associated with OCx becomes an output tied to OCx. <b>Note:</b> For an output line to be driven by an OCx the OCPDx must be cleared. |

| 3:0<br>OLx | <b>Output Level</b> — These fourpairs of control bits are encoded to specify the output action to be taken as a result of a successful OCx compare. When either OMx or OLx is 1, the pin associated with OCx becomes an output tied to OCx. <b>Note:</b> For an output line to be driven by an OCx the OCPDx must be cleared. |

#### Table 12-7. Compare Result Output Action

| OMx | OLx | Action                                                 |

|-----|-----|--------------------------------------------------------|

| 0   | 0   | No output compare<br>action on the timer output signal |

| 0   | 1   | Toggle OCx output line                                 |

| 1   | 0   | Clear OCx output line to zero                          |

| 1   | 1   | Set OCx output line to one                             |

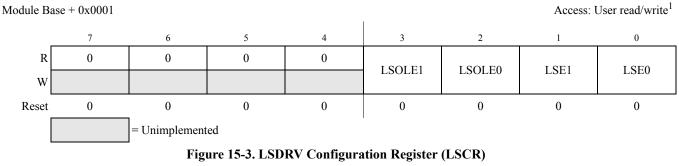

# **15.3.4 LSDRV Configuration Register (LSCR)**

<sup>1</sup> Read: Anytime Write: Anytime

#### Table 15-5. LSCR Register Field Descriptions

| Field         | Description                                                                                                                                                                                                                                                                                                                                                                                           |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 3-2<br>LSOLEx | <b>LSDRV High-Load Resistance Open-Load Detection Enable</b><br>These bits enable the measurement function to detect an open-load condition on the related low-side driver operating on<br>high-load resistance loads. If the low-side driver is enabled and is not being driven by the selected source, then the high-load<br>resistance detection circuit is activated when this bit is set to '1'. |  |

|               | <ul> <li>0 high-load resistance open-load detection is disabled</li> <li>1 high-load resistance open-load detection is enabled</li> </ul>                                                                                                                                                                                                                                                             |  |

| 1-0<br>LSEx   | LSDRV Enable<br>These bits control the bias of the related low-side driver circuit.                                                                                                                                                                                                                                                                                                                   |  |

|               | 0 Low-side driver is disabled.<br>1 Low-side driver is enabled.                                                                                                                                                                                                                                                                                                                                       |  |

|               | NOTE                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|               | After enabling the low-side driver (write "1" to LSEx) a settling time $t_{LS\_settling}$ is required before the low-side driver is allowed to be turned on (e.g. by writing LSDRx bits).                                                                                                                                                                                                             |  |

# Chapter 16 LIN Physical Layer (S12LINPHYV2)

| Rev. No.<br>(Item No.) | Date (Submitted<br>By) | Sections Affected | Substantial Change(s)                                                                                   |

|------------------------|------------------------|-------------------|---------------------------------------------------------------------------------------------------------|

| V02.11                 | 19 Sep 2013            | All               | <ul><li>Removed preliminary note.</li><li>Fixed grammar and spelling throughout the document.</li></ul> |

| V02.12                 | 20 Sep 2013            | Standby Mode      | - Clarified Standby mode behavior.                                                                      |

| V02.13                 | 8 Oct 2013             | All               | - More grammar, spelling, and formating fixes throughout the document.                                  |

Table 16-1. Revision History Table

# 16.1 Introduction

The LIN (Local Interconnect Network) bus pin provides a physical layer for single-wire communication in automotive applications. The LIN Physical Layer is designed to meet the LIN Physical Layer 2.2 specification from LIN consortium.

# 16.1.1 Features

The LIN Physical Layer module includes the following distinctive features:

- Compliant with LIN Physical Layer 2.2 specification.

- Compliant with the SAE J2602-2 LIN standard.

- Standby mode with glitch-filtered wake-up.

- Slew rate selection optimized for the baud rates: 10.4 kbit/s, 20 kbit/s and Fast Mode (up to 250 kbit/s).

- Switchable 34 k $\Omega$ /330 k $\Omega$  pullup resistors (in shutdown mode, 330 k $\Omega$  only)

- Current limitation for LIN Bus pin falling edge.

- Overcurrent protection.

- LIN TxD-dominant timeout feature monitoring the LPTxD signal.

- Automatic transmitter shutdown in case of an overcurrent or TxD-dominant timeout.

- Fulfills the OEM "Hardware Requirements for LIN (CAN and FlexRay) Interfaces in Automotive Applications" v1.3.

The LIN transmitter is a low-side MOSFET with current limitation and overcurrent transmitter shutdown. A selectable internal pullup resistor with a serial diode structure is integrated, so no external pullup components are required for the application in a slave node. To be used as a master node, an external

# Chapter 17 Supply Voltage Sensor - (BATSV2)

| Rev. No.<br>(Item No.) | Data        | Sections Affected    | Substantial Change(s)                                                                                 |

|------------------------|-------------|----------------------|-------------------------------------------------------------------------------------------------------|

| V01.00                 | 15 Dec 2010 | all                  | Initial Version                                                                                       |

| V02.00                 | 16 Mar 2011 | 17.3.2.1<br>17.4.2.1 | <ul> <li>added BVLS[1] to support four voltage level</li> <li>moved BVHS to register bit 6</li> </ul> |

#### Table 17-1. Revision History Table

# 17.1 Introduction

The BATS module provides the functionality to measure the voltage of the battery supply pin VSENSE or of the chip supply pin VSUP.

### 17.1.1 Features

Either One of the voltage present on the VSENSE or VSUP pin can be routed via an internal divider to the internal Analog to Digital Converter. Independent of the routing to the Analog to Digital Converter, it is possible to route one of these voltages to a comparator to generate a low or a high voltage interrupt to alert the MCU.

## 17.1.2 Modes of Operation

The BATS module behaves as follows in the system power modes:

1. Run mode

The activation of the VSENSE Level Sense Enable (BSESE=1) or ADC connection Enable (BSEAE=1) closes the path from the VSENSE pin through the resistor chain to ground and enables the associated features if selected.

The activation of the VSUP Level Sense Enable (BSUSE=1) or ADC connection Enable (BSUAE=1) closes the path from VSUP pin through the resistor chain to ground and enables the associated features if selected.

BSESE takes precedence over BSUSE. BSEAE takes precedence over BSUAE.

2. Stop mode

During stop mode operation the path from the VSENSE pin through the resistor chain to ground is opened and the low voltage sense features are disabled.

#### 64 KByte Flash Module (S12FTMRG64K512V1) for S12VR64

| CCOBIX[2:0] | FCCOB Parameters |              |  |

|-------------|------------------|--------------|--|

| 000         | 0x0C             | Not required |  |

| 001         | Ke               | y 0          |  |

| 010         | Ke               | y 1          |  |

| 011         | Ke               | y 2          |  |

| 100         | Key 3            |              |  |

Table 18-52. Verify Backdoor Access Key Command FCCOB Requirements

Upon clearing CCIF to launch the Verify Backdoor Access Key command, the Memory Controller will check the FSEC KEYEN bits to verify that this command is enabled. If not enabled, the Memory Controller sets the ACCERR bit in the FSTAT register and terminates. If the command is enabled, the Memory Controller compares the key provided in FCCOB to the backdoor comparison key in the Flash configuration field with Key 0 compared to 0x3\_FF00, etc. If the backdoor keys match, security will be released. If the backdoor keys do not match, security is not released and all future attempts to execute the Verify Backdoor Access Key command are aborted (set ACCERR) until a reset occurs. The CCIF flag is set after the Verify Backdoor Access Key operation has completed.

| Register | Error Bit | Error Condition                                                                                                         |

|----------|-----------|-------------------------------------------------------------------------------------------------------------------------|

| FSTAT    |           | Set if CCOBIX[2:0] != 100 at command launch                                                                             |

|          |           | Set if an incorrect backdoor key is supplied                                                                            |

|          | ACCERR    | Set if backdoor key access has not been enabled (KEYEN[1:0] != 10, see Section 18.3.2.2 Flash Security Register (FSEC)) |

|          |           | Set if the backdoor key has mismatched since the last reset                                                             |

|          | FPVIOL    | None                                                                                                                    |

| Ν        | MGSTAT1   | None                                                                                                                    |

|          | MGSTAT0   | None                                                                                                                    |

Table 18-53. Verify Backdoor Access Key Command Error Handling

### 18.4.6.12 Set User Margin Level Command

The Set User Margin Level command causes the Memory Controller to set the margin level for future read operations of the P-Flash or EEPROM block.

Table 18-54. Set User Margin Level Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters      |                                                   |

|-------------|-----------------------|---------------------------------------------------|

| 000         | 0x0D                  | Flash block selection code [1:0]. See Table 18-34 |

| 001         | Margin level setting. |                                                   |

Upon clearing CCIF to launch the Set User Margin Level command, the Memory Controller will set the user margin level for the targeted block and then set the CCIF flag.

### NOTE

When the EEPROM block is targeted, the EEPROM user margin levels are applied only to the EEPROM reads. However, when the P-Flash block is targeted, the P-Flash user margin levels are applied to both P-Flash and EEPROM reads. It is not possible to apply user margin levels to the P-Flash block only.

Valid margin level settings for the Set User Margin Level command are defined in Table 18-55.

| CCOB<br>(CCOBIX=001) | Level Description                |

|----------------------|----------------------------------|

| 0x0000               | Return to Normal Level           |

| 0x0001               | User Margin-1 Level <sup>1</sup> |

| 0x0002               | User Margin-0 Level <sup>2</sup> |

Table 18-55. Valid Set User Margin Level Settings

Read margin to the erased state

<sup>2</sup> Read margin to the programmed state

#### Table 18-56. Set User Margin Level Command Error Handling

| Register | Error Bit | Error Condition                                                              |

|----------|-----------|------------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] != 001 at command launch                                  |

|          |           | Set if command not available in current mode (see Table 18-27)               |

| FSTAT    |           | Set if an invalid FlashBlockSelectionCode[1:0] is supplied (See Table 18-34) |

|          |           | Set if an invalid margin level setting is supplied                           |

|          | FPVIOL    | None                                                                         |

|          | MGSTAT1   | None                                                                         |

|          | MGSTAT0   | None                                                                         |

#### NOTE

User margin levels can be used to check that Flash memory contents have adequate margin for normal level read operations. If unexpected results are encountered when checking Flash memory contents at user margin levels, a potential loss of information has been detected.

## 18.4.6.13 Set Field Margin Level Command

The Set Field Margin Level command, valid in special modes only, causes the Memory Controller to set the margin level specified for future read operations of the P-Flash or EEPROM block.

# 19.4.6.2 Erase Verify Block Command

The Erase Verify Block command allows the user to verify that an entire P-Flash or EEPROM block has been erased. The FCCOB FlashBlockSelectionCode[1:0]bits determine which block must be verified.

Table 19-33. Erase Verify Block Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters |                                                         |

|-------------|------------------|---------------------------------------------------------|

| 000         | 0x02             | Flash block<br>selection code [1:0]. See<br>Table 19-34 |

| Selection code[1:0] | Flash block to be verified |

|---------------------|----------------------------|

| 00                  | EEPROM                     |

| 01                  | Invalid (ACCERR)           |

| 10                  | Invalid (ACCERR)           |

| 11                  | P-Flash                    |

#### Table 19-34. Flash block selection code description

Upon clearing CCIF to launch the Erase Verify Block command, the Memory Controller will verify that the selected P-Flash or EEPROM block is erased. The CCIF flag will set after the Erase Verify Block operation has completed. If the block is not erased, it means blank check failed, both MGSTAT bits will be set.

Table 19-35. Erase Verify Block Command Error Handling

| Register | Error Bit | Error Condition                                                                                   |

|----------|-----------|---------------------------------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] != 000 at command launch                                                       |

| FSTAT    | ACCERK    | Set if an invalid FlashBlockSelectionCode[1:0] is supplied                                        |

|          | FPVIOL    | None                                                                                              |

|          | MGSTAT1   | Set if any errors have been encountered during the read or if blank check failed.                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the read or if blank check failed. |

# 19.4.6.3 Erase Verify P-Flash Section Command

The Erase Verify P-Flash Section command will verify that a section of code in the P-Flash memory is erased. The Erase Verify P-Flash Section command defines the starting point of the code to be verified and the number of phrases.

# A.1.2 Current Injection

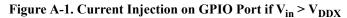

Power supply must maintain regulation within operating  $V_{DDX}$  or  $V_{DD}$  range during instantaneous and operating maximum current conditions. Figure A-1. shows a 5V GPIO pad driver and the on chip voltage regulator with VDDX output. It shows also the power & gound pins VSUP, VDDX, VSSX and VSSA. Px represents any 5V GPIO pin. Assume Px is configured as an input. The pad driver transistors P1 and N1 are switched off (high impedance). If the voltage  $V_{in}$  on Px is greated than  $V_{DDX}$  a positive injection current  $I_{in}$  will flow through diode D1 into VDDX node. If this injection current  $I_{in}$  is greater than  $I_{Load}$ , the internal power supply VDDX may go out of regulation. Ensure external  $V_{DDX}$  load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power; e.g., if no system clock is present, or if clock rate is very low which would reduce overall power consumption.

## A.1.3 Absolute Maximum Ratings

Absolute maximum ratings are stress ratings only. A functional operation under or outside those maxima is not guaranteed. Stress beyond those limits may affect the reliability or cause permanent damage of the device.

This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than

MC9812VR Family Reference Manual, Rev. 4.2

# Appendix I BATS Electrical Specifications

This section describe the electrical characteristics of the Supply Voltage Sense module.

# I.1 Maximum Ratings

#### Table I-1. Maximum ratings of the Supply Voltage Sense - (BATS).

Characteristics noted under conditions  $5.5V \le VSUP \le 18 V$ ,  $-40^{\circ}C \le T_J \le 150^{\circ}C^1$  unless otherwise noted. Typical values noted reflect the approximate parameter mean at  $T_A = 25^{\circ}C^2$  under nominal conditions unless otherwise noted.

| Num | Ratings           | Symbol                | Min | Тур | Max | Unit |

|-----|-------------------|-----------------------|-----|-----|-----|------|

| 1   | VSENSE Max Rating | V <sub>VSENSE_M</sub> | -27 | -   | 42  | V    |

<sup>1</sup> T<sub>J</sub>: Junction Temperature

<sup>2</sup>  $T_A$ : Ambient Temperature

# P.31 0x0240 -0x027F Port Integration Module<sup>1</sup> (PIM) Map 4 of 4

| Address  | Name      |             | Bit 7 | Bit 6 | Bit 5   | Bit 4   | Bit 3         | Bit 2         | Bit 1   | Bit 0   |

|----------|-----------|-------------|-------|-------|---------|---------|---------------|---------------|---------|---------|

| 0x0260-0 | Reserved  | R           | 0     | 0     | 0       | 0       | 0             | 0             | 0       | 0       |

| x0268    |           | W           | 0     | 0     | 0       | 0       | DTH 2         | DTH 0         | DTH 1   | DTH 0   |

| 0x0269   | PTIL      | R<br>W      | 0     | 0     | 0       | 0       | PTIL3         | PTIL2         | PTIL1   | PTIL0   |

| 0x026A   | DDRL      | R<br>W      | 0     | 0     | 0       | 0       | DDRL3         | DDRL2         | DDRL1   | DDRL0   |

| 0x026B   | PTAL      | R<br>W      | 0     | 0     | 0       | 0       | PTAENL        | 0             | PTAL1   | PTAL0   |

| 0x026C   | PIRL      | R<br>W      | 0     | 0     | 0       | 0       | PIRL3         | PIRL2         | PIRL1   | PIRL0   |

| 0x026D   | PPSL      | R<br>W      | 0     | 0     | 0       | 0       | PPSL3         | PPSL2         | PPSL1   | PPSL0   |

| 0x026E   | PIEL      | R<br>W      | 0     | 0     | 0       | 0       | PIEL3         | PIEL2         | PIEL1   | PIELO   |

| 0x026F   | PIFL      | R<br>W      | 0     | 0     | 0       | 0       | PIFL3         | PIFL2         | PIFL1   | PIFL0   |

| 0x0270   | Reserved  | R           | 0     | 0     | 0       | 0       | 0             | 0             | 0       | 0       |

| 0.0270   | Reserved  | W           |       |       |         |         |               |               |         |         |

| 0x0271   | PT1AD     | R<br>W      | 0     | 0     | PT1AD5  | PT1AD4  | <u>PT1AD3</u> | <u>PT1AD2</u> | PT1AD1  | PT1AD0  |

| 0x0272   | Reserved  | R<br>W      | 0     | 0     | 0       | 0       | 0             | 0             | 0       | 0       |

| 0x0273   | PTI1AD    | R<br>W      | 0     | 0     | PTI1AD5 | PTI1AD4 | PTI1AD3       | PTI1AD2       | PTI1AD1 | PTI1AD0 |

| 0x0274   | Reserved  | R<br>W      | 0     | 0     | 0       | 0       | 0             | 0             | 0       | 0       |

| 0x0275   | DDR1AD    | R<br>W      | 0     | 0     | DDR1AD5 | DDR1AD4 | DDR1AD3       | DDR1AD2       | DDR1AD1 | DDR1AD0 |

| 0x0276-0 | Reserved  | R           | 0     | 0     | 0       | 0       | 0             | 0             | 0       | 0       |

| x0278    | Reserved  | W           |       |       |         |         |               |               |         |         |

| 0x0279   | PER1AD    | R<br>W      | 0     | 0     | PER1AD5 | PER1AD4 | PER1AD3       | PER1AD2       | PER1AD1 | PER1AD0 |

| 0x027A   | Reserved  | R           | 0     | 0     | 0       | 0       | 0             | 0             | 0       | 0       |

| 01102711 | iteserveu | W           |       |       |         |         |               |               |         |         |

| 0x027B   | PPS1AD    | R<br>W      | 0     | 0     | PPS1AD5 | PPS1AD4 | PPS1AD3       | PPS1AD2       | PPS1AD1 | PPS1AD0 |

| 0x027C   | Reserved  | R<br>W      | 0     | 0     | 0       | 0       | 0             | 0             | 0       | 0       |

| 0x027D   | PIE1AD    | R<br>W      | 0     | 0     | PIE1AD5 | PIE1AD4 | PIE1AD3       | PIE1AD2       | PIE1AD1 | PIE1AD0 |

| 0x027E   | Reserved  | R           | 0     | 0     | 0       | 0       | 0             | 0             | 0       | 0       |

| 0x027F   | PIF1AD    | W<br>R<br>W | 0     | 0     | PIF1AD5 | PIF1AD4 | PIF1AD3       | PIF1AD2       | PIF1AD1 | PIF1AD0 |

Register and register bits in <u>bold underlined</u> are only available on S12VR64/48. On S12VR32/16 these locations read 0 and write is not implemented.