Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | RL78                                                                            |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 24MHz                                                                           |

| Connectivity               | CSI, I <sup>2</sup> C, UART/USART                                               |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                         |

| Number of I/O              | 18                                                                              |

| Program Memory Size        | 8KB (8K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | 2K x 8                                                                          |

| RAM Size                   | 768 x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                     |

| Data Converters            | A/D 11x8/10b                                                                    |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 24-WFQFN Exposed Pad                                                            |

| Supplier Device Package    | 24-HWQFN (4x4)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f10278ana-u5 |

RL78/G12 1. OUTLINE

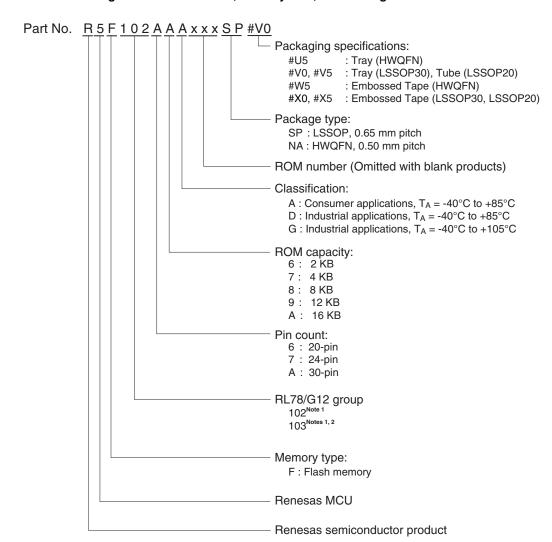

#### 1.2 List of Part Numbers

<R>

Figure 1-1. Part Number, Memory Size, and Package of RL78/G12

- Notes 1. For details about the differences between the R5F102 products and the R5F103 products of RL78/G12, see 1.1 Differences between the R5F102 Products and the R5F103 Products.

- 2. Products only for "A: Consumer applications ( $T_A = -40 \text{ to } +85^{\circ}\text{C}$ )" and "D: Industrial applications ( $T_A = -40 \text{ to } +85^{\circ}\text{C}$ )"

RL78/G12 1. OUTLINE

#### 1.3 Differences between the R5F102 Products and the R5F103 Products

The following are differences between the R5F102 products and the R5F103 products.

- O Whether the data flash memory is mounted or not

- O High-speed on-chip oscillator oscillation frequency accuracy

- O Number of channels in serial interface

- O Whether the DMA function is mounted or not

- O Whether a part of the safety functions are mounted or not

#### 1.3.1 Data Flash

The data flash memory of 2 KB is mounted on the R5F102 products, but not on the R5F103 products.

| Product                       | Data Flash  |

|-------------------------------|-------------|

| R5F102 products               | 2KB         |

| R5F1026A, R5F1027A, R5F102AA, |             |

| R5F10269, R5F10279, R5F102A9, |             |

| R5F10268, R5F10278, R5F102A8, |             |

| R5F10267, R5F10277, R5F102A7, |             |

| R5F10266 Note                 |             |

| R5F103 products               | Not mounted |

| R5F1036A, R5F1037A, R5F103AA, |             |

| R5F10369, R5F10379, R5F103A9, |             |

| R5F10368, R5F10378 R5F103A8,  |             |

| R5F10367, R5F10377, R5F103A7, |             |

| R5F10366                      |             |

**Note** The RAM in the R5F10266 has capacity as small as 256 bytes. Depending on the customer's program specification, the stack area to execute the data flash library may not be kept and data may not be written to or erased from the data flash memory.

**Caution** When the flash memory is rewritten via a user program, the code flash area and RAM area are used because each library is used. When using the library, refer to RL78 Family Flash Self Programming Library Type01 User's Manual and RL78 Family Data Flash Library Type04 User's Manual.

## 2.1 Absolute Maximum Ratings

Absolute Maximum Ratings (T<sub>A</sub> = 25°C)

| Parameter                                    | Symbols          |                    | Conditions                                                                                                                                         | Ratings                                                                | Unit |

|----------------------------------------------|------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|------|

| Supply Voltage                               | V <sub>DD</sub>  |                    |                                                                                                                                                    | -0.5 to + 6.5                                                          | V    |

| REGC terminal input voltage <sup>Note1</sup> | VIREGC           | REGC               |                                                                                                                                                    | -0.3 to +2.8<br>and -0.3 to V <sub>DD</sub> + 0.3<br><sub>Note 2</sub> | V    |

| Input Voltage                                | VII              | Other than P60, F  | P61                                                                                                                                                | -0.3 to V <sub>DD</sub> + 0.3 <sup>Note 3</sup>                        | V    |

|                                              | Vı2              | P60, P61 (N-ch o   | pen drain)                                                                                                                                         | -0.3 to 6.5                                                            | V    |

| Output Voltage                               | Vo               |                    |                                                                                                                                                    | -0.3 to V <sub>DD</sub> + 0.3 <sup>Note 3</sup>                        | V    |

| Analog input voltage                         | Val              | 20-, 24-pin produc | cts: ANI0 to ANI3, ANI16 to ANI22                                                                                                                  | -0.3 to V <sub>DD</sub> + 0.3                                          | V    |

|                                              |                  | 30-pin products: A | ANIO to ANI3, ANI16 to ANI19                                                                                                                       | and -0.3 to<br>AVREF(+)+0.3 Notes 3, 4                                 |      |

| Output current, high                         | <b>І</b> он1     | Per pin            | Other than P20 to P23                                                                                                                              | -40                                                                    | mA   |

|                                              |                  | Total of all pins  | All the terminals other than P20 to P23                                                                                                            | -170                                                                   | mA   |

|                                              |                  |                    | 20-, 24-pin products: P40 to P42                                                                                                                   | -70                                                                    | mA   |

|                                              |                  |                    | 30-pin products: P00, P01, P40, P120                                                                                                               |                                                                        |      |

|                                              |                  |                    | 20-, 24-pin products: P00 to P03 <sup>Note 5</sup> ,<br>P10 to P14<br>30-pin products: P10 to P17, P30, P31,<br>P50, P51, P147                     | -100                                                                   | mA   |

|                                              | <b>І</b> он2     | Per pin            | P20 to P23                                                                                                                                         | -0.5                                                                   | mA   |

|                                              |                  | Total of all pins  |                                                                                                                                                    | -2                                                                     | mA   |

| Output current, low                          | lo <sub>L1</sub> | Per pin            | Other than P20 to P23                                                                                                                              | 40                                                                     | mA   |

|                                              |                  | Total of all pins  | All the terminals other than P20 to P23                                                                                                            | 170                                                                    | mA   |

|                                              |                  |                    | 20-, 24-pin products: P40 to P42<br>30-pin products: P00, P01, P40, P120                                                                           | 70                                                                     | mA   |

|                                              |                  |                    | 20-, 24-pin products: P00 to P03 <sup>Note 5</sup> ,<br>P10 to P14, P60, P61<br>30-pin products: P10 to P17, P30, P31,<br>P50, P51, P60, P61, P147 | 100                                                                    | mA   |

|                                              | lo <sub>L2</sub> | Per pin            | P20 to P23                                                                                                                                         | 1                                                                      | mA   |

|                                              |                  | Total of all pins  |                                                                                                                                                    | 5                                                                      | mA   |

| Operating ambient temperature                | Та               |                    |                                                                                                                                                    | -40 to +85                                                             | °C   |

| Storage temperature                          | T <sub>stg</sub> |                    |                                                                                                                                                    | -65 to +150                                                            | °C   |

Notes 1. 30-pin product only.

- 2. Connect the REGC pin to  $V_{SS}$  via a capacitor (0.47 to 1  $\mu$ F). This value determines the absolute maximum rating of the REGC pin. Do not use it with voltage applied.

- 3. Must be 6.5 V or lower.

- 4. Do not exceed AVREF(+) + 0.3 V in case of A/D conversion target pin.

- 5. 24-pin products only.

Caution Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameter. That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions that ensure that the absolute maximum ratings are not exceeded.

Remarks 1. Unless specified otherwise, the characteristics of alternate-function pins are the same as those of the port

- **2.** AVREF(+): + side reference voltage of the A/D converter.

- 3. Vss: Reference voltage

$(TA = -40 \text{ to } +85^{\circ}C, 1.8 \text{ V} \le VDD \le 5.5 \text{ V}, Vss = 0 \text{ V})$

(3/4)

| (                    |                  |                                                                     |                                                                                   |                      |                 |                    |          |

|----------------------|------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------|----------------------|-----------------|--------------------|----------|

| Parameter            | Symbol           | Condition                                                           | s                                                                                 | MIN.                 | TYP.            | MAX.               | Unit     |

| Input voltage, high  | V <sub>IH1</sub> | Normal input buffer                                                 |                                                                                   | 0.8V <sub>DD</sub>   |                 | V <sub>DD</sub>    | ٧        |

|                      |                  | 20-, 24-pin products: P00 to P0<br>P40 to P42                       |                                                                                   |                      |                 |                    |          |

|                      |                  | 30-pin products: P00, P01, P1<br>P40, P50, P51, P120, P147          | 0 to P17, P30, P31,                                                               |                      |                 |                    |          |

|                      | V <sub>IH2</sub> | TTL input buffer                                                    | $4.0~V \leq V_{DD} \leq 5.5~V$                                                    | 2.2                  |                 | V <sub>DD</sub>    | ٧        |

|                      |                  | 20-, 24-pin products: P10, P11                                      | $3.3~V \leq V_{DD} < 4.0~V$                                                       | 2.0                  |                 | V <sub>DD</sub>    | ٧        |

|                      |                  | 30-pin products: P01, P10,<br>P11, P13 to P17                       | 1.8 V ≤ V <sub>DD</sub> < 3.3 V                                                   | 1.5                  |                 | V <sub>DD</sub>    | <b>V</b> |

|                      | VIH3             | P20 to P23                                                          | P20 to P23                                                                        |                      |                 | V <sub>DD</sub>    | ٧        |

|                      | V <sub>IH4</sub> | P60, P61                                                            | 0.7V <sub>DD</sub>                                                                |                      | 6.0             | ٧                  |          |

|                      | V <sub>IH5</sub> | P121, P122, P125 <sup>Note 1</sup> , P137, I                        | 0.8V <sub>DD</sub>                                                                |                      | V <sub>DD</sub> | ٧                  |          |

| Input voltage, low   | VIL1             | Normal input buffer                                                 |                                                                                   | 0                    |                 | 0.2V <sub>DD</sub> | ٧        |

|                      |                  | 20-, 24-pin products: P00 to P0<br>P40 to P42                       |                                                                                   |                      |                 |                    |          |

|                      |                  | 30-pin products: P00, P01, P10<br>P40, P50, P51, P120, P147         | to P17, P30, P31,                                                                 |                      |                 |                    |          |

|                      | V <sub>IL2</sub> | TTL input buffer                                                    | $4.0~V \leq V_{DD} \leq 5.5~V$                                                    | 0                    |                 | 0.8                | >        |

|                      |                  | 20-, 24-pin products: P10, P11                                      | $3.3~V \leq V_{DD} < 4.0~V$                                                       | 0                    |                 | 0.5                | ٧        |

|                      |                  | 30-pin products: P01, P10,<br>P11, P13 to P17                       | $1.8~V \le V_{DD} < 3.3~V$                                                        | 0                    |                 | 0.32               | V        |

|                      | V <sub>IL3</sub> | P20 to P23                                                          |                                                                                   | 0                    |                 | 0.3V <sub>DD</sub> | ٧        |

|                      | V <sub>IL4</sub> | P60, P61                                                            |                                                                                   | 0                    |                 | 0.3V <sub>DD</sub> | ٧        |

|                      | V <sub>IL5</sub> | P121, P122, P125 <sup>Note 1</sup> , P137, I                        | EXCLK, RESET                                                                      | 0                    |                 | 0.2V <sub>DD</sub> | ٧        |

| Output voltage, high | V <sub>OH1</sub> | 20-, 24-pin products:<br>P00 to P03 <sup>Note 2</sup> , P10 to P14, | $4.0 \text{ V} \le \text{V}_{DD} \le 5.5 \text{ V},$ $I_{OH1} = -10.0 \text{ mA}$ | V <sub>DD</sub> -1.5 |                 |                    | V        |

|                      |                  | P40 to P42<br>30-pin products:                                      | $4.0 \text{ V} \le \text{V}_{DD} \le 5.5 \text{ V},$ $I_{OH1} = -3.0 \text{ mA}$  | V <sub>DD</sub> -0.7 |                 |                    | V        |

|                      |                  | P00, P01, P10 to P17, P30, P31, P40, P50, P51, P120,                | $2.7~V \leq V_{DD} \leq 5.5~V,$ $I_{OH1} = -2.0~mA$                               | V <sub>DD</sub> -0.6 |                 |                    | V        |

|                      |                  | P147                                                                | $1.8 \text{ V} \le \text{V}_{DD} \le 5.5 \text{ V},$ $I_{OH1} = -1.5 \text{ mA}$  | V <sub>DD</sub> -0.5 |                 |                    | V        |

|                      | V <sub>OH2</sub> | P20 to P23                                                          | Iон₂ = −100 μA                                                                    | V <sub>DD</sub> -0.5 |                 |                    | V        |

Notes 1. 20, 24-pin products only.

2. 24-pin products only.

Caution The maximum value of V<sub>IH</sub> of pins P10 to P12 and P41 for 20-pin products, P01, P10 to P12, and P41 for 24-pin products, and P00, P10 to P15, P17, and P50 for 30-pin products is V<sub>DD</sub> even in N-ch open-drain mode. High level is not output in the N-ch open-drain mode.

**Remark** Unless specified otherwise, the characteristics of alternate-function pins are the same as those of the port pins.

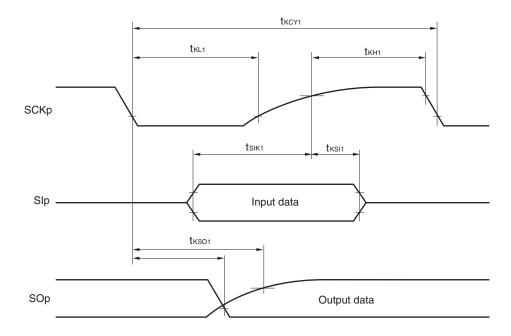

# (2) During communication at same potential (CSI mode) (master mode, SCK00... internal clock output, corresponding CSI00 only)

$(T_A = -40 \text{ to } +85^{\circ}\text{C}, 2.7 \text{ V} \le V_{DD} \le 5.5 \text{ V}, \text{Vss} = 0 \text{ V})$

| Parameter                                          | Symbol                         | Conditions                     | HS (high-spo | ,          | LS (low-sp | Unit |    |

|----------------------------------------------------|--------------------------------|--------------------------------|--------------|------------|------------|------|----|

|                                                    |                                |                                | MIN.         | MAX.       | MIN.       | MAX. |    |

| SCK00 cycle time                                   | tkCY1                          | tkcy1 ≥ 2/fclk                 | 83.3         |            | 250        |      | ns |

| SCK00 high-/low-tkH1, level width tkL1             | $4.0~V \leq V_{DD} \leq 5.5~V$ | tkcy1/2-7                      |              | tkcy1/2-50 |            | ns   |    |

|                                                    | t <sub>KL1</sub>               | $2.7~V \leq V_{DD} \leq 5.5~V$ | tkcy1/2-10   |            | tkcy1/2-50 |      | ns |

| SI00 setup time                                    | tsıĸı                          | $4.0~V \leq V_{DD} \leq 5.5~V$ | 23           |            | 110        |      | ns |

| (to SCK00↑) Note 1                                 |                                | $2.7~V \leq V_{DD} \leq 5.5~V$ | 33           |            | 110        |      | ns |

| SI00 hold time<br>(from SCK00↑) Note2              | tksi1                          |                                | 10           |            | 10         |      | ns |

| Delay time from<br>SCK00↓ to SO00<br>output Note 3 | tkso1                          | C = 20 pF Note 4               |              | 10         |            | 10   | ns |

- **Notes 1.** When DAP00 = 0 and CKP00 = 0, or DAP00 = 1 and CKP00 = 1. The SI00 setup time becomes "to  $SCK00\downarrow$ " when DAP00 = 0 and CKP00 = 1, or DAP00 = 1 and CKP00 = 0.

- 2. When DAP00 = 0 and CKP00 = 0, or DAP00 = 1 and CKP00 = 1. The SI00 hold time becomes "from SCK00 $\downarrow$ " when DAP00 = 0 and CKP00 = 1, or DAP00 = 1 and CKP00 = 0.

- 3. When DAP00 = 0 and CKP00 = 0, or DAP00 = 1 and CKP00 = 1. The delay time to SO00 output becomes "from SCK00 $\uparrow$ " when DAP00 = 0 and CKP00 = 1, or DAP00 = 1 and CKP00 = 0.

- 4. C is the load capacitance of the SCK00 and SO00 output lines.

**Caution** Select the normal input buffer for the SI00 pin and the normal output mode for the SO00 and SCK00 pins by using port input mode register 1 (PIM1) and port output mode register 1 (POM1).

Remarks 1. This specification is valid only when CSI00's peripheral I/O redirect function is not used.

fmck: Serial array unit operation clock frequency (Operation clock to be set by the serial clock select register 0 (SPS0) and the CKS00 bit of serial mode register 00 (SMR00).)

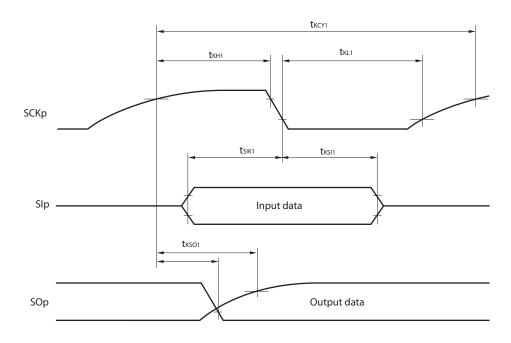

# (3) During communication at same potential (CSI mode) (master mode, SCKp... internal clock output) ( $T_A = -40$ to +85°C, 1.8 V $\leq$ V<sub>DD</sub> $\leq$ 5.5 V, Vss = 0 V)

| Parameter                                  | Symbol           | Conditions                            |                                 | HS (high-<br>main) N |      | LS (low-spe | -    | Unit |

|--------------------------------------------|------------------|---------------------------------------|---------------------------------|----------------------|------|-------------|------|------|

|                                            |                  |                                       |                                 | MIN.                 | MAX. | MIN.        | MAX. |      |

| SCKp cycle time                            | tkcy1            | tkcy1 ≥ 4/fcLk                        | $2.7~V \leq V_{DD} \leq 5.5~V$  | 167                  |      | 500         |      | ns   |

|                                            |                  |                                       | $2.4~V \leq V_{DD} \leq 5.5~V$  | 250                  |      | 500         |      | ns   |

|                                            |                  |                                       | $1.8~V \leq V_{DD} \leq 5.5~V$  | -                    |      | 500         |      | ns   |

| SCKp high-/low-level width                 | tкн1,            | $4.0~V \leq V_{DD} \leq$              | 4.0 V ≤ V <sub>DD</sub> ≤ 5.5 V |                      |      | tkcy1/2-50  |      | ns   |

|                                            | t <sub>KL1</sub> | $2.7~V \leq V_{\text{DD}} \leq 5.5~V$ |                                 | tkcy1/2-18           |      | tkcy1/2-50  |      | ns   |

|                                            |                  | $2.4~V \leq V_{DD} \leq$              | 5.5 V                           | tkcy1/2-38           |      | tkcy1/2-50  |      | ns   |

|                                            |                  | 1.8 V ≤ V <sub>DD</sub> ≤             | 5.5 V                           | -                    |      | tkcy1/2-50  |      | ns   |

| SIp setup time (to SCKp↑)                  | tsıĸı            | $4.0~V \leq V_{DD} \leq$              | 5.5 V                           | 44                   |      | 110         |      | ns   |

| Note 1                                     |                  | $2.7 \text{ V} \leq V_{DD} \leq 8$    | $2.7~V \leq V_{DD} \leq 5.5~V$  |                      |      | 110         |      | ns   |

|                                            |                  | $2.4~V \leq V_{DD} \leq$              | 5.5 V                           | 75                   |      | 110         |      | ns   |

|                                            |                  | $1.8~V \leq V_{DD} \leq$              | 5.5 V                           | -                    |      | 110         |      | ns   |

| SIp hold time<br>(from SCKp↑) Note 2       | tksıı            |                                       |                                 | 19                   |      | 19          |      | ns   |

| Delay time from SCKp↓ to SOp output Note 3 | tkso1            | C = 30 pF Note4                       |                                 |                      | 25   |             | 25   | ns   |

- Notes 1. When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The SIp setup time becomes "to SCKp↓" when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

- 2. When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The SIp hold time becomes "from SCKp↓" when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

- **3.** When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The delay time to SOp output becomes "from SCKp $\uparrow$ " when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

- 4. C is the load capacitance of the SCKp and SOp output lines.

**Caution** Select the normal input buffer for the SIp pin and the normal output mode for the SOp and SCKp pins by using port input mode register 1 (PIM1) and port output mode registers 0, 1, 4 (POM0, POM1, POM4).

- **Remarks 1.** p: CSI number (p = 00, 01, 11, 20), m: Unit number (m = 0, 1), n: Channel number (n = 0, 1, 3: "1, 3" is only for the R5F102 products)

- 2. fmck: Serial array unit operation clock frequency

(Operation clock to be set by the serial clock select register m (SPSm) and the CKSmn bit of serial mode register mn (SMRmn). m: Unit number (m = 0, 1), n: Channel number (n = 0, 1, 3: "1, 3" is only for the R5F102 products.))

- This value as an example is calculated when the conditions described in the "Conditions" column are met.

Refer to Note 4 above to calculate the maximum transfer rate under conditions of the customer.

- **6.** The smaller maximum transfer rate derived by using fmck/6 or the following expression is the valid maximum transfer rate.

Expression for calculating the transfer rate when 2.7 V  $\leq$  VDD < 4.0 V and 2.3 V  $\leq$  Vb  $\leq$  2.7 V

Maximum transfer rate =

$$\frac{1}{\{-C_b \times R_b \times \ln (1 - \frac{2.0}{V_b})\} \times 3}$$

[bps]

$$\text{Baud rate error (theoretical value)} = \frac{\frac{1}{\text{Transfer rate} \times 2} - \{-C_b \times R_b \times \ln (1 - \frac{2.0}{V_b})\}}{\frac{1}{(\text{Transfer rate})} \times \text{Number of transferred bits}} \times 100 \, [\%]$$

- \* This value is the theoretical value of the relative difference between the transmission and reception sides.

- **7.** This value as an example is calculated when the conditions described in the "Conditions" column are met. Refer to **Note 6** above to calculate the maximum transfer rate under conditions of the customer.

- 8. The smaller maximum transfer rate derived by using fmck/6 or the following expression is the valid maximum transfer rate.

Expression for calculating the transfer rate when 1.8 V  $\leq$  V<sub>DD</sub> < 3.3 V, 1.6 V  $\leq$  V<sub>b</sub>  $\leq$  2.0 V

$$\label{eq:maximum transfer rate} \text{Maximum transfer rate} = \frac{1}{\{-C_b \times R_b \times \text{In } (1-\frac{1.5}{V_b})\} \times 3} \quad \text{[bps]}$$

Baud rate error (theoretical value) =

$$\frac{\frac{1}{\text{Transfer rate} \times 2} - \{-C_b \times R_b \times \ln(1 - \frac{1.5}{V_b})\}}{\frac{1}{(\text{Transfer rate}) \times \text{Number of transferred bits}}} \times 100 \, [\%]$$

- \* This value is the theoretical value of the relative difference between the transmission and reception sides.

- **9.** This value as an example is calculated when the conditions described in the "Conditions" column are met. Refer to **Note 8** above to calculate the maximum transfer rate under conditions of the customer.

Caution Select the TTL input buffer for the RxDq pin and the N-ch open drain output (VDD tolerance) mode for the TxDq pin by using port input mode register g (PIMg) and port output mode register g (POMg). For VIH and VIL, see the DC characteristics with TTL input buffer selected.

- Notes 1. When DAP00 = 0 and CKP00 = 0, or DAP00 = 1 and CKP00 = 1

- **2.** When DAP00 = 0 and CKP00 = 1, or DAP00 = 1 and CKP00 = 0.

- Caution Select the TTL input buffer for the SI00 pin and the N-ch open drain output (VDD tolerance) mode for the SO00 pin and SCK00 pin by using port input mode register 1 (PIM1) and port output mode register 1 (POM1).

For VIH and VIL, see the DC characteristics with TTL input buffer selected.

- **Remarks 1.** Rb [ $\Omega$ ]:Communication line (SCK00, SO00) pull-up resistance, Cb [F]: Communication line (SCK00, SO00) load capacitance, Vb [V]: Communication line voltage

- fmck: Serial array unit operation clock frequency (Operation clock to be set by the serial clock select register 0 (SPS0) and the CKS00 bit of serial mode register 00 (SMR00).)

# (8) Communication at different potential (1.8 V, 2.5 V, 3 V) (CSI mode) (master mode, SCKp... internal clock output) (3/3)

$(T_A = -40 \text{ to } +85^{\circ}\text{C}, 1.8 \text{ V} \le V_{DD} \le 5.5 \text{ V}, \text{Vss} = 0 \text{ V})$

| Parameter                            | Symbol | Conditions                                                                                                                                                        | HS (high-speed main) Mode |      | ,    | /-speed<br>Mode | Unit |

|--------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------|------|-----------------|------|

|                                      |        |                                                                                                                                                                   | MIN.                      | MAX. | MIN. | MAX.            |      |

| SIp setup time<br>(to SCKp↓) Note 1  | tsıĸı  | $ 4.0 \ V \leq V_{DD} \leq 5.5 \ V, \ 2.7 \ V \leq V_b \leq 4.0 \ V, $ $ C_b = 30 \ pF, \ R_b = 1.4 \ k\Omega $                                                   | 44                        |      | 110  |                 | ns   |

|                                      |        | $ 2.7 \; V \leq V_{DD} < 4.0 \; V,  2.3 \; V \leq V_b \leq 2.7 \; V, \\ C_b = 30 \; pF, \; R_b = 2.7 \; k\Omega $                                                 | 44                        |      | 110  |                 | ns   |

|                                      |        | $ \begin{aligned} &1.8 \ V \leq V_{DD} < 3.3 \ V, \ 1.6 \ V \leq V_{b} \leq 2.0 \ V^{\text{Note 2}}, \\ &C_{b} = 30 \ pF, \ R_{b} = 5.5 \ k\Omega \end{aligned} $ | 110                       |      | 110  |                 | ns   |

| SIp hold time<br>(from SCKp↓) Note 1 | tksii  | $ 4.0 \ V \leq V_{DD} \leq 5.5 \ V, \ 2.7 \ V \leq V_b \leq 4.0 \ V, $ $ C_b = 30 \ pF, \ R_b = 1.4 \ k\Omega $                                                   | 19                        |      | 19   |                 | ns   |

|                                      |        | $ 2.7 \; V \leq V_{DD} < 4.0 \; V,  2.3 \; V \leq V_b \leq 2.7 \; V, \\ C_b = 30 \; pF, \; R_b = 2.7 \; k\Omega $                                                 | 19                        |      | 19   |                 | ns   |

|                                      |        | $\begin{split} 1.8 \ V & \leq V_{DD} < 3.3 \ V, \ 1.6 \ V \leq V_b \leq 2.0 \ V^{\text{Note 2}}, \\ C_b & = 30 \ pF, \ R_b = 5.5 \ k\Omega \end{split}$           | 19                        |      | 19   |                 | ns   |

| Delay time from SCKp↑ to             | tkso1  | $ 4.0 \ V \leq V_{DD} \leq 5.5 \ V, \ 2.7 \ V \leq V_b \leq 4.0 \ V, $ $ C_b = 30 \ pF, \ R_b = 1.4 \ k\Omega $                                                   |                           | 25   |      | 25              | ns   |

| SOp output Note 1                    |        | $ 2.7 \; V \leq V_{DD} < 4.0 \; V,  2.3 \; V \leq V_b \leq 2.7 \; V, \\ C_b = 30 \; pF, \; R_b = 2.7 \; k\Omega $                                                 |                           | 25   |      | 25              | ns   |

|                                      |        | $\begin{split} 1.8 \ V & \leq V_{DD} < 3.3 \ V, \ 1.6 \ V \leq V_b \leq 2.0 \ V^{\text{Note 2}}, \\ C_b & = 30 \ pF, \ R_b = 5.5 \ k\Omega \end{split}$           |                           | 25   |      | 25              | ns   |

- **Notes 1.** When DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

- 2. Use it with  $V_{DD} \ge V_b$ .

- Cautions 1. Select the TTL input buffer for the SIp pin and the N-ch open drain output (VDD tolerance) mode for the SOp pin and SCKp pin by using port input mode register 1 (PIM1) and port output mode register 1 (POM1). For VIH and VIL, see the DC characteristics with TTL input buffer selected.

- 2. CSI01 and CSI11 cannot communicate at different potential.

- **Remarks 1.** R<sub>b</sub> [ $\Omega$ ]: Communication line (SCKp, SOp) pull-up resistance, C<sub>b</sub> [F]: Communication line (SCKp, SOp) load capacitance, V<sub>b</sub> [V]: Communication line voltage

- 2. p: CSI number (p = 00, 20), m: Unit number (m = 0, 1), n: Channel number (n = 0)

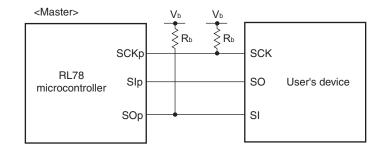

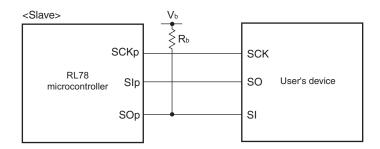

#### CSI mode connection diagram (during communication at different potential)

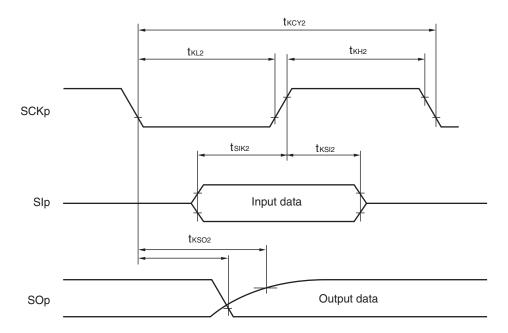

(9) Communication at different potential (1.8 V, 2.5 V, 3 V) (CSI mode) (slave mode, SCKp... external clock input)

$(T_A = -40 \text{ to } +85^{\circ}\text{C}, 1.8 \text{ V} \le V_{DD} \le 5.5 \text{ V}, \text{ Vss} = 0 \text{ V})$

| Parameter                                         | Symbol             | Co                                                 | onditions                                                  | HS (high-spe |          | LS (low-spe  | Unit     |    |

|---------------------------------------------------|--------------------|----------------------------------------------------|------------------------------------------------------------|--------------|----------|--------------|----------|----|

|                                                   |                    |                                                    |                                                            | MIN.         | MAX.     | MIN.         | MAX.     |    |

| SCKp cycle time Note 1                            | tkcy2              | $4.0~V \leq V_{DD} \leq 5.5~V,$                    | 20 MHz < fмcк ≤ 24 MHz                                     | 12/fмск      |          | -            |          | ns |

|                                                   |                    | $2.7~V \leq V_b \leq 4.0~V$                        | 8 MHz < fмcк ≤ 20 MHz                                      | 10/fмск      |          | =            |          | ns |

|                                                   |                    |                                                    | 4 MHz < fмcк ≤ 8 MHz                                       | 8/fмск       |          | 16/fмск      |          | ns |

|                                                   |                    |                                                    | fмcк ≤ 4 MHz                                               | 6/fмск       |          | 10/fмск      |          | ns |

|                                                   |                    | $2.7 \text{ V} \le \text{V}_{DD} < 4.0 \text{ V},$ | 20 MHz < fмcк ≤ 24 MHz                                     | 16/fмск      |          | _            |          | ns |

|                                                   |                    | $2.3~V \leq V_b \leq 2.7~V$                        | 16 MHz < fмcк ≤ 20 MHz                                     | 14/fмск      |          | =            |          | ns |

|                                                   |                    |                                                    | 8 MHz < fмск ≤ 16 MHz                                      | 12/fмск      |          | _            |          | ns |

|                                                   |                    |                                                    | 4 MHz < fмcк ≤ 8 MHz                                       | 8/fмск       |          | 16/fмск      |          | ns |

|                                                   |                    |                                                    | fмcк ≤ 4 MHz                                               | 6/fмск       |          | 10/fмск      |          | ns |

|                                                   |                    | $1.8 \text{ V} \le \text{V}_{DD} < 3.3 \text{ V},$ | 20 MHz < fмcк ≤ 24 MHz                                     | 36/fмск      |          | _            |          | ns |

|                                                   |                    | $1.6~V \leq V_b \leq 2.0~V$                        | 16 MHz < fмcк ≤ 20 MHz                                     | 32/fмск      |          | =            |          | ns |

|                                                   |                    | Note 2                                             | 8 MHz < fмск ≤ 16 MHz                                      | 26/fмск      |          | _            |          | ns |

|                                                   |                    |                                                    | 4 MHz < fмcк ≤ 8 MHz                                       | 16/fмск      |          | 16/fмск      |          | ns |

|                                                   |                    |                                                    | fмcк ≤ 4 MHz                                               | 10/fмск      |          | 10/fмск      |          | ns |

| SCKp high-/low-level                              | t <sub>KH2</sub> , | $4.0~V \leq V_{DD} \leq 5.5~V,$                    | $2.7~V \leq V_b \leq 4.0~V$                                | tkcy2/2 - 12 |          | tkcy2/2 - 50 |          | ns |

| width                                             | t <sub>KL2</sub>   | $2.7 \text{ V} \le \text{V}_{DD} < 4.0 \text{ V},$ | $2.3~V \leq V_b \leq 2.7~V$                                | tkcy2/2 - 18 |          | tkcy2/2 - 50 |          | ns |

|                                                   |                    | $1.8 \text{ V} \le \text{V}_{DD} < 3.3 \text{ V},$ | $1.6~V \leq V_b \leq 2.0~V^{\text{Note 2}}$                | tkcy2/2 - 50 |          | tkcy2/2 - 50 |          | ns |

| SIp setup time                                    | tsik2              | $4.0~V \leq V_{DD} \leq 5.5~V,$                    | $2.7~V \leq V_{DD} \leq 4.0~V$                             | 1/fmck + 20  |          | 1/fмск + 30  |          | ns |

| (to SCKp↑) Note 3                                 |                    | $2.7 \text{ V} \le \text{V}_{DD} < 4.0 \text{ V},$ | $2.3~V \leq V_b \leq 2.7~V$                                | 1/fmck + 20  |          | 1/fмск + 30  |          | ns |

|                                                   |                    | $1.8 \text{ V} \le \text{V}_{DD} < 3.3 \text{ V},$ | $1.6~V \leq V_{DD} \leq 2.0~V^{Note~2}$                    | 1/fmck + 30  |          | 1/fмск + 30  |          | ns |

| SIp hold time<br>(from SCKp <sup>↑</sup> ) Note 4 | tksi2              |                                                    |                                                            | 1/fмск + 31  |          | 1/fмск + 31  |          | ns |

| Delay time from                                   | tkso2              | $4.0~V \leq V_{DD} \leq 5.5~V,$                    | $2.7 \text{ V} \le V_b \le 4.0 \text{ V},$                 |              | 2/fмск + |              | 2/fмск + | ns |

| SCKp↓ to SOp                                      |                    | C <sub>b</sub> = 30 pF, R <sub>b</sub> = 1.4       | kΩ                                                         |              | 120      |              | 573      |    |

| output Note 5                                     |                    | $2.7 \text{ V} \le \text{V}_{DD} < 4.0 \text{ V},$ | $2.3 \text{ V} \le V_b \le 2.7 \text{ V},$                 |              | 2/fмск + |              | 2/fмск + | ns |

|                                                   |                    | C <sub>b</sub> = 30 pF, R <sub>b</sub> = 2.7       | kΩ                                                         |              | 214      |              | 573      |    |

|                                                   |                    | $1.8 \text{ V} \le \text{V}_{DD} < 3.3 \text{ V},$ | $1.6 \text{ V} \le V_b \le 2.0 \text{ V}^{\text{Note 2}},$ |              | 2/fмск + |              | 2/fмск + | ns |

|                                                   | 1                  | C <sub>b</sub> = 30 pF, R <sub>b</sub> = 5.5       | kΩ                                                         |              | 573      |              | 573      |    |

Notes 1. Transfer rate in the SNOOZE mode: MAX. 1 Mbps

- 2. Use it with  $V_{DD} \ge V_b$ .

- 3. When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The SIp setup time becomes "to  $SCKp\downarrow$ " when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

- **4.** When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The SIp hold time becomes "from  $SCKp\downarrow$ " when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

- **5.** When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The delay time to SOp output becomes "from SCKp $\uparrow$ " when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

Cautions 1. Select the TTL input buffer for the SIp and SCKp pins and the N-ch open drain output (VDD tolerance) mode for the SOp pin by using port input mode register 1 (PIM1) and port output mode register 1 (POM1).

For VIH and VIL, see the DC characteristics with TTL input buffer selected.

2. CSI01 and CSI11 cannot communicate at different potential.

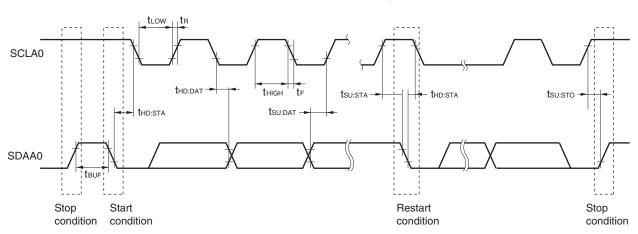

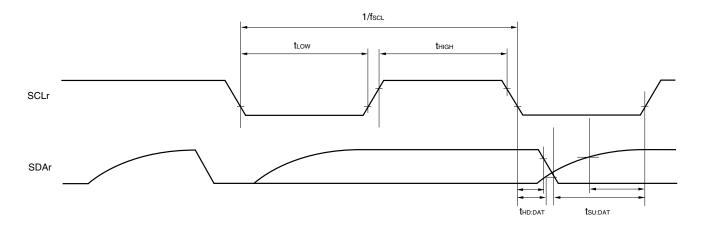

#### 2.5.2 Serial interface IICA

$(T_A = -40 \text{ to } +85^{\circ}\text{C}, 1.8 \text{ V} \le V_{DD} \le 5.5 \text{ V}, \text{Vss} = 0 \text{ V})$

| Parameter                                       | Symbol  | Conditions               | HS     | (high-spee              | Unit      |      |     |

|-------------------------------------------------|---------|--------------------------|--------|-------------------------|-----------|------|-----|

|                                                 |         |                          | LS     | (low-spee               | d main) m | ode  |     |

|                                                 |         |                          | Standa | Standard Mode Fast Mode |           | Mode |     |

|                                                 |         |                          | MIN.   | MAX.                    | MIN.      | MAX. |     |

| SCLA0 clock frequency                           | fscL    | Fast mode: fclk≥ 3.5 MHz |        |                         | 0         | 400  | kHz |

|                                                 |         | Normal mode: fclk≥ 1 MHz | 0      | 100                     |           |      | kHz |

| Setup time of restart condition                 | tsu:sta |                          | 4.7    |                         | 0.6       |      | μS  |

| Hold time <sup>Note 1</sup>                     | thd:sta |                          | 4.0    |                         | 0.6       |      | μS  |

| Hold time when SCLA0 = "L"                      | tLOW    |                          | 4.7    |                         | 1.3       |      | μS  |

| Hold time when SCLA0 = "H"                      | tніgн   |                          | 4.0    |                         | 0.6       |      | μS  |

| Data setup time (reception)                     | tsu:dat |                          | 250    |                         | 100       |      | ns  |

| Data hold time (transmission) <sup>Note 2</sup> | thd:dat |                          | 0      | 3.45                    | 0         | 0.9  | μS  |

| Setup time of stop condition                    | tsu:sto |                          | 4.0    |                         | 0.6       |      | μS  |

| Bus-free time                                   | tBUF    |                          | 4.7    |                         | 1.3       |      | μS  |

Notes 1. The first clock pulse is generated after this period when the start/restart condition is detected.

2. The maximum value (MAX.) of thd:DAT is during normal transfer and a wait state is inserted in the ACK (acknowledge) timing.

Caution Only in the 30-pin products, the values in the above table are applied even when bit 2 (PIOR2) in the peripheral I/O redirection register (PIOR) is 1. At this time, the pin characteristics (IoH1, IoL1, VoH1, VoL1) must satisfy the values in the redirect destination.

**Remark** The maximum value of Cb (communication line capacitance) and the value of Rb (communication line pull-up resistor) at that time in each mode are as follows.

Normal mode:  $C_b$  = 400 pF, Rb = 2.7 k $\Omega$  Fast mode:  $C_b$  = 320 pF, Rb = 1.1 k $\Omega$

#### IICA serial transfer timing

<R>

(3) When reference voltage (+) = V<sub>DD</sub> (ADREFP1 = 0, ADREFP0 = 0), reference voltage (-) = V<sub>SS</sub> (ADREFM = 0), target pin: ANI0 to ANI3, ANI16 to ANI22, internal reference voltage, and temperature sensor output voltage

$(T_A = -40 \text{ to } +85^{\circ}\text{C}, 1.8 \text{ V} \le V_{DD} \le 5.5 \text{ V}, V_{SS} = 0 \text{ V}, \text{ Reference voltage (+)} = V_{DD}, \text{ Reference voltage (-)} = V_{SS})$

| Parameter                                  | Symbol | Condition                                                                   | ns                                                 | MIN.   | TYP.                    | MAX.              | Unit |

|--------------------------------------------|--------|-----------------------------------------------------------------------------|----------------------------------------------------|--------|-------------------------|-------------------|------|

| Resolution                                 | Res    |                                                                             |                                                    | 8      |                         | 10                | bit  |

| Overall error <sup>Note 1</sup>            | AINL   | 10-bit resolution                                                           |                                                    |        | 1.2                     | ±7.0              | LSB  |

|                                            |        |                                                                             |                                                    |        | 1.2                     | $\pm 10.5$ Note 3 | LSB  |

| Conversion time                            | tconv  | 10-bit resolution                                                           | $3.6~V \leq V_{DD} \leq 5.5~V$                     | 2.125  |                         | 39                | μs   |

|                                            |        | Target pin: ANIO to ANI3,                                                   | $2.7~V \leq V_{DD} \leq 5.5~V$                     | 3.1875 |                         | 39                | μS   |

|                                            |        | ANI16 to ANI22                                                              | $1.8~V \leq V_{DD} \leq 5.5~V$                     | 17     |                         | 39                | μs   |

|                                            |        |                                                                             |                                                    | 57     |                         | 95                | μS   |

| Conversion time                            | tconv  | 10-bit resolution                                                           | $3.6~V \leq V_{DD} \leq 5.5~V$                     | 2.375  |                         | 39                | μS   |

|                                            |        | voltage, and temperature                                                    | $2.7 \text{ V} \leq \text{VDD} \leq 5.5 \text{ V}$ | 3.5625 |                         | 39                | μS   |

|                                            |        |                                                                             | $2.4~V \leq V_{DD} \leq 5.5~V$                     | 17     |                         | 39                | μS   |

| Zero-scale error <sup>Notes 1, 2</sup>     | EZS    | 10-bit resolution                                                           |                                                    |        |                         | ±0.60             | %FSR |

|                                            |        |                                                                             |                                                    |        | ±0.85                   | %FSR              |      |

| Full-scale errorNotes 1, 2                 | EFS    | 10-bit resolution                                                           |                                                    |        |                         | ±0.60             | %FSR |

|                                            |        |                                                                             |                                                    |        |                         | ±0.85             | %FSR |

| Integral linearity error <sup>Note 1</sup> | ILE    | 10-bit resolution                                                           |                                                    |        |                         | ±4.0              | LSB  |

|                                            |        |                                                                             |                                                    |        |                         | ±6.5 Note 3       | LSB  |

| Differential linearity error Note 1        | DLE    | 10-bit resolution                                                           |                                                    |        |                         | ±2.0              | LSB  |

|                                            |        |                                                                             |                                                    |        |                         | ±2.5 Note 3       | LSB  |

| Analog input voltage                       | VAIN   | ANI0 to ANI3, ANI16 to ANI2                                                 | 2                                                  | 0      |                         | V <sub>DD</sub>   | V    |

|                                            |        | Internal reference voltage (2.4 V ≤ VDD ≤ 5.5 V, HS (high-speed main) mode) |                                                    |        | V <sub>BGR</sub> Note 4 |                   |      |

|                                            |        | Temperature sensor output v (2.4 V $\leq$ VDD $\leq$ 5.5 V, HS (high        | •                                                  |        | VTMPS25 Note 4          | 1                 | V    |

Notes 1. Excludes quantization error (±1/2 LSB).

- 2. This value is indicated as a ratio (%FSR) to the full-scale value.

- **3.** When the conversion time is set to 57  $\mu$ s (min.) and 95  $\mu$ s (max.).

- 4. Refer to 28.6.2 Temperature sensor/internal reference voltage characteristics.

## 2.6.2 Temperature sensor/internal reference voltage characteristics

(T<sub>A</sub> = -40 to +85°C, 2.4 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, V<sub>SS</sub> = 0 V, HS (high-speed main) mode

| Parameter                         | Symbol              | Conditions                                                        | MIN. | TYP. | MAX. | Unit  |

|-----------------------------------|---------------------|-------------------------------------------------------------------|------|------|------|-------|

| Temperature sensor output voltage | V <sub>TMPS25</sub> | Setting ADS register = 80H,<br>TA = +25°C                         |      | 1.05 |      | ٧     |

| Internal reference voltage        | V <sub>BGR</sub>    | Setting ADS register = 81H                                        | 1.38 | 1.45 | 1.50 | V     |

| Temperature coefficient           | FVTMPS              | Temperature sensor output voltage that depends on the temperature |      | -3.6 |      | mV/°C |

| Operation stabilization wait time | tамр                |                                                                   | 5    |      |      | μS    |

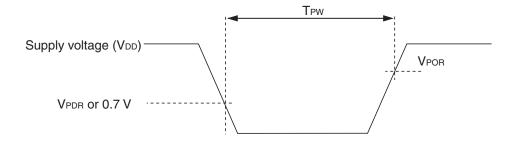

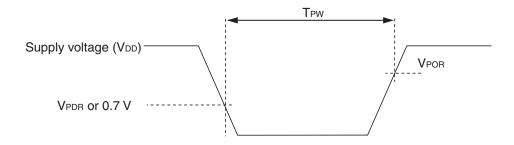

### 2.6.3 POR circuit characteristics

$(T_A = -40 \text{ to } +85^{\circ}\text{C}, \text{ Vss} = 0 \text{ V})$

| <u>,                                      </u> |                  |                        |      |      |      |      |

|------------------------------------------------|------------------|------------------------|------|------|------|------|

| Parameter                                      | Symbol           | Conditions             | MIN. | TYP. | MAX. | Unit |

| Detection voltage                              | Vpor             | Power supply rise time | 1.47 | 1.51 | 1.55 | ٧    |

|                                                | V <sub>PDR</sub> | Power supply fall time | 1.46 | 1.50 | 1.54 | ٧    |

| Minimum pulse width Note                       | T <sub>PW</sub>  |                        | 300  |      |      | μs   |

Note Minimum time required for a POR reset when V<sub>DD</sub> exceeds below V<sub>PDR</sub>. This is also the minimum time required for a POR reset from when V<sub>DD</sub> exceeds below 0.7 V to when V<sub>DD</sub> exceeds V<sub>PDR</sub> while STOP mode is entered or the main system clock is stopped through setting bit 0 (HIOSTOP) and bit 7 (MSTOP) in the clock operation status control register (CSC).

## 2.9 Dedicated Flash Memory Programmer Communication (UART)

$(T_A = -40 \text{ to } +85^{\circ}\text{C}, 1.8 \text{ V} \le V_{DD} \le 5.5 \text{ V}, \text{Vss} = 0 \text{ V})$

| Parameter     | Symbol | Conditions                | MIN.    | TYP. | MAX.      | Unit |

|---------------|--------|---------------------------|---------|------|-----------|------|

| Transfer rate |        | During serial programming | 115,200 |      | 1,000,000 | bps  |

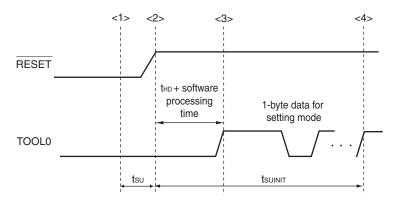

### 2.10 Timing of Entry to Flash Memory Programming Modes

$(T_A = -40 \text{ to } +85^{\circ}\text{C}, 1.8 \text{ V} \le V_{DD} \le 5.5 \text{ V}, \text{Vss} = 0 \text{ V})$

| Parameter                                                                                                                                                    | Symbol  | Conditions                                                   | MIN. | TYP. | MAX. | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------------------------------------------------|------|------|------|------|

| Time to complete the communication for the initial setting after the external reset is released                                                              | tsuinit | POR and LVD reset are released before external reset release |      |      | 100  | ms   |

| Time to release the external reset after the TOOL0 pin is set to the low level                                                                               | tsu     | POR and LVD reset are released before external reset release | 10   |      |      | μS   |

| Time to hold the TOOL0 pin at the low level after the external reset is released (excluding the processing time of the firmware to control the flash memory) | tнo     | POR and LVD reset are released before external reset release | 1    |      |      | ms   |

- <1> The low level is input to the TOOL0 pin.

- <2> The external reset is released (POR and LVD reset must be released before the external reset is released.).

- <3> The TOOL0 pin is set to the high level.

- <4> Setting of the flash memory programming mode by UART reception and complete the baud rate setting.

Remark tsuinit: Communication for the initial setting must be completed within 100 ms after the external reset is released during this period.

$t_{\text{SU}}$ : Time to release the external reset after the TOOL0 pin is set to the low level

thd: Time to hold the TOOL0 pin at the low level after the external reset is released (excluding the processing time of the firmware to control the flash memory)

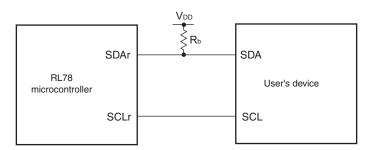

#### (4) During communication at same potential (simplified I<sup>2</sup>C mode)

$(T_A = -40 \text{ to } +105^{\circ}\text{C}, 2.4 \text{ V} \le V_{DD} \le 5.5 \text{ V}, \text{Vss} = 0 \text{ V})$

| Parameter                     | Symbol  | Conditions                                      | HS (high-speed main) Mode       |            | Unit |

|-------------------------------|---------|-------------------------------------------------|---------------------------------|------------|------|

|                               |         |                                                 | MIN.                            | MAX.       |      |

| SCLr clock frequency          | fscL    | $C_b=100~pF,~R_b=3~k\Omega$                     |                                 | 100 Note 1 | kHz  |

| Hold time when SCLr = "L"     | tLOW    | $C_b=100~pF,~R_b=3~k\Omega$                     | 4600                            |            | ns   |

| Hold time when SCLr = "H"     | thigh   | $C_b = 100 \text{ pF}, R_b = 3 \text{ k}\Omega$ | 4600                            |            | ns   |

| Data setup time (reception)   | tsu:dat | $C_b=100~pF,~R_b=3~k\Omega$                     | 1/f <sub>MCK</sub> + 580 Note 2 |            | ns   |

| Data hold time (transmission) | thd:dat | $C_b = 100 \text{ pF}, R_b = 3 \text{ k}\Omega$ | 0                               | 1420       | ns   |

- Notes 1. The value must also be equal to or less than fmck/4.

- 2. Set tsu:DAT so that it will not exceed the hold time when SCLr = "L" or SCLr = "H".

**Caution** Select the N-ch open drain output (V<sub>DD</sub> tolerance) mode for SDAr by using port output mode register h (POMh).

#### Simplified I<sup>2</sup>C mode connection diagram (during communication at same potential)

### Simplified I<sup>2</sup>C mode serial transfer timing (during communication at same potential)

- **Remarks 1.**  $\mathsf{R}_{\mathsf{b}}\left[\Omega\right]$ :Communication line (SDAr) pull-up resistance

- Cb [F]: Communication line (SCLr, SDAr) load capacitance

- 2. r: IIC number (r = 00, 01, 11, 20), h: = POM number (h = 0, 1, 4, 5)

- 3. fmck: Serial array unit operation clock frequency (Operation clock to be set by the serial clock select register m (SPSm) and the CKSmn bit of serial mode register mn (SMRmn).

- m: Unit number (m = 0, 1), n: Channel number (0, 1, 3))

# CSI mode serial transfer timing (master mode) (during communication at different potential) (When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1)

# CSI mode serial transfer timing (master mode) (during communication at different potential) (When DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.)

**Remark** p: CSI number (p = 00, 20), m: Unit number (m = 0, 1), n: Channel number (n = 0)

### CSI mode connection diagram (during communication at different potential)

CSI mode serial transfer timing (slave mode) (during communication at different potential)

(When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1.)

**Remarks 1.** R<sub>b</sub> [ $\Omega$ ]: Communication line (SOp) pull-up resistance, C<sub>b</sub> [F]: Communication line (SOp) load capacitance, V<sub>b</sub> [V]: Communication line voltage

- 2. p: CSI number (p = 00, 20), m: Unit number (m = 0, 1), n: Channel number (n = 0)

- fmck: Serial array unit operation clock frequency (Operation clock to be set by the serial clock select register m (SPSm) and the CKSmn bit of serial mode register mn (SMRmn))

(3) When reference voltage (+) = V<sub>DD</sub> (ADREFP1 = 0, ADREFP0 = 0), reference voltage (-) = V<sub>SS</sub> (ADREFM = 0), target pin: ANI0 to ANI3, ANI16 to ANI22, internal reference voltage, and temperature sensor output voltage

$(T_A = -40 \text{ to } +105^{\circ}\text{C}, 2.4 \text{ V} \le V_{DD} \le 5.5 \text{ V}, \text{Vss} = 0 \text{ V}, \text{Reference voltage (+)} = V_{DD}, \text{ Reference voltage (-)} = V_{SS})$

| Parameter                                  | Symbol | Condition                                                                  | ns                                                 | MIN.   | TYP.           | MAX.            | Unit |

|--------------------------------------------|--------|----------------------------------------------------------------------------|----------------------------------------------------|--------|----------------|-----------------|------|

| Resolution                                 | Res    |                                                                            |                                                    | 8      |                | 10              | bit  |

| Overall error <sup>Note 1</sup>            | AINL   | 10-bit resolution                                                          |                                                    |        | 1.2            | ±7.0            | LSB  |

| Conversion time                            | tconv  | 10-bit resolution                                                          | $3.6~V \leq V_{DD} \leq 5.5~V$                     | 2.125  |                | 39              | μs   |

|                                            |        | Target pin: ANI0 to ANI3,                                                  | $2.7~V \leq V_{DD} \leq 5.5~V$                     | 3.1875 |                | 39              | μs   |

|                                            |        | ANI16 to ANI22                                                             | $2.4~V \leq V_{DD} \leq 5.5~V$                     | 17     |                | 39              | μs   |

| Conversion time                            | tconv  | 10-bit resolution                                                          | $3.6~V \leq V_{DD} \leq 5.5~V$                     | 2.375  |                | 39              | μs   |

|                                            |        | Target pin: internal reference                                             | $2.7 \text{ V} \leq \text{VDD} \leq 5.5 \text{ V}$ | 3.5625 |                | 39              | μs   |

|                                            |        | voltage, and temperature sensor output voltage (HS (high-speed main) mode) | $2.4~V \leq V_{DD} \leq 5.5~V$                     | 17     |                | 39              | μs   |

| Zero-scale error <sup>Notes 1, 2</sup>     | EZS    | 10-bit resolution                                                          |                                                    |        | ±0.60          | %FSR            |      |

| Full-scale errorNotes 1, 2                 | EFS    | 10-bit resolution                                                          |                                                    |        | ±0.60          | %FSR            |      |

| Integral linearity error <sup>Note 1</sup> | ILE    | 10-bit resolution                                                          |                                                    |        |                | ±4.0            | LSB  |

| Differential linearity error Note 1        | DLE    | 10-bit resolution                                                          |                                                    |        |                | ±2.0            | LSB  |

| Analog input voltage                       | VAIN   | ANI0 to ANI3, ANI16 to ANI2                                                | 2                                                  | 0      |                | V <sub>DD</sub> | ٧    |

|                                            |        | Internal reference voltage (HS (high-speed main) mode)                     |                                                    |        | VBGR Note 3    |                 | V    |

|                                            |        | Temperature sensor output v (HS (high-speed main) mode)                    | 3                                                  |        | VTMPS25 Note 3 | 1               | V    |

Notes 1. Excludes quantization error ( $\pm 1/2$  LSB).

- 2. This value is indicated as a ratio (%FSR) to the full-scale value.

- 3. Refer to 29.6.2 Temperature sensor/internal reference voltage characteristics.

## 3.6.2 Temperature sensor/internal reference voltage characteristics

(T<sub>A</sub> = -40 to +105°C, 2.4 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, V<sub>SS</sub> = 0 V, HS (high-speed main) mode

| Parameter                         | Symbol              | Conditions                                                        | MIN. | TYP. | MAX. | Unit  |

|-----------------------------------|---------------------|-------------------------------------------------------------------|------|------|------|-------|

| Temperature sensor output voltage | V <sub>TMPS25</sub> | Setting ADS register = 80H,<br>TA = +25°C                         |      | 1.05 |      | V     |

| Internal reference voltage        | V <sub>BGR</sub>    | Setting ADS register = 81H                                        | 1.38 | 1.45 | 1.50 | V     |

| Temperature coefficient           | Fvтмps              | Temperature sensor output voltage that depends on the temperature |      | -3.6 |      | mV/°C |

| Operation stabilization wait time | tamp                |                                                                   | 5    |      |      | μs    |

### 3.6.3 POR circuit characteristics

$(T_A = -40 \text{ to } +105^{\circ}\text{C}, \text{ Vss} = 0 \text{ V})$

| Parameter                | Symbol           | Conditions             | MIN. | TYP. | MAX. | Unit |

|--------------------------|------------------|------------------------|------|------|------|------|

| Detection voltage        | VPOR             | Power supply rise time | 1.45 | 1.51 | 1.57 | V    |

|                          | V <sub>PDR</sub> | Power supply fall time | 1.44 | 1.50 | 1.56 | V    |

| Minimum pulse width Note | T <sub>PW</sub>  |                        | 300  |      |      | μs   |

Note Minimum time required for a POR reset when V<sub>DD</sub> exceeds below V<sub>PDR</sub>. This is also the minimum time required for a POR reset from when V<sub>DD</sub> exceeds below 0.7 V to when V<sub>DD</sub> exceeds V<sub>PDR</sub> while STOP mode is entered or the main system clock is stopped through setting bit 0 (HIOSTOP) and bit 7 (MSTOP) in the clock operation status control register (CSC).

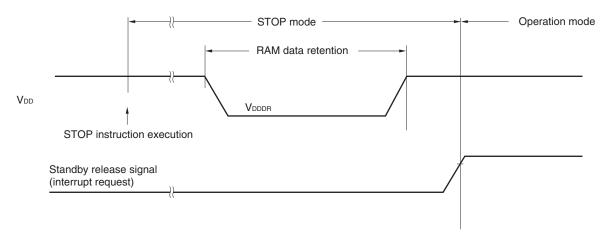

### <R> 3.7 RAM Data Retention Characteristics

$(T_A = -40 \text{ to } +105^{\circ}\text{C}, \text{ Vss} = 0 \text{ V})$

| Parameter                     | Symbol            | Conditions | MIN.      | TYP. | MAX. | Unit |

|-------------------------------|-------------------|------------|-----------|------|------|------|

| Data retention supply voltage | V <sub>DDDR</sub> |            | 1.44 Note |      | 5.5  | V    |

<R> Note This depends on the POR detection voltage. For a falling voltage, data in RAM are retained until the voltage reaches the level that triggers a POR reset but not once it reaches the level at which a POR reset is generated.

## 3.8 Flash Memory Programming Characteristics

$(T_A = -40 \text{ to } +105^{\circ}\text{C}. 2.4 \text{ V} < V_{DD} < 5.5 \text{ V}. \text{ Vss} = 0 \text{ V})$

| Parameter                          | Symbol | Conditions                               | MIN.    | TYP.      | MAX. | Unit  |

|------------------------------------|--------|------------------------------------------|---------|-----------|------|-------|

| System clock frequency             | fclk   |                                          | 1       |           | 24   | MHz   |

| Code flash memory rewritable times | Cerwr  | Retained for 20 years  TA = 85°C Notes 4 | 1,000   |           |      | Times |

| Data flash memory rewritable times |        | Retained for 1 year  TA = 25°C Notes 4   |         | 1,000,000 |      |       |

|                                    |        | Retained for 5 years  TA = 85°C Notes 4  | 100,000 |           |      |       |

|                                    |        | Retained for 20 years  TA = 85°C Notes 4 | 10,000  |           |      |       |

- **Notes 1.** 1 erase + 1 write after the erase is regarded as 1 rewrite. The retaining years are until next rewrite after the rewrite.

- 2. When using flash memory programmer and Renesas Electronics self programming library

- **3.** These are the characteristics of the flash memory and the results obtained from reliability testing by Renesas Electronics Corporation.

- 4. This temperature is the average value at which data are retained.