Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

XF

| Product Status             | Obsolete                                                                        |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | RL78                                                                            |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 24MHz                                                                           |

| Connectivity               | CSI, I <sup>2</sup> C, UART/USART, USB                                          |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                         |

| Number of I/O              | 22                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | 2K x 8                                                                          |

| RAM Size                   | 5.5K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                                     |

| Data Converters            | A/D 8x8/10b                                                                     |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 32-WFQFN Exposed Pad                                                            |

| Supplier Device Package    | 32-HWQFN (5x5)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f10kbcgna-u0 |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### ROM, RAM capacities

| Flash ROM | Data flash | RAM                    | RL78/G1C           |                    |

|-----------|------------|------------------------|--------------------|--------------------|

|           |            |                        | 32-pin             | 48-pin             |

| 32 KB     | 2 KB       | 5.5 KB <sup>Note</sup> | R5F10JBC, R5F10KBC | R5F10JGC, R5F10KGC |

Note This is about 4.5 KB when the self-programming function is used.

**Remark** The functions mounted depend on the product. See **1.6 Outline of Functions**.

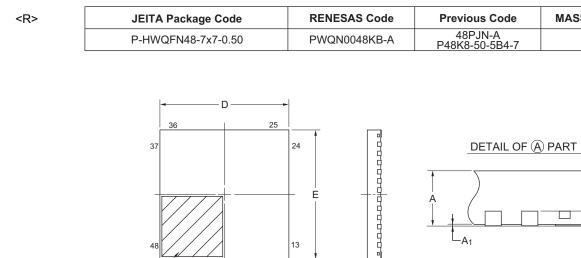

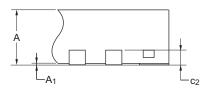

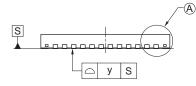

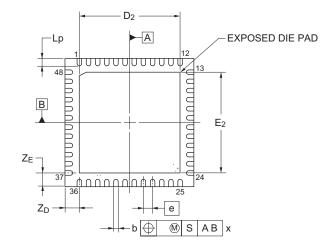

#### 1.2 List of Part Numbers

| Pin count | Package                | USB Function             | Fields of<br>Application <sup>Note</sup> | Part Number                     |

|-----------|------------------------|--------------------------|------------------------------------------|---------------------------------|

| 32 pins   | 32-pin plastic HWQFN   | Host/Function controller | А                                        | R5F10JBCANA#U0, R5F10JBCANA#W0  |

|           | (5 × 5 , 0.5 mm pitch) |                          | G                                        | R5F10JBCGNA#U0, R5F10JBCGNA#W0  |

|           |                        | Function controller only | А                                        | R5F10KBCANA#U0, R5F10KBCANA#W0  |

|           |                        |                          | G                                        | R5F10KBCGNA#U0, R5F10KBCGNA#W0  |

|           | 32-pin plastic LQFP    | Host/Function controller | А                                        | R5F10JBCAFP#V0, R5F10JBCAFP#X0  |

|           | (7 × 7 , 0.8 mm pitch) |                          | G                                        | R5F10JBCGFP#V0, R5F10JBCGFP#X0  |

|           |                        | Function controller only | А                                        | R5F10KBCAFP#V0, R5F10KBCAFP#X0  |

|           |                        |                          | G                                        | R5F10KBCGFP#V0, R5F10KBCGFP#X0  |

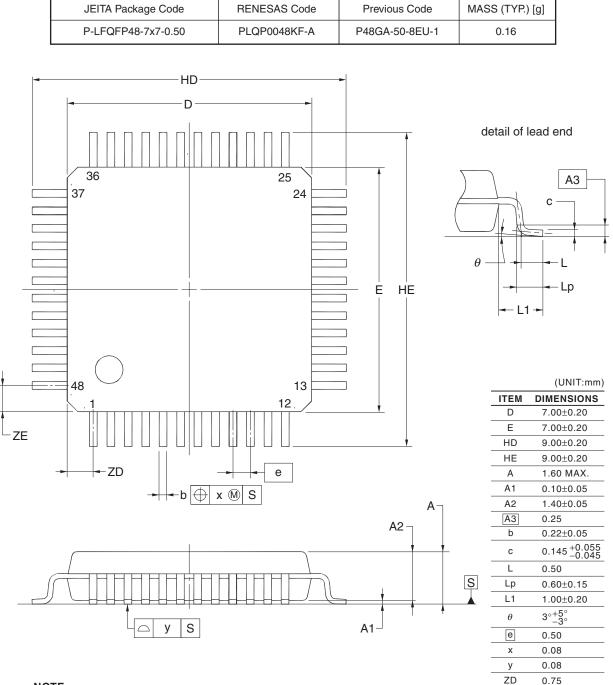

| 48 pins   | 48-pin plastic LFQFP   | Host/Function controller | А                                        | R5F10JGCAFB#V0, R5F10JGCAFB#X0  |

|           | (7 × 7 , 0.5 mm pitch) |                          | G                                        | R5F10JGCGFB#V0, R5F10JGCGFB#X0  |

|           |                        | Function controller only | А                                        | R5F10KGCAFB#V0, R5F10KGCAFB#X0s |

|           |                        |                          | G                                        | R5F10JGCANA#U0, R5F10JGCANA#W0  |

|           | 48-pin plastic HWQFN   | Host/Function controller | А                                        | R5F10JGCANA#U0, R5F10JGCANA#W0  |

|           | (7 × 7 , 0.5 mm pitch) |                          | G                                        | R5F10JGCGNA#U0, R5F10JGCGNA#W0  |

|           |                        | Function controller only | А                                        | R5F10KGCANA#U0, R5F10KGCANA#W0  |

|           |                        |                          | G                                        | R5F10KGCGNA#U0, R5F10KGCGNA#W0  |

Note For the fields of application, refer to Figure 1-1 Part Number, Memory Size, and Package of RL78/G1C.

Caution The part number above is valid as of when this manual was issued. For the latest part number, see the web page of the target product on the Renesas Electronics website.

#### 1.6 Outline of Functions

[32-pin, 48-pin products]

| Item             |                                        | Item                             | 32                                                                                      | 2-pin                                                                       | 48-pin                                              |                     |  |

|------------------|----------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------|---------------------|--|

|                  |                                        |                                  | R5F10JBC                                                                                | R5F10KBC                                                                    | R5F10JGC                                            | R5F10KGC            |  |

| Co               | ode flash                              | memory (KB)                      | 32 KB                                                                                   |                                                                             | 32 KB                                               |                     |  |

| Dat              | ata flash r                            | memory (KB)                      | 2 KB                                                                                    |                                                                             | 2 KB                                                |                     |  |

| RA               | AM (KB)                                |                                  | 5.5 KB Note 1                                                                           |                                                                             | 5.5 KB Note 1                                       |                     |  |

| Me               | emory spa                              | ace                              | 1 MB                                                                                    |                                                                             |                                                     |                     |  |

| Ma<br>sys<br>clo | stem                                   | High-speed system<br>clock       | HS (High-speed main)                                                                    | scillation, external main<br>mode: 1 to 20 MHz (V⊳<br>mode: 1 to 16 MHz (V⊳ |                                                     | K)                  |  |

|                  |                                        | High-speed on-chip<br>oscillator |                                                                                         | ' to 5.5 V), 1 to 16 MHz                                                    | (V <sub>DD</sub> = 2.4 to 5.5 V)                    |                     |  |

|                  |                                        | PLL clock                        | 6, 12, 24 MHz <sup>Note 2</sup> :                                                       | VDD = 2.4 to 5.5 V                                                          |                                                     |                     |  |

| Sul              | ıbsystem                               | clock                            |                                                                                         | -                                                                           | XT1 (crystal) oscillation<br>32.768 kHz (TYP.): Vot |                     |  |

| Lov              | w-speed                                | on-chip oscillator               | On-chip oscillation (W                                                                  | atchdog timer/Real-time                                                     | clock/12-bit interval timer                         | clock)              |  |

|                  |                                        |                                  | 15 kHz (TYP.): VDD = 2                                                                  | 2.4 to 5.5 V                                                                |                                                     |                     |  |

| Ge               | eneral-pu                              | rpose register                   | 8 bits $	imes$ 32 registers (8                                                          | bits $\times$ 8 registers $\times$ 4 ba                                     | anks)                                               |                     |  |

| Mir              | nimum in                               | struction execution time         | 0.04167 $\mu$ s (High-speed on-chip oscillator: fHoco = 48 MHz /fiH = 24 MHz operation) |                                                                             |                                                     |                     |  |

|                  |                                        |                                  | 0.04167 $\mu$ s (PLL clock: fPLL = 48 MHz /fiH = 24 MHz <sup>Note 2</sup> operation)    |                                                                             |                                                     |                     |  |

|                  |                                        |                                  | 0.05 $\mu$ s (High-speed system clock: f <sub>MX</sub> = 20 MHz operation)              |                                                                             |                                                     |                     |  |

|                  |                                        |                                  | $- 30.5 \ \mu s \ (Subsystem \ clock: \ f_{SUB} = 32.768 \ kHoperation)$                |                                                                             |                                                     |                     |  |

| Ins              | struction s                            | set                              | <ul> <li>Multiplication (8 bit</li> </ul>                                               | for/logical operation (8/1 s $\times$ 8 bits)                               | 6 bits)<br>iet, reset, test, and Boolea             | n operation), etc.  |  |

| I/O              | ) port                                 | Total                            | 22                                                                                      |                                                                             | 38                                                  |                     |  |

|                  |                                        | CMOS I/O                         | 16 (N-ch O.D. I/O [VDD                                                                  | withstand voltage]: 5)                                                      | 28 (N-ch O.D. I/O [VDD                              | withstand voltage]: |  |

|                  |                                        | CMOS input                       | 3                                                                                       |                                                                             | 5                                                   |                     |  |

|                  |                                        | CMOS output                      |                                                                                         | -                                                                           | 1                                                   |                     |  |

|                  | N-ch open-drain I/O<br>(6 V tolerance) |                                  | 3                                                                                       |                                                                             | 4                                                   |                     |  |

| Tim              | mer                                    | 16-bit timer                     | 4 channel                                                                               |                                                                             |                                                     |                     |  |

|                  |                                        | Watchdog timer                   | 1 channel                                                                               |                                                                             |                                                     |                     |  |

|                  |                                        | Real-time clock (RTC)            | 1 channel Note 3                                                                        |                                                                             |                                                     |                     |  |

|                  |                                        | 12-bit Interval timer (IT)       | 1 channel                                                                               |                                                                             |                                                     |                     |  |

|                  |                                        | Timer output                     | 4 channels (PWM outp                                                                    | ut: 3) <sup>Note 4</sup>                                                    |                                                     |                     |  |

|                  |                                        | RTC output                       | _                                                                                       |                                                                             | 1                                                   |                     |  |

|                  |                                        |                                  |                                                                                         |                                                                             | • 1 Hz (subsystem cloc                              | k: four = 32 768 kH |  |

**Notes 1.** In the case of the 5.5 KB, this is about 4.5 KB when the self-programming function is used.

2. In the PLL clock 48 MHz operation, the system clock is 2/4/8 dividing ratio.

- **3.** In 32-pin products, this channel can only be used for the constant-period interrupt function based on the low-speed on-chip oscillator clock (fiL).

- 4. The number of PWM outputs varies depending on the setting of channels in use (the number of masters and slaves).

Caution This outline describes the functions at the time when Peripheral I/O redirection register (PIOR) is set to 00H.

| Items                                    | Symbol | Conditions                                                                                                                                                                   | MIN.                                                      | TYP. | MAX. | Unit                      |    |

|------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|------|------|---------------------------|----|

| Output current,<br>Iow <sup>Note 1</sup> | Iol1   | Per pin for P00, P01, P14 to P17,<br>P30, P31, P40, P41, P50, P51,<br>P70 to P75, P120, P130, P140                                                                           | $2.4V \leq V_{\text{DD}} \leq 5.5 \text{ V}$              |      |      | 20.0 <sup>Note</sup><br>2 | mA |

|                                          |        | Per pin for P60 to P63                                                                                                                                                       | $2.4V \leq V_{\text{DD}} \leq 5.5 \text{ V}$              |      |      | 20.0 <sup>Note</sup><br>2 | mA |

|                                          |        | Total of P00, P01, P40, P41, P120,                                                                                                                                           | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$                     |      |      | 70.0                      | mA |

|                                          |        | P130, P140<br>(When duty $\leq 70\%$ <sup>Note 3</sup> )<br>Total of P14 to P17, P30, P31, P50,<br>P51, P60 to P63, P70 to P75<br>(When duty $\leq 70\%$ <sup>Note 3</sup> ) | $2.7~V \leq V_{\text{DD}} < 4.0~V$                        |      |      | 15.0                      | mA |

|                                          |        |                                                                                                                                                                              | $2.4 \text{ V} \leq \text{V}_{\text{DD}} < 2.7 \text{ V}$ |      |      | 9.0                       | mA |

|                                          |        |                                                                                                                                                                              | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$                     |      |      | 80.0                      | mA |

|                                          |        |                                                                                                                                                                              | $2.7~V \leq V_{\text{DD}} < 4.0~V$                        |      |      | 35.0                      | mA |

|                                          |        |                                                                                                                                                                              | $2.4 \text{ V} \leq \text{V}_{\text{DD}} < 2.7 \text{ V}$ |      |      | 20.0                      | mA |

|                                          |        | Total of all pins<br>(When duty $\leq 70\%^{\text{Note 3}}$ )                                                                                                                | $2.4V \le V_{\text{DD}} \le 5.5 \text{ V}$                |      |      | 150.0                     | mA |

|                                          | IOL2   | Per pin for P20 to P27                                                                                                                                                       | $2.4V \leq V_{\text{DD}} \leq 5.5~V$                      |      |      | 0.4 Note 2                | mA |

|                                          |        | Total of all pins<br>(When duty ≤ 70% <sup>Note 3</sup> )                                                                                                                    | $2.4V \leq V_{\text{DD}} \leq 5.5 \text{ V}$              |      |      | 5.0                       | mA |

#### $(T_A = -40 \text{ to } +85^{\circ}C, 2.4 \text{ V} \le \text{V}_{DD} \le 5.5 \text{ V}, \text{V}_{SS} = 0 \text{ V})$

- **Notes 1**. Value of current at which the device operation is guaranteed even if the current flows from an output pin to the Vss pin.

- 2. However, do not exceed the total current value.

- **3.** Specification under conditions where the duty factor  $\leq$  70%.

The output current value that has changed to the duty factor > 70% the duty ratio can be calculated with the following expression (when changing the duty ratio to n%).

- Total output current of pins =  $(I_{OL} \times 0.7)/(n \times 0.01)$

- <Example> Where n = 80% and IoL = 10.0 mA

Total output current of pins =  $(10.0 \times 0.7)/(80 \times 0.01) \approx 8.7$  mA

However, the current that is allowed to flow into one pin does not vary depending on the duty factor. A current higher than the absolute maximum rating must not flow into one pin.

**Remark** Unless specified otherwise, the characteristics of alternate-function pins are the same as those of the port pins.

### 2.3.2 Supply current characteristics

(1/2)

| Parameter         | Symbol |                        |                                                                 | Conditions                                                                |                         |                         | MIN. | TYP. | MAX. | Unit     |

|-------------------|--------|------------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------|-------------------------|-------------------------|------|------|------|----------|

| Supply            | IDD1   | Operating              | HS                                                              | fносо = 48 MHz                                                            | Basic                   | V <sub>DD</sub> = 5.0 V |      | 1.7  |      | mA       |

| Current<br>Note 1 | mode   | (High-speed main) mode | f <sub>IH</sub> = 24 MHz <sup>Note 3</sup>                      | operation                                                                 | V <sub>DD</sub> = 3.0 V |                         | 1.7  |      | mA   |          |

|                   |        |                        | Note 6                                                          |                                                                           | Normal                  | V <sub>DD</sub> = 5.0 V |      | 3.7  | 5.5  | mA       |

|                   |        |                        |                                                                 |                                                                           | operation               | V <sub>DD</sub> = 3.0 V |      | 3.7  | 5.5  | mA       |

|                   |        |                        |                                                                 | f <sub>HOCO</sub> = 24 MHz <sup>Note 5</sup>                              | Normal                  | V <sub>DD</sub> = 5.0 V |      | 2.3  | 3.2  | mA       |

|                   |        |                        |                                                                 | f⊪ = 12 MHz <sup>Note 3</sup>                                             | operation               | V <sub>DD</sub> = 3.0 V |      | 2.3  | 3.2  | mA       |

|                   |        |                        |                                                                 | fHOCO = 12 MHz <sup>Note 5</sup>                                          | Normal                  | V <sub>DD</sub> = 5.0 V |      | 1.6  | 2.0  | mA       |

|                   |        |                        |                                                                 | f⊪ = 6 MHz <sup>Note 3</sup>                                              | operation               | V <sub>DD</sub> = 3.0 V |      | 1.6  | 2.0  | mA       |

|                   |        |                        |                                                                 | fHOCO = 6 MHz Note                                                        | Normal                  | V <sub>DD</sub> = 5.0 V |      | 1.2  | 1.5  | mA       |

|                   |        |                        |                                                                 | <sup>5</sup><br>f⊮ = 3 MHz <sup>Note 3</sup>                              | operation               | V <sub>DD</sub> = 3.0 V |      | 1.2  | 1.5  | mA       |

|                   |        |                        | HS                                                              | f <sub>MX</sub> = 20 MHz <sup>Note 2</sup> ,                              | Normal                  | Square wave input       |      | 3.0  | 4.6  | mA       |

|                   |        |                        | (High-speed                                                     | V <sub>DD</sub> = 5.0 V                                                   | operation               | Resonator connection    |      | 3.2  | 4.8  | mA       |

|                   |        |                        | main) mode<br>Note 6                                            | f <sub>MX</sub> = 20 MHz <sup>Note 2</sup> ,                              | Normal                  | Square wave input       |      | 3.0  | 4.6  | mA       |

|                   |        |                        |                                                                 | V <sub>DD</sub> = 3.0 V                                                   | operation               | Resonator connection    |      | 3.2  | 4.8  | mA       |

|                   |        |                        | f <sub>MX</sub> = 10 MHz <sup>Note 2</sup> ,                    | Normal operation                                                          | Square wave input       |                         | 1.9  | 2.7  | mA   |          |

|                   |        |                        | V <sub>DD</sub> = 5.0 V                                         |                                                                           | Resonator connection    |                         | 1.9  | 2.7  | mA   |          |

|                   |        |                        | f <sub>MX</sub> = 10 MHz <sup>Note 2</sup> ,                    | Normal operation                                                          | Square wave input       |                         | 1.9  | 2.7  | mA   |          |

|                   |        |                        | V <sub>DD</sub> = 3.0 V                                         |                                                                           | Resonator connection    |                         | 1.9  | 2.7  | mA   |          |

|                   |        |                        | HS<br>(High-speed<br>main) mode<br>(PLL<br>operation)<br>Note 6 | fpll = 48 MHz,                                                            | Normal                  | V <sub>DD</sub> = 5.0 V |      | 4.0  | 5.9  | mA       |

|                   |        |                        |                                                                 |                                                                           | operation               | V <sub>DD</sub> = 3.0 V |      | 4.0  | 5.9  | mA       |

|                   |        |                        |                                                                 | f <sub>PLL</sub> = 48 MHz,<br>f <sub>CLK</sub> = 12 MHz <sup>Note 2</sup> | Normal                  | V <sub>DD</sub> = 5.0 V |      | 2.6  | 3.6  | mA       |

|                   |        |                        |                                                                 |                                                                           | operation               | V <sub>DD</sub> = 3.0 V |      | 2.6  | 3.6  | mA       |

|                   |        |                        |                                                                 | f <sub>PLL</sub> = 48 MHz,                                                | Normal                  | V <sub>DD</sub> = 5.0 V |      | 1.9  | 2.4  | mA       |

|                   |        |                        |                                                                 | fclk = 6 MHz <sup>Note 2</sup>                                            | operation               | V <sub>DD</sub> = 3.0 V |      | 1.9  | 2.4  | mA       |

|                   |        |                        | Subsystem                                                       | fsuв = 32.768 kHz                                                         | Normal                  | Resonator connection    |      | 4.1  | 4.9  | μA       |

|                   |        |                        | clock<br>operation                                              | Note 4<br>T <sub>A</sub> = −40°C                                          | operation               | Square wave input       |      | 4.2  | 5.0  | μA       |

|                   |        |                        |                                                                 | f <sub>SUB</sub> = 32.768 kHz<br>Note 4                                   | Normal                  | Square wave input       |      | 4.1  | 4.9  | μA       |

|                   |        |                        |                                                                 | $T_A = +25^{\circ}C$                                                      | operation               | Resonator connection    |      | 4.2  | 5.0  | μA       |

|                   |        |                        |                                                                 | fsuв = 32.768 kHz                                                         | Normal                  | Square wave input       |      | 4.2  | 5.5  | μA       |

|                   |        |                        | Note 4<br>T <sub>A</sub> = +50°C                                | operation                                                                 | Resonator connection    |                         | 4.3  | 5.6  | μA   |          |

|                   |        |                        |                                                                 | fsuв = 32.768 kHz                                                         | Normal                  | Square wave input       |      | 4.2  | 6.3  | μA       |

|                   |        |                        |                                                                 | Note 4<br>T <sub>A</sub> = +70°C                                          | operation               | Resonator connection    |      | 4.3  | 6.4  | μA       |

|                   |        |                        |                                                                 | fsuв = 32.768 kHz                                                         | Normal                  | Square wave input       |      | 4.8  | 7.7  | μA       |

|                   |        |                        |                                                                 | Note 4                                                                    | operation               | Resonator connection    |      | 4.0  | 7.8  | μA<br>μA |

|                   |        |                        |                                                                 | T <sub>A</sub> = +85°C                                                    |                         |                         |      |      |      | μα (     |

(Notes and Remarks are listed on the next page.)

| Parameter                                            | Symbol                         |                  | Conditions                                                                                          |  |      | MAX.  | Unit |

|------------------------------------------------------|--------------------------------|------------------|-----------------------------------------------------------------------------------------------------|--|------|-------|------|

| Low-speed on-chip<br>oscillator operating<br>current | FIL Note 1                     |                  |                                                                                                     |  | 0.20 |       | μA   |

| RTC operating current                                | IRTC<br>Notes 1, 2, 3          |                  |                                                                                                     |  | 0.02 |       | μA   |

| 12-bit interval timer operating current              | IIT Notes 1, 2, 4              |                  |                                                                                                     |  | 0.02 |       | μA   |

| Watchdog timer<br>operating current                  | IWDT<br>Notes 1, 2, 5          | f⊩ = 15 kHz      |                                                                                                     |  | 0.22 |       | μA   |

| A/D converter                                        | IADC Notes 1,                  | When conversion  | Normal mode, $AV_{REFP} = V_{DD} = 5.0 V$                                                           |  | 1.3  | 1.7   | mA   |

| operating current                                    | 6                              | at maximum speed | Low voltage mode, AV <sub>REFP</sub> = V <sub>DD</sub> = 3.0 V                                      |  | 0.5  | 0.7   | mA   |

| A/D converter reference voltage current              | IADREF <sup>Note</sup><br>1    |                  |                                                                                                     |  | 75.0 |       | μA   |

| Temperature sensor<br>operating current              | ITMPS Note 1                   |                  |                                                                                                     |  | 75.0 |       | μA   |

| LVD operating current                                | ILVD Notes 1,<br>7             |                  |                                                                                                     |  | 0.08 |       | μA   |

| Self-programming<br>operating current                | <sub>FSP</sub> Notes 1,<br>9   |                  |                                                                                                     |  | 2.00 | 12.20 | mA   |

| BGO operating current                                | I <sub>BGO</sub> Notes 1,<br>8 |                  |                                                                                                     |  | 2.00 | 12.20 | mA   |

| SNOOZE operating                                     | ISNOZ Note 1                   | ADC operation    | The mode is performed Note 10                                                                       |  | 0.50 | 1.06  | mA   |

| current                                              |                                |                  | The A/D conversion operations are performed, Low voltage mode, $AV_{REFP} = V_{DD} = 3.0 \text{ V}$ |  | 1.20 | 1.62  | mA   |

|                                                      |                                | CSI operation    |                                                                                                     |  | 0.70 | 0.84  | mA   |

# (TA = -40 to +85°C, 2.4 V $\leq$ VDD $\leq$ 5.5 V, Vss = 0 V) (1/2)

(Notes and Remarks are listed on the next page.)

| Parameter                                                | Symbol        | Conditions                                                                                             |                                       | MIN.         | TYP. | MAX. | Unit |

|----------------------------------------------------------|---------------|--------------------------------------------------------------------------------------------------------|---------------------------------------|--------------|------|------|------|

| SCKp cycle time                                          | tkCY1         | tксү1 ≥ 4/fcLк                                                                                         | $2.7~V \leq V_{\text{DD}} \leq 5.5~V$ | 167          |      |      | ns   |

|                                                          |               |                                                                                                        | $2.4~V \leq V_{\text{DD}} \leq 5.5~V$ | 250          |      |      | ns   |

| SCKp high-/low-level width                               | <b>t</b> кн1, | $4.0~V \leq V_{\text{DD}} \leq$                                                                        | 5.5 V                                 | tксү1/2 – 12 |      |      | ns   |

|                                                          | <b>t</b> ĸ∟1  | $2.7~V \leq V_{\text{DD}} \leq$                                                                        | 5.5 V                                 | tксү1/2 – 18 |      |      | ns   |

|                                                          |               | $2.4~V \leq V_{\text{DD}} \leq 5.5~V$                                                                  |                                       | tксү1/2 – 38 |      |      | ns   |

| SIp setup time (to SCKp $\uparrow$ ) <sup>Note 1</sup>   | tsik1         | $4.0~V \leq V_{\text{DD}} \leq$                                                                        | 5.5 V                                 | 44           |      |      | ns   |

|                                                          |               | $\begin{array}{c} 2.7 \ V \leq V_{DD} \leq 5.5 \ V \\ \\ 2.4 \ V \leq V_{DD} \leq 5.5 \ V \end{array}$ |                                       | 44           |      |      | ns   |

|                                                          |               |                                                                                                        |                                       | 75           |      |      | ns   |

| SIp hold time (from SCKp1) $^{\rm Note\ 2}$              | tksi1         |                                                                                                        |                                       | 19           |      |      | ns   |

| Delay time from SCKp↓ to<br>SOp output <sup>Note 3</sup> | tkso1         | C = 30 pF <sup>Note 4</sup>                                                                            |                                       |              |      | 25   | ns   |

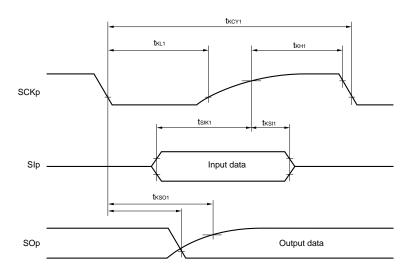

# (3) During communication at same potential (CSI mode) (master mode, SCKp... internal clock output) $(T_A = -40 \text{ to } +85^{\circ}\text{C}, 2.4 \text{ V} \le \text{V}_{DD} \le 5.5 \text{ V}, \text{V}_{SS} = 0 \text{ V})$

- **Notes 1.** When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The SIp setup time becomes "to SCKp↓" when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

- 2. When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The SIp hold time becomes "from SCKp↓" when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

- 3. When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The delay time to SOp output becomes "from SCKp<sup>↑</sup>" when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

- 4. C is the load capacitance of the SCKp and SOp output lines.

# Caution Select the normal input buffer for the SIp pin and the normal output mode for the SOp pin and SCKp pin by using port input mode register g (PIMg) and port output mode register g (POMg).

**Remarks 1.** p: CSI number (p = 00, 01), m: Unit number (m = 0), n: Channel number (n = 0, 1), g: PIM and POM numbers (g = 0, 3, 5, 7)

fMCK: Serial array unit operation clock frequency

(Operation clock to be set by the CKSmn bit of serial mode register mn (SMRmn). m: Unit number,

n: Channel number (mn = 00, 01))

**Notes 6.** The smaller maximum transfer rate derived by using fMck/6 or the following expression is the valid maximum transfer rate.

Expression for calculating the transfer rate when 2.4 V  $\leq$  V\_{DD} < 3.3 V and 1.6 V  $\leq$  V\_b  $\leq$  2.0 V

Maximum transfer rate =

$$\frac{1}{\{-C_b \times R_b \times \ln (1 - \frac{1.5}{V_b})\} \times 3}$$

[bps]

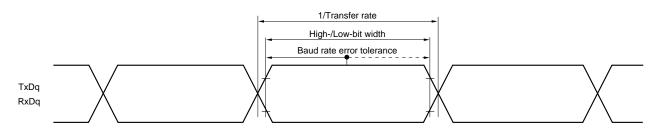

Baud rate error (theoretical value) =  $\frac{\frac{1}{\text{Transfer rate} \times 2} - \{-C_b \times R_b \times \ln(1 - \frac{1.5}{V_b})\}}{(\frac{1}{\text{Transfer rate}}) \times \text{Number of transferred bits}} \times 100 [\%]$

- \* This value is the theoretical value of the relative difference between the transmission and reception sides.

- **7.** This value as an example is calculated when the conditions described in the "Conditions" column are met. Refer to Note 6 above to calculate the maximum transfer rate under conditions of the customer.

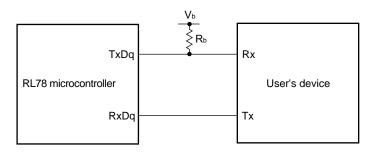

- Caution Select the TTL input buffer for the RxDq pin and the N-ch open drain output (V<sub>DD</sub> tolerance) mode for the TxDq pin by using port input mode register g (PIMg) and port output mode register g (POMg). For V<sub>H</sub> and V<sub>L</sub>, see the DC characteristics with TTL input buffer selected.

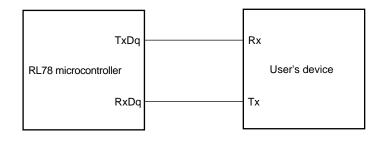

UART mode connection diagram (during communication at different potential)

#### CSI mode serial transfer timing (master mode) (during communication at different potential) (When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1.)

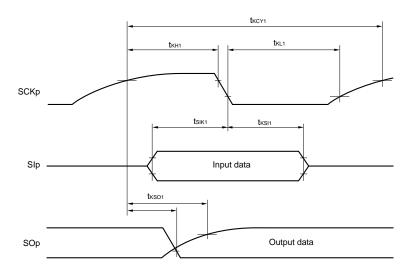

CSI mode serial transfer timing (master mode) (during communication at different potential) (When DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.)

- **Remarks 1.** p: CSI number (p = 00), m: Unit number, n: Channel number (mn = 00), g: PIM and POM number (g = 0, 3, 5, 7)

- **2.** CSI01 cannot communicate at different potential. Use other CSI for communication at different potential.

# (9) Communication at different potential (1.8 V, 2.5 V, 3 V) (CSI mode) (slave mode, SCKp... external clock input)

| Parameter                                       | Symbol        | C                                                                                 | Conditions                                                             | MIN.             | TYP. | MAX.     | Unit |

|-------------------------------------------------|---------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------|------------------|------|----------|------|

| SCKp cycle time Note 1                          | tксү2         | $4.0 V \le V_{DD} \le 5.5 V$ ,                                                    | 20 MHz < $f_{MCK} \leq$ 24 MHz                                         | 12/ <b>f</b> мск |      |          | ns   |

|                                                 |               | $2.7  V \le V_b \le 4.0  V$                                                       | 8 MHz < fмск ≤20 MHz                                                   | 10/ <b>f</b> мск |      |          | ns   |

|                                                 |               |                                                                                   | 4 MHz < fмск ≤ 8 MHz                                                   | 8/fмск           |      |          | ns   |

|                                                 |               |                                                                                   | fмск ≤4 MHz                                                            | 6/fмск           |      |          | ns   |

|                                                 |               | $2.7 V \le V_{DD} < 4.0 V$ ,                                                      | 20 MHz < fмск ≤24 MHz                                                  | 16/ <b>f</b> мск |      |          | ns   |

|                                                 |               | $2.3  V \le V_b \le 2.7  V$                                                       | 16 MHz < fмск ≤ 20 MHz                                                 | 14/ <b>f</b> мск |      |          | ns   |

|                                                 |               |                                                                                   | 8 MHz < fмск ≤ 16 MHz                                                  | 12/ <b>f</b> мск |      |          | ns   |

|                                                 |               |                                                                                   | 4 MHz < fмск ≤8 MHz                                                    | <b>8/f</b> мск   |      |          | ns   |

|                                                 |               |                                                                                   | fмск ≤4 MHz                                                            | <b>6/f</b> мск   |      |          | ns   |

|                                                 |               | $2.4 V \le V_{DD} < 3.3 V$ ,                                                      | 20 MHz < fмск ≤24 MHz                                                  | <b>36/f</b> мск  |      |          | ns   |

|                                                 |               | $1.6 V \le V_b \le 2.0 V^{Note}$                                                  | 16 MHz < fмск ≤ 20 MHz                                                 | <b>32/f</b> мск  |      |          | ns   |

|                                                 |               | 2                                                                                 | 8 MHz < fмск ≤ 16 MHz                                                  | <b>26/f</b> мск  |      |          | ns   |

|                                                 |               |                                                                                   | $4 \text{ MHz} < f_{MCK} \le 8 \text{ MHz}$                            | 16/ <b>f</b> мск |      |          | ns   |

|                                                 |               |                                                                                   | fмск ≤4 MHz                                                            | 10/ <b>f</b> мск |      |          | ns   |

| SCKp high-/low-level width                      | tкн2,<br>tкL2 | $4.0 \ V \leq V_{DD} \leq 5.5 \ V, \ 2.7 \ V \leq V_b \leq 4.0 \ V$               |                                                                        | tксү2/2 –<br>12  |      |          | ns   |

|                                                 |               | $2.7 \text{ V} \le \text{V}_{\text{DD}} < 4.0 \text{ V}$                          | $V_{,} 2.3 \text{ V} \leq V_{b} \leq 2.7 \text{ V}$                    | tксү2/2 –<br>18  |      |          | ns   |

|                                                 |               | $2.4~V \leq V_{\text{DD}}$ < 3.3 V, 1.6 V $\leq V_{b} \leq 2.0~V^{\text{Note 2}}$ |                                                                        | tксү2/2 –<br>50  |      |          | ns   |

| SIp setup time<br>(to SCKp↑) <sup>Note 3</sup>  | tsık2         | $4.0 \text{ V} \le \text{V}_{\text{DD}} \le 5.5 \text{ V}$                        | $V_{\rm b}, 2.7~V \le V_{\rm b} \le 4.0~V$                             | 1/fмск +<br>20   |      |          | ns   |

|                                                 |               | $2.7 \text{ V} \le \text{V}_{\text{DD}} < 4.0 \text{ V}$                          | $V_{\rm r}, 2.3 \ V \le V_{\rm b} \le 2.7 \ V_{\rm b}$                 | 1/fмск +<br>20   |      |          | ns   |

|                                                 |               | $2.4 \text{ V} \le \text{V}_{\text{DD}} < 3.3 \text{ V}$                          | $V_{\rm b}$ 1.6 V $\leq$ V <sub>b</sub> $\leq$ 2.0 V <sup>Note 2</sup> | 1/fмск +<br>30   |      |          | ns   |

| SIp hold time<br>(from SCKp↑) <sup>Note 4</sup> | tksı2         |                                                                                   |                                                                        | 1/fмск + 31      |      |          | ns   |

| Delay time from SCKp↓ to                        | tĸso2         | $4.0~V \le V_{\text{DD}} \le 5.5~V$                                               | $V, 2.7 V \le V_b \le 4.0 V,$                                          |                  |      | 2/fмск + | ns   |

| SOp output Note 5                               |               | C <sub>b</sub> = 30 pF, R <sub>b</sub> = 1.                                       | 4 kΩ                                                                   |                  |      | 120      |      |

|                                                 |               | $2.7 \text{ V} \le \text{V}_{\text{DD}} < 4.0 \text{ V}$                          | $V_{\rm r}, 2.3 \ V \le V_{\rm b} \le 2.7 \ V_{\rm r},$                |                  |      | 2/fмск + | ns   |

|                                                 |               | C <sub>b</sub> = 30 pF, R <sub>b</sub> = 2.                                       | 7 kΩ                                                                   |                  |      | 214      |      |

|                                                 |               | $2.4 \text{ V} \le \text{V}_{\text{DD}} < 3.3 \text{ V}$                          | ', 1.6 V $\leq$ V <sub>b</sub> $\leq$ 2.0 V <sup>Note 2</sup> ,        |                  |      | 2/fмск + | ns   |

|                                                 |               | C <sub>b</sub> = 30 pF, R <sub>b</sub> = 5.                                       | 5 kΩ                                                                   |                  |      | 573      |      |

#### Notes 1. Transfer rate in the SNOOZE mode : MAX. 1 Mbps

- **2.** Use it with  $V_{DD} \ge V_b$ .

- 3. When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The SIp setup time becomes "to SCKp↓" when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

- 4. When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The SIp hold time becomes "from SCKp↓" when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

- 5. When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The delay time to SOp output becomes "from SCKp<sup>↑</sup>" when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

(Caution and Remarks are listed on the next page.)

RENESAS

# 2.6 Analog Characteristics

# 2.6.1 A/D converter characteristics

Classification of A/D converter characteristics

| Input channel                                                      | Reference Voltage                                                                              |                                                                        |                                                                                  |  |  |  |

|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------|--|--|--|

|                                                                    | Reference voltage (+) =<br>AV <sub>REFP</sub><br>Reference voltage (–) =<br>AV <sub>REFM</sub> | Reference voltage (+) = V <sub>DD</sub><br>Reference voltage (-) = Vss | Reference voltage (+) =<br>V <sub>BGR</sub><br>Reference voltage (–) =<br>AVREFM |  |  |  |

| ANI0 to ANI7                                                       | Refer to 2.6.1 (1).                                                                            | Refer to 2.6.1 (3).                                                    | Refer to 2.6.1 (4).                                                              |  |  |  |

| ANI16, ANI17, ANI19                                                | Refer to 2.6.1 (2).                                                                            |                                                                        |                                                                                  |  |  |  |

| Internal reference voltage<br>Temperature sensor output<br>voltage | Refer to <b>2.6.1 (1)</b> .                                                                    |                                                                        | _                                                                                |  |  |  |

# (1) When AV<sub>REF (+)</sub> = AV<sub>REFP</sub>/ANI0 (ADREFP1 = 0, ADREFP0 = 1), reference voltage (-) = AV<sub>REFM</sub>/ANI1 (ADREFM = 1), target pin : ANI2 to ANI7, internal reference voltage, and temperature sensor output voltage

| $(T_A = -40 \text{ to } +85^{\circ}\text{C}, 2.4 \text{ V} \le \text{AV}_{\text{REFP}} \le \text{V}_{\text{DD}} \le 5.5 \text{ V}, \text{ V}_{\text{SS}} = 0 \text{ V}, \text{ Reference voltage (+) = AV}_{\text{REFP}}, \text{ Reference voltage (-)} \ge 10^{\circ}\text{C}, 1$ |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| $= AV_{REFM} = 0 V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Parameter                                  | Symbol | Cond                                                                                              | itions                                                  | MIN.                               | TYP. | MAX.   | Unit |

|--------------------------------------------|--------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------|------------------------------------|------|--------|------|

| Resolution                                 | Res    |                                                                                                   |                                                         | 8                                  |      | 10     | bit  |

| Overall error <sup>Note 1</sup>            | AINL   | 10-bit resolution<br>AV <sub>REFP</sub> = V <sub>DD</sub> <sup>Note 3</sup>                       | $2.4 \text{ V} \leq \text{VDD} \leq 5.5 \text{ V}$      |                                    | 1.2  | ±3.5   | LSB  |

| Conversion time                            | tconv  | 10-bit resolution                                                                                 | $3.6~\text{V} \leq \text{V}\text{DD} \leq 5.5~\text{V}$ | 2.125                              |      | 39     | μs   |

|                                            |        | Target pin: ANI2 to<br>ANI7                                                                       | $2.7~V \leq V_{DD} \leq 5.5~V$                          | 3.1875                             |      | 39     | μs   |

|                                            |        |                                                                                                   | $2.4~V \leq V_{DD} \leq 5.5~V$                          | 17                                 |      | 39     | μs   |

|                                            |        | 10-bit resolution                                                                                 | $3.6~V \leq V_{DD} \leq 5.5~V$                          | 2.375                              |      | 39     | μs   |

|                                            |        | Target pin: Internal                                                                              | $2.7~V \leq V \text{DD} \leq 5.5~V$                     | 3.5625                             |      | 39     | μs   |

|                                            |        | reference voltage,<br>and temperature<br>sensor output voltage<br>(HS (high-speed<br>main) mode)  | $2.4~V \leq V \text{DD} \leq 5.5~V$                     | 17                                 |      | 39     | μs   |

| Zero-scale error <sup>Notes 1, 2</sup>     | EZS    | 10-bit resolution<br>AV <sub>REFP</sub> = V <sub>DD</sub> <sup>Note 3</sup>                       | $2.4 \text{ V} \leq \text{VDD} \leq 5.5 \text{ V}$      |                                    |      | ±0.25  | %FSR |

| Full-scale error <sup>Notes 1, 2</sup>     | EFS    | 10-bit resolution<br>AV <sub>REFP</sub> = V <sub>DD</sub> <sup>Note 3</sup>                       | $2.4 \text{ V} \leq \text{VDD} \leq 5.5 \text{ V}$      |                                    |      | ±0.25  | %FSR |

| Integral linearity error <sup>Note 1</sup> | ILE    | 10-bit resolution<br>AV <sub>REFP</sub> = V <sub>DD</sub> <sup>Note 3</sup>                       | $2.4 \text{ V} \leq \text{VDD} \leq 5.5 \text{ V}$      |                                    |      | ±2.5   | LSB  |

| Differential linearity error Note 1        | DLE    | 10-bit resolution<br>AV <sub>REFP</sub> = V <sub>DD</sub> <sup>Note 3</sup>                       | $2.4~V \leq V \text{DD} \leq 5.5~V$                     |                                    |      | ±1.5   | LSB  |

| Analog input voltage                       | VAIN   | ANI2 to ANI7                                                                                      | ·                                                       | 0                                  |      | AVREFP | V    |

|                                            |        | Internal reference voltage (2.4 V $\leq$ V <sub>DD</sub> $\leq$ 5.5 V, HS (high-speed main) mode) |                                                         | V <sub>BGR</sub> <sup>Note 4</sup> |      |        | V    |

|                                            |        | Temperature sensor output voltage (2.4 V $\leq$ VDD $\leq$ 5.5 V, HS (high-speed main) mode)      |                                                         | V <sub>TMPS25</sub> Note 4         |      |        | V    |

(**Notes** are listed on the next page.)

#### 3.2.3 PLL oscillator characteristics

#### (TA = -40 to +105°C, 2.4 V $\leq$ VDD $\leq$ 5.5 V, Vss = 0 V)

| Oscillators               | Parameters | Conditions                                                                                                  | MIN.  | TYP.  | MAX.  | Unit |

|---------------------------|------------|-------------------------------------------------------------------------------------------------------------|-------|-------|-------|------|

| PLL input frequency Note  | fpllin     | High-speed system clock                                                                                     | 6.00  |       | 16.00 | MHz  |

| PLL output frequency Note | fpll       |                                                                                                             |       | 48.00 |       | MHz  |

| Lock up time              |            | From PLL output enable to stabilization of the<br>output frequency                                          | 40.00 |       |       | μs   |

| Interval time             |            | From PLL stop to PLL re-operation setteing<br>Wait time                                                     | 4.00  |       |       | μs   |

| Setting wait time         |            | From after PLL input clock stabilization and PLL<br>setting is fixed to start setting<br>Wait time required | 1.00  |       |       | μs   |

Note Indicates only oscillator characteristics. Refer to AC Characteristics for instruction execution time.

### 3.3 DC Characteristics

#### 3.3.1 Pin characteristics

#### $(T_A = -40 \text{ to } +105^{\circ}\text{C}, 2.4 \text{ V} \le \text{V}_{DD} \le 5.5 \text{ V}, \text{V}_{SS} = 0 \text{ V})$

| Items                                     | Symbol | Conditions                                                                                         |                                                            | MIN. | TYP. | MAX.                      | Unit |

|-------------------------------------------|--------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------|------|------|---------------------------|------|

| Output current,<br>high <sup>Note 1</sup> | Іон1   | Per pin for P00, P01, P14 to P17,<br>P30, P31, P40, P41, P50, P51, P70 to<br>P75, P120, P130, P140 | $2.4~\text{V} \leq \text{V}_{\text{DD}} \leq 5.5~\text{V}$ |      |      | -3.0 <sup>Note</sup><br>2 | mA   |

|                                           |        | Total of P00, P01, P40, P41, P120,                                                                 | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$                      |      |      | -30.0                     | mA   |

|                                           |        | P130, P140                                                                                         | $2.7~V \leq V_{\text{DD}} < 4.0~V$                         |      |      | -10.0                     | mA   |

|                                           |        | (When duty $\leq$ 70% <sup>Note 3</sup> )                                                          | $2.4~V \leq V_{\text{DD}} < 2.7~V$                         |      |      | -5.0                      | mA   |

|                                           |        | Total of P14 to P17, P30, P31, P50, P51, P70 to P75 (When duty $\leq$ 70% <sup>Note 3</sup> )      | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$                      |      |      | -30.0                     | mA   |

|                                           |        |                                                                                                    | $2.7~V \leq V_{\text{DD}} < 4.0~V$                         |      |      | -19.0                     | mA   |

|                                           |        |                                                                                                    | $2.4~V \leq V_{\text{DD}} < 2.7~V$                         |      |      | -10.0                     | mA   |

|                                           |        | Total of all pins<br>(When duty ≤ 70% <sup>Note 3</sup> )                                          | $2.4~V \leq V_{\text{DD}} \leq 5.5~V$                      |      |      | -60.0                     | mA   |

| Іон2                                      | Іон2   | Per pin for P20 to P27                                                                             | $2.4~V \leq V_{\text{DD}} \leq 5.5~V$                      |      |      | -0.1 <sup>Note</sup><br>2 | mA   |

|                                           |        | Total of all pins<br>(When duty ≤ 70% <sup>Note 3</sup> )                                          | $2.4~V \le V_{\text{DD}} \le 5.5~V$                        |      |      | -1.5                      | mA   |

- **Notes 1**. Value of current at which the device operation is guaranteed even if the current flows from the V<sub>DD</sub> pin to an output pin.

- 2. However, do not exceed the total current value.

- **3.** Specification under conditions where the duty factor  $\leq$  70%.

The output current value that has changed to the duty factor > 70% the duty ratio can be calculated with the following expression (when changing the duty ratio to n%).

- Total output current of pins =  $(I_{OH} \times 0.7)/(n \times 0.01)$

- <Example> Where n = 80% and IoH = -10.0 mA

Total output current of pins =  $(-10.0 \times 0.7)/(80 \times 0.01) \approx -8.7$  mA

However, the current that is allowed to flow into one pin does not vary depending on the duty factor. A current higher than the absolute maximum rating must not flow into one pin.

#### Caution P00, P01, P30, and P74 do not output high level in N-ch open-drain mode.

**Remark** Unless specified otherwise, the characteristics of alternate-function pins are the same as those of the port pins.

| Items                                    | Symbol | Conditions                                                                                         |                                                           | MIN. | TYP.                                                      | MAX.                                         | Unit |  |      |    |

|------------------------------------------|--------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------|------|-----------------------------------------------------------|----------------------------------------------|------|--|------|----|

| Output current,<br>low <sup>Note 1</sup> | Iol1   | Per pin for P00, P01, P14 to P17,<br>P30, P31, P40, P41, P50, P51,<br>P70 to P75, P120, P130, P140 | $2.4V \leq V_{\text{DD}} \leq 5.5 \text{ V}$              |      |                                                           | 8.5 <sup>Note 2</sup>                        | mA   |  |      |    |

|                                          |        | Per pin for P60 to P63                                                                             | $2.4V \leq V_{\text{DD}} \leq 5.5~V$                      |      |                                                           | 15.0 Note 2                                  | mA   |  |      |    |

|                                          |        | Total of P00, P01, P40, P41, P120,                                                                 | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$                     |      |                                                           | 40.0                                         | mA   |  |      |    |

|                                          |        | P130, P140<br>(When duty ≤ 70% <sup>Note 3</sup> )                                                 | $2.7~V \leq V_{\text{DD}} < 4.0~V$                        |      |                                                           | 15.0                                         | mA   |  |      |    |

|                                          |        |                                                                                                    | $2.4 \text{ V} \leq \text{V}_{\text{DD}} < 2.7 \text{ V}$ |      |                                                           | 9.0                                          | mA   |  |      |    |

|                                          |        | Total of P14 to P17, P30, P31, P50,                                                                | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$                     |      |                                                           | 40.0                                         | mA   |  |      |    |

|                                          |        | P51, P60 to P63, P70 to P75                                                                        | $2.7~V \leq V_{\text{DD}} < 4.0~V$                        |      |                                                           | 35.0                                         | mA   |  |      |    |

|                                          |        | (When duty $\leq 70\%$ <sup>Note 3</sup> )                                                         | $2.4 \text{ V} \leq \text{V}_{\text{DD}} < 2.7 \text{ V}$ |      |                                                           | 20.0                                         | mA   |  |      |    |

|                                          |        |                                                                                                    |                                                           |      | Total of all pins<br>(When duty ≤ 70% <sup>Note 3</sup> ) | $2.4V \leq V_{\text{DD}} \leq 5.5 \text{ V}$ |      |  | 80.0 | mA |

|                                          | IOL2   | Per pin for P20 to P27                                                                             | $2.4V \leq V_{\text{DD}} \leq 5.5~V$                      |      |                                                           | 0.4 Note 2                                   | mA   |  |      |    |

|                                          |        | Total of all pins<br>(When duty ≤ 70% <sup>Note 3</sup> )                                          | $2.4V \leq V_{\text{DD}} \leq 5.5 \; V$                   |      |                                                           | 5.0                                          | mA   |  |      |    |

#### $(T_A = -40 \text{ to } +105^{\circ}\text{C}, 2.4 \text{ V} \le \text{V}_{DD} \le 5.5 \text{ V}, \text{V}_{SS} = 0 \text{ V})$

- **Notes 1**. Value of current at which the device operation is guaranteed even if the current flows from an output pin to the Vss pin.

- 2. However, do not exceed the total current value.

- **3.** Specification under conditions where the duty factor  $\leq$  70%.

- The output current value that has changed to the duty factor > 70% the duty ratio can be calculated with the following expression (when changing the duty ratio to n%).

- Total output current of pins =  $(I_{OL} \times 0.7)/(n \times 0.01)$

- <Example> Where n = 80% and IoL = 10.0 mA

Total output current of pins =  $(10.0 \times 0.7)/(80 \times 0.01) \approx 8.7$  mA