Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                      |

|----------------------------|---------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                             |

| Core Size                  | 32-Bit Single-Core                                                                          |

| Speed                      | 144MHz                                                                                      |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, LINbus, MMC/SD, SPI, UART/USART, USB OTG, USIC |

| Peripherals                | DMA, I <sup>2</sup> S, LED, POR, Touch-Sense, WDT                                           |

| Number of I/O              | 75                                                                                          |

| Program Memory Size        | 1.5MB (1.5M × 8)                                                                            |

| Program Memory Type        | FLASH                                                                                       |

| EEPROM Size                | -                                                                                           |

| RAM Size                   | 276K x 8                                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 3.63V                                                                               |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                       |

| Oscillator Type            | External                                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                           |

| Mounting Type              | Surface Mount                                                                               |

| Package / Case             | 100-LQFP Exposed Pad                                                                        |

| Supplier Device Package    | PG-LQFP-100-25                                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xmc4700f100f1536aaxqma1          |

|                            |                                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### About this Document

# About this Document

This Data Sheet is addressed to embedded hardware and software developers. It provides the reader with detailed descriptions about the ordering designations, available features, electrical and physical characteristics of the XMC4[78]00 series devices.

The document describes the characteristics of a superset of the XMC4[78]00 series devices. For simplicity, the various device types are referred to by the collective term XMC4[78]00 throughout this manual.

#### XMC4000 Family User Documentation

The set of user documentation includes:

- Reference Manual

- decribes the functionality of the superset of devices.

- Data Sheets

- list the complete ordering designations, available features and electrical characteristics of derivative devices.

- Errata Sheets

- list deviations from the specifications given in the related Reference Manual or Data Sheets. Errata Sheets are provided for the superset of devices.

# Attention: Please consult all parts of the documentation set to attain consolidated knowledge about your device.

Application related guidance is provided by Users Guides and Application Notes.

Please refer to http://www.infineon.com/xmc4000 to get access to the latest versions of those documents.

#### **Summary of Features**

# 1 Summary of Features

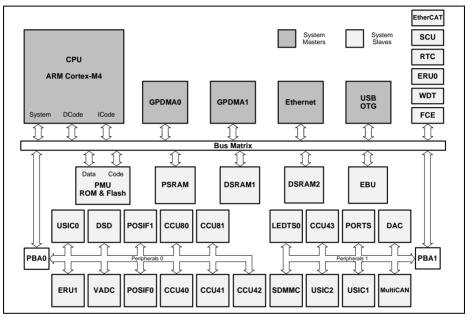

The XMC4[78]00 devices are members of the XMC4000 Family of microcontrollers based on the ARM Cortex-M4 processor core. The XMC4000 is a family of high performance and energy efficient microcontrollers optimized for Industrial Connectivity, Industrial Control, Power Conversion, Sense & Control.

Figure 1 System Block Diagram

#### **CPU Subsystem**

- CPU Core

- High Performance 32-bit ARM Cortex-M4 CPU

- 16-bit and 32-bit Thumb2 instruction set

- DSP/MAC instructions

- System timer (SysTick) for Operating System support

- Floating Point Unit

- Memory Protection Unit

- Nested Vectored Interrupt Controller

- General Purpose DMA with up-to channels

- Event Request Unit (ERU) for programmable processing of external and internal service requests

- Flexible CRC Engine (FCE) for multiple bit error detection

Data Sheet

#### **Summary of Features**

| Derivative <sup>1)</sup> | LED<br>TS<br>Intf. | SD<br>MMC<br>Intf. | EBU<br>Intf. <sup>2)</sup> | ETH<br>Intf.<br>3) | ECAT<br>Slave<br>Intf. | USB<br>Intf. | USIC<br>Chan. | MultiCAN<br>Nodes,<br>MO |

|--------------------------|--------------------|--------------------|----------------------------|--------------------|------------------------|--------------|---------------|--------------------------|

| XMC4800-E196x2048        | 1                  | 1                  | SDM                        | MR                 | 2 x<br>MII             | 1            | 3 x 2         | N[05]<br>MO[0255]        |

| XMC4800-F144x2048        | 1                  | 1                  | SDM                        | MR                 | 2 x<br>MII             | 1            | 3 x 2         | N[05]<br>MO[0255]        |

| XMC4800-F100x2048        | 1                  | 1                  | M16                        | R                  | 2 x<br>MII             | 1            | 3 x 2         | N[05]<br>MO[0255]        |

| XMC4800-E196x1536        | 1                  | 1                  | SDM                        | MR                 | 2 x<br>MII             | 1            | 3 x 2         | N[05]<br>MO[0255]        |

| XMC4800-F144x1536        | 1                  | 1                  | SDM                        | MR                 | 2 x<br>MII             | 1            | 3 x 2         | N[05]<br>MO[0255]        |

| XMC4800-F100x1536        | 1                  | 1                  | M16                        | R                  | 2 x<br>MII             | 1            | 3 x 2         | N[05]<br>MO[0255]        |

| XMC4800-E196x1024        | 1                  | 1                  | SDM                        | MR                 | 2 x<br>MII             | 1            | 3 x 2         | N[05]<br>MO[0255]        |

| XMC4800-F144x1024        | 1                  | 1                  | SDM                        | MR                 | 2 x<br>MII             | 1            | 3 x 2         | N[05]<br>MO[0255]        |

| XMC4800-F100x1024        | 1                  | 1                  | M16                        | R                  | 2 x<br>MII             | 1            | 3 x 2         | N[05]<br>MO[0255]        |

# Table 2Features of XMC4[78]00 Device Types (cont'd)

1) x is a placeholder for the supported temperature range.

2) Memory types supported S=SDRAM, D=DEMUX, M=MUX 16-bit and 32-bit, M16=MUX 16-bit

3) Supported interfaces, M=MII, R=RMII.

| Table 3 | Features of XMC4[78]00 Device Types |

|---------|-------------------------------------|

|---------|-------------------------------------|

| Derivative <sup>1)</sup> | ADC<br>Chan. | DSD<br>Chan. | DAC<br>Chan. | CCU4<br>Slice | CCU8<br>Slice | POSIF<br>Intf. |

|--------------------------|--------------|--------------|--------------|---------------|---------------|----------------|

| XMC4700-E196x2048        | 32           | 4            | 2            | 4 x 4         | 2 x 4         | 2              |

| XMC4700-F144x2048        | 32           | 4            | 2            | 4 x 4         | 2 x 4         | 2              |

| XMC4700-F100x2048        | 24           | 4            | 2            | 4 x 4         | 2 x 4         | 2              |

| XMC4700-E196x1536        | 32           | 4            | 2            | 4 x 4         | 2 x 4         | 2              |

| XMC4700-F144x1536        | 32           | 4            | 2            | 4 x 4         | 2 x 4         | 2              |

| XMC4700-F100x1536        | 24           | 4            | 2            | 4 x 4         | 2 x 4         | 2              |

| XMC4800-E196x2048        | 32           | 4            | 2            | 4 x 4         | 2 x 4         | 2              |

|                          |              |              |              |               |               |                |

# XMC4700 / XMC4800 XMC4000 Family

#### **General Device Information**

| Table 10 | Package Pi | n Mapping | (cont'd) |          |                                                                             |

|----------|------------|-----------|----------|----------|-----------------------------------------------------------------------------|

| Function | LFBGA-196  | LQFP-144  | LQFP-100 | Pad Type | Notes                                                                       |

| P0.11    | G5         | 139       | 95       | A1+      |                                                                             |

| P0.12    | F5         | 138       | 94       | A1+      |                                                                             |

| P0.13    | E5         | 137       | -        | A1+      |                                                                             |

| P0.14    | G6         | 136       | -        | A1+      |                                                                             |

| P0.15    | E6         | 135       | -        | A1+      |                                                                             |

| P1.0     | F9         | 112       | 79       | A1+      |                                                                             |

| P1.1     | G9         | 111       | 78       | A1+      |                                                                             |

| P1.2     | E11        | 110       | 77       | A2       |                                                                             |

| P1.3     | E12        | 109       | 76       | A2       |                                                                             |

| P1.4     | E10        | 108       | 75       | A1+      |                                                                             |

| P1.5     | F10        | 107       | 74       | A1+      |                                                                             |

| P1.6     | D9         | 116       | 83       | A2       |                                                                             |

| P1.7     | D10        | 115       | 82       | A2       |                                                                             |

| P1.8     | C10        | 114       | 81       | A2       |                                                                             |

| P1.9     | D11        | 113       | 80       | A2       |                                                                             |

| P1.10    | F12        | 106       | 73       | A1+      |                                                                             |

| P1.11    | F11        | 105       | 72       | A1+      |                                                                             |

| P1.12    | G11        | 104       | 71       | A2       |                                                                             |

| P1.13    | G12        | 103       | 70       | A2       |                                                                             |

| P1.14    | G10        | 102       | 69       | A2       |                                                                             |

| P1.15    | J12        | 94        | 68       | A2       |                                                                             |

| P2.0     | L11        | 74        | 52       | A2       |                                                                             |

| P2.1     | M12        | 73        | 51       | A2       | After a system reset, via<br>HWSEL this pin selects<br>the DB.TDO function. |

| P2.2     | M11        | 72        | 50       | A2       |                                                                             |

| P2.3     | N11        | 71        | 49       | A2       |                                                                             |

| P2.4     | N10        | 70        | 48       | A2       |                                                                             |

| P2.5     | P10        | 69        | 47       | A2       |                                                                             |

| P2.6     | L9         | 76        | 54       | A1+      |                                                                             |

| P2.7     | M9         | 75        | 53       | A1+      |                                                                             |

| P2.8     | N9         | 68        | 46       | A2       |                                                                             |

| P2.9     | P9         | 67        | 45       | A2       |                                                                             |

#### Table 12 Port I/O Functions (cont'd)

| Function  | Outputs |      |      |      | Inputs |      |      |      |               |               |               |       |               |               |       |       |

|-----------|---------|------|------|------|--------|------|------|------|---------------|---------------|---------------|-------|---------------|---------------|-------|-------|

|           | ALT1    | ALT2 | ALT3 | ALT4 | HWO0   | HWO1 | HWIO | HWI1 | Input         | Input         | Input         | Input | Input         | Input         | Input | Input |

| XTAL1     |         |      |      |      |        |      |      |      | U0C0.<br>DX0F | U0C1.<br>DX0F | U1C0.<br>DX0F |       | U2C0.<br>DX0F | U2C1.<br>DX0F |       |       |

| XTAL2     |         |      |      |      |        |      |      |      |               |               |               |       |               |               |       |       |

| RTC_XTAL1 |         |      |      |      |        |      |      |      |               |               | ERU0.<br>1B1  |       |               |               |       |       |

| RTC_XTAL2 |         |      |      |      |        |      |      |      |               |               |               |       |               |               |       |       |

Data Sheet

Infineon

XMC4700 / XMC4800 XMC4000 Family

# 3 Electrical Parameters

Attention: All parameters in this chapter are preliminary target values and may change based on characterization results.

## 3.1 General Parameters

#### 3.1.1 Parameter Interpretation

The parameters listed in this section partly represent the characteristics of the XMC4[78]00 and partly its requirements on the system. To aid interpreting the parameters easily when evaluating them for a design, they are marked with a two-letter abbreviation in column "Symbol":

• CC

Such parameters indicate **C**ontroller **C**haracteristics, which are a distinctive feature of the XMC4[78]00 and must be regarded for system design.

SR

Such parameters indicate **S**ystem Requirements, which must be provided by the application system in which the XMC4[78]00 is designed in.

# XMC4700 / XMC4800 XMC4000 Family

#### **Electrical Parameters**

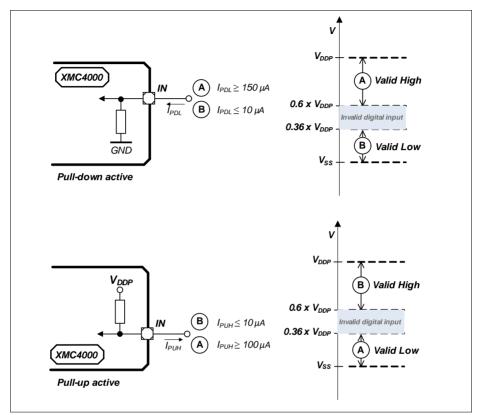

#### Figure 13 Pull Device Input Characteristics

Figure 13 visualizes the input characteristics with an active internal pull device:

- in the cases "A" the internal pull device is overridden by a strong external driver;

- in the cases "B" the internal pull device defines the input logical state against a weak external load.

| Parameter                                                                       | Symbol                                                 |      | Value | S         | Unit | Note /                                                                                    |  |

|---------------------------------------------------------------------------------|--------------------------------------------------------|------|-------|-----------|------|-------------------------------------------------------------------------------------------|--|

|                                                                                 | -                                                      | Min. | Тур.  | Typ. Max. |      | Test Condition                                                                            |  |

| Total Unadjusted Error                                                          | TUE CC                                                 | -4   | -     | 4         | LSB  | 12-bit resolution;                                                                        |  |

| Differential Non-Linearity<br>Error <sup>8)</sup>                               | EA <sub>DNL</sub><br>CC                                | -3   | -     | 3         | LSB  | $V_{\text{DDA}} = 3.3 \text{ V};$ $V_{\text{AREF}} = V_{\text{DDA}}^{7)}$                 |  |

| Gain Error <sup>8)</sup>                                                        | EA <sub>GAIN</sub><br>CC                               | -4   | -     | 4         | LSB  |                                                                                           |  |

| Integral Non-Linearity <sup>8)</sup>                                            | EA <sub>INL</sub> CC                                   | -3   | -     | 3         | LSB  | -                                                                                         |  |

| Offset Error <sup>8)</sup>                                                      | EA <sub>OFF</sub><br>CC                                | -4   | -     | 4         | LSB  |                                                                                           |  |

| Worst case ADC $V_{\text{DDA}}$<br>power supply current per<br>active converter | I <sub>DDAA</sub><br>CC                                | _    | 1.5   | 2         | mA   | during conversion<br>$V_{\text{DDP}} = 3.6 \text{ V},$<br>$T_{\text{J}} = 150 \text{ °C}$ |  |

| Charge consumption on $V_{\text{AREF}}$ per conversion <sup>5)</sup>            | $\begin{array}{c} Q_{\rm CONV} \\ { m CC} \end{array}$ | -    | 30    | -         | рС   | $0 V \le V_{AREF} \le V_{DDA}^{9)}$                                                       |  |

| ON resistance of the analog input path                                          | R <sub>AIN</sub> CC                                    | -    | 600   | 1 200     | Ohm  |                                                                                           |  |

| ON resistance for the ADC test (pull down for AIN7)                             | R <sub>AIN7T</sub><br>CC                               | 180  | 550   | 900       | Ohm  |                                                                                           |  |

| Resistance of the reference voltage input path                                  | R <sub>AREF</sub><br>CC                                | _    | 700   | 1 700     | Ohm  |                                                                                           |  |

#### Table 25 VADC Parameters (Operating Conditions apply)

1) A running conversion may become imprecise in case the normal conditions are violated (voltage overshoot).

If the analog reference voltage is below V<sub>DDA</sub>, then the ADC converter errors increase. If the reference voltage is reduced by the factor k (k<1), TUE, DNL, INL, Gain, and Offset errors increase also by the factor 1/k.</li>

- 3) The leakage current definition is a continuous function, as shown in figure ADCx Analog Inputs Leakage. The numerical values defined determine the characteristic points of the given continuous linear approximation they do not define step function (see Figure 16).

- 4) The sampling capacity of the conversion C-network is pre-charged to V<sub>AREF</sub>/2 before the sampling moment. Because of the parasitic elements, the voltage measured at AINx can deviate from V<sub>AREF</sub>/2.

- 5) Applies to AINx, when used as alternate reference input.

- 6) This represents an equivalent switched capacitance. This capacitance is not switched to the reference voltage at once. Instead, smaller capacitances are successively switched to the reference voltage.

- For 10-bit conversions, the errors are reduced to 1/4; for 8-bit conversions, the errors are reduced to 1/16. Never less than ±1 LSB.

- 8) The sum of DNL/INL/GAIN/OFF errors does not exceed the related total unadjusted error TUE.

- 9) The resulting current for a conversion can be calculated with  $I_{AREF} = Q_{CONV} / t_c$ . The fastest 12-bit post-calibrated conversion of  $t_c = 459$  ns results in a typical average current of  $I_{AREF} = 65.4 \mu A$ .

55

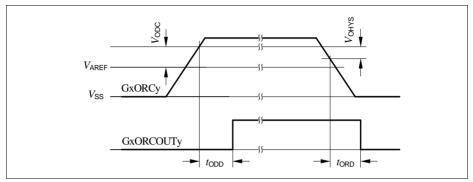

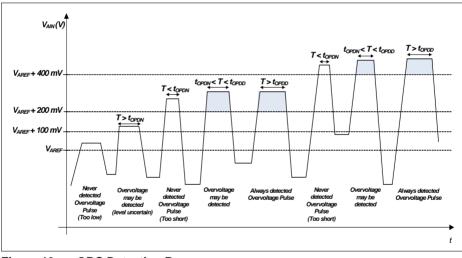

# 3.2.4 Out-of-Range Comparator (ORC)

The Out-of-Range Comparator (ORC) triggers on analog input voltages ( $V_{AIN}$ ) above the analog reference<sup>1</sup> ( $V_{AREF}$ ) on selected input pins (GxORCy) and generates a service request trigger (GxORCOUTy).

Note: These parameters are not subject to production test, but verified by design and/or characterization.

The parameters in Table 28 apply for the maximum reference voltage  $V_{\text{AREF}} = V_{\text{DDA}} + 50 \text{ mV}.$

|                                                |                   |    | · ·  | •      |                  |      |                                                       |  |

|------------------------------------------------|-------------------|----|------|--------|------------------|------|-------------------------------------------------------|--|

| Parameter                                      | Symbol            |    |      | Values | 5                | Unit | Note / Test Condition                                 |  |

|                                                |                   |    | Min. | Тур.   | Max.             | 1    |                                                       |  |

| DC Switching Level                             | $V_{\text{ODC}}$  | CC | 100  | 125    | 210              | mV   | $V_{\text{AIN}} \ge V_{\text{AREF}} + V_{\text{ODC}}$ |  |

| Hysteresis                                     | VOHYS             | CC | 50   | -      | V <sub>ODC</sub> | mV   |                                                       |  |

| Detection Delay of a persistent<br>Overvoltage | t <sub>ODD</sub>  | CC | 50   | -      | 450              | ns   | $V_{\text{AIN}} \ge V_{\text{AREF}}$ + 210 mV         |  |

|                                                |                   |    | 45   | -      | 105              | ns   | $V_{\text{AIN}} \ge V_{\text{AREF}}$ + 400 mV         |  |

| Always detected                                | t <sub>OPDD</sub> | CC | 440  | -      | -                | ns   | $V_{\text{AIN}} \ge V_{\text{AREF}}$ + 210 mV         |  |

| Overvoltage Pulse                              |                   |    | 90   | -      | -                | ns   | $V_{\text{AIN}} \ge V_{\text{AREF}}$ + 400 mV         |  |

| Never detected                                 | t <sub>OPDN</sub> | СС | -    | -      | 45               | ns   | $V_{\text{AIN}} \ge V_{\text{AREF}}$ + 210 mV         |  |

| Overvoltage Pulse                              |                   |    | -    | -      | 30               | ns   | $V_{\text{AIN}} \ge V_{\text{AREF}}$ + 400 mV         |  |

| Release Delay                                  | t <sub>ORD</sub>  | CC | 65   | -      | 105              | ns   | $V_{AIN} \leq V_{AREF}$                               |  |

| Enable Delay                                   | t <sub>OED</sub>  | CC | -    | 100    | 200              | ns   |                                                       |  |

## Table 28 ORC Parameters (Operating Conditions apply)

<sup>1)</sup> Always the standard VADC reference, alternate references do not apply to the ORC.

# XMC4700 / XMC4800 XMC4000 Family

#### **Electrical Parameters**

Figure 18 GxORCOUTy Trigger Generation

Figure 19 ORC Detection Ranges

# 3.2.8 Power Supply Current

The total power supply current defined below consists of a leakage and a switching component.

Application relevant values are typically lower than those given in the following tables, and depend on the customer's system operating conditions (e.g. thermal connection or used application configurations).

If not stated otherwise, the operating conditions for the parameters in the following table are:

$V_{\rm DDP}$  = 3.3 V,  $T_{\rm A}$  = 25 °C

| Parameter                                                               | Symb              | Symbol |      | Values | S    | Unit | Note /          |  |

|-------------------------------------------------------------------------|-------------------|--------|------|--------|------|------|-----------------|--|

|                                                                         |                   |        | Min. | Тур.   | Max. |      | Test Condition  |  |

| Active supply current <sup>1)11)</sup>                                  | $I_{\rm DDPA}$    | CC     | -    | 135    | -    | mA   | 144 / 144 / 144 |  |

| Peripherals enabled                                                     |                   |        | -    | 125    | -    |      | 144 / 72 / 72   |  |

| Frequency: $f_{CPU}/f_{PERIPH}/f_{CCU}$ in MHz                          |                   |        | -    | 97     | -    |      | 72 / 72 / 144   |  |

| JCPU, JPERIPH, JCCU                                                     |                   |        | -    | 80     | -    |      | 24 / 24 / 24    |  |

|                                                                         |                   |        | -    | 68     | -    |      | 1/1/1           |  |

| Active supply current<br>Code execution from RAM<br>Flash in Sleep mode | $I_{\rm DDPA}$    | CC     | -    | 108    | -    | mA   | 144 / 144 / 144 |  |

|                                                                         |                   |        | -    | 98     | -    |      | 144 / 72 / 72   |  |

| Active supply current <sup>2)</sup>                                     | I <sub>DDPA</sub> | CC     | -    | 86     | -    | mA   | 144 / 144 / 144 |  |

| Peripherals disabled                                                    |                   |        | -    | 85     | -    |      | 144 / 72 / 72   |  |

| Frequency: $f_{CPU}/f_{PERIPH}/f_{CCU}$ in MHz                          |                   |        | -    | 70     | -    | -    | 72 / 72 / 144   |  |

| JCPU, JPERIPH, JCCU                                                     |                   |        | _    | 55     | -    |      | 24 / 24 / 24    |  |

|                                                                         |                   |        | -    | 50     | -    |      | 1/1/1           |  |

| Sleep supply current <sup>3)</sup>                                      | $I_{\rm DDPS}$    | CC     | -    | 127    | -    | mA   | 144 / 144 / 144 |  |

| Peripherals enabled                                                     |                   |        | _    | 115    | -    |      | 144 / 72 / 72   |  |

| Frequency: $f_{CPU}/f_{PERIPH}/f_{CCU}$ in MHz                          |                   |        | _    | 93     | -    | -    | 72 / 72 / 144   |  |

|                                                                         |                   |        | -    | 57     | -    |      | 24 / 24 / 24    |  |

|                                                                         |                   |        | -    | 47     | -    | 1    | 1/1/1           |  |

| $f_{\rm CPU}/f_{\rm PERIPH}/f_{\rm CCU}$ in kHz                         | 1                 |        | -    | 48     | -    | 1    | 100 / 100 / 100 |  |

#### Table 34 Power Supply Parameters

Note: These parameters are not subject to production test, but verified by design and/or characterization.

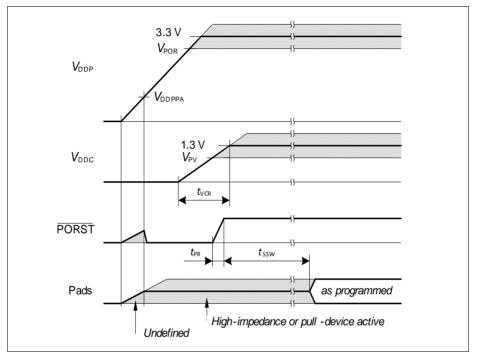

- 2) Maximum threshold for reset deassertion.

- 3) The  $V_{\text{DDP}}$  monitoring has a typical hysteresis of  $V_{\text{PORHYS}}$  = 180 mV.

- If t<sub>PR</sub> is not met, low spikes on PORST may be seen during start up (e.g. reset pulses generated by the supply monitoring due to a slow ramping V<sub>DDP</sub>).

Figure 26 Power-Up Behavior

## 3.3.3 Power Sequencing

While starting up and shutting down as well as when switching power modes of the system it is important to limit the current load steps. A typical cause for such load steps is changing the CPU frequency  $f_{\rm CPU}$ . Load steps exceeding the below defined values may cause a power on reset triggered by the supply monitor.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

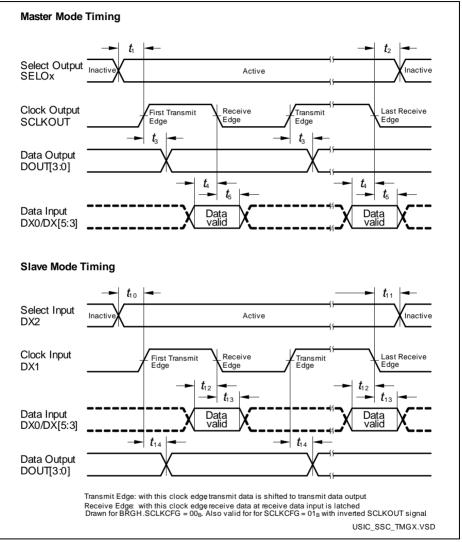

## Table 47 USIC SSC Slave Mode Timing

| Parameter                                                                                 |                  | nbol |      | Values | S    | Unit | Note /         |  |

|-------------------------------------------------------------------------------------------|------------------|------|------|--------|------|------|----------------|--|

|                                                                                           |                  |      | Min. | Тур.   | Max. |      | Test Condition |  |

| DX1 slave clock period                                                                    | t <sub>CLK</sub> | SR   | 66.6 | -      | -    | ns   |                |  |

| Select input DX2 setup to first clock input DX1 transmit edge <sup>1)</sup>               | t <sub>10</sub>  | SR   | 3    | -      | -    | ns   |                |  |

| Select input DX2 hold after<br>last clock input DX1 receive<br>edge <sup>1)</sup>         | t <sub>11</sub>  | SR   | 4    | -      | -    | ns   |                |  |

| Receive data input<br>DX0/DX[5:3] setup time to<br>shift clock receive edge <sup>1)</sup> | t <sub>12</sub>  | SR   | 6    | -      | -    | ns   |                |  |

| Data input DX0/DX[5:3] hold<br>time from clock input DX1<br>receive edge <sup>1)</sup>    | t <sub>13</sub>  | SR   | 4    | -      | -    | ns   |                |  |

| Data output DOUT[3:0] valid time                                                          | t <sub>14</sub>  | СС   | 0    | -      | 24   | ns   |                |  |

This input timing is valid for asynchronous input signal handling of slave select input, shift clock input, and receive data input (bits DXnCR.DSEN = 0).

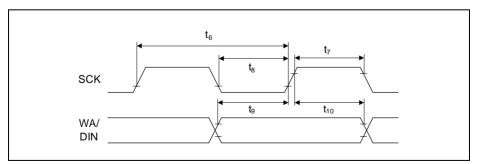

Figure 33 USIC - SSC Master/Slave Mode Timing

Note: This timing diagram shows a standard configuration, for which the slave select signal is low-active, and the serial clock signal is not shifted and not inverted.

| Figure 35 | USIC IIS Master | Transmitter Timing |  |

|-----------|-----------------|--------------------|--|

|-----------|-----------------|--------------------|--|

| Parameter       | Symbol                    |                             | Values | 3    | Unit | Note /<br>Test Condition |

|-----------------|---------------------------|-----------------------------|--------|------|------|--------------------------|

|                 |                           | Min.                        | Тур.   | Max. |      |                          |

| Clock period    | t <sub>6</sub> SR         | 66.6                        | _      | -    | ns   |                          |

| Clock high time | t <sub>7</sub> SR         | 0.35 x<br>t <sub>6min</sub> | -      | -    | ns   |                          |

| Clock low time  | t <sub>8</sub> SR         | 0.35 x<br>t <sub>6min</sub> | -      | -    | ns   |                          |

| Set-up time     | t <sub>9</sub> SR         | 0.2 x<br>t <sub>6min</sub>  | -      | -    | ns   |                          |

| Hold time       | <i>t</i> <sub>10</sub> SR | 0                           | -      | -    | ns   |                          |

Figure 36 USIC IIS Slave Receiver Timing

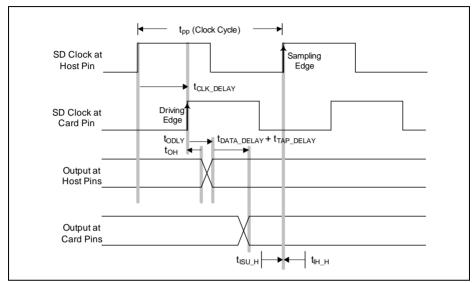

# Full-Speed Input Path (Read)

Figure 38 Full-Speed Input Path

## Full-Speed Read Meeting Setup (Maximum Delay)

The following equations show how to calculate the allowed combined propagation delay range of the SD\_CLK and SD\_DAT/CMD signals on the PCB.

(5)

```

t_{\text{CLK\_DELAY}} + t_{\text{DATA\_DELAY}} + t_{\text{TAP\_DELAY}} + t_{\text{ODLY}} + t_{\text{ISU\_F}} < 0.5 \times t_{\text{pp}}

```

$t_{\mathrm{CLK\_DELAY}} + t_{\mathrm{DATA\_DELAY}} < 0.5 \times t_{pp} - t_{\mathrm{ODLY}} - t_{\mathrm{ISU\_F}} - t_{\mathrm{TAP\_DELAY}}$

$t_{\mathrm{CLK\_DELAY}} + t_{\mathrm{DATA\_DELAY}} < 20 - 14 - 2 - t_{\mathrm{TAP\_DELAY}}$

$t_{\rm CLK\_DELAY} + t_{\rm DATA\_DELAY} < 4 - t_{\rm TAP\_DELAY}$

The data + clock delay can be up to 4 ns for a 40 ns clock cycle.

## Write Timing

## Table 58 Asynchronous Write Timing, Multiplexed and Demultiplexed

| Parameter            | Symbol          | Limit Values |                 | Unit |      |    |

|----------------------|-----------------|--------------|-----------------|------|------|----|

|                      |                 |              |                 | Min. | Max. |    |

| A(24:0) output delay | to RD/WR rising | CC           | t <sub>30</sub> | -2.5 | 2.5  | ns |

| A(24:0) output delay |                 | CC           | t <sub>31</sub> | -2.5 | 2.5  |    |

| CS rising edge       |                 | CC           | t <sub>32</sub> | -2   | 2    |    |

| ADV rising edge      |                 | CC           | t <sub>33</sub> | -2   | 4.5  |    |

| BC rising edge       |                 | CC           | t <sub>34</sub> | -2.5 | 2    |    |

| WAIT input setup     |                 | SR           | t <sub>35</sub> | 12   | -    |    |

| WAIT input hold      |                 | SR           | t <sub>36</sub> | 0    | -    |    |

| Data output delay    |                 | CC           | t <sub>37</sub> | -5.5 | 2    |    |

| Data output delay    |                 | CC           | t <sub>38</sub> | -5.5 | 2    |    |

| RD / WR output delay |                 | CC           | t <sub>39</sub> | -2.5 | 1.5  |    |

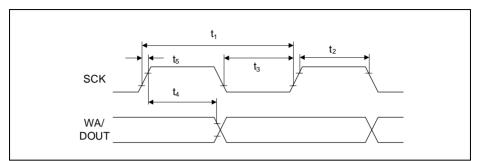

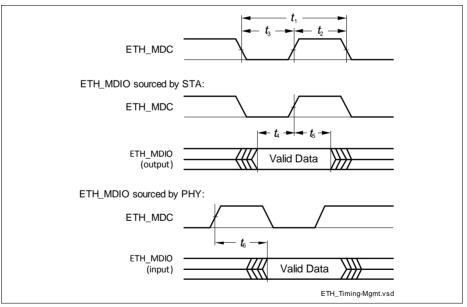

# 3.3.12.2 ETH Management Signal Parameters (ETH\_MDC, ETH\_MDIO)

| Parameter                    |                       | nbol | Values |      |      | Unit | Note /                 |  |

|------------------------------|-----------------------|------|--------|------|------|------|------------------------|--|

|                              |                       |      | Min.   | Тур. | Max. | -    | Test Conditi<br>on     |  |

| ETH_MDC period               | <i>t</i> <sub>1</sub> | CC   | 400    | -    | -    | ns   | C <sub>L</sub> = 25 pF |  |

| ETH_MDC high time            | <i>t</i> <sub>2</sub> | CC   | 160    | -    | -    | ns   |                        |  |

| ETH_MDC low time             | t <sub>3</sub>        | CC   | 160    | _    | -    | ns   |                        |  |

| ETH_MDIO setup time (output) | $t_4$                 | CC   | 10     | -    | -    | ns   |                        |  |

| ETH_MDIO hold time (output)  | $t_5$                 | CC   | 10     | -    | -    | ns   |                        |  |

| ETH_MDIO data valid (input)  | $t_6$                 | SR   | 0      | —    | 300  | ns   |                        |  |

#### Table 64 ETH Management Signal Timing Parameters

Figure 52 ETH Management Signal Timing

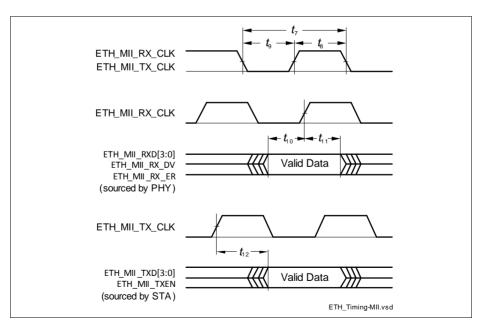

# 3.3.12.3 ETH MII Parameters

In the following, the parameters of the MII (Media Independent Interface) are described.

| Parameter                 | Symbol                 |    | Values |      |      | Unit | Note /                 |  |

|---------------------------|------------------------|----|--------|------|------|------|------------------------|--|

|                           |                        |    | Min.   | Тур. | Max. |      | Test Condition         |  |

| Clock period, 10 Mbps     | <i>t</i> <sub>7</sub>  | SR | 400    | -    | -    | ns   | C <sub>L</sub> = 25 pF |  |

| Clock high time, 10 Mbps  | <i>t</i> <sub>8</sub>  | SR | 140    | -    | 260  | ns   | -                      |  |

| Clock low time, 10 Mbps   | t <sub>9</sub>         | SR | 140    | -    | 260  | ns   | -                      |  |

| Clock period, 100 Mbps    | <i>t</i> <sub>7</sub>  | SR | 40     | -    | -    | ns   | -                      |  |

| Clock high time, 100 Mbps | <i>t</i> <sub>8</sub>  | SR | 14     | -    | 26   | ns   | -                      |  |

| Clock low time, 100 Mbps  | t <sub>9</sub>         | SR | 14     | -    | 26   | ns   |                        |  |

| Input setup time          | <i>t</i> <sub>10</sub> | SR | 10     | -    | -    | ns   | -                      |  |

| Input hold time           | <i>t</i> <sub>11</sub> | SR | 10     | -    | -    | ns   |                        |  |

| Output valid time         | <i>t</i> <sub>12</sub> | CC | 0      | -    | 25   | ns   |                        |  |

Table 65 ETH MII Signal Timing Parameters

#### Figure 53 ETH MII Signal Timing

#### **Quality Declarations**

# 5 Quality Declarations

The qualification of the XMC4[78]00 is executed according to the JEDEC standard JESD47I.

Note: For automotive applications refer to the Infineon automotive microcontrollers.

| Parameter                                                        | Symbol                 |      | Value | s     | Unit | Note /<br>Test Condition                                     |  |

|------------------------------------------------------------------|------------------------|------|-------|-------|------|--------------------------------------------------------------|--|

|                                                                  |                        | Min. | Тур.  | Max.  |      |                                                              |  |

| Operation lifetime                                               | t <sub>OP</sub> CC     | 20   | -     | -     | а    | $T_{\rm J} \le 109^{\circ}{ m C},$<br>device permanent<br>on |  |

| ESD susceptibility<br>according to Human Body<br>Model (HBM)     | $V_{\rm HBM}$ SR       | -    | -     | 3 000 | V    | EIA/JESD22-<br>A114-B                                        |  |

| ESD susceptibility<br>according to Charged<br>Device Model (CDM) | V <sub>CDM</sub><br>SR | -    | -     | 1 000 | V    | Conforming to JESD22-C101-C                                  |  |

| Moisture sensitivity level                                       | MSL<br>CC              | _    | -     | 3     | -    | JEDEC<br>J-STD-020D                                          |  |

| Soldering temperature                                            | $T_{\rm SDR}$<br>SR    | -    | _     | 260   | °C   | Profile according<br>to JEDEC<br>J-STD-020D                  |  |

#### Table 72Quality Parameters