Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                                      |

|----------------------------|---------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                             |

| Core Size                  | 32-Bit Single-Core                                                                          |

| Speed                      | 144MHz                                                                                      |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, LINbus, MMC/SD, SPI, UART/USART, USB OTG, USIC |

| Peripherals                | DMA, I <sup>2</sup> S, LED, POR, Touch-Sense, WDT                                           |

| Number of I/O              | 75                                                                                          |

| Program Memory Size        | 1.5MB (1.5M x 8)                                                                            |

| Program Memory Type        | FLASH                                                                                       |

| EEPROM Size                | -                                                                                           |

| RAM Size                   | 276K x 8                                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 3.63V                                                                               |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                       |

| Oscillator Type            | External                                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                          |

| Mounting Type              | Surface Mount                                                                               |

| Package / Case             | 100-LQFP Exposed Pad                                                                        |

| Supplier Device Package    | PG-LQFP-100-25                                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xmc4700f100k1536aaxqma1          |

|                            |                                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Summary of Features

- Tri-stated in input mode

- Push/pull or open drain output mode

- Boundary scan test support over JTAG interface

## **On-Chip Debug Support**

- Full support for debug features: 8 breakpoints, CoreSight, trace

- · Various interfaces: ARM-JTAG, SWD, single wire trace

# 1.1 Ordering Information

The ordering code for an Infineon microcontroller provides an exact reference to a specific product. The code "XMC4<DDD>-<Z><PPP><T><FFFF>" identifies:

- <DDD> the derivatives function set

- <Z> the package variant

- E: LFBGA

- F: LQFP

- Q: VQFN

- <PPP> package pin count

- <T> the temperature range:

- F: -40°C to 85°C

- K: -40°C to 125°C

- <FFFF> the Flash memory size.

For ordering codes for the XMC4[78]00 please contact your sales representative or local distributor.

This document describes several derivatives of the XMC4[78]00 series, some descriptions may not apply to a specific product. Please see **Table 1**.

For simplicity the term XMC4[78]00 is used for all derivatives throughout this document.

# 1.2 Device Types

These device types are available and can be ordered through Infineon's direct and/or distribution channels.

| Table 1 | Synopsis of XMC4[78]00 Device Types |

|---------|-------------------------------------|

|---------|-------------------------------------|

| Derivative <sup>1)</sup> | Package      | Flash<br>Kbytes | SRAM<br>Kbytes |

|--------------------------|--------------|-----------------|----------------|

| XMC4700-E196x2048        | PG-LFBGA-196 | 2048            | 352            |

| XMC4700-F144x2048        | PG-LQFP-144  | 2048            | 352            |

| XMC4700-F100x2048        | PG-LQFP-100  | 2048            | 352            |

| XMC4700-E196x1536        | PG-LFBGA-196 | 1536            | 276            |

# XMC4700 / XMC4800 XMC4000 Family

### **General Device Information**

| Table 10         Package Pin Mapping (cont'd) |           |          |          |            |                                                                                                                                                                                                  |  |  |  |

|-----------------------------------------------|-----------|----------|----------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Function                                      | LFBGA-196 | LQFP-144 | LQFP-100 | Pad Type   | Notes                                                                                                                                                                                            |  |  |  |

| P14.14                                        | К3        | 32       | 21       | AN/DIG_IN  |                                                                                                                                                                                                  |  |  |  |

| P14.15                                        | K2        | 31       | 20       | AN/DIG_IN  |                                                                                                                                                                                                  |  |  |  |

| P15.2                                         | K1        | 30       | 19       | AN/DIG_IN  |                                                                                                                                                                                                  |  |  |  |

| P15.3                                         | J2        | 29       | 18       | AN/DIG_IN  |                                                                                                                                                                                                  |  |  |  |

| P15.4                                         | J4        | 28       | -        | AN/DIG_IN  |                                                                                                                                                                                                  |  |  |  |

| P15.5                                         | J3        | 27       | -        | AN/DIG_IN  |                                                                                                                                                                                                  |  |  |  |

| P15.6                                         | J5        | 26       | -        | AN/DIG_IN  |                                                                                                                                                                                                  |  |  |  |

| P15.7                                         | J6        | 25       | -        | AN/DIG_IN  |                                                                                                                                                                                                  |  |  |  |

| P15.8                                         | P6        | 54       | 39       | AN/DIG_IN  |                                                                                                                                                                                                  |  |  |  |

| P15.9                                         | N6        | 53       | 38       | AN/DIG_IN  |                                                                                                                                                                                                  |  |  |  |

| P15.12                                        | M5        | 50       | -        | AN/DIG_IN  |                                                                                                                                                                                                  |  |  |  |

| P15.13                                        | P4        | 49       | -        | AN/DIG_IN  |                                                                                                                                                                                                  |  |  |  |

| P15.14                                        | N4        | 44       | -        | AN/DIG_IN  |                                                                                                                                                                                                  |  |  |  |

| P15.15                                        | M4        | 43       | -        | AN/DIG_IN  |                                                                                                                                                                                                  |  |  |  |

| USB_DP                                        | G1        | 16       | 9        | special    |                                                                                                                                                                                                  |  |  |  |

| USB_DM                                        | F1        | 15       | 8        | special    |                                                                                                                                                                                                  |  |  |  |

| HIB_IO_0                                      | H4        | 21       | 14       | A1 special | At the first power-up and<br>with every reset of the<br>hibernate domain this pin<br>is configured as open-<br>drain output and drives<br>"0".<br>As output the medium<br>driver mode is active. |  |  |  |

| HIB_IO_1                                      | H3        | 20       | 13       | A1 special | At the first power-up and<br>with every reset of the<br>hibernate domain this pin<br>is configured as input with<br>no pull device active.<br>As output the medium<br>driver mode is active.     |  |  |  |

| тск                                           | J8        | 93       | 67       | A1         | Weak pull-down active.                                                                                                                                                                           |  |  |  |

| TMS                                           | J7        | 92       | 66       | A1+        | Weak pull-up active.<br>As output the strong-soft<br>driver mode is active.                                                                                                                      |  |  |  |

## 3.1.2 Absolute Maximum Ratings

Stresses above the values listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

| Parameter                                                                                                              | Symb                 | ol | Values |      |                                       | Unit | Note /                |

|------------------------------------------------------------------------------------------------------------------------|----------------------|----|--------|------|---------------------------------------|------|-----------------------|

|                                                                                                                        |                      |    | Min.   | Тур. | Max.                                  |      | Test Con<br>dition    |

| Storage temperature                                                                                                    | $T_{\rm ST}$         | SR | -65    | -    | 150                                   | °C   | _                     |

| Junction temperature                                                                                                   | $T_{J}$              | SR | -40    | -    | 150                                   | °C   | _                     |

| Voltage at 3.3 V power supply pins with respect to $V_{SS}$                                                            | $V_{DDP}$            | SR | -      | -    | 4.3                                   | V    | -                     |

| Voltage on any Class A and dedicated input pin with respect to $V_{\rm SS}$                                            | V <sub>IN</sub>      | SR | -1.0   | -    | V <sub>DDP</sub> + 1.0<br>or max. 4.3 | V    | whichever<br>is lower |

| Voltage on any analog input pin with respect to $V_{\rm AGND}$                                                         | $V_{AIN}$ $V_{AREF}$ | SR | -1.0   | -    | V <sub>DDP</sub> + 1.0<br>or max. 4.3 | V    | whichever<br>is lower |

| Input current on any pin<br>during overload condition                                                                  | I <sub>IN</sub>      | SR | -10    | -    | +10                                   | mA   |                       |

| Absolute maximum sum of all<br>input circuit currents for one<br>port group during overload<br>condition <sup>1)</sup> | $\Sigma I_{\rm IN}$  | SR | -25    | -    | +25                                   | mA   |                       |

| Absolute maximum sum of all<br>input circuit currents during<br>overload condition                                     | $\Sigma I_{\rm IN}$  | SR | -100   | -    | +100                                  | mA   |                       |

### Table 13 Absolute Maximum Rating Parameters

1) The port groups are defined in **Table 17**.

**Figure 10** explains the input voltage ranges of  $V_{\rm IN}$  and  $V_{\rm AIN}$  and its dependency to the supply level of  $V_{\rm DDP}$ . The input voltage must not exceed 4.3 V, and it must not be more than 1.0 V above  $V_{\rm DDP}$ . For the range up to  $V_{\rm DDP}$  + 1.0 V also see the definition of the overload conditions in Section 3.1.3.

## Table 14 Overload Parameters

| Parameter                                                                  | Symbol              |      | Values |      |    | Note /                                                |

|----------------------------------------------------------------------------|---------------------|------|--------|------|----|-------------------------------------------------------|

|                                                                            |                     | Min. | Тур.   | Max. |    | Test Condition                                        |

| Input current on any port pin during overload condition                    | I <sub>OV</sub> SR  | -5   | -      | 5    | mA |                                                       |

| Absolute sum of all input circuit currents for one port                    | I <sub>OVG</sub> SR | -    | -      | 20   | mA | $\Sigma  I_{OVx} $ , for all $I_{OVx} < 0 \text{ mA}$ |

| group during overload condition <sup>1)</sup>                              |                     | -    | -      | 20   | mA | $\Sigma  I_{OVx} $ , for all $I_{OVx} > 0 \text{ mA}$ |

| Absolute sum of all input<br>circuit currents during<br>overload condition | I <sub>OVS</sub> SR | -    | -      | 80   | mA | $\Sigma I_{OVG}$                                      |

1) The port groups are defined in Table 17.

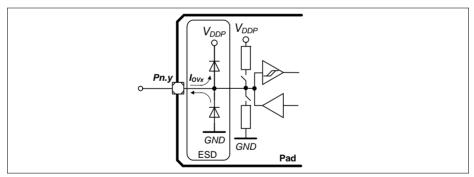

**Figure 11** shows the path of the input currents during overload via the ESD protection structures. The diodes against  $V_{\text{DDP}}$  and ground are a simplified representation of these ESD protection structures.

Figure 11 Input Overload Current via ESD structures

Table 15 and Table 16 list input voltages that can be reached under overload conditions.Note that the absolute maximum input voltages as defined in the Absolute MaximumRatings must not be exceeded during overload.

## Table 21 Standard Pads Class\_A1

| Parameter             | Symbol                  | Va                     | lues                         | Unit | Note /                                                   |

|-----------------------|-------------------------|------------------------|------------------------------|------|----------------------------------------------------------|

|                       |                         | Min.                   | Max.                         |      | Test Condition                                           |

| Input leakage current | I <sub>OZA1</sub> CC    | -500                   | 500                          | nA   | $0 \text{ V} \leq V_{\text{IN}} \leq V_{\text{DDP}}$     |

| Input high voltage    | $V_{\rm IHA1}~{\rm SR}$ | $0.6 	imes V_{ m DDP}$ | $V_{\text{DDP}}$ + 0.3       | V    | max. 3.6 V                                               |

| Input low voltage     | $V_{\rm ILA1}{\rm SR}$  | -0.3                   | $0.36 \times V_{\text{DDF}}$ | . V  |                                                          |

| Output high voltage,  | $V_{OHA1}$              | V <sub>DDP</sub> - 0.4 | -                            | V    | $I_{OH} \ge$ -400 $\mu$ A                                |

| $POD^{1)} = weak$     | CC                      | 2.4                    | -                            | V    | $I_{OH} \ge$ -500 $\mu$ A                                |

| Output high voltage,  |                         | V <sub>DDP</sub> - 0.4 | -                            | V    | $I_{\rm OH} \ge$ -1.4 mA                                 |

| $POD^{1} = medium$    |                         | 2.4                    | -                            | V    | $I_{OH} \ge -2 \text{ mA}$                               |

| Output low voltage    | V <sub>OLA1</sub><br>CC | -                      | 0.4                          | V    | $I_{OL} \le 500 \ \mu A;$<br>POD <sup>1)</sup> = weak    |

|                       |                         | _                      | 0.4                          | V    | $I_{OL} \le 2 \text{ mA};$<br>POD <sup>1)</sup> = medium |

| Fall time             | t <sub>FA1</sub> CC     | _                      | 150                          | ns   | $C_{L} = 20 \text{ pF};$<br>POD <sup>1)</sup> = weak     |

|                       |                         | -                      | 50                           | ns   | $C_{\rm L}$ = 50 pF;<br>POD <sup>1)</sup> = medium       |

| Rise time             | t <sub>RA1</sub> CC     | -                      | 150                          | ns   | $C_{\rm L}$ = 20 pF;<br>POD <sup>1)</sup> = weak         |

|                       |                         | -                      | 50                           | ns   | $C_{L} = 50 \text{ pF};$<br>POD <sup>1)</sup> = medium   |

1) POD = Pin Out Driver

## Table 22 Standard Pads Class\_A1+

| Parameter             | Symbol Values         |                          |  | Unit                      | Note / |                                                      |

|-----------------------|-----------------------|--------------------------|--|---------------------------|--------|------------------------------------------------------|

|                       |                       | Min.                     |  | Max.                      |        | Test Condition                                       |

| Input leakage current | I <sub>OZA1+</sub> CC | -1                       |  | 1                         | μΑ     | $0 \text{ V} \leq V_{\text{IN}} \leq V_{\text{DDP}}$ |

| Input high voltage    | $V_{\rm IHA1+}\rm SR$ | $0.6 \times V_{\rm DDP}$ |  | $V_{\text{DDP}}$ + 0.3    | V      | max. 3.6 V                                           |

| Input low voltage     | $V_{\rm ILA1+}\rm SR$ | -0.3                     |  | $0.36 \times V_{\rm DDP}$ | V      |                                                      |

## **Conversion Time**

| Table 26 | <b>Conversion Time</b> (Operating Conditions apply) |

|----------|-----------------------------------------------------|

|----------|-----------------------------------------------------|

| Parameter Symbol   |                |    | Values                                                      | Unit | Note                                                                                             |

|--------------------|----------------|----|-------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------|

| Conversion<br>time | t <sub>C</sub> | CC | $2 \times T_{ADC}$ +<br>(2 + N + STC + PC +DM) × $T_{ADCI}$ |      | N = 8, 10, 12 for<br>N-bit conversion<br>$T_{ADC} = 1 / f_{PERIPH}$<br>$T_{ADCI} = 1 / f_{ADCI}$ |

- STC defines additional clock cycles to extend the sample time

- · PC adds two cycles if post-calibration is enabled

- DM adds one cycle for an extended conversion time of the MSB

## **Conversion Time Examples**

System assumptions:

$f_{ADC}$  = 144 MHz i.e.  $t_{ADC}$  = 6.9 ns, DIVA = 3,  $f_{ADCI}$  = 36 MHz i.e.  $t_{ADCI}$  = 27.8 ns

According to the given formulas the following minimum conversion times can be achieved (STC = 0, DM = 0):

12-bit post-calibrated conversion (PC = 2):

$t_{\text{CN12C}} = (2 + 12 + 2) \times t_{\text{ADCI}} + 2 \times t_{\text{ADC}} = 16 \times 27.8 \text{ ns} + 2 \times 6.9 \text{ ns} = 459 \text{ ns}$ 12-bit uncalibrated conversion:

$t_{CN12} = (2 + 12) \times t_{ADC1} + 2 \times t_{ADC} = 14 \times 27.8 \text{ ns} + 2 \times 6.9 \text{ ns} = 403 \text{ ns}$

10-bit uncalibrated conversion:

$t_{CN10} = (2 + 10) \times t_{ADCI} + 2 \times t_{ADC} = 12 \times 27.8 \text{ ns} + 2 \times 6.9 \text{ ns} = 348 \text{ ns}$

8-bit uncalibrated:

$t_{CN8} = (2 + 8) \times t_{ADC1} + 2 \times t_{ADC} = 10 \times 27.8 \text{ ns} + 2 \times 6.9 \text{ ns} = 292 \text{ ns}$

# 3.2.3 Digital to Analog Converters (DAC)

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Parameter                      | Symbol                    |                   | Values |      |      | Unit          | Note /                                                                            |

|--------------------------------|---------------------------|-------------------|--------|------|------|---------------|-----------------------------------------------------------------------------------|

|                                |                           |                   | Min.   | Тур. | Max. | -             | Test Condition                                                                    |

| RMS supply current             | I <sub>DD</sub>           | CC                | -      | 2.5  | 4    | mA            | per active DAC<br>channel,<br>without load<br>currents of DAC<br>outputs          |

| Resolution                     | RES                       | CC                | _      | 12   | -    | Bit           |                                                                                   |

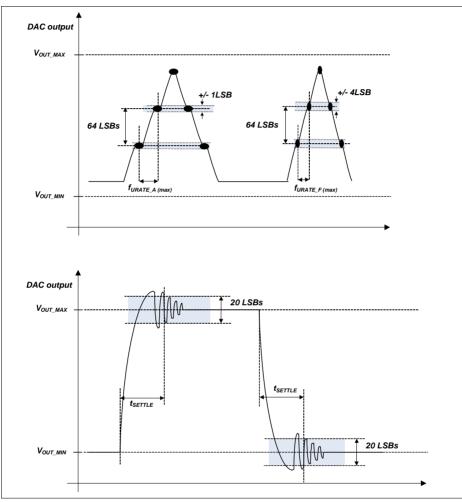

| Update rate                    | f <sub>urate.</sub>       | _ <sub>A</sub> CC | _      |      | 2    | Msam<br>ple/s | data rate, where<br>DAC can follow<br>64 LSB code jumps<br>to ± 1LSB accuracy     |

| Update rate                    | f <sub>urate.</sub>       | _ <sub>F</sub> CC | _      |      | 5    | Msam<br>ple/s | data rate, where<br>DAC can follow<br>64 LSB code jumps<br>to ± 4 LSB accuracy    |

| Settling time                  | t <sub>settle</sub>       | E CC              | -      | 1    | 2    | μs            | at full scale jump,<br>output voltage<br>reaches target<br>value ± 20 LSB         |

| Slew rate                      | SR                        | CC                | 2      | 5    | -    | V/µs          |                                                                                   |

| Minimum output<br>voltage      | V <sub>OUT_</sub> N<br>CC | MIN               | -      | 0.3  | -    | V             | code value<br>unsigned: 000 <sub>H</sub> ;<br>signed: 800 <sub>H</sub>            |

| Maximum output<br>voltage      | V <sub>OUT_</sub> N<br>CC | МАХ               | -      | 2.5  | _    | V             | code value<br>unsigned: FFF <sub>H</sub> ;<br>signed: 7FF <sub>H</sub>            |

| Integral non-linearity         | INL                       | CC                | -5.5   | ±2.5 | 5.5  | LSB           | $\begin{array}{l} R_L \geq 5 \text{ kOhm}, \\ C_L \leq 50 \text{ pF} \end{array}$ |

| Differential non-<br>linearity | DNL                       | СС                | -2     | ±1   | 2    | LSB           | $\begin{array}{l} R_L \geq 5 \text{ kOhm,} \\ C_L \leq 50 \text{ pF} \end{array}$ |

| Table 27 | DAC Parameters | (Operating Conditions apply) |

|----------|----------------|------------------------------|

|----------|----------------|------------------------------|

| Parameter                         | Symbol                       |        | Values |      |      | Note /                                                  |

|-----------------------------------|------------------------------|--------|--------|------|------|---------------------------------------------------------|

|                                   |                              | Min.   | Тур.   | Max. |      | Test Condition                                          |

| Offset error                      | ED <sub>OFF</sub> C          | С      | ±20    |      | mV   |                                                         |

| Gain error                        | $ED_{G_{IN}}CO$              | C -6.5 | -1.5   | 3    | %    |                                                         |

| Startup time                      | t <sub>STARTUP</sub> C       | C –    | 15     | 30   | μs   | time from output<br>enabling till code<br>valid ±16 LSB |

| 3dB Bandwidth of<br>Output Buffer | <i>f</i> <sub>C1</sub> C     | C 2.5  | 5      | -    | MHz  | verified by design                                      |

| Output sourcing current           | I <sub>OUT_SOURC</sub><br>CC | CE -   | -30    | -    | mA   |                                                         |

| Output sinking<br>current         | I <sub>OUT_SINK</sub><br>CC  | -      | 0.6    | -    | mA   |                                                         |

| Output resistance                 | R <sub>OUT</sub> C           | C –    | 50     | -    | Ohm  |                                                         |

| Load resistance                   | R <sub>L</sub> S             | R 5    | -      | -    | kOhm |                                                         |

| Load capacitance                  | C <sub>L</sub> S             | R –    | -      | 50   | pF   |                                                         |

| Signal-to-Noise<br>Ratio          | SNR CO                       | -      | 70     | -    | dB   | examination<br>bandwidth < 25 kHz                       |

| Total Harmonic<br>Distortion      | THD C                        | C –    | 70     | -    | dB   | examination<br>bandwidth < 25 kHz                       |

| Power Supply<br>Rejection Ratio   | PSRR CO                      | C –    | 56     | -    | dB   | to $V_{\rm DDA}$ verified by design                     |

### Table 27 DAC Parameters (Operating Conditions apply) (cont'd)

### **Conversion Calculation**

Unsigned: DACxDATA = 4095 × ( $V_{OUT}$  -  $V_{OUT\_MIN}$ ) / ( $V_{OUT\_MAX}$  -  $V_{OUT\_MIN}$ ) Signed: DACxDATA = 4095 × ( $V_{OUT}$  -  $V_{OUT\_MIN}$ ) / ( $V_{OUT\_MAX}$  -  $V_{OUT\_MIN}$ ) - 2048

Figure 17 DAC Conversion Examples

- 1) In case the Program Verify feature detects weak bits, these bits will be programmed once more. The reprogramming takes an additional time of 5.5 ms.

- 2) The following formula applies to the wait state configuration: FCON.WSPFLASH × (1 /  $f_{CPU}$ )  $\geq t_a$ .

- 3) Storage and inactive time included.

- 4) Values given are valid for an average weighted junction temperature of  $T_{\rm J}$  = 110°C.

- 5) Only valid with robust EEPROM emulation algorithm, equally cycling the logical sectors. For more details see the Reference Manual.

## 3.3.4 Phase Locked Loop (PLL) Characteristics

Note: These parameters are not subject to production test, but verified by design and/or characterization.

### Main and USB PLL

| Parameter                | Symbol                     |      | Values | S    | Unit | Note /<br>Test Condition                                                    |

|--------------------------|----------------------------|------|--------|------|------|-----------------------------------------------------------------------------|

|                          |                            | Min. | Тур.   | Max. |      |                                                                             |

| Accumulated Jitter       | D <sub>P</sub> CC          | -    | -      | ±5   | ns   | accumulated<br>over 300 cycles<br>$f_{SYS}$ = 144 MHz                       |

| Duty Cycle <sup>1)</sup> | D <sub>DC</sub> CC         | 46   | 50     | 54   | %    | Low pulse to<br>total period,<br>assuming an<br>ideal input clock<br>source |

| PLL base frequency       | f <sub>pllbase</sub><br>CC | 30   | -      | 140  | MHz  |                                                                             |

| VCO input frequency      | $f_{\sf REF}\sf CC$        | 4    | -      | 16   | MHz  |                                                                             |

| VCO frequency range      | $f_{\rm VCO}  {\rm CC}$    | 260  | -      | 520  | MHz  |                                                                             |

| PLL lock-in time         | t <sub>L</sub> CC          | -    | -      | 400  | μS   |                                                                             |

### Table 39PLL Parameters

1) 50% for even K2 divider values, 50±(10/K2) for odd K2 divider values.

## **Slow Internal Clock Source**

| Parameter         | Symbol                  |      | Values |      | Unit | Note /<br>Test Condition                                               |

|-------------------|-------------------------|------|--------|------|------|------------------------------------------------------------------------|

|                   |                         | Min. | Тур.   | Max. |      |                                                                        |

| Nominal frequency | $f_{\rm OSI}{\rm CC}$   | -    | 32.768 | -    | kHz  |                                                                        |

| Accuracy          | ∆f <sub>OSI</sub><br>CC | -4   | -      | 4    | %    | $V_{BAT} = const.$<br>0 °C $\leq T_{A} \leq$<br>85 °C                  |

|                   |                         | -5   | -      | 5    | %    | $V_{BAT}$ = const.<br>$T_A < 0 \text{ °C or}$<br>$T_A > 85 \text{ °C}$ |

|                   |                         | -5   | -      | 5    | %    | $2.4 \text{ V} \le V_{\text{BAT}},$<br>$T_{\text{A}} = 25 \text{ °C}$  |

|                   |                         | -10  | -      | 10   | %    | $1.95 V \le V_{BAT} < 2.4 V,$<br>$T_A = 25 °C$                         |

| Start-up time     | t <sub>OSIS</sub> CC    | -    | 50     | -    | μS   |                                                                        |

### Table 41 Slow Internal Clock Parameters

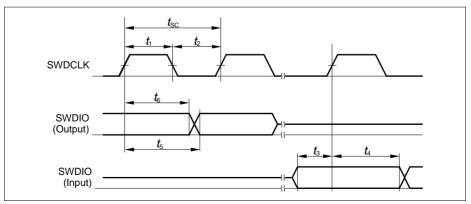

# 3.3.7 Serial Wire Debug Port (SW-DP) Timing

The following parameters are applicable for communication through the SW-DP interface.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

Note: Operating conditions apply.

| Table 43 | SWD Interface Timing Parameters (Operating Conditions apply) |

|----------|--------------------------------------------------------------|

|----------|--------------------------------------------------------------|

| Parameter                                      |                       | nbol |      | Values | 6      | Unit | Note /                 |

|------------------------------------------------|-----------------------|------|------|--------|--------|------|------------------------|

|                                                |                       |      | Min. | Тур.   | Max.   |      | Test Condition         |

| SWDCLK clock period                            | t <sub>SC</sub>       | SR   | 25   | -      | -      | ns   | C <sub>L</sub> = 30 pF |

|                                                |                       |      | 40   | -      | -      | ns   | C <sub>L</sub> = 50 pF |

| SWDCLK high time                               | <i>t</i> <sub>1</sub> | SR   | 10   | -      | 500000 | ns   |                        |

| SWDCLK low time                                | <i>t</i> <sub>2</sub> | SR   | 10   | -      | 500000 | ns   |                        |

| SWDIO input setup to SWDCLK rising edge        | <i>t</i> <sub>3</sub> | SR   | 6    | -      | _      | ns   |                        |

| SWDIO input hold<br>after SWDCLK rising edge   | <i>t</i> <sub>4</sub> | SR   | 6    | -      | -      | ns   |                        |

| SWDIO output valid time                        | $t_5$                 | CC   | -    | -      | 17     | ns   | C <sub>L</sub> = 50 pF |

| after SWDCLK rising edge                       |                       |      | -    | -      | 13     | ns   | C <sub>L</sub> = 30 pF |

| SWDIO output hold time from SWDCLK rising edge | <i>t</i> <sub>6</sub> | СС   | 3    | -      | _      | ns   |                        |

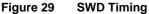

# Table 49 USIC IIC Fast Mode Timing<sup>1)</sup>

| Parameter                                              | Symbol                   |                            | Values |      | Unit | Note /         |

|--------------------------------------------------------|--------------------------|----------------------------|--------|------|------|----------------|

|                                                        |                          | Min.                       | Тур.   | Max. |      | Test Condition |

| Fall time of both SDA and SCL                          | t <sub>1</sub><br>CC/SR  | 20 +<br>0.1*C <sub>b</sub> | -      | 300  | ns   |                |

| Rise time of both SDA and SCL                          | t <sub>2</sub><br>CC/SR  | 20 +<br>0.1*C <sub>b</sub> | -      | 300  | ns   |                |

| Data hold time                                         | t <sub>3</sub><br>CC/SR  | 0                          | -      | -    | μs   |                |

| Data set-up time                                       | t <sub>4</sub><br>CC/SR  | 100                        | -      | -    | ns   |                |

| LOW period of SCL clock                                | t <sub>5</sub><br>CC/SR  | 1.3                        | -      | -    | μs   |                |

| HIGH period of SCL clock                               | t <sub>6</sub><br>CC/SR  | 0.6                        | -      | -    | μs   |                |

| Hold time for (repeated)<br>START condition            | t <sub>7</sub><br>CC/SR  | 0.6                        | -      | -    | μs   |                |

| Set-up time for repeated START condition               | t <sub>8</sub><br>CC/SR  | 0.6                        | -      | -    | μs   |                |

| Set-up time for STOP condition                         | t <sub>9</sub><br>CC/SR  | 0.6                        | -      | -    | μs   |                |

| Bus free time between a<br>STOP and START<br>condition | t <sub>10</sub><br>CC/SR | 1.3                        | -      | -    | μs   |                |

| Capacitive load for each bus line                      | C <sub>b</sub> SR        | -                          | -      | 400  | pF   |                |

Due to the wired-AND configuration of an IIC bus system, the port drivers of the SCL and SDA signal lines need to operate in open-drain mode. The high level on these lines must be held by an external pull-up device, approximately 10 kOhm for operation at 100 kbit/s, approximately 2 kOhm for operation at 400 kbit/s.

2) C<sub>b</sub> refers to the total capacitance of one bus line in pF.

## Figure 34 USIC IIC Stand and Fast Mode Timing

## 3.3.9.4 Inter-IC Sound (IIS) Interface Timing

The following parameters are applicable for a USIC channel operated in IIS mode.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Parameter       | Symbol            |                   | Values | ues Unit          |    | Note /         |

|-----------------|-------------------|-------------------|--------|-------------------|----|----------------|

|                 |                   | Min.              | Тур.   | Max.              |    | Test Condition |

| Clock period    | t <sub>1</sub> CC | 33.3              | -      | -                 | ns |                |

| Clock high time | t <sub>2</sub> CC | 0.35 x            | -      | _                 | ns |                |

|                 |                   | t <sub>1min</sub> |        |                   |    |                |

| Clock low time  | t <sub>3</sub> CC | 0.35 x            | _      | -                 | ns |                |

|                 |                   | t <sub>1min</sub> |        |                   |    |                |

| Hold time       | t <sub>4</sub> CC | 0                 | -      | -                 | ns |                |

| Clock rise time | t <sub>5</sub> CC | _                 | -      | 0.15 x            | ns |                |

|                 |                   |                   |        | t <sub>1min</sub> |    |                |

93

### Table 50 USIC IIS Master Transmitter Timing

| No clock delay:   |                                                                                                                                                            |     |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|                   |                                                                                                                                                            | (7) |

|                   | $t_{ODLY\_H} + t_{DATA\_DELAY} + t_{TAP\_DELAY} + t_{ISU} < t_{WL}$                                                                                        |     |

| With clock delay: |                                                                                                                                                            |     |

|                   | $t_{ODLY H} + t_{DATA DELAY} + t_{TAP DELAY} + t_{ISU} < t_{WL} + t_{CLK DELAY}$                                                                           | (8) |

|                   | CODLY_H + *DATA_DELAY + *TAP_DELAY + *ISU > *WL + *CLK_DELAY                                                                                               |     |

|                   |                                                                                                                                                            | (9) |

|                   | $t_{\text{DATA}\_\text{DELAY}} + t_{\text{TAP}\_\text{DELAY}} - t_{\text{CLK}\_\text{DELAY}} < t_{\text{WL}} - t_{\text{ISU}} - t_{\text{ODLY}\_\text{H}}$ |     |

|                   | $t_{\text{DATA}\_\text{DELAY}} - t_{\text{CLK}\_\text{DELAY}} < t_{\text{WL}} - t_{\text{ISU}} - t_{\text{ODLY}\_H} - t_{\text{TAP}\_\text{DELAY}}$        |     |

|                   | $t_{DATA\_DELAY} - t_{CLK\_DELAY} < 10 - 6 - 14 - t_{TAP\_DELAY}$                                                                                          |     |

|                   | $t_{\text{DATA\_DELAY}} - t_{\text{CLK\_DELAY}} < -10 - t_{\text{TAP\_DELAY}}$                                                                             |     |

The data delay is less than the clock delay by at least 10 ns in the ideal case where  $t_{WL}$ = 10 ns.

## High-Speed Write Meeting Hold (Minimum Delay)

The following equations show how to calculate the allowed skew range between the SD\_CLK and SD\_DAT/CMD signals on the PCB.

(10)

$t_{\mathrm{CLK\_DELAY}} < t_{WL} + t_{\mathrm{OH\_H}} + t_{\mathrm{DATA\_DELAY}} + t_{\mathrm{TAP\_DELAY}} - t_{\mathrm{IH}}$

$t_{\mathrm{CLK\_DELAY}} - t_{\mathrm{DATA\_DELAY}} < t_{\mathrm{WL}} + t_{\mathrm{OH\_H}} + t_{\mathrm{TAP\_DELAY}} - t_{\mathrm{IH}}$

$t_{\text{CLK\_DELAY}} - t_{\text{DATA\_DELAY}} < 10 + 2 + t_{\text{TAP\_DELAY}} - 2$

$t_{\rm CLK\_DELAY} - t_{\rm DATA\_DELAY} < 10 + t_{\rm TAP\_DELAY}$

The clock can be delayed versus data up to 13.2 ns (external delay line) in ideal case of  $t_{WL}$ = 10 ns, with maximum  $t_{TAP DELAY}$  = 3.2 ns programmed.

# 3.3.10.2 EBU Burst Mode Access Timing

- Note: These parameters are not subject to production test, but verified by design and/or characterization.

- Note: Operating Conditions apply, with Class A2 pins and  $C_1 = 16 \text{ pF}$ .

| Parameter                                                                 | Symbol                  |    |      | Values | 5    | Unit | Note /         |

|---------------------------------------------------------------------------|-------------------------|----|------|--------|------|------|----------------|

|                                                                           |                         |    | Min. | Тур.   | Max. |      | Test Condition |

| Output delay from BFCLKO rising edge                                      | <i>t</i> <sub>10</sub>  | СС | -2   | -      | 2    | ns   | -              |

| RD and RD/WR<br>active/inactive after<br>BFCLKO active edge <sup>1)</sup> | t <sub>12</sub>         | CC | -2   | -      | 2    | ns   | -              |

| CSx output delay from<br>BFCLKO active edge <sup>1)</sup>                 | t <sub>21</sub>         | CC | -2.5 | -      | 1.5  | ns   | -              |

| ADV active/inactive after<br>BFCLKO active edge <sup>2)</sup>             | t <sub>22</sub>         | CC | -2   | -      | 2    | ns   | _              |

| BAA active/inactive after<br>BFCLKO active edge <sup>2)</sup>             | <i>t</i> <sub>22a</sub> | CC | -2.5 | -      | 1.5  | ns   | -              |

| Data setup to BFCLKI rising edge <sup>3)</sup>                            | <i>t</i> <sub>23</sub>  | SR | 3    | -      | -    | ns   | -              |

| Data hold from BFCLKI rising edge <sup>3)</sup>                           | <i>t</i> <sub>24</sub>  | SR | 0    | -      | -    | ns   | -              |

| WAIT setup (low or high) to BFCLKI rising edge <sup>3)</sup>              | t <sub>25</sub>         | SR | 3    | -      | -    | ns   | -              |

| WAIT hold (low or high) from BFCLKI rising edge <sup>3)</sup>             | t <sub>26</sub>         | SR | 0    | -      | -    | ns   | -              |

### Table 59 EBU Burst Mode Read / Write Access Timing Parameters

1) An active edge can be a rising or falling edge, depending on the settings of bits BFCON.EBSE / ECSE and the clock divider ratio.

Negative minimum values for these parameters mean that the last data read during a burst may be corrupted. However, with clock feedback enabled, this value is an oversampling not required for the internal bus transaction, and will be discarded.

2) This parameter is valid for BUSCONx.EBSE = 1 and BUSAPx.EXTCLK = 00<sub>B</sub>.

For BUSCONx.EBSE = 1 and other values of BUSAPx.EXTCLK, ADV and BAA will be delayed by 1/2 of the internal bus clock period  $T_{CPU}$  = 1 /  $f_{CPU}$ .

For BUSCONx. EBSE = 0 and BUSAPx.EXTCLK =  $11_B$ , add 2 internal bus clock periods.

For BUSCONx. EBSE = 0 and other values of BUSAPx.EXTCLK, add 1 internal bus clock period.

## XMC4700 / XMC4800 XMC4000 Family

### **Electrical Parameters**

Figure 48 EBU SDRAM Read Access Timing

## Package and Reliability

The difference between junction temperature and ambient temperature is determined by  $\Delta T = (P_{INT} + P_{IOSTAT} + P_{IODYN}) \times R_{\Theta JA}$

The internal power consumption is defined as

$P_{\text{INT}} = V_{\text{DDP}} \times I_{\text{DDP}}$  (switching current and leakage current).

The static external power consumption caused by the output drivers is defined as  $P_{\text{IOSTAT}} = \Sigma((V_{\text{DDP}} - V_{\text{OH}}) \times I_{\text{OH}}) + \Sigma(V_{\text{OI}} \times I_{\text{OI}})$

The dynamic external power consumption caused by the output drivers ( $P_{IODYN}$ ) depends on the capacitive load connected to the respective pins and their switching frequencies.

If the total power dissipation for a given system configuration exceeds the defined limit, countermeasures must be taken to ensure proper system operation:

- Reduce  $V_{\text{DDP}}$ , if possible in the system

- Reduce the system frequency

- Reduce the number of output pins

- Reduce the load on active output drivers

# 4.2 Package Outlines

The availability of different packages for different devices types is listed in Table 1.

The exposed die pad dimensions are listed in Table 71.

www.infineon.com

Published by Infineon Technologies AG