Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                      |

|----------------------------|---------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                             |

| Core Size                  | 32-Bit Single-Core                                                                          |

| Speed                      | 144MHz                                                                                      |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, LINbus, MMC/SD, SPI, UART/USART, USB OTG, USIC |

| Peripherals                | DMA, I <sup>2</sup> S, LED, POR, Touch-Sense, WDT                                           |

| Number of I/O              | 75                                                                                          |

| Program Memory Size        | 1.5MB (1.5M x 8)                                                                            |

| Program Memory Type        | FLASH                                                                                       |

| EEPROM Size                | -                                                                                           |

| RAM Size                   | 276К х 8                                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 3.63V                                                                               |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                       |

| Oscillator Type            | External                                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                           |

| Mounting Type              | Surface Mount                                                                               |

| Package / Case             | 100-LQFP Exposed Pad                                                                        |

| Supplier Device Package    | PG-LQFP-100-25                                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xmc4800f100f1536aaxqma1          |

|                            |                                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# XMC4700 / XMC4800

Microcontroller Series for Industrial Applications

XMC4000 Family

ARM<sup>®</sup> Cortex<sup>®</sup>-M4 32-bit processor core

Data Sheet V1.0 2016-01

## Microcontrollers

#### XMC4[78]00 Data Sheet

#### Revision History: V1.0 2016-01

Previous Versions: V0.7 2015-10 (preliminary)

| Page  | Subjects                                                                                                                                   |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 8     | Corrected EtherCAT features to 8 Fieldbus Memory Management Units (FMMU) and 8 Sync Manager.                                               |

| 46    | Added footnote explaining minimum $V_{\text{BAT}}$ requirements to start the hibernate domain and/or oscillation of a crystal on RTC_XTAL. |

| 53    | Added HIBIO characteristics.                                                                                                               |

| 58    | Corrected DAC INL and gain error.                                                                                                          |

| 70    | Changed frequency dependency of the current consumption.                                                                                   |

| 73    | Added peripheral idle current overview.                                                                                                    |

| 127ff | Updated package parameters and drawings.                                                                                                   |

| 132   | Higher HBM and CDM ESD limits.                                                                                                             |

#### Trademarks

C166<sup>™</sup>, TriCore<sup>™</sup>, XMC<sup>™</sup> and DAVE<sup>™</sup> are trademarks of Infineon Technologies AG.

ARM<sup>®</sup>, ARM Powered<sup>®</sup>, Cortex<sup>®</sup>, Thumb<sup>®</sup> and AMBA<sup>®</sup> are registered trademarks of ARM, Limited.

CoreSight<sup>™</sup>, ETM<sup>™</sup>, Embedded Trace Macrocell<sup>™</sup> and Embedded Trace Buffer<sup>™</sup> are trademarks of ARM, Limited.

Synopsys<sup>™</sup> is a trademark of Synopsys, Inc.

#### We Listen to Your Comments

Is there any information in this document that you feel is wrong, unclear or missing? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to: mcdocu.comments@infineon.com

#### About this Document

## About this Document

This Data Sheet is addressed to embedded hardware and software developers. It provides the reader with detailed descriptions about the ordering designations, available features, electrical and physical characteristics of the XMC4[78]00 series devices.

The document describes the characteristics of a superset of the XMC4[78]00 series devices. For simplicity, the various device types are referred to by the collective term XMC4[78]00 throughout this manual.

#### XMC4000 Family User Documentation

The set of user documentation includes:

- Reference Manual

- decribes the functionality of the superset of devices.

- Data Sheets

- list the complete ordering designations, available features and electrical characteristics of derivative devices.

- Errata Sheets

- list deviations from the specifications given in the related Reference Manual or Data Sheets. Errata Sheets are provided for the superset of devices.

## Attention: Please consult all parts of the documentation set to attain consolidated knowledge about your device.

Application related guidance is provided by Users Guides and Application Notes.

Please refer to http://www.infineon.com/xmc4000 to get access to the latest versions of those documents.

#### Summary of Features

#### **On-Chip Memories**

- 16 KB on-chip boot ROM

- 96 KB on-chip high-speed program memory

- 128 KB on-chip high speed data memory

- 128 KB on-chip high-speed communication memory

- 2,048 KB on-chip Flash Memory with 8 KB instruction cache

#### **Communication Peripherals**

- Ethernet MAC module capable of 10/100 Mbit/s transfer rates

- EtherCATSlave interface (ECAT) capable of 100 Mbit/s transfer rates with 2 MII ports, 8 Fieldbus Memory Management Units (FMMU), 8 Sync Manager, 64 bit distributed clocks

- Universal Serial Bus, USB 2.0 host, Full-Speed OTG, with integrated PHY

- Controller Area Network interface (MultiCAN), Full-CAN/Basic-CAN with 6 nodes, 256 message objects (MO), data rate up to 1 MBaud

- Six Universal Serial Interface Channels (USIC), providing 6 serial channels, usable as UART, double-SPI, quad-SPI, IIC, IIS and LIN interfaces

- LED and Touch-Sense Controller (LEDTS) for Human-Machine interface

- SD and Multi-Media Card interface (SDMMC) for data storage memory cards

- External Bus Interface Unit (EBU) enabling communication with external memories and off-chip peripherals

#### **Analog Frontend Peripherals**

- Four Analog-Digital Converters (VADC) of 12-bit resolution, 8 channels each, with input out-of-range comparators

- Delta Sigma Demodulator with four channels, digital input stage for A/D signal conversion

- Digital-Analog Converter (DAC) with two channels of 12-bit resolution

#### **Industrial Control Peripherals**

- Two Capture/Compare Units 8 (CCU8) for motor control and power conversion

- · Four Capture/Compare Units 4 (CCU4) for use as general purpose timers

- Two Position Interfaces (POSIF) for servo motor positioning

- Window Watchdog Timer (WDT) for safety sensitive applications

- Die Temperature Sensor (DTS)

- · Real Time Clock module with alarm support

- System Control Unit (SCU) for system configuration and control

#### Input/Output Lines

- Programmable port driver control module (PORTS)

- Individual bit addressability

#### **Summary of Features**

#### Table 1Synopsis of XMC4[78]00 Device Types (cont'd)

| Derivative <sup>1)</sup> | Package      | Flash<br>Kbytes | SRAM<br>Kbytes |  |

|--------------------------|--------------|-----------------|----------------|--|

| XMC4700-F144x1536        | PG-LQFP-144  | 1536            | 276            |  |

| XMC4700-F100x1536        | PG-LQFP-100  | 1536            | 276            |  |

| XMC4800-E196x2048        | PG-LFBGA-196 | 2048            | 352            |  |

| XMC4800-F144x2048        | PG-LQFP-144  | 2048            | 352            |  |

| XMC4800-F100x2048        | PG-LQFP-100  | 2048            | 352            |  |

| XMC4800-E196x1536        | PG-LFBGA-196 | 1536            | 276            |  |

| XMC4800-F144x1536        | PG-LQFP-144  | 1536            | 276            |  |

| XMC4800-F100x1536        | PG-LQFP-100  | 1536            | 276            |  |

| XMC4800-E196x1024        | PG-LFBGA-196 | 1024            | 200            |  |

| XMC4800-F144x1024        | PG-LQFP-144  | 1024            | 200            |  |

| XMC4800-F100x1024        | PG-LQFP-100  | 1024            | 200            |  |

1) x is a placeholder for the supported temperature range.

## 1.3 Device Type Features

The following table lists the available features per device type.

## Table 2 Features of XMC4[78]00 Device Types

| Derivative <sup>1)</sup> | LED<br>TS<br>Intf. | SD<br>MMC<br>Intf. | EBU<br>Intf. <sup>2)</sup> | ETH<br>Intf.<br>3) | ECAT<br>Slave<br>Intf. | USB<br>Intf. | USIC<br>Chan. | MultiCAN<br>Nodes,<br>MO |

|--------------------------|--------------------|--------------------|----------------------------|--------------------|------------------------|--------------|---------------|--------------------------|

| XMC4700-E196x2048        | 1                  | 1                  | SDM                        | MR                 | -                      | 1            | 3 x 2         | N[05]<br>MO[0255]        |

| XMC4700-F144x2048        | 1                  | 1                  | SDM                        | MR                 | -                      | 1            | 3 x 2         | N[05]<br>MO[0255]        |

| XMC4700-F100x2048        | 1                  | 1                  | M16                        | R                  | -                      | 1            | 3 x 2         | N[05]<br>MO[0255]        |

| XMC4700-E196x1536        | 1                  | 1                  | SDM                        | MR                 | -                      | 1            | 3 x 2         | N[05]<br>MO[0255]        |

| XMC4700-F144x1536        | 1                  | 1                  | SDM                        | MR                 | -                      | 1            | 3 x 2         | N[05]<br>MO[0255]        |

| XMC4700-F100x1536        | 1                  | 1                  | M16                        | R                  | -                      | 1            | 3 x 2         | N[05]<br>MO[0255]        |

## XMC4700 / XMC4800 XMC4000 Family

#### **General Device Information**

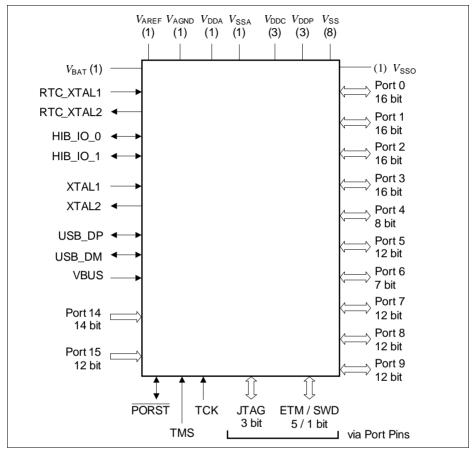

Figure 3 XMC4[78]00 Logic Symbol PG-LFBGA-196

. . . .

## XMC4700 / XMC4800 XMC4000 Family

#### **General Device Information**

| Table 10         Package Pin Mapping (cont'd) |           |          |          |                   |       |  |  |  |

|-----------------------------------------------|-----------|----------|----------|-------------------|-------|--|--|--|

| Function                                      | LFBGA-196 | LQFP-144 | LQFP-100 | Pad Type          | Notes |  |  |  |

| P8.5                                          | B5        | -        | -        | A1+               |       |  |  |  |

| P8.6                                          | A2        | -        | -        | A1+               |       |  |  |  |

| P8.7                                          | B4        | -        | -        | A1+               |       |  |  |  |

| P8.8                                          | A3        | -        | -        | A2                |       |  |  |  |

| P8.9                                          | A5        | -        | -        | A1+               |       |  |  |  |

| P8.10                                         | A4        | -        | -        | A1+               |       |  |  |  |

| P8.11                                         | A6        | -        | -        | A1+               |       |  |  |  |

| P9.0                                          | F13       | -        | -        | A2                |       |  |  |  |

| P9.1                                          | E14       | -        | -        | A2                |       |  |  |  |

| P9.2                                          | D14       | -        | -        | A1+               |       |  |  |  |

| P9.3                                          | D13       | -        | -        | A2                |       |  |  |  |

| P9.4                                          | A12       | -        | -        | A1+               |       |  |  |  |

| P9.5                                          | A11       | -        | -        | A1+               |       |  |  |  |

| P9.6                                          | B11       | -        | -        | A1+               |       |  |  |  |

| P9.7                                          | A9        | -        | -        | A1+               |       |  |  |  |

| P9.8                                          | A8        | -        | -        | A1+               |       |  |  |  |

| P9.9                                          | A10       | -        | -        | A1+               |       |  |  |  |

| P9.10                                         | B8        | -        | -        | A1+               |       |  |  |  |

| P9.11                                         | B9        | -        | -        | A1+               |       |  |  |  |

| P14.0                                         | N3        | 42       | 31       | AN/DIG_IN         |       |  |  |  |

| P14.1                                         | N2        | 41       | 30       | AN/DIG_IN         |       |  |  |  |

| P14.2                                         | M3        | 40       | 29       | AN/DIG_IN         |       |  |  |  |

| P14.3                                         | L4        | 39       | 28       | AN/DIG_IN         |       |  |  |  |

| P14.4                                         | M1        | 38       | 27       | AN/DIG_IN         |       |  |  |  |

| P14.5                                         | M2        | 37       | 26       | AN/DIG_IN         |       |  |  |  |

| P14.6                                         | L3        | 36       | 25       | AN/DIG_IN         |       |  |  |  |

| P14.7                                         | L2        | 35       | 24       | AN/DIG_IN         |       |  |  |  |

| P14.8                                         | P5        | 52       | 37       | AN/DAC/DI<br>G_IN |       |  |  |  |

| P14.9                                         | N5        | 51       | 36       | AN/DAC/DI<br>G_IN |       |  |  |  |

| P14.12                                        | L1        | 34       | 23       | AN/DIG_IN         |       |  |  |  |

| P14.13                                        | K4        | 33       | 22       | AN/DIG_IN         |       |  |  |  |

. ..

- -

## 3.1.2 Absolute Maximum Ratings

Stresses above the values listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

| Parameter                                                                                                     | Symbol               |    |           | Va | lues                                  | Unit | Note /                |  |

|---------------------------------------------------------------------------------------------------------------|----------------------|----|-----------|----|---------------------------------------|------|-----------------------|--|

|                                                                                                               |                      |    | Min. Typ. |    | Max.                                  |      | Test Con<br>dition    |  |

| Storage temperature                                                                                           | $T_{\rm ST}$         | SR | -65       | -  | 150                                   | °C   | _                     |  |

| Junction temperature                                                                                          | $T_{J}$              | SR | -40       | -  | 150                                   | °C   | _                     |  |

| Voltage at 3.3 V power supply pins with respect to $V_{\rm SS}$                                               | $V_{DDP}$            | SR | -         | -  | 4.3                                   | V    | -                     |  |

| Voltage on any Class A and dedicated input pin with respect to $V_{\rm SS}$                                   | V <sub>IN</sub>      | SR | -1.0      | -  | V <sub>DDP</sub> + 1.0<br>or max. 4.3 | V    | whichever<br>is lower |  |

| Voltage on any analog input pin with respect to $V_{\rm AGND}$                                                | $V_{AIN}$ $V_{AREF}$ | SR | -1.0      | -  | V <sub>DDP</sub> + 1.0<br>or max. 4.3 | V    | whichever<br>is lower |  |

| Input current on any pin<br>during overload condition                                                         | I <sub>IN</sub>      | SR | -10       | -  | +10                                   | mA   |                       |  |

| Absolute maximum sum of all input circuit currents for one port group during overload condition <sup>1)</sup> | $\Sigma I_{\rm IN}$  | SR | -25       | -  | +25                                   | mA   |                       |  |

| Absolute maximum sum of all<br>input circuit currents during<br>overload condition                            | $\Sigma I_{\rm IN}$  | SR | -100      | -  | +100                                  | mA   |                       |  |

#### Table 13 Absolute Maximum Rating Parameters

1) The port groups are defined in **Table 17**.

**Figure 10** explains the input voltage ranges of  $V_{\rm IN}$  and  $V_{\rm AIN}$  and its dependency to the supply level of  $V_{\rm DDP}$ . The input voltage must not exceed 4.3 V, and it must not be more than 1.0 V above  $V_{\rm DDP}$ . For the range up to  $V_{\rm DDP}$  + 1.0 V also see the definition of the overload conditions in Section 3.1.3.

## 3.2.9 Flash Memory Parameters

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Parameter                                                                 | Symbol                                      |       | Values    | 5   | Unit   | Note /                                                                                    |  |

|---------------------------------------------------------------------------|---------------------------------------------|-------|-----------|-----|--------|-------------------------------------------------------------------------------------------|--|

|                                                                           |                                             | Min.  | Typ. Max. |     |        | Test Condition                                                                            |  |

| Erase Time per 256<br>Kbyte Sector                                        | $t_{\sf ERP}\sf CC$                         | -     | 5         | 5.5 | S      |                                                                                           |  |

| Erase Time per 64 Kbyte<br>Sector                                         | t <sub>ERP</sub> CC                         | -     | 1.2       | 1.4 | S      |                                                                                           |  |

| Erase Time per 16 Kbyte<br>Logical Sector                                 | t <sub>ERP</sub> CC                         | -     | 0.3       | 0.4 | S      |                                                                                           |  |

| Program time per page <sup>1)</sup>                                       | $t_{\sf PRP}\sf CC$                         | -     | 5.5       | 11  | ms     |                                                                                           |  |

| Erase suspend delay                                                       | t <sub>FL_ErSusp</sub>                      | -     | -         | 15  | ms     |                                                                                           |  |

| Wait time after margin change                                             | t <sub>FL_Margin</sub><br><sub>Del</sub> CC | 10    | -         | -   | μs     |                                                                                           |  |

| Wake-up time                                                              | t <sub>WU</sub> CC                          | -     | -         | 270 | μS     |                                                                                           |  |

| Read access time                                                          | t <sub>a</sub> CC                           | 22    | -         | _   | ns     | For operation<br>with $1/f_{CPU} < t_a$<br>wait states must<br>be configured <sup>2</sup> |  |

| Data Retention Time,<br>Physical Sector <sup>3)4)</sup>                   | t <sub>RET</sub> CC                         | 20    | -         | -   | years  | Max. 1000<br>erase/program<br>cycles                                                      |  |

| Data Retention Time,<br>Logical Sector <sup>3)4)</sup>                    | t <sub>RETL</sub> CC                        | 20    | -         | -   | years  | Max. 100<br>erase/program<br>cycles                                                       |  |

| Data Retention Time,<br>User Configuration Block<br>(UCB) <sup>3)4)</sup> | t <sub>RTU</sub> CC                         | 20    | -         | _   | years  | Max. 4<br>erase/program<br>cycles per UCB                                                 |  |

| Endurance on 64 Kbyte<br>Physical Sector PS4                              | N <sub>EPS4</sub><br>CC                     | 10000 | -         | _   | cycles | Cycling<br>distributed over<br>life time <sup>5)</sup>                                    |  |

#### Table 36 Flash Memory Parameters

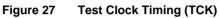

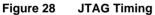

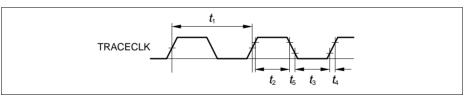

## 3.3.8 Embedded Trace Macro Cell (ETM) Timing

The data timing refers to the active clock edge. The XMC4[78]00 ETM uses the half-rate clocking mode. In this mode both, the rising and falling clock edges are active clock edges.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

Note: Operating conditions apply, with  $C_L \leq 15 \text{ pF}$ .

| Parameter                           | Symbol                |    | Values |      |      | Unit | Note /         |  |

|-------------------------------------|-----------------------|----|--------|------|------|------|----------------|--|

|                                     |                       |    | Min.   | Тур. | Max. |      | Test Condition |  |

| TRACECLK period                     | <i>t</i> <sub>1</sub> | СС | 13.8   | -    | -    | ns   | -              |  |

| TRACECLK high time                  | <i>t</i> <sub>2</sub> | СС | 2      | -    | -    | ns   | -              |  |

| TRACECLK low time                   | $t_3$                 | СС | 2      | -    | -    | ns   | -              |  |

| TRACECLK and<br>TRACEDATA rise time | <i>t</i> <sub>4</sub> | СС | -      | -    | 3    | ns   | -              |  |

| TRACECLK and<br>TRACEDATA fall time | <i>t</i> <sub>5</sub> | СС | -      | -    | 3    | ns   | -              |  |

| TRACEDATA output valid time         | <i>t</i> <sub>6</sub> | CC | -2     | -    | 3    | ns   | -              |  |

#### Table 44 ETM Interface Timing Parameters

#### Figure 30 ETM Clock Timing

#### Figure 31 ETM Data Timing

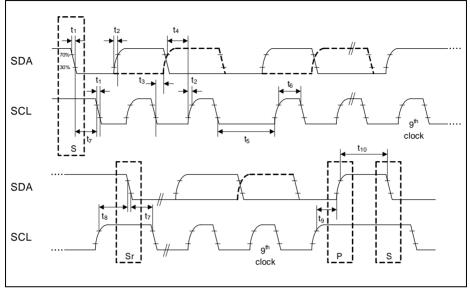

## Figure 34 USIC IIC Stand and Fast Mode Timing

## 3.3.9.4 Inter-IC Sound (IIS) Interface Timing

The following parameters are applicable for a USIC channel operated in IIS mode.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Parameter       | Symbol            |                   | Values | 5                 | Unit | Note /         |

|-----------------|-------------------|-------------------|--------|-------------------|------|----------------|

|                 |                   | Min.              | Тур.   | Max.              |      | Test Condition |

| Clock period    | t <sub>1</sub> CC | 33.3              | -      | -                 | ns   |                |

| Clock high time | t <sub>2</sub> CC | 0.35 x            | -      | _                 | ns   |                |

|                 |                   | t <sub>1min</sub> |        |                   |      |                |

| Clock low time  | t <sub>3</sub> CC | 0.35 x            | _      | -                 | ns   |                |

|                 |                   | t <sub>1min</sub> |        |                   |      |                |

| Hold time       | t <sub>4</sub> CC | 0                 | -      | -                 | ns   |                |

| Clock rise time | t <sub>5</sub> CC | _                 | -      | 0.15 x            | ns   |                |

|                 |                   |                   |        | t <sub>1min</sub> |      |                |

93

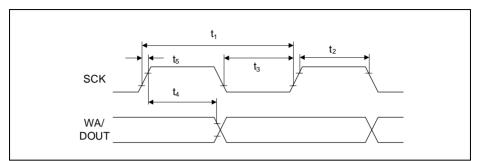

#### Table 50 USIC IIS Master Transmitter Timing

| Figure 35 | USIC IIS Master | Transmitter Timing |  |

|-----------|-----------------|--------------------|--|

|-----------|-----------------|--------------------|--|

| Parameter       | Symbol                    | Values                      |      |      | Unit | Note /         |  |

|-----------------|---------------------------|-----------------------------|------|------|------|----------------|--|

|                 |                           | Min.                        | Тур. | Max. |      | Test Condition |  |

| Clock period    | t <sub>6</sub> SR         | 66.6                        | _    | -    | ns   |                |  |

| Clock high time | t <sub>7</sub> SR         | 0.35 x<br>t <sub>6min</sub> | -    | -    | ns   |                |  |

| Clock low time  | t <sub>8</sub> SR         | 0.35 x<br>t <sub>6min</sub> | -    | -    | ns   |                |  |

| Set-up time     | t <sub>9</sub> SR         | 0.2 x<br>t <sub>6min</sub>  | -    | -    | ns   |                |  |

| Hold time       | <i>t</i> <sub>10</sub> SR | 0                           | -    | -    | ns   |                |  |

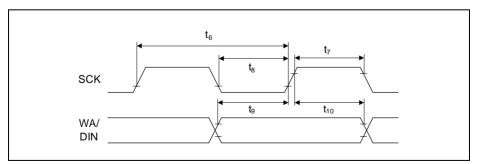

Figure 36 USIC IIS Slave Receiver Timing

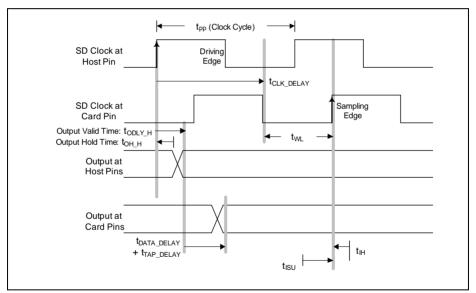

#### Table 53SD Card Bus Timing for Full-Speed Mode<sup>1)</sup> (cont'd)

| Parameter                 | Symbol            | Value | s    | Unit | Note/ Test |  |

|---------------------------|-------------------|-------|------|------|------------|--|

|                           |                   | Min.  | Max. |      | Condition  |  |

| SD card output valid time | t <sub>ODLY</sub> | -     | 14   | ns   |            |  |

| SD card output hold time  | t <sub>OH</sub>   | 0     | -    | ns   |            |  |

1) Reference card timing values for calculation examples. Not subject to production test and not characterized.

#### Full-Speed Output Path (Write)

#### Figure 37 Full-Speed Output Path

#### Full-Speed Write Meeting Setup (Maximum Delay)

The following equations show how to calculate the allowed skew range between the SD\_CLK and SD\_DAT/CMD signals on the PCB.

No clock delay:

$t_{ODLY\_F} + t_{DATA\_DELAY} + t_{TAP\_DELAY} + t_{ISU} < t_{WL}$

| Parameter                         |                    |    | Symbol                 | Limit Values |      | Unit |

|-----------------------------------|--------------------|----|------------------------|--------------|------|------|

|                                   |                    |    |                        | Min.         | Max. | 1    |

| A(15:0) output valid              | from SDCLKO        | CC | t <sub>6</sub>         | -            | 9    | ns   |

| A(15:0) output hold               | low-to-high        | CC | <i>t</i> <sub>7</sub>  | 3            | -    |      |

| CS(3:0) low                       | - transition       | CC | t <sub>8</sub>         | -            | 9    |      |

| CS(3:0) high                      | -                  | CC | t <sub>9</sub>         | 3            | -    |      |

| RAS low                           | -                  | CC | <i>t</i> <sub>10</sub> | -            | 9    |      |

| RAS high                          |                    | SR | t <sub>11</sub>        | 3            | -    |      |

| CAS low                           |                    | SR | t <sub>12</sub>        | -            | 9    |      |

| CAS high                          |                    | CC | t <sub>13</sub>        | 3            | -    |      |

| RD/WR low                         | -                  | CC | t <sub>14</sub>        | -            | 9    |      |

| RD/WR high                        | -                  | CC | t <sub>15</sub>        | 3            | -    |      |

| BC(3:0) low                       |                    | CC | t <sub>16</sub>        | -            | 9    |      |

| BC(3:0) high                      | -                  | CC | t <sub>17</sub>        | 3            | -    |      |

| D(15:0) output valid              | -                  | CC | t <sub>18</sub>        | -            | 9    |      |

| D(15:0) output hold               |                    | CC | t <sub>19</sub>        | 3            | -    |      |

| CKE output valid <sup>1)</sup>    |                    | CC | t <sub>22</sub>        | -            | 7    |      |

| CKE output hold <sup>1)</sup>     | -                  | CC | t <sub>23</sub>        | 2            | -    |      |

| D(15:0) input hold                |                    | SR | t <sub>21</sub>        | 3            | -    |      |

| D(15:0) input setup to transition | SDCLKO low-to-high | SR | t <sub>20</sub>        | 4            | -    |      |

## Table 62 EBU SDRAM Access Signal Timing Parameters

1) Not depicted in the read and write access timing figures below.

## 3.3.12 Ethernet Interface (ETH) Characteristics

For proper operation of the Ethernet Interface it is required that  $f_{SYS} \ge 100 \text{ MHz}$ .

Note: These parameters are not subject to production test, but verified by design and/or characterization.

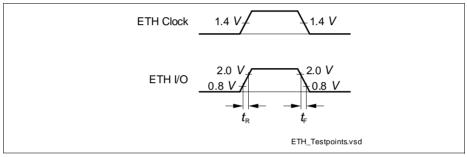

## 3.3.12.1 ETH Measurement Reference Points

Figure 51 ETH Measurement Reference Points

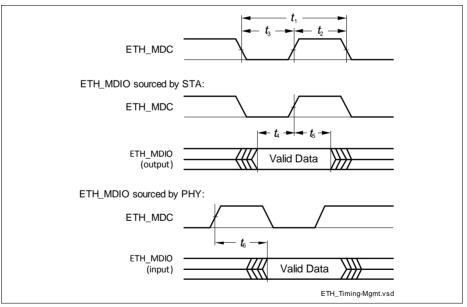

## 3.3.12.2 ETH Management Signal Parameters (ETH\_MDC, ETH\_MDIO)

| Parameter                    |                       | nbol | Values |      |      | Unit | Note /                 |

|------------------------------|-----------------------|------|--------|------|------|------|------------------------|

|                              |                       |      | Min.   | Тур. | Max. | -    | Test Conditi<br>on     |

| ETH_MDC period               | <i>t</i> <sub>1</sub> | CC   | 400    | -    | -    | ns   | C <sub>L</sub> = 25 pF |

| ETH_MDC high time            | <i>t</i> <sub>2</sub> | CC   | 160    | -    | -    | ns   |                        |

| ETH_MDC low time             | t <sub>3</sub>        | CC   | 160    | _    | -    | ns   |                        |

| ETH_MDIO setup time (output) | $t_4$                 | CC   | 10     | -    | -    | ns   |                        |

| ETH_MDIO hold time (output)  | $t_5$                 | CC   | 10     | -    | -    | ns   |                        |

| ETH_MDIO data valid (input)  | $t_6$                 | SR   | 0      | —    | 300  | ns   |                        |

#### Table 64 ETH Management Signal Timing Parameters

Figure 52 ETH Management Signal Timing

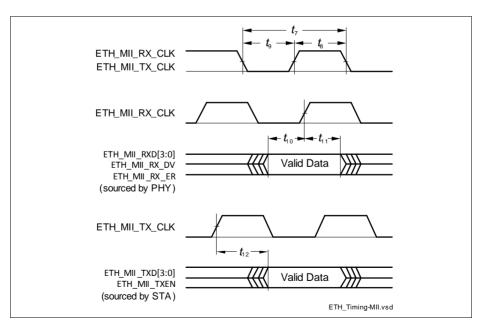

## 3.3.12.3 ETH MII Parameters

In the following, the parameters of the MII (Media Independent Interface) are described.

| Parameter                 |                        | Symbol |      | Values |      |    | Note /                 |

|---------------------------|------------------------|--------|------|--------|------|----|------------------------|

|                           |                        |        | Min. | Тур.   | Max. |    | Test Condition         |

| Clock period, 10 Mbps     | <i>t</i> <sub>7</sub>  | SR     | 400  | -      | -    | ns | C <sub>L</sub> = 25 pF |

| Clock high time, 10 Mbps  | <i>t</i> <sub>8</sub>  | SR     | 140  | -      | 260  | ns | -                      |

| Clock low time, 10 Mbps   | t <sub>9</sub>         | SR     | 140  | -      | 260  | ns | -                      |

| Clock period, 100 Mbps    | <i>t</i> <sub>7</sub>  | SR     | 40   | -      | -    | ns | -                      |

| Clock high time, 100 Mbps | <i>t</i> <sub>8</sub>  | SR     | 14   | -      | 26   | ns | -                      |

| Clock low time, 100 Mbps  | t <sub>9</sub>         | SR     | 14   | -      | 26   | ns |                        |

| Input setup time          | <i>t</i> <sub>10</sub> | SR     | 10   | -      | -    | ns | -                      |

| Input hold time           | <i>t</i> <sub>11</sub> | SR     | 10   | -      | -    | ns |                        |

| Output valid time         | <i>t</i> <sub>12</sub> | CC     | 0    | -      | 25   | ns |                        |

Table 65 ETH MII Signal Timing Parameters

#### Figure 53 ETH MII Signal Timing

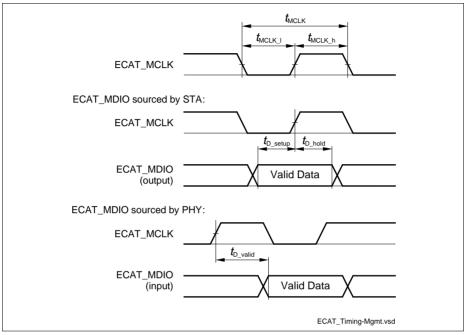

## 3.3.13.3 MII Timing TX Characteristics

| Table 68 | ETH MII TX Signal Timing Parameters |

|----------|-------------------------------------|

|----------|-------------------------------------|

| Parameter                                                                   | Symbol                       | Values |      |      | Unit | Note /         |

|-----------------------------------------------------------------------------|------------------------------|--------|------|------|------|----------------|

|                                                                             |                              | Min.   | Тур. | Max. |      | Test Condition |

| PHY_CLK25, TX_CLK period                                                    | t <sub>TX_CLK</sub><br>SR    | -      | 40   | -    | ns   |                |

| Delay between PHY clock<br>source PHY_CLK25 and<br>TX_CLK output of the PHY | t <sub>PHY_delay</sub><br>SR | -      | -    | -    | ns   | PHY dependent  |

www.infineon.com

Published by Infineon Technologies AG