Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Product Status             | Active                                                                                      |

|----------------------------|---------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                             |

| Core Size                  | 32-Bit Single-Core                                                                          |

| Speed                      | 144MHz                                                                                      |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, LINbus, MMC/SD, SPI, UART/USART, USB OTG, USIC |

| Peripherals                | DMA, I <sup>2</sup> S, LED, POR, Touch-Sense, WDT                                           |

| Number of I/O              | 75                                                                                          |

| Program Memory Size        | 1.5MB (1.5M × 8)                                                                            |

| Program Memory Type        | FLASH                                                                                       |

| EEPROM Size                | -                                                                                           |

| RAM Size                   | 276К х 8                                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 3.63V                                                                               |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                       |

| Oscillator Type            | External                                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                          |

| Mounting Type              | Surface Mount                                                                               |

| Package / Case             | 100-LQFP Exposed Pad                                                                        |

| Supplier Device Package    | PG-LQFP-100-25                                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xmc4800f100k1536aaxqma1          |

|                            |                                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## XMC4700 / XMC4800 XMC4000 Family

## **General Device Information**

| Table 10 | Package Pi | Package Pin Mapping (cont'd) |          |          |       |  |  |  |  |

|----------|------------|------------------------------|----------|----------|-------|--|--|--|--|

| Function | LFBGA-196  | LQFP-144                     | LQFP-100 | Pad Type | Notes |  |  |  |  |

| P5.3     | L10        | 81                           | -        | A2       |       |  |  |  |  |

| P5.4     | M10        | 80                           | -        | A2       |       |  |  |  |  |

| P5.5     | L8         | 79                           | -        | A2       |       |  |  |  |  |

| P5.6     | M8         | 78                           | -        | A2       |       |  |  |  |  |

| P5.7     | L7         | 77                           | 55       | A1+      |       |  |  |  |  |

| P5.8     | K6         | 58                           | -        | A2       |       |  |  |  |  |

| P5.9     | M6         | 57                           | -        | A2       |       |  |  |  |  |

| P5.10    | K5         | 56                           | -        | A1+      |       |  |  |  |  |

| P5.11    | L5         | 55                           | -        | A1+      |       |  |  |  |  |

| P6.0     | J10        | 101                          | -        | A2       |       |  |  |  |  |

| P6.1     | H9         | 100                          | -        | A2       |       |  |  |  |  |

| P6.2     | K10        | 99                           | -        | A2       |       |  |  |  |  |

| P6.3     | J9         | 98                           | -        | A1+      |       |  |  |  |  |

| P6.4     | H10        | 97                           | -        | A2       |       |  |  |  |  |

| P6.5     | H11        | 96                           | -        | A2       |       |  |  |  |  |

| P6.6     | H12        | 95                           | -        | A2       |       |  |  |  |  |

| P7.0     | L13        | -                            | -        | A2       |       |  |  |  |  |

| P7.1     | M13        | -                            | -        | A2       |       |  |  |  |  |

| P7.2     | N13        | -                            | -        | A2       |       |  |  |  |  |

| P7.3     | M14        | -                            | -        | A2       |       |  |  |  |  |

| P7.4     | N14        | -                            | -        | A1+      |       |  |  |  |  |

| P7.5     | L14        | -                            | -        | A1+      |       |  |  |  |  |

| P7.6     | K14        | -                            | -        | A1+      |       |  |  |  |  |

| P7.7     | J14        | -                            | -        | A1+      |       |  |  |  |  |

| P7.8     | H14        | -                            | -        | A2       |       |  |  |  |  |

| P7.9     | G13        | -                            | -        | A1+      |       |  |  |  |  |

| P7.10    | G14        | -                            | -        | A1+      |       |  |  |  |  |

| P7.11    | F14        | -                            | -        | A1+      |       |  |  |  |  |

| P8.0     | B7         | -                            | -        | A2       |       |  |  |  |  |

| P8.1     | A7         | -                            | -        | A2       |       |  |  |  |  |

| P8.2     | B3         | -                            | -        | A2       |       |  |  |  |  |

| P8.3     | B2         | -                            | -        | A2       |       |  |  |  |  |

| P8.4     | B6         | -                            | -        | A1+      |       |  |  |  |  |

#### Data Sheet

## **General Device Information**

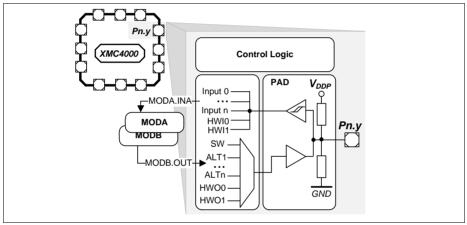

## 2.2.2 Port I/O Functions

The following general scheme is used to describe each Port pin:

## Table 11 Port I/O Function Description

| Function | Outputs  |          |          | Inputs   |          |          |  |

|----------|----------|----------|----------|----------|----------|----------|--|

|          | ALT1     | ALTn     | HWO0     | HWI0     | Input    | Input    |  |

| P0.0     |          | MODA.OUT | MODB.OUT | MODB.INA | MODC.INA |          |  |

| Pn.y     | MODA.OUT |          |          |          | MODA.INA | MODC.INB |  |

## Figure 8 Simplified Port Structure

Pn.y is the port pin name, defining the control and data bits/registers associated with it. As GPIO, the port is under software control. Its input value is read via Pn\_IN.y, Pn\_OUT defines the output value.

Up to four alternate output functions (ALT1/2/3/4) can be mapped to a single port pin, selected by Pn\_IOCR.PC. The output value is directly driven by the respective module, with the pin characteristics controlled by the port registers (within the limits of the connected pad).

The port pin input can be connected to multiple peripherals. Most peripherals have an input multiplexer to select between different possible input sources.

The input path is also active while the pin is configured as output. This allows to feedback an output to on-chip resources without wasting an additional external pin.

By Pn\_HWSEL it is possible to select between different hardware "masters" (HWO0/HWI0). The selected peripheral can take control of the pin(s). Hardware control overrules settings in the respective port pin registers.

The XMC4[78]00 has a common ground concept, all  $V_{\rm SS}$ ,  $V_{\rm SSA}$  and  $V_{\rm SSO}$  pins share the same ground potential. In packages with an exposed die pad it must be connected to the common ground as well.

$V_{\rm AGND}$  is the low potential to the analog reference  $V_{\rm AREF}$ . Depending on the application it can share the common ground or have a different potential. In devices with shared  $V_{\rm DDA}/V_{\rm AREF}$  and  $V_{\rm SSA}/V_{\rm AGND}$  pins the reference is tied to the supply. Some analog channels can optionally serve as "Alternate Reference"; further details on this operating mode are described in the Reference Manual.

When  $V_{\text{DDP}}$  is supplied,  $V_{\text{BAT}}$  must be supplied as well. If no other supply source (e.g. battery) is connected to  $V_{\text{BAT}}$ , the  $V_{\text{BAT}}$  pin can also be connected directly to  $V_{\text{DDP}}$ .

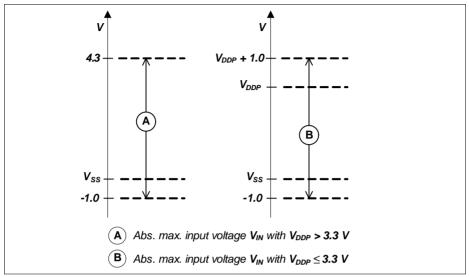

Figure 10 Absolute Maximum Input Voltage Ranges

## 3.1.3 Pin Reliability in Overload

When receiving signals from higher voltage devices, low-voltage devices experience overload currents and voltages that go beyond their own IO power supplies specification.

Table 14 defines overload conditions that will not cause any negative reliability impact if all the following conditions are met:

- full operation life-time is not exceeded

- Operating Conditions are met for

- pad supply levels ( $V_{\text{DDP}}$  or  $V_{\text{DDA}}$ )

- temperature

If a pin current is outside of the **Operating Conditions** but within the overload conditions, then the parameters of this pin as stated in the Operating Conditions can no longer be guaranteed. Operation is still possible in most cases but with relaxed parameters.

Note: An overload condition on one or more pins does not require a reset.

Note: A series resistor at the pin to limit the current to the maximum permitted overload current is sufficient to handle failure situations like short to battery.

## Table 14 Overload Parameters

| Parameter                                                                  | Symbol              |      | Values | 5    | Unit | Note /<br>Test Condition                              |

|----------------------------------------------------------------------------|---------------------|------|--------|------|------|-------------------------------------------------------|

|                                                                            |                     | Min. | Тур.   | Max. |      |                                                       |

| Input current on any port pin during overload condition                    | I <sub>OV</sub> SR  | -5   | -      | 5    | mA   |                                                       |

| Absolute sum of all input circuit currents for one port                    | I <sub>OVG</sub> SR | -    | -      | 20   | mA   | $\Sigma  I_{OVx} $ , for all $I_{OVx} < 0 \text{ mA}$ |

| group during overload condition <sup>1)</sup>                              |                     | -    | -      | 20   | mA   | $\Sigma  I_{OVx} $ , for all $I_{OVx} > 0 \text{ mA}$ |

| Absolute sum of all input<br>circuit currents during<br>overload condition | I <sub>OVS</sub> SR | -    | -      | 80   | mA   | $\Sigma I_{OVG}$                                      |

1) The port groups are defined in Table 17.

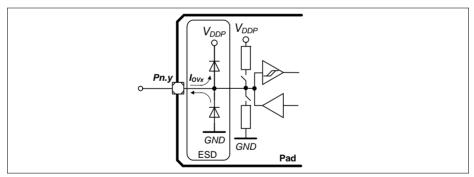

**Figure 11** shows the path of the input currents during overload via the ESD protection structures. The diodes against  $V_{\text{DDP}}$  and ground are a simplified representation of these ESD protection structures.

Figure 11 Input Overload Current via ESD structures

Table 15 and Table 16 list input voltages that can be reached under overload conditions.Note that the absolute maximum input voltages as defined in the Absolute MaximumRatings must not be exceeded during overload.

## 3.1.4 Pad Driver and Pad Classes Summary

This section gives an overview on the different pad driver classes and their basic characteristics.

| Table 18Pad Driver and Pad Classes Overview |

|---------------------------------------------|

|---------------------------------------------|

| Class | Power<br>Supply | Туре         | Sub-Class                    | Speed<br>Grade | Load   | Termination                    |

|-------|-----------------|--------------|------------------------------|----------------|--------|--------------------------------|

| A     | 3.3 V           | LVTTL<br>I/O | <b>A1</b><br>(e.g. GPIO)     | 6 MHz          | 100 pF | No                             |

|       |                 |              | A1+<br>(e.g. serial I/Os)    | 25 MHz         | 50 pF  | Series termination recommended |

|       |                 |              | <b>A2</b><br>(e.g. ext. Bus) | 80 MHz         | 15 pF  | Series termination recommended |

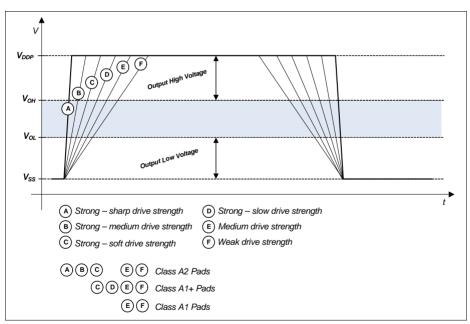

Figure 12 Output Slopes with different Pad Driver Modes

Figure 12 is a qualitative display of the resulting output slope performance with different output driver modes. The detailed input and output characteristics are listed in Section 3.2.1.

## 3.2 DC Parameters

## 3.2.1 Input/Output Pins

The digital input stage of the shared analog/digital input pins is identical to the input stage of the standard digital input/output pins.

The Pull-up on the PORST pin is identical to the Pull-up on the standard digital input/output pins.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Parameter                                                | Symbol                   | Va                          | alues | Unit | Note / Test Condition                                   |

|----------------------------------------------------------|--------------------------|-----------------------------|-------|------|---------------------------------------------------------|

|                                                          |                          | Min.                        | Max.  |      |                                                         |

| Pin capacitance (digital inputs/outputs)                 | C <sub>IO</sub> CC       | -                           | 10    | pF   |                                                         |

| Pull-down current                                        | $ I_{PDL} $              | 150                         | -     | μΑ   | $^{1)}V_{\rm IN} \ge 0.6 \times V_{\rm DDP}$            |

|                                                          | SR                       | _                           | 10    | μΑ   | $^{2)}V_{\mathrm{IN}} \leq 0.36 	imes V_{\mathrm{DDP}}$ |

| Pull-Up current                                          | $ I_{\rm PUH} $          | _                           | 10    | μΑ   | $^{2)}V_{\rm IN} \ge 0.6 \times V_{\rm DDP}$            |

|                                                          | SR                       | 100                         | -     | μΑ   | $^{1)}V_{\rm IN} \leq 0.36 \times V_{\rm DDP}$          |

| Input Hysteresis for pads of all A classes <sup>3)</sup> | HYSA<br>CC               | $0.1 \times V_{\text{DDP}}$ | -     | V    |                                                         |

| PORST spike filter<br>always blocked pulse<br>duration   | t <sub>SF1</sub> CC      | -                           | 10    | ns   |                                                         |

| PORST spike filter<br>pass-through pulse<br>duration     | t <sub>SF2</sub> CC      | 100                         | -     | ns   |                                                         |

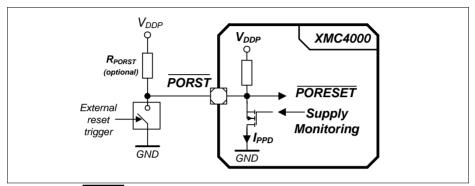

| PORST pull-down current                                  | I <sub>PPD</sub>  <br>CC | 13                          | -     | mA   | V <sub>IN</sub> = 1.0 V                                 |

## Table 20 Standard Pad Parameters

Current required to override the pull device with the opposite logic level ("force current").

With active pull device, at load currents between force and keep current the input state is undefined.

Load current at which the pull device still maintains the valid logic level ("keep current").

With active pull device, at load currents between force and keep current the input state is undefined.

Hysteresis is implemented to avoid metastable states and switching due to internal ground bounce. It can not be guaranteed that it suppresses switching due to external system noise.

47

## Table 22 Standard Pads Class\_A1+

| Parameter            | Symbol               | Va                     | lues | Unit | Note /<br>Test Condition                                                |

|----------------------|----------------------|------------------------|------|------|-------------------------------------------------------------------------|

|                      |                      | Min.                   | Max. |      |                                                                         |

| Output high voltage, | V <sub>OHA1+</sub>   | V <sub>DDP</sub> - 0.4 | -    | V    | <i>I</i> <sub>OH</sub> ≥ -400 μA                                        |

| $POD^{1)} = weak$    | CC                   | 2.4                    | -    | V    | <i>I</i> <sub>OH</sub> ≥ -500 μA                                        |

| Output high voltage, |                      | $V_{\rm DDP}$ - 0.4    | -    | V    | I <sub>OH</sub> ≥ -1.4 mA                                               |

| $POD^{1)} = medium$  |                      | 2.4                    | -    | V    | I <sub>OH</sub> ≥ -2 mA                                                 |

| Output high voltage, |                      | $V_{\rm DDP}$ - 0.4    | -    | V    | $I_{\rm OH} \ge$ -1.4 mA                                                |

| $POD^{1)} = strong$  |                      | 2.4                    | _    | V    | $I_{\rm OH} \ge$ -2 mA                                                  |

| Output low voltage   | $V_{\rm OLA1+}$ CC   | _                      | 0.4  | V    | $I_{OL} \le 500 \ \mu A;$<br>POD <sup>1)</sup> = weak                   |

|                      |                      | -                      | 0.4  | V    | $I_{OL} \le 2 \text{ mA};$<br>POD <sup>1)</sup> = medium                |

|                      |                      | -                      | 0.4  | V    | $I_{OL} \le 2 \text{ mA};$<br>POD <sup>1)</sup> = strong                |

| Fall time            | t <sub>FA1+</sub> CC | -                      | 150  | ns   | $C_{L} = 20 \text{ pF};$<br>POD <sup>1)</sup> = weak                    |

|                      |                      | -                      | 50   | ns   | $C_{\rm L}$ = 50 pF;<br>POD <sup>1)</sup> = medium                      |

|                      |                      | _                      | 28   | ns   | $C_{L} = 50 \text{ pF};$<br>POD <sup>1)</sup> = strong;<br>edge = slow  |

|                      |                      | _                      | 16   | ns   | $C_{L} = 50 \text{ pF};$<br>POD <sup>1)</sup> = strong;<br>edge = soft; |

| Rise time            | t <sub>RA1+</sub> CC | -                      | 150  | ns   | $C_{\rm L}$ = 20 pF;<br>POD <sup>1)</sup> = weak                        |

|                      |                      | -                      | 50   | ns   | $C_{L} = 50 \text{ pF};$<br>POD <sup>1)</sup> = medium                  |

|                      |                      | -                      | 28   | ns   | $C_{L} = 50 \text{ pF};$<br>POD <sup>1)</sup> = strong;<br>edge = slow  |

|                      |                      | -                      | 16   | ns   | $C_{L} = 50 \text{ pF};$<br>POD <sup>1)</sup> = strong;<br>edge = soft  |

1) POD = Pin Out Driver

| Parameter                                                                       | Symbol                                                          |      | Value | S     | Unit | Note /                                                                                    |

|---------------------------------------------------------------------------------|-----------------------------------------------------------------|------|-------|-------|------|-------------------------------------------------------------------------------------------|

|                                                                                 | -                                                               | Min. | Тур.  | Max.  | -    | Test Condition                                                                            |

| Total Unadjusted Error                                                          | TUE CC                                                          | -4   | -     | 4     | LSB  | 12-bit resolution;                                                                        |

| Differential Non-Linearity<br>Error <sup>8)</sup>                               | EA <sub>DNL</sub><br>CC                                         | -3   | -     | 3     | LSB  | $V_{\text{DDA}} = 3.3 \text{ V};$ $V_{\text{AREF}} = V_{\text{DDA}}^{7)}$                 |

| Gain Error <sup>8)</sup>                                                        | EA <sub>GAIN</sub><br>CC                                        | -4   | -     | 4     | LSB  |                                                                                           |

| Integral Non-Linearity <sup>8)</sup>                                            | EA <sub>INL</sub> CC                                            | -3   | -     | 3     | LSB  | -                                                                                         |

| Offset Error <sup>8)</sup>                                                      | EA <sub>OFF</sub><br>CC                                         | -4   | -     | 4     | LSB  |                                                                                           |

| Worst case ADC $V_{\text{DDA}}$<br>power supply current per<br>active converter | I <sub>DDAA</sub><br>CC                                         | _    | 1.5   | 2     | mA   | during conversion<br>$V_{\text{DDP}} = 3.6 \text{ V},$<br>$T_{\text{J}} = 150 \text{ °C}$ |

| Charge consumption on $V_{\text{AREF}}$ per conversion <sup>5)</sup>            | $\begin{array}{c} Q_{\mathrm{CONV}} \\ \mathrm{CC} \end{array}$ | -    | 30    | -     | рС   | $0 V \le V_{AREF} \le V_{DDA}^{9)}$                                                       |

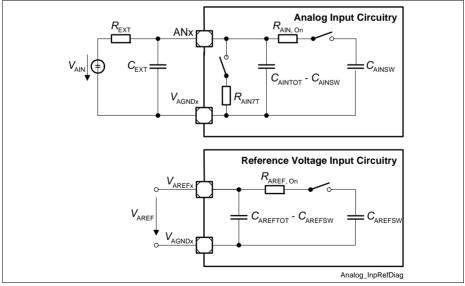

| ON resistance of the analog input path                                          | R <sub>AIN</sub> CC                                             | -    | 600   | 1 200 | Ohm  |                                                                                           |

| ON resistance for the ADC test (pull down for AIN7)                             | R <sub>AIN7T</sub><br>CC                                        | 180  | 550   | 900   | Ohm  |                                                                                           |

| Resistance of the reference voltage input path                                  | R <sub>AREF</sub><br>CC                                         | _    | 700   | 1 700 | Ohm  |                                                                                           |

## Table 25 VADC Parameters (Operating Conditions apply)

1) A running conversion may become imprecise in case the normal conditions are violated (voltage overshoot).

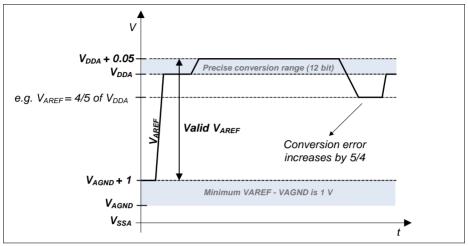

If the analog reference voltage is below V<sub>DDA</sub>, then the ADC converter errors increase. If the reference voltage is reduced by the factor k (k<1), TUE, DNL, INL, Gain, and Offset errors increase also by the factor 1/k.</li>

- 3) The leakage current definition is a continuous function, as shown in figure ADCx Analog Inputs Leakage. The numerical values defined determine the characteristic points of the given continuous linear approximation they do not define step function (see Figure 16).

- 4) The sampling capacity of the conversion C-network is pre-charged to V<sub>AREF</sub>/2 before the sampling moment. Because of the parasitic elements, the voltage measured at AINx can deviate from V<sub>AREF</sub>/2.

- 5) Applies to AINx, when used as alternate reference input.

- 6) This represents an equivalent switched capacitance. This capacitance is not switched to the reference voltage at once. Instead, smaller capacitances are successively switched to the reference voltage.

- For 10-bit conversions, the errors are reduced to 1/4; for 8-bit conversions, the errors are reduced to 1/16. Never less than ±1 LSB.

- 8) The sum of DNL/INL/GAIN/OFF errors does not exceed the related total unadjusted error TUE.

- 9) The resulting current for a conversion can be calculated with  $I_{AREF} = Q_{CONV} / t_c$ . The fastest 12-bit post-calibrated conversion of  $t_c = 459$  ns results in a typical average current of  $I_{AREF} = 65.4 \mu A$ .

55

## Figure 14 VADC Reference Voltage Range

The power-up calibration of the VADC requires a maximum number of 4  $352 f_{ADCI}$  cycles.

| Condition                                           | s apply)            |       |        |       |      |                                                      |

|-----------------------------------------------------|---------------------|-------|--------|-------|------|------------------------------------------------------|

| Parameter                                           | Symbol              |       | Values | 5     | Unit | Note /                                               |

|                                                     |                     | Min.  | Тур.   | Max.  |      | Test Condition                                       |

| Input low voltage                                   | $V_{\rm IL}$ SR     | -     | -      | 0.8   | V    |                                                      |

| Input high voltage<br>(driven)                      | V <sub>IH</sub> SR  | 2.0   | -      | -     | V    |                                                      |

| Input high voltage<br>(floating) <sup>1)</sup>      | V <sub>IHZ</sub> SR | 2.7   | -      | 3.6   | V    |                                                      |

| Differential input sensitivity                      | V <sub>DIS</sub> CC | 0.2   | -      | -     | V    |                                                      |

| Differential common mode range                      | V <sub>CM</sub> CC  | 0.8   | -      | 2.5   | V    |                                                      |

| Output low voltage                                  | V <sub>OL</sub> CC  | 0.0   | -      | 0.3   | V    | 1.5 kOhm pull-<br>up to 3.6 V                        |

| Output high voltage                                 | V <sub>OH</sub> CC  | 2.8   | -      | 3.6   | V    | 15 kOhm pull-<br>down to 0 V                         |

| DP pull-up resistor (idle bus)                      | R <sub>PUI</sub> CC | 900   | -      | 1 575 | Ohm  |                                                      |

| DP pull-up resistor<br>(upstream port<br>receiving) | R <sub>PUA</sub> CC | 1 425 | -      | 3 090 | Ohm  |                                                      |

| DP, DM pull-down resistor                           | R <sub>PD</sub> CC  | 14.25 | -      | 24.8  | kOhm |                                                      |

| Input impedance DP,<br>DM                           | Z <sub>INP</sub> CC | 300   | -      | -     | kOhm | $0 \text{ V} \leq V_{\text{IN}} \leq V_{\text{DDP}}$ |

| Driver output resistance<br>DP, DM                  | Z <sub>DRV</sub> CC | 28    | -      | 44    | Ohm  |                                                      |

# Table 31 USB OTG Data Line (USB\_DP, USB\_DM) Parameters (Operating Conditions apply)

Measured at A-connector with 1.5 kOhm ± 5% to 3.3 V ± 0.3 V connected to USB\_DP or USB\_DM and at Bconnector with 15 kOhm ± 5% to ground connected to USB\_DP and USB\_DM.

## 3.3.2 Power-Up and Supply Monitoring

**PORST** is always asserted when  $V_{\text{DDP}}$  and/or  $V_{\text{DDC}}$  violate the respective thresholds.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

## Figure 25 PORST Circuit

| Table 37 | Supply | Monitoring | Parameters |

|----------|--------|------------|------------|

|----------|--------|------------|------------|

| Parameter                                                       | Symbol                   |                    | Value | s                  | Unit | Note /                                                                                                           |

|-----------------------------------------------------------------|--------------------------|--------------------|-------|--------------------|------|------------------------------------------------------------------------------------------------------------------|

|                                                                 |                          | Min.               | Тур.  | Max.               |      | Test Condition                                                                                                   |

| Digital supply voltage reset threshold                          | V <sub>POR</sub> CC      | 2.79 <sup>1)</sup> | _     | 3.05 <sup>2)</sup> | V    | 3)                                                                                                               |

| Core supply voltage reset threshold                             | $V_{\rm PV}$ CC          | -                  | -     | 1.17               | V    |                                                                                                                  |

| $V_{\text{DDP}}$ voltage to ensure defined pad states           | V <sub>DDPPA</sub><br>CC | -                  | 1.0   | -                  | V    |                                                                                                                  |

| PORST rise time                                                 | t <sub>PR</sub> SR       | _                  | _     | 2                  | μs   | 4)                                                                                                               |

| Startup time from power-on reset with code execution from Flash | t <sub>SSW</sub> CC      | -                  | 2.5   | 3.5                | ms   | Time to the first<br>user code<br>instruction                                                                    |

| $V_{\rm DDC}$ ramp up time                                      | t <sub>VCR</sub> CC      | _                  | 550   | _                  | μS   | Ramp up after<br>power-on or<br>after a reset<br>triggered by a<br>violation of<br>$V_{\rm POR}$ or $V_{\rm PV}$ |

1) Minimum threshold for reset assertion.

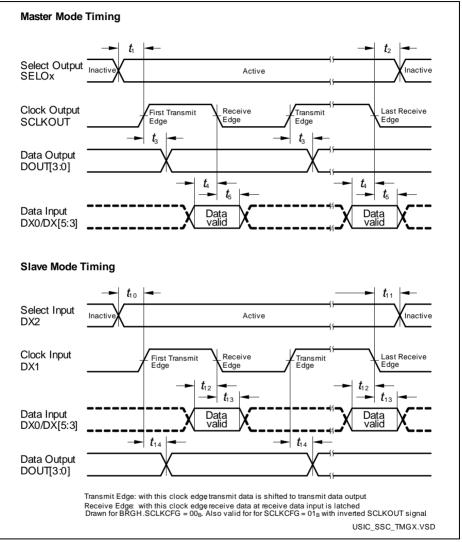

Figure 33 USIC - SSC Master/Slave Mode Timing

Note: This timing diagram shows a standard configuration, for which the slave select signal is low-active, and the serial clock signal is not shifted and not inverted.

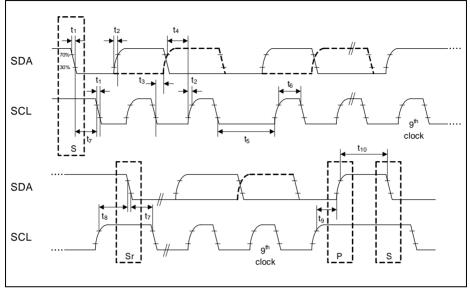

## 3.3.9.3 Inter-IC (IIC) Interface Timing

The following parameters are applicable for a USIC channel operated in IIC mode.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Parameter                                        | Symbol                   |      | Values | S    | Unit | Note /         |

|--------------------------------------------------|--------------------------|------|--------|------|------|----------------|

|                                                  |                          | Min. | Тур.   | Max. |      | Test Condition |

| Fall time of both SDA and SCL                    | t <sub>1</sub><br>CC/SR  | -    | -      | 300  | ns   |                |

| Rise time of both SDA and SCL                    | t <sub>2</sub><br>CC/SR  | -    | -      | 1000 | ns   |                |

| Data hold time                                   | t <sub>3</sub><br>CC/SR  | 0    | -      | -    | μs   |                |

| Data set-up time                                 | t <sub>4</sub><br>CC/SR  | 250  | -      | -    | ns   |                |

| LOW period of SCL clock                          | t <sub>5</sub><br>CC/SR  | 4.7  | -      | -    | μs   |                |

| HIGH period of SCL clock                         | t <sub>6</sub><br>CC/SR  | 4.0  | -      | -    | μs   |                |

| Hold time for (repeated)<br>START condition      | t <sub>7</sub><br>CC/SR  | 4.0  | -      | -    | μs   |                |

| Set-up time for repeated START condition         | t <sub>8</sub><br>CC/SR  | 4.7  | -      | -    | μs   |                |

| Set-up time for STOP condition                   | t <sub>9</sub><br>CC/SR  | 4.0  | -      | -    | μs   |                |

| Bus free time between a STOP and START condition | t <sub>10</sub><br>CC/SR | 4.7  | -      | -    | μs   |                |

| Capacitive load for each bus line                | $C_{\rm b}{\rm SR}$      | -    | -      | 400  | pF   |                |

## Table 48 USIC IIC Standard Mode Timing<sup>1)</sup>

Due to the wired-AND configuration of an IIC bus system, the port drivers of the SCL and SDA signal lines need to operate in open-drain mode. The high level on these lines must be held by an external pull-up device, approximately 10 kOhm for operation at 100 kbit/s, approximately 2 kOhm for operation at 400 kbit/s.

## Figure 34 USIC IIC Stand and Fast Mode Timing

## 3.3.9.4 Inter-IC Sound (IIS) Interface Timing

The following parameters are applicable for a USIC channel operated in IIS mode.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Parameter       | Symbol            |                   | Values | 5                 | Unit | Note /         |

|-----------------|-------------------|-------------------|--------|-------------------|------|----------------|

|                 |                   | Min.              | Тур.   | Max.              |      | Test Condition |

| Clock period    | t <sub>1</sub> CC | 33.3              | -      | -                 | ns   |                |

| Clock high time | t <sub>2</sub> CC | 0.35 x            | -      | _                 | ns   |                |

|                 |                   | t <sub>1min</sub> |        |                   |      |                |

| Clock low time  | t <sub>3</sub> CC | 0.35 x            | _      | -                 | ns   |                |

|                 |                   | t <sub>1min</sub> |        |                   |      |                |

| Hold time       | t <sub>4</sub> CC | 0                 | -      | -                 | ns   |                |

| Clock rise time | t <sub>5</sub> CC | _                 | -      | 0.15 x            | ns   |                |

|                 |                   |                   |        | t <sub>1min</sub> |      |                |

93

## Table 50 USIC IIS Master Transmitter Timing

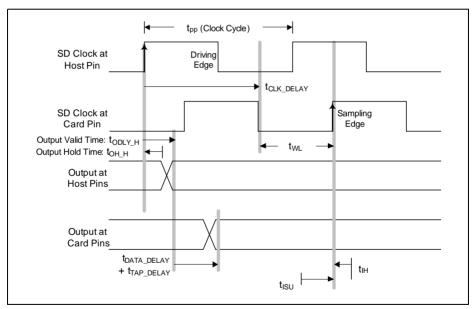

## 3.3.9.5 SDMMC Interface Timing

- Note: These parameters are not subject to production test, but verified by design and/or characterization.

- Note: Operating Conditions apply, total external capacitive load  $C_1 = 40 \text{ pF}$ .

AC Timing Specifications (Full-Speed Mode)

| Parameter                                                | Symbol              |    | Values    | 5  | Unit | Note/ Test |

|----------------------------------------------------------|---------------------|----|-----------|----|------|------------|

|                                                          |                     |    | Min. Max. |    |      | Condition  |

| Clock frequency in full speed transfer mode $(1/t_{pp})$ | $f_{\sf pp}$        | СС | 0         | 24 | MHz  |            |

| Clock cycle in full speed transfer mode                  | t <sub>pp</sub>     | СС | 40        | -  | ns   |            |

| Clock low time                                           | t <sub>WL</sub>     | СС | 10        | -  | ns   |            |

| Clock high time                                          | t <sub>WH</sub>     | CC | 10        | -  | ns   |            |

| Clock rise time                                          | t <sub>TLH</sub>    | CC | -         | 10 | ns   |            |

| Clock fall time                                          | t <sub>THL</sub>    | CC | -         | 10 | ns   |            |

| Inputs setup to clock rising edge                        | t <sub>ISU_F</sub>  | SR | 2         | -  | ns   |            |

| Inputs hold after clock rising edge                      | t <sub>IH_F</sub>   | SR | 2         | -  | ns   |            |

| Outputs valid time in full speed mode                    | t <sub>ODLY_F</sub> | CC | -         | 10 | ns   |            |

| Outputs hold time in full speed mode                     | t <sub>OH_F</sub>   | СС | 0         | -  | ns   |            |

## Table 52 SDMMC Timing for Full-Speed Mode

| Table 53 | SD Card Bus Timing for Full-Speed Mode <sup>1)</sup> |

|----------|------------------------------------------------------|

|----------|------------------------------------------------------|

| Parameter                | Symbol           | Values |      | Unit | Note/ Test |  |

|--------------------------|------------------|--------|------|------|------------|--|

|                          |                  | Min.   | Max. |      | Condition  |  |

| SD card input setup time | t <sub>ISU</sub> | 5      | -    | ns   |            |  |

| SD card input hold time  | t <sub>IH</sub>  | 5      | -    | ns   |            |  |

## Table 55 SD Card Bus Timing for High-Speed Mode<sup>1)</sup>

| Parameter                 | Symbol            | Value | s    | Unit | Note/ Test |

|---------------------------|-------------------|-------|------|------|------------|

|                           |                   | Min.  | Max. |      | Condition  |

| SD card input setup time  | t <sub>ISU</sub>  | 6     | _    | ns   |            |

| SD card input hold time   | t <sub>IH</sub>   | 2     | -    | ns   |            |

| SD card output valid time | t <sub>ODLY</sub> | -     | 14   | ns   |            |

| SD card output hold time  | t <sub>OH</sub>   | 2.5   | _    | ns   |            |

1) Reference card timing values for calculation examples. Not subject to production test and not characterized.

## High-Speed Output Path (Write)

## Figure 39 High-Speed Output Path

## High-Speed Write Meeting Setup (Maximum Delay)

The following equations show how to calculate the allowed skew range between the SD\_CLK and SD\_DAT/CMD signals on the PCB.

| Parameter                         |                    |    | Symbol                 | Limit \ | Limit Values |    |

|-----------------------------------|--------------------|----|------------------------|---------|--------------|----|

|                                   |                    |    |                        | Min.    | Max.         |    |

| A(15:0) output valid              | from SDCLKO        | CC | t <sub>6</sub>         | -       | 9            | ns |

| A(15:0) output hold               | low-to-high        | CC | <i>t</i> <sub>7</sub>  | 3       | -            |    |

| CS(3:0) low                       | - transition       | CC | t <sub>8</sub>         | -       | 9            |    |

| CS(3:0) high                      | -                  | CC | t <sub>9</sub>         | 3       | -            |    |

| RAS low                           | -                  | CC | <i>t</i> <sub>10</sub> | -       | 9            |    |

| RAS high                          | -                  | SR | t <sub>11</sub>        | 3       | -            |    |

| CAS low                           | -                  | SR | t <sub>12</sub>        | -       | 9            |    |

| CAS high                          | -                  | CC | t <sub>13</sub>        | 3       | -            |    |

| RD/WR low                         | -                  | CC | t <sub>14</sub>        | -       | 9            |    |

| RD/WR high                        | -                  | CC | t <sub>15</sub>        | 3       | -            |    |

| BC(3:0) low                       |                    | CC | t <sub>16</sub>        | -       | 9            |    |

| BC(3:0) high                      | -                  | CC | t <sub>17</sub>        | 3       | -            |    |

| D(15:0) output valid              | -                  | CC | t <sub>18</sub>        | -       | 9            |    |

| D(15:0) output hold               |                    | CC | t <sub>19</sub>        | 3       | -            |    |

| CKE output valid <sup>1)</sup>    |                    | CC | t <sub>22</sub>        | -       | 7            |    |

| CKE output hold <sup>1)</sup>     | -                  | CC | t <sub>23</sub>        | 2       | -            |    |

| D(15:0) input hold                |                    | SR | t <sub>21</sub>        | 3       | -            |    |

| D(15:0) input setup to transition | SDCLKO low-to-high | SR | t <sub>20</sub>        | 4       | -            |    |

## Table 62 EBU SDRAM Access Signal Timing Parameters

1) Not depicted in the read and write access timing figures below.

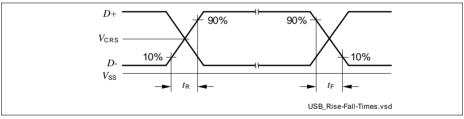

## 3.3.11 USB Interface Characteristics

The Universal Serial Bus (USB) Interface is compliant to the USB Rev. 2.0 Specification and the OTG Specification Rev. 1.3. High-Speed Mode is not supported.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Parameter Symbol        |                       | bol |      | Value | s      | Unit | Note /                 |  |

|-------------------------|-----------------------|-----|------|-------|--------|------|------------------------|--|

|                         |                       |     | Min. | Тур.  | Max.   |      | Test Condition         |  |

| Rise time               | t <sub>R</sub>        | CC  | 4    | -     | 20     | ns   | C <sub>L</sub> = 50 pF |  |

| Fall time               | t <sub>F</sub>        | CC  | 4    | -     | 20     | ns   | C <sub>L</sub> = 50 pF |  |

| Rise/Fall time matching | $t_{\rm R}/t_{\rm F}$ | CC  | 90   | -     | 111.11 | %    | C <sub>L</sub> = 50 pF |  |

| Crossover voltage       | $V_{CRS}$             | CC  | 1.3  | -     | 2.0    | V    | C <sub>L</sub> = 50 pF |  |

Table 63

USB Timing Parameters (operating conditions apply)

Figure 50 USB Signal Timing

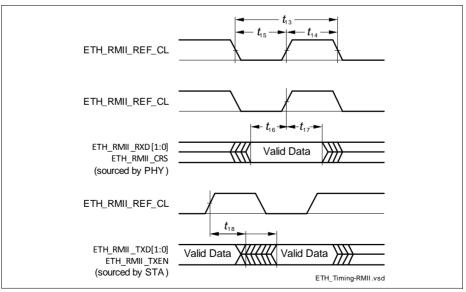

## 3.3.12.4 ETH RMII Parameters

In the following, the parameters of the RMII (Reduced Media Independent Interface) are described.

| Table 66 ETH RMII Signal Timing Parameter | Table 66 | RMII Signal Timing Parameters |

|-------------------------------------------|----------|-------------------------------|

|-------------------------------------------|----------|-------------------------------|

| Parameter                                      |                 | Symbol |      | Value | S    | Unit | Note /                            |  |

|------------------------------------------------|-----------------|--------|------|-------|------|------|-----------------------------------|--|

|                                                |                 |        | Min. | Тур.  | Max. |      | Test Condit<br>ion                |  |

| ETH_RMII_REF_CL clock period                   | t <sub>13</sub> | SR     | 20   | -     | _    | ns   | C <sub>L</sub> = 25 pF;<br>50 ppm |  |

| ETH_RMII_REF_CL clock high time                | t <sub>14</sub> | SR     | 7    | -     | 13   | ns   | C <sub>L</sub> = 25 pF            |  |

| ETH_RMII_REF_CL clock low time                 | t <sub>15</sub> | SR     | 7    | -     | 13   | ns   |                                   |  |

| ETH_RMII_RXD[1:0],<br>ETH_RMII_CRS setup time  | t <sub>16</sub> | SR     | 4    | -     | _    | ns   |                                   |  |

| ETH_RMII_RXD[1:0],<br>ETH_RMII_CRS hold time   | t <sub>17</sub> | SR     | 2    | -     | -    | ns   |                                   |  |

| ETH_RMII_TXD[1:0],<br>ETH_RMII_TXEN data valid | t <sub>18</sub> | CC     | 4    | -     | 15   | ns   |                                   |  |

Figure 54 ETH RMII Signal Timing