# E. Renesas Electronics America Inc - UPD78F1000GB-GAF-AX Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | 78K/0R                                                                               |

| Core Size                  | 16-Bit                                                                               |

| Speed                      | 20MHz                                                                                |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                     |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                              |

| Number of I/O              | 33                                                                                   |

| Program Memory Size        | 16KB (16K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 1K x 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                          |

| Data Converters            | A/D 10x10b                                                                           |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 44-LQFP                                                                              |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f1000gb-gaf-ax |

|                            |                                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                                                                                                                                                                                                                                                                                     |                      |                                                                |                                                                                                                                                                                                                                                                                                                   |                            |                                |                           | 1           |             |                               | (2/2)                         |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------------------|---------------------------|-------------|-------------|-------------------------------|-------------------------------|--|--|--|

| Iter                                                                                                                                                                                                                                                                                                | n                    |                                                                |                                                                                                                                                                                                                                                                                                                   | 78K0R/KF3-                 | r                              | ~                         | <u> </u>    | r           | /KG3-L                        | ~                             |  |  |  |

|                                                                                                                                                                                                                                                                                                     |                      | μ PD78F1010                                                    | μ PD78F1011                                                                                                                                                                                                                                                                                                       | μ PD78F1012                | μ PD78F1027                    | μ PD78F1028               | μ PD78F1013 | μ PD78F1014 | μ PD78F1029 <sup>Note 1</sup> | μ PD78F1030 <sup>Note 1</sup> |  |  |  |

| Clock output/buzze                                                                                                                                                                                                                                                                                  | er output            |                                                                |                                                                                                                                                                                                                                                                                                                   |                            |                                | 2                         |             |             |                               |                               |  |  |  |

|                                                                                                                                                                                                                                                                                                     |                      | (periphe<br>• 256 Hz                                           | <ul> <li>2.44 kHz, 4.88 kHz, 9.76 kHz, 1.25 MHz, 2.5 MHz, 5 MHz, 10 MHz<br/>(peripheral hardware clock: f<sub>MAIN</sub> = 20 MHz operation)</li> <li>256 Hz, 512 Hz, 1.024 kHz, 2.048 kHz, 4.096 kHz, 8.192 kHz, 16.384 kHz, 32.768 kHz<br/>(Subsystem clock: f<sub>SUB</sub> = 32.768 kHz operation)</li> </ul> |                            |                                |                           |             |             |                               |                               |  |  |  |

| 10-bit resolution A/<br>(AV <sub>REF</sub> = 1.8 to 5.5                                                                                                                                                                                                                                             |                      |                                                                |                                                                                                                                                                                                                                                                                                                   | 12 channel                 | S                              |                           |             | 16 ch       | annels                        |                               |  |  |  |

| Comparators                                                                                                                                                                                                                                                                                         |                      |                                                                |                                                                                                                                                                                                                                                                                                                   |                            |                                | -                         |             |             |                               |                               |  |  |  |

| Programmable gai                                                                                                                                                                                                                                                                                    | n amplifiers         |                                                                |                                                                                                                                                                                                                                                                                                                   |                            |                                | _                         |             |             |                               |                               |  |  |  |

| Serial interface                                                                                                                                                                                                                                                                                    |                      | <ul> <li>CSI: 1 d</li> <li>CSI: 1 d</li> <li>UART s</li> </ul> | hannel/UA<br>hannel/UA<br>upporting I                                                                                                                                                                                                                                                                             | RT: 1 chan<br>_IN-bus: 1 c | nel/simplifie<br>nel/simplifie | ed I <sup>2</sup> C: 1 ch | annel       | F1029, 78F  | -1030)                        |                               |  |  |  |

|                                                                                                                                                                                                                                                                                                     | I <sup>2</sup> C bus |                                                                | 1 channel                                                                                                                                                                                                                                                                                                         |                            |                                |                           |             |             |                               |                               |  |  |  |

| Multiplier/divider                                                                                                                                                                                                                                                                                  |                      |                                                                | <ul> <li>16 bits × 16 bits = 32 bits (multiplication)</li> <li>32 bits ÷ 32 bits = 32 bits (division)</li> </ul>                                                                                                                                                                                                  |                            |                                |                           |             |             |                               |                               |  |  |  |

| DMA controller                                                                                                                                                                                                                                                                                      |                      | 2 channels                                                     |                                                                                                                                                                                                                                                                                                                   |                            |                                |                           |             |             |                               |                               |  |  |  |

| Vectored interrupt                                                                                                                                                                                                                                                                                  | Internal             |                                                                | 33                                                                                                                                                                                                                                                                                                                |                            | 3                              | 35                        | ;           | 33          | 3                             | 35                            |  |  |  |

| sources                                                                                                                                                                                                                                                                                             | External             |                                                                |                                                                                                                                                                                                                                                                                                                   |                            |                                | 13                        |             |             |                               |                               |  |  |  |

| Key interrupt                                                                                                                                                                                                                                                                                       |                      | 8 channel                                                      | s (KR0 to k                                                                                                                                                                                                                                                                                                       | (R7)                       |                                |                           |             |             |                               |                               |  |  |  |

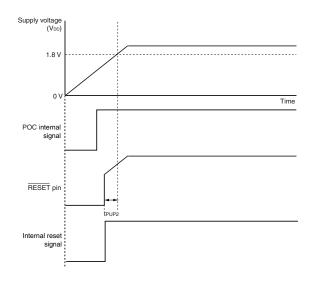

| Reset       • Reset by RESET pin         • Internal reset by watchdog timer         • Internal reset by power-on-clear         • Internal reset by low-voltage detector         • Internal reset by illegal instruction execution Note 2         • Internal reset by a reset processing check error |                      |                                                                |                                                                                                                                                                                                                                                                                                                   |                            |                                |                           |             |             |                               |                               |  |  |  |

| Power-on-clear cire                                                                                                                                                                                                                                                                                 | cuit                 | • Power-o<br>• Power-d                                         |                                                                                                                                                                                                                                                                                                                   | 1.61 ±0.09<br>1.59 ±0.09   |                                |                           |             |             |                               |                               |  |  |  |

| Low-voltage detect                                                                                                                                                                                                                                                                                  | tor                  | 1.91 V to                                                      | 1.91 V to 4.22 V (16 stages)                                                                                                                                                                                                                                                                                      |                            |                                |                           |             |             |                               |                               |  |  |  |

| On-chip debug fun                                                                                                                                                                                                                                                                                   | ction                | Provided                                                       | Provided                                                                                                                                                                                                                                                                                                          |                            |                                |                           |             |             |                               |                               |  |  |  |

| Power supply volta                                                                                                                                                                                                                                                                                  | ige                  | V <sub>DD</sub> = 1.8                                          | to 5.5 V                                                                                                                                                                                                                                                                                                          |                            |                                |                           |             |             |                               |                               |  |  |  |

| Operating ambient temperature $T_A = -40$ to $+85 \ ^{\circ}C$                                                                                                                                                                                                                                      |                      |                                                                |                                                                                                                                                                                                                                                                                                                   |                            |                                |                           |             |             |                               |                               |  |  |  |

**Notes 1.** The  $\mu$ PD78F1029 and  $\mu$ PD78F1030 don't have the FBGA package.

2. The illegal instruction is generated when instruction code FFH is executed.

Reset by the illegal instruction execution not issued by emulation with the in-circuit emulator or on-chip debug emulator.

# (1) Port functions (2/2): 78K0R/KE3-L

| Function Name | I/O    | Function                                                                                                                                                                               | After Reset           | Alternate Function   |

|---------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------|

| P70           | I/O    | Port 7.                                                                                                                                                                                | Input port            | KR0/SO01/INTP4       |

| P71           |        | 8-bit I/O port.                                                                                                                                                                        |                       | KR1/SI01/INTP5       |

| P72           |        | Input of P71, P72, P74, and P75 can be set to TTL buffer.<br>Output of P70, P72, P73, and P75 can be set to N-ch open-drain                                                            |                       | KR2/SCK01/INTP6      |

| P73           |        | output (V <sub>DD</sub> tolerance).                                                                                                                                                    |                       | KR3/SO00/TxD0        |

| P74           |        | Input/output can be specified in 1-bit units.                                                                                                                                          |                       | KR4/SI00/RxD0        |

| P75           |        | Use of an on-chip pull-up resistor can be specified by a software                                                                                                                      |                       | KR5/SCK00            |

| P76           |        | setting.                                                                                                                                                                               |                       | KR6                  |

| P77           |        |                                                                                                                                                                                        |                       | KR7                  |

| P80           | I/O    | Port 8.<br>4-bit I/O port.                                                                                                                                                             | Analog input          | CMP0P/INTP3/<br>PGAI |

| P81           |        | Inputs/output can be specified in 1-bit units.                                                                                                                                         |                       | CMP0M                |

| P82           |        | Inputs of P80 to P83 can be set as comparator inputs or programmable gain amplifier inputs.                                                                                            |                       | CMP1P/INTP7          |

| P83           |        |                                                                                                                                                                                        |                       | CMP1M                |

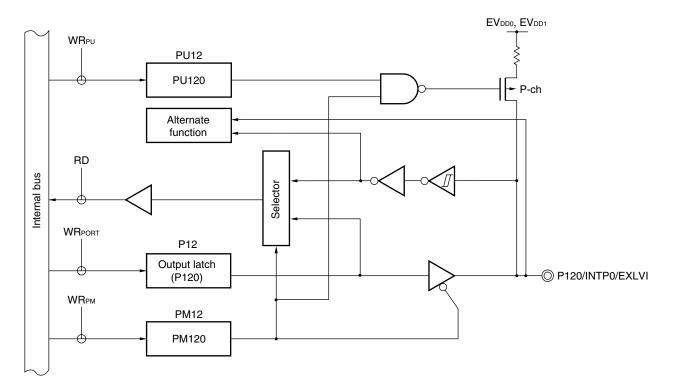

| P120          | I/O    | Port 12.                                                                                                                                                                               | Input port            | INTP0/EXLVI          |

| P121          | Input  | 1-bit I/O port and 4-bit input port.                                                                                                                                                   |                       | X1                   |

| P122          |        | For only P120, input/output can be specified in 1-bit units.<br>For only P120, use of an on-chip pull-up resistor can be specified                                                     |                       | X2/EXCLK             |

| P123          |        | by a software setting.                                                                                                                                                                 |                       | XT1                  |

| P124          |        |                                                                                                                                                                                        |                       | XT2                  |

| P140          | Output | Port 14.                                                                                                                                                                               | Output port           | PCLBUZ0              |

| P141          | I/O    | 1-bit output port and 1-bit I/O port.<br>For only P141, input/output can be specified.<br>For only P141, use of an on-chip pull-up resistor can be specified<br>by a software setting. | Input port            | PCLBUZ1              |

| P150 to P153  | I/O    | Port 15.<br>4-bit I/O port.<br>Input/output can be specified in 1-bit units.                                                                                                           | Digital input<br>port | ANI8 to ANI11        |

# (1) Port functions (2/3): 78K0R/KG3-L

| Function Name | I/O    | Function                                                                                                                                                                                         | After Reset | Alternate Function        |

|---------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------------------|

| P50           | I/O    | Port 5.                                                                                                                                                                                          | Input port  | SCK40 <sup>Note</sup>     |

| P51           |        | 8-bit I/O port.                                                                                                                                                                                  |             | SI40/RxD4 <sup>Note</sup> |

| P52           |        | Input/output can be specified in 1-bit units.<br>Use of an on-chip pull-up resistor can be specified by a                                                                                        |             | SO40/TxD4 <sup>Note</sup> |

| P53           |        | software setting.                                                                                                                                                                                |             | SCK41 <sup>Note</sup>     |

| P54           |        |                                                                                                                                                                                                  |             | SI41 <sup>Note</sup>      |

| P55           |        |                                                                                                                                                                                                  |             | SO41 <sup>Note</sup>      |

| P56           |        |                                                                                                                                                                                                  |             | _                         |

| P57           |        |                                                                                                                                                                                                  |             | _                         |

| P60           | I/O    | Port 6.                                                                                                                                                                                          | Input port  | SCL0                      |

| P61           |        | 8-bit I/O port.                                                                                                                                                                                  |             | SDA0                      |

| P62, P63      |        | Output of P60 to P63 can be set to N-ch open-drain output                                                                                                                                        |             | _                         |

| P64 to P67    |        | <ul><li>(6 V tolerance).</li><li>Input/output can be specified in 1-bit units.</li><li>For only P64 to P67, use of an on-chip pull-up resistor can be specified by a software setting.</li></ul> |             | TI10/TO10 to<br>TI13/TO13 |

| P70 to P73    | I/O    | Port 7.                                                                                                                                                                                          | Input port  | KR0 to KR3                |

| P74 to P77    |        | 8-bit I/O port.                                                                                                                                                                                  |             | KR4/INTP8 to              |

|               |        | Input/output can be specified in 1-bit units.<br>Use of an on-chip pull-up resistor can be specified by a<br>software setting.                                                                   |             | KR7/INTP11                |

| P80 to P87    | I/O    | Port 8.<br>8-bit I/O port.<br>Input/output can be specified in 1-bit units.<br>Use of an on-chip pull-up resistor can be specified by a<br>software setting.                                     | Input port  | _                         |

| P91           | I/O    | Port 9.<br>1-bit I/O port.<br>Input/output can be specified in 1-bit units.<br>Use of an on-chip pull-up resistor can be specified by a<br>software setting.                                     | Input port  | _                         |

| P110, P111    | I/O    | Port 11.<br>2-bit I/O port.<br>Input/output can be specified in 1-bit units.<br>Use of an on-chip pull-up resistor can be specified by a<br>software setting.                                    | Input port  | _                         |

| P120          | I/O    | Port 12.                                                                                                                                                                                         | Input port  | INTP0/EXLVI               |

| P121          | Input  | 1-bit I/O port and 4-bit input port.                                                                                                                                                             |             | X1                        |

| P122          | 1      | For only P120, use of an on-chip pull-up resistor can be                                                                                                                                         |             | X2/EXCLK                  |

| P123          |        | specified by a software setting.                                                                                                                                                                 |             | XT1                       |

| P124          |        |                                                                                                                                                                                                  |             | XT2                       |

| P130          | Output | Port 13.<br>1-bit output port and 1-bit I/O port.                                                                                                                                                | Output port | -                         |

| P131          | I/O    | For only P131, use of an on-chip pull-up resistor can be specified by a software setting.                                                                                                        | Input port  | TI06/TO06                 |

**Note** SCK40, SCK41, SI40, SI41, SO40, SO41, TxD4, RxD4 are only mounted in the  $\mu$  PD78F1027 and 78F1028.

# 3.2.17 RESET

This is the active-low system reset input pin.

When the external reset pin is not used, connect this pin directly or via a resistor to EVDD0 or EVDD1.

When the external reset pin is used, design the circuit based on VDD.

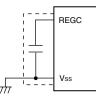

# 3.2.18 REGC

This is the pin for connecting regulator output (2.4 V) stabilization capacitance for internal operation. Connect this pin to Vss via a capacitor (0.47 to 1  $\mu$ F: target).

Also, use a capacitor with good characteristics, since it is used to stabilize internal voltage.

#### Caution Keep the wiring length as short as possible for the broken-line part in the above figure.

#### 3.2.19 FLMD0

This is a pin for setting flash memory programming mode. Perform either of the following processing.

#### (a) In normal operation mode

It is recommended to leave this pin open during normal operation.

The FLMD0 pin must always be kept at the Vss level before reset release but does not have to be pulled down externally because it is internally pulled down by reset. However, pulling it down must be kept selected (i.e., FLMDPUP = "0", default value) by using bit 7 (FLMDPUP) of the background event control register (BECTL) (see **26.5 (1) Back ground event control register**). To pull it down externally, use a resistor of 200 k $\Omega$  or smaller. Self programming and the rewriting of flash memory with the programmer can be prohibited using hardware, by directly connecting this pin to the Vss pin.

#### (b) In self programming mode

It is recommended to leave this pin open when using the self programming function. To pull it down externally, use a resistor of 100 k $\Omega$  to 200 k $\Omega$ .

In the self programming mode, the setting is switched to pull up in the self programming library.

#### (c) In flash memory programming mode

Directly connect this pin to a flash memory programmer when data is written by the flash memory programmer. This supplies a writing voltage of the V<sub>DD</sub> level to the FLMD0 pin.

The FLMD0 pin does not have to be pulled down externally because it is internally pulled down by reset. To pull it down externally, use a resistor of 1 k $\Omega$  to 200 k $\Omega$ .

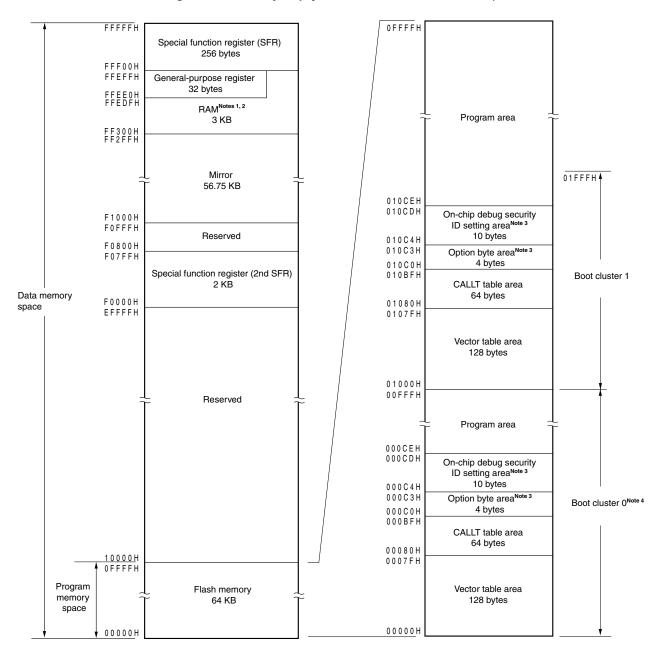

- **Notes 1.** While using the self-programming function, the area FFE20H to FFEFFH cannot be used as stack memory. Furthermore, the areas of FF300H to FF6FFH also cannot be used with the  $\mu$ PD78F1003, 78F1006 and 78F1009.

- 2. Instructions can be executed from the RAM area excluding the general-purpose register area.

- **3.** When boot swap is not used: Set the option bytes to 000C0H to 000C3H, and the on-chip debug security IDs to 000C4H to 000CDH.

- When boot swap is used:Set the option bytes to 000C0H to 000C3H and 010C0H to 010C3H, and the<br/>on-chip debug security IDs to 000C4H to 000CDH and 010C4H to 010CDH.

- 4. Writing boot cluster 0 can be prohibited depending on the setting of security (see 26.7 Security Setting).

| Address | Special Function Register (SFR) Name | Syn    | nbol  | R/W | Manipu       | lable Bit    | Range        | After Reset | Z              | 조              | 즈     | 즈     | 즈            | Z            |

|---------|--------------------------------------|--------|-------|-----|--------------|--------------|--------------|-------------|----------------|----------------|-------|-------|--------------|--------------|

|         |                                      |        |       |     | 1-bit        | 8-bit        | 16-bit       |             | KC3-L (44-pin) | KC3-L (48-pin) | KD3-L | KE3-L | KF3-L        | KG3-L        |

| F01DCH  | Timer channel stop register 1        | TT1L   | TT1   | R/W | $\checkmark$ | $\checkmark$ | $\checkmark$ | 0000H       | -              | -              | -     | -     | $\checkmark$ |              |

| F01DDH  |                                      | -      |       |     | -            | -            |              |             | -              | Ι              | Ι     | -     | $\checkmark$ | $\checkmark$ |

| F01DEH  | Timer clock select register 1        | TPS1L  | TPS1  | R/W | -            | $\checkmark$ | $\checkmark$ | 0000H       | -              | Ι              | Ι     | -     | $\checkmark$ |              |

| F01DFH  |                                      | -      |       |     | -            | -            |              |             | -              | -              | -     | -     | $\checkmark$ | $\checkmark$ |

| F01E0H  | Timer output register 1              | TO1L   | TO1   | R/W | -            | $\checkmark$ | $\checkmark$ | 0000H       | -              | Ι              | Ι     | -     | $\checkmark$ | $\checkmark$ |

| F01E1H  |                                      | -      |       |     | -            | -            |              |             | _              | -              | -     | -     | $\checkmark$ |              |

| F01E2H  | Timer output enable register 1       | TOE1L  | TOE1  | R/W | $\checkmark$ | $\checkmark$ | $\checkmark$ | 0000H       | -              | Ι              | Ι     | -     | $\checkmark$ | $\checkmark$ |

| F01E3H  |                                      | -      |       |     | _            | -            |              |             | _              | -              | -     | -     | $\checkmark$ |              |

| F01E4H  | Timer output level register 1        | TOL1L  | TOL1  | R/W | -            | $\checkmark$ | $\checkmark$ | 0000H       | -              | -              | -     | -     | $\checkmark$ |              |

| F01E5H  |                                      | -      |       |     | _            | -            |              |             | _              | -              | -     | -     | $\checkmark$ |              |

| F01E6H  | Timer output mode register 1         | TOM1L  | TOM1  | R/W | _            | $\checkmark$ | $\checkmark$ | 0000H       | _              | -              | -     | -     | $\checkmark$ |              |

| F01B7H  |                                      | -      |       |     | _            | _            |              |             | _              | -              | -     | -     | $\checkmark$ |              |

| F0200H  | Serial status register 20            | SSR20L | SSR20 | R/W | -            | $\checkmark$ | $\checkmark$ | 0000H       | -              | Ι              | Ι     | -     | Note         | Note         |

| F0201H  |                                      | -      |       |     | -            | -            |              |             | -              | Ι              | Ι     | -     | Note         | Note         |

| F0202H  | Serial status register 21            | SSR21L | SSR21 | R/W | _            | $\checkmark$ | $\checkmark$ | 0000H       | _              | -              | -     | -     | Note         | Note         |

| F0203H  |                                      | -      |       |     | _            | -            |              |             | _              | -              | -     | -     | Note         | Note         |

| F0204H  | Serial flag clear trigger register   | SIR20L | SIR20 | R/W | -            | $\checkmark$ | $\checkmark$ | 0000H       | -              | -              | -     | -     | Note         | Note         |

| F0205H  | 20                                   | -      |       |     | _            | -            |              |             | _              | -              | -     | -     | Note         | Note         |

| F0206H  | Serial flag clear trigger register   | SIR21L | SIR21 | R/W | -            | $\checkmark$ | $\checkmark$ | 0000H       | -              | -              | -     | -     | Note         | Note         |

| F0207H  | 21                                   | -      |       |     | _            | -            |              |             | _              | -              | -     | -     | Note         | Note         |

| F0208H  | Serial mode register 20              | SMR20  |       | R/W | -            | -            | $\checkmark$ | 0020H       | -              | -              | -     | -     | Note         | Note         |

| F0209H  |                                      |        |       |     |              |              |              |             |                |                |       |       |              |              |

| F020AH  | Serial mode register 21              | SMR21  |       | R/W | -            | -            | $\checkmark$ | 0020H       | -              | -              | -     | -     | Note         | Note         |

| F020BH  |                                      |        |       |     |              |              |              |             |                |                |       |       |              |              |

| F020CH  | Serial communication operation       | SCR20  |       | R/W | -            | -            | $\checkmark$ | 0087H       | -              | -              | -     | -     | Note         | Note         |

| F020DH  | setting register 20                  |        |       |     |              |              |              |             |                |                |       |       |              |              |

| F020EH  | Serial communication operation       | SCR21  |       | R/W | -            | -            | $\checkmark$ | 0087H       | -              | -              | -     | -     | Note         | Note         |

| F020FH  | setting register 21                  |        |       |     |              |              |              |             |                |                |       |       |              |              |

| F0210H  | Serial channel enable status         | SE2L   | SE2   | R   | $\checkmark$ | $\checkmark$ | $\checkmark$ | 0000H       | _              | -              | -     | _     | Note         | Note         |

| F0211H  | register 2                           | -      |       |     | -            | -            |              |             | -              | _              | _     | -     | Note         | Note         |

| F0212H  | Serial channel start register 2      | SS2L   | SS2   | R/W | $\checkmark$ | $\checkmark$ | $\checkmark$ | 0000H       | -              | -              | -     | -     | Note         | Note         |

| F0213H  |                                      | -      |       |     | -            | -            |              |             | -              | -              | _     | -     | Note         | Note         |

| F0214H  | Serial channel stop register 2       | ST2L   | ST2   | R/W | $\checkmark$ | $\checkmark$ | $\checkmark$ | 0000H       | _              | -              | _     | _     | Note         | Note         |

| F0215H  |                                      | _      |       |     | _            | _            |              |             | -              |                |       | -     | Note         | Note         |

| F0216H  | Serial clock select register2        | SPS2L  | SPS2  | R/W | $\checkmark$ | $\checkmark$ | $\checkmark$ | 0000H       | _              |                |       | -     | Note         | Note         |

| F0217H  |                                      | -      |       |     | -            | _            |              |             | -              | -              | -     | -     | Note         | Note         |

# Table 4-6. Extended SFR (2nd SFR) List (7/8)

Note Those are only mounted in the 78K0R/KF3-L ( $\mu$  PD78F1027 and 78F1028) and the 78K0R/KG3-L ( $\mu$  PD78F1029 and 78F1030).

# (6) A/D port configuration register (ADPC)

This register switches the ANI0/P20 to ANI7/P27 and ANI8/P150 to ANI11/P153 pins to digital I/O of port or analog input of A/D converter.

The ADPC register can be set by an 8-bit memory manipulation instruction.

Reset signal generation sets this register to 10H.

# Figure 5-41. Format of A/D Port Configuration Register (ADPC)

| Address | : F0017H | After reset: 10H | R/W |       |       |       |       |       |

|---------|----------|------------------|-----|-------|-------|-------|-------|-------|

| Symbol  | 7        | 6                | 5   | 4     | 3     | 2     | 1     | 0     |

| ADPC    | 0        | 0                | 0   | ADPC4 | ADPC3 | ADPC2 | ADPC1 | ADPC0 |

| ADPC4 | ADPC3 | ADPC2    | ADPC1 | ADPC0 |                           | Analog input (A)/digital I/O (D) switching |       |       |      |      |      |      |         |      |      |      |

|-------|-------|----------|-------|-------|---------------------------|--------------------------------------------|-------|-------|------|------|------|------|---------|------|------|------|

|       |       |          |       |       |                           | Port 15 Port 2                             |       |       |      |      |      |      | Port 15 |      |      |      |

|       |       |          |       |       | ANI11                     | ANI10                                      | ANI9  | ANI8  | ANI7 | ANI6 | ANI5 | ANI4 | ANI3    | ANI2 | ANI1 | ANI0 |

|       |       |          |       |       | /P153                     | /P152                                      | /P151 | /P150 | /P27 | /P26 | /P25 | /P24 | /P23    | /P22 | /P21 | /P20 |

| 0     | 0     | 0        | 0     | 0     | А                         | А                                          | А     | А     | А    | А    | А    | А    | А       | А    | А    | А    |

| 0     | 0     | 0        | 0     | 1     | А                         | А                                          | А     | А     | А    | А    | А    | А    | А       | А    | А    | D    |

| 0     | 0     | 0        | 1     | 0     | А                         | А                                          | А     | А     | А    | А    | А    | А    | А       | А    | D    | D    |

| 0     | 0     | 0        | 1     | 1     | А                         | А                                          | А     | А     | А    | А    | А    | А    | А       | D    | D    | D    |

| 0     | 0     | 1        | 0     | 0     | А                         | А                                          | А     | А     | А    | А    | А    | А    | D       | D    | D    | D    |

| 0     | 0     | 1        | 0     | 1     | А                         | А                                          | А     | А     | А    | А    | А    | D    | D       | D    | D    | D    |

| 0     | 0     | 1        | 1     | 0     | А                         | А                                          | А     | А     | А    | А    | D    | D    | D       | D    | D    | D    |

| 0     | 0     | 1        | 1     | 1     | А                         | А                                          | А     | А     | А    | D    | D    | D    | D       | D    | D    | D    |

| 0     | 1     | 0        | 0     | 0     | А                         | А                                          | А     | А     | D    | D    | D    | D    | D       | D    | D    | D    |

| 0     | 1     | 0        | 0     | 1     | А                         | А                                          | А     | D     | D    | D    | D    | D    | D       | D    | D    | D    |

| 0     | 1     | 0        | 1     | 0     | А                         | А                                          | D     | D     | D    | D    | D    | D    | D       | D    | D    | D    |

| 0     | 1     | 0        | 1     | 1     | А                         | D                                          | D     | D     | D    | D    | D    | D    | D       | D    | D    | D    |

| 1     | 0     | 0        | 0     | 0     | D D D D D D D D D D D D D |                                            |       |       |      |      |      | D    |         |      |      |      |

|       | Other | than the | above |       | Setting prohibited        |                                            |       |       |      |      |      |      |         |      |      |      |

Cautions 1. Set a channel to be used for A/D conversion in the input mode by using port mode register 2 and 15 (PM2, PM15).

- 2. Do not set the pin that is set by the ADPC register as digital I/O by the analog input channel specification register (ADS).

- 3. Be sure to first set the ADCEN bit of peripheral enable register 0 (PER0) to 1 when setting up the ADPC register. If ADCEN = 0, writing to the ADPC register is ignored and specified values are returned to the initial values.

Remark

P20/ANI0 to P27/ANI7, P150/ANI8, and P151/ANI9: 78K0R/KC3-L (40-pin, 44-pin)

P20/ANI0 to P27/ANI7, P150/ANI8 to P152/ANI10: 78K0R/KC3-L (48-pin), 78K0R/KD3-L

P20/ANI0 to P27/ANI7, P150/ANI8 to P153/ANI11: 78K0R/KE3-L

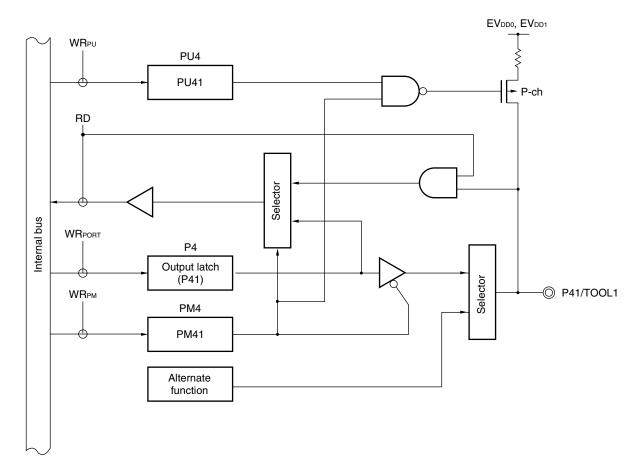

Figure 6-16. Block Diagram of P41

- P4: Port register 4

- PU4: Pull-up resistor option register 4

- PM4: Port mode register 4

- RD: Read signal

- WR xx: Write signal

Figure 6-42. Block Diagram of P120

- P12: Port register 12

- PU12: Pull-up resistor option register 12

- PM12: Port mode register 12

- RD: Read signal

- WR××: Write signal

#### (6) A/D port configuration register (ADPC)

This register switches the P20/ANI0 to P27/ANI7 and P150/ANI8 to P157/ANI15 pins to digital I/O of port or analog input of A/D converter.

The ADPC register can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation sets this register to 10H.

#### Figure 6-60. Format of A/D Port Configuration Register (ADPC)

Address: F0017H After reset: 10H R/W

| Symbol | 7 | 6 | 5 | 4     | 3     | 2     | 1     | 0     |

|--------|---|---|---|-------|-------|-------|-------|-------|

| ADPC   | 0 | 0 | 0 | ADPC4 | ADPC3 | ADPC2 | ADPC1 | ADPC0 |

| ADP | ADP   | ADP  |       | ADP |                |                   | Analog input (A)/digital I/O (D) switching |                |   |   |               |               |              |              | witchi       | ng           |              |              |              |              |

|-----|-------|------|-------|-----|----------------|-------------------|--------------------------------------------|----------------|---|---|---------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| C4  | C3    | C2   | C1    | C0  |                | Port 15           |                                            |                |   |   |               | Port 2        |              |              |              |              |              |              |              |              |

|     |       |      |       |     | ANI15/<br>P157 | ANI14/<br>P156    | ANI13/<br>P155                             | ANI12/<br>P154 | - |   | ANI9/<br>P151 | ANI8/<br>P150 | ANI7/<br>P27 | ANI6/<br>P26 | ANI5/<br>P25 | ANI4/<br>P24 | ANI3/<br>P23 | ANI2/<br>P22 | ANI1/<br>P21 | ANI0/<br>P20 |

| 0   | 0     | 0    | 0     | 0   | А              | А                 | А                                          | А              | А | Α | А             | А             | А            | Α            | А            | А            | А            | А            | А            | А            |

| 0   | 0     | 0    | 0     | 1   | А              | Α                 | А                                          | А              | А | Α | А             | Α             | Α            | Α            | Α            | Α            | Α            | А            | Α            | D            |

| 0   | 0     | 0    | 1     | 0   | А              | А                 | А                                          | А              | А | А | А             | А             | Α            | А            | А            | А            | А            | А            | D            | D            |

| 0   | 0     | 0    | 1     | 1   | А              | Α                 | А                                          | А              | А | Α | А             | А             | А            | Α            | А            | А            | А            | D            | D            | D            |

| 0   | 0     | 1    | 0     | 0   | А              | А                 | А                                          | А              | А | А | А             | А             | А            | А            | А            | Α            | D            | D            | D            | D            |

| 0   | 0     | 1    | 0     | 1   | А              | Α                 | Α                                          | Α              | Α | Α | А             | Α             | Α            | Α            | Α            | D            | D            | D            | D            | D            |

| 0   | 0     | 1    | 1     | 0   | А              | Α                 | А                                          | А              | А | А | А             | А             | А            | Α            | D            | D            | D            | D            | D            | D            |

| 0   | 0     | 1    | 1     | 1   | А              | Α                 | А                                          | А              | А | Α | А             | Α             | Α            | D            | D            | D            | D            | D            | D            | D            |

| 0   | 1     | 0    | 0     | 0   | А              | Α                 | А                                          | А              | А | А | А             | А             | D            | D            | D            | D            | D            | D            | D            | D            |

| 0   | 1     | 0    | 0     | 1   | А              | А                 | А                                          | А              | А | А | А             | D             | D            | D            | D            | D            | D            | D            | D            | D            |

| 0   | 1     | 0    | 1     | 0   | А              | А                 | А                                          | А              | А | А | D             | D             | D            | D            | D            | D            | D            | D            | D            | D            |

| 0   | 1     | 0    | 1     | 1   | А              | Α                 | Α                                          | Α              | Α | D | D             | D             | D            | D            | D            | D            | D            | D            | D            | D            |

| 0   | 1     | 1    | 0     | 0   | А              | Α                 | Α                                          | Α              | D | D | D             | D             | D            | D            | D            | D            | D            | D            | D            | D            |

| 0   | 1     | 1    | 0     | 1   | А              | Α                 | Α                                          | D              | D | D | D             | D             | D            | D            | D            | D            | D            | D            | D            | D            |

| 0   | 1     | 1    | 1     | 0   | А              | А                 | D                                          | D              | D | D | D             | D             | D            | D            | D            | D            | D            | D            | D            | D            |

| 0   | 1     | 1    | 1     | 1   | А              | D                 | D                                          | D              | D | D | D             | D             | D            | D            | D            | D            | D            | D            | D            | D            |

| 1   | 0     | 0    | 0     | 0   | D              |                   |                                            |                |   |   |               |               | D            |              |              |              |              |              |              |              |

|     | Other | than | above | )   | Setti          | etting prohibited |                                            |                |   |   |               |               |              |              |              |              |              |              |              |              |

Cautions 1. Set the channel used for A/D conversion to the input mode by using port mode registers 2 and 15 (PM2, PM15).

- 2. Do not set the pin set by the ADPC register as digital I/O by the analog input channel specification register (ADS).

- 3. P20/ANI0 to P27/ANI7 and P150/ANI8 to P157/ANI15 are set as analog inputs in the order of P157/ANI15, ..., P150/ANI8, P27/ANI7, ..., P20/ANI0 by the A/D port configuration register (ADPC). When using P20/ANI0 to P27/ANI7 and P150/ANI8 to P157/ANI15 as analog inputs, start designing from P157/ANI15.

- 4. Be sure to first set the ADCEN bit of peripheral enable register 0 (PER0) to 1 when setting up the ADPC register. If ADCEN = 0, writing to the ADPC register is ignored and specified values are returned to the initial values.

Remark

P20/ANI0 to P27/ANI7, P150/ANI8 to P153/ANI11:

78K0R/KF3-L

P20/ANI0 to P27/ANI7, P150/ANI8 to P157/ANI15:

78K0R/KG3-L

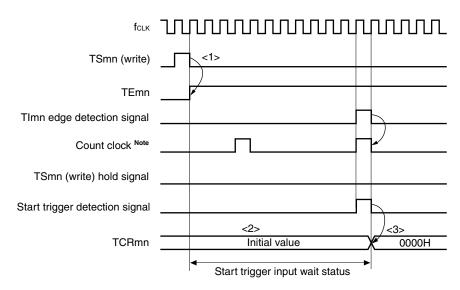

# (e) Start timing in capture & one-count mode

<1> Operation is enabled (TEmn = 1) by writing 1 to the TSmn bit.

<2> Enters the start trigger input wait status, and timer/counter register mn (TCRmn) holds the initial value.</3> On start trigger detection, 0000H is loaded to the TCRmn register and count starts.

Figure 8-19. Start Timing (In Capture & One-count Mode)

- **Note** When the capture & one-count mode is set, the operation clock (f<sub>MCK</sub>) is selected as count clock (CCSmn = 0).

- Caution An input signal sampling error is generated since operation starts upon start trigger detection (If the TImn pin input signal is used as a start trigger, an error of one count clock occurs.)

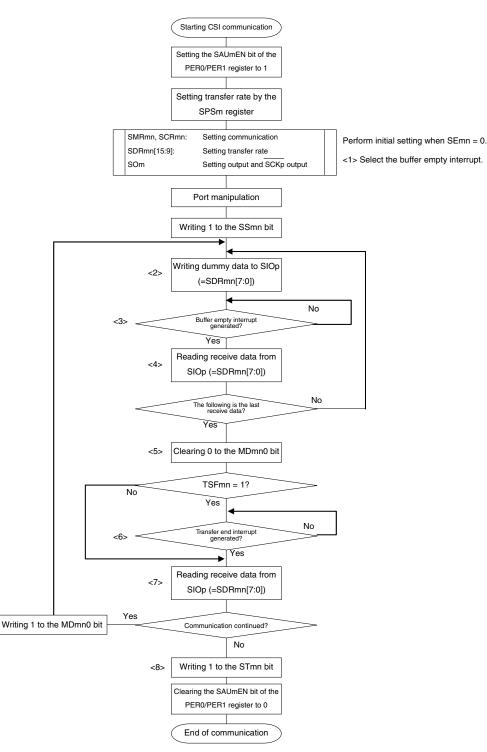

### Figure 14-43. Flowchart of Master Reception (in Continuous Reception Mode)

- Caution After setting the PER0/PER1 register to 1, be sure to set the SPSm register after 4 or more clocks have elapsed.

- **Remark** <1> to <8> in the figure correspond to <1> to <8> in **Figure 14-42 Timing Chart of Master Reception** (in Continuous Reception Mode).

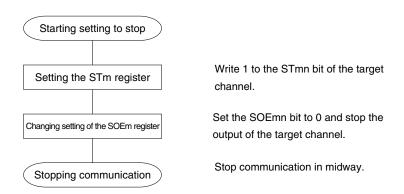

### Figure 14-54. Procedure for Stopping Slave Transmission

**Remark** Even after communication is stopped, the pin level is retained. To resume the operation, re-set the SOm register (see Figure 14-55 Procedure for Resuming Slave Transmission).

# 14.6 Operation of UART (UART0 to UART4) Communication

This is a start-stop synchronization function using two lines: serial data transmission (TxD) and serial data reception (RxD) lines. By using these two communication lines, each data frame, which consist of a start bit, data, parity bit, and stop bit, is transferred asynchronously (using the internal baud rate) between the microcontroller and the other communication party. Full-duplex UART communication can be performed by using a channel dedicated to transmission (even-numbered channel) and a channel dedicated to reception (odd-numbered channel). The LIN-bus can be implemented by using timer array unit 0 with an external interrupt (INTP0).

[Data transmission/reception]

- Data length of 5, 7, or 8 bits

- Select the MSB/LSB first

- Level setting of transmit/receive data and select of reverse

- Parity bit appending and parity check functions

- Stop bit appending

- [Interrupt function]

- Transfer end interrupt/buffer empty interrupt

- Error interrupt in case of framing error, parity error, or overrun error

[Error detection flag]

• Framing error, parity error, or overrun error

The LIN-bus is accepted in UART0 of the 78K0R/KC3-L, 78K0R/KD3-L, 78K0R/KE3-L and UART3 of the 78K0R/KF3-L, 78K0R/KG3-L.

[LIN-bus functions]

- Wakeup signal detection

- Sync break field (SBF) detection

- · Sync field measurement, baud rate calculation

Using the external interrupt (INTP0) and timer array unit 0

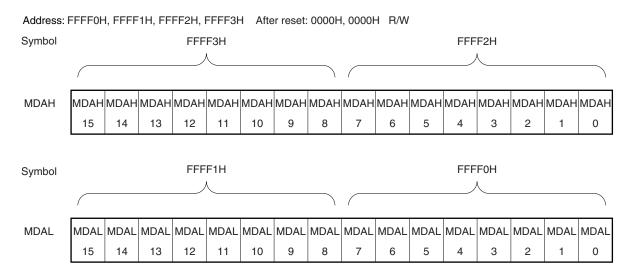

# (1) Multiplication/division data register A (MDAH, MDAL)

The MDAH and MDAL registers set the values that are used for a multiplication or division operation and store the operation result. They set the multiplier and multiplicand data in the multiplication mode, and set the dividend data in the division mode. Furthermore, the operation result (quotient) is stored in the MDAH and MDAL registers in the division mode.

The MDAH and MDAL registers can be set by a 16-bit manipulation instruction. Reset signal generation clears these registers to 0000H.

## Figure 16-2. Format of Multiplication/Division Data Register A (MDAH, MDAL)

- Cautions 1. Do not rewrite the MDAH and MDAL registers values during division operation processing (while the multiplication/division control register (MDUC) is 81H). The operation will be executed in this case, but the operation result will be an undefined value.

- 2. The MDAH and MDAL registers values read during division operation processing (while MDUC is 81H) will not be guaranteed.

The following table shows the functions of the MDAH and MDAL registers during operation execution.

| DIVMODE | Operation Mode      | Setting                        | Operation Result                 |

|---------|---------------------|--------------------------------|----------------------------------|

| 0       | Multiplication mode | MDAH: Multiplier               | _                                |

|         |                     | MDAL: Multiplicand             |                                  |

| 1       | Division mode       | MDAH: Divisor (higher 16 bits) | MDAH: Division result (quotient) |

|         |                     | MDAL: Dividend (lower 16 bits) | Higher 16 bits                   |

|         |                     |                                | MDAL: Division result (quotient) |

|         |                     |                                | Lower 16 bits                    |

Remark DIVMODE: Bit 7 of the multiplication/division control register (MDUC)

# 17.5.2 Consecutive capturing of A/D conversion results

- A flowchart of an example of setting for consecutively capturing A/D conversion results is shown below.

- Consecutive capturing of A/D conversion results.

- DMA channel 1 is used for DMA transfer.

- DMA start source: INTAD

- Interrupt of A/D is specified by IFC13 to IFC10 = 1100B.

- Transfers FFF1EH and FFF1FH (2 bytes) of the 10-bit A/D conversion result register (ADCR) to 512 bytes of FFCE0H to FFEDFH of RAM.

Remark IFC13 to IFC10: Bits 3 to 0 of DMA mode control registers 1 (DMC1)

|                       | Hardware                                                          | Status After Reset<br>Acknowledgment <sup>Note 1</sup> |

|-----------------------|-------------------------------------------------------------------|--------------------------------------------------------|

| Serial interface IICA | IICA shift register (IICA)                                        | 00H                                                    |

|                       | IICA status register (IICS)                                       | 00H                                                    |

|                       | IICA flag register (IICF)                                         | 00H                                                    |

|                       | IICA control register 0 (IICCTL0)                                 | 00H                                                    |

|                       | IICA control register 1 (IICCTL1)                                 | 00H                                                    |

|                       | IICA low-level width setting register (IICWL)                     | FFH                                                    |

|                       | IICA high-level width setting register (IICWH)                    | FFH                                                    |

|                       | Slave address register (SVA)                                      | 00H                                                    |

| Multiplier/divider    | Multiplication/division data register A (L) (MDAL)                | 0000H                                                  |

|                       | Multiplication/division data register A (H) (MDAH)                | 0000H                                                  |

|                       | Multiplication/division data register B (L) (MDBL)                | 0000H                                                  |

|                       | Multiplication/division data register B (H) (MDBH)                | 0000H                                                  |

|                       | Multiplication/division data register C (L) (MDCL)                | 0000H                                                  |

|                       | Multiplication/division data register C (H) (MDCH)                | 0000H                                                  |

|                       | Multiplication/division control register (MDUC)                   | 00H                                                    |

| Key interrupt         | Key return mode register (KRM)                                    | 00H                                                    |

| Reset function        | Reset control flag register (RESF)                                | 00H <sup>Note 2</sup>                                  |

| Low-voltage detector  | Low-voltage detection register (LVIM)                             | 00H <sup>Note 3</sup>                                  |

|                       | Low-voltage detection level select register (LVIS)                | 0EH <sup>Note 2</sup>                                  |

| Regulator             | Regulator mode control register (RMC)                             | 00H                                                    |

| DMA controller        | SFR address registers 0, 1 (DSA0, DSA1)                           | 00H                                                    |

|                       | RAM address registers 0L, 0H, 1L, 1H (DRA0L, DRA0H, DRA1L, DRA1H) | 00H                                                    |

|                       | Byte count registers 0L, 0H, 1L, 1H (DBC0L, DBC0H, DBC1L, DBC1H)  | 00H                                                    |

|                       | Mode control registers 0, 1 (DMC0, DMC1)                          | 00H                                                    |

|                       | Operation control registers 0, 1 (DRC0, DRC1)                     | 00H                                                    |

**Notes 1.** During reset signal generation or oscillation stabilization time wait, only the PC contents among the hardware statuses become undefined. All other hardware statuses remain unchanged after reset.

2. These values vary depending on the reset source.

| Register | Reset Source | RESET Input   | Reset by POC  | Reset by<br>Execution of Illegal<br>Instruction | Reset by WDT  | Reset by INIRF | Reset by LVI |

|----------|--------------|---------------|---------------|-------------------------------------------------|---------------|----------------|--------------|

| RESF     | TRAP bit     | Cleared (0)   | Cleared (0)   | Set (1)                                         | Held          | Held           | Held         |

|          | WDRF bit     |               |               | Held                                            | Set (1)       | Held           | Held         |

|          | INIRF bit    |               |               | Held                                            | Held          | Set (1)        | Held         |

|          | LVIRF bit    |               |               | Held                                            | Held          | Held           | Set (1)      |

| LVIS     |              | Cleared (0EH) | Cleared (0EH) | Cleared (0EH)                                   | Cleared (0EH) | Cleared (0EH)  | Held         |

3. This value varies depending on the reset source and the option byte.

Remark The special function register (SFR) mounted depend on the product. See 4.2.4 Special function registers (SFRs) and 4.2.5 Extended special function registers (2nd SFRs: 2nd Special Function Registers).

| Dedicated Flash Memory Programmer |        |                                          | 78K0R/Kx3-L                    | Connection |

|-----------------------------------|--------|------------------------------------------|--------------------------------|------------|

| Signal Name                       | I/O    | Pin Function                             | Pin Name                       |            |

| FLMD0                             | Output | Mode signal                              | FLMD0                          | 0          |

| VDD                               | I/O    | V_DD voltage generation/power monitoring | VDD, EVDD, EVDD0, EVDD1, AVREF | 0          |

| GND                               | _      | Ground                                   | Vss, EVss, EVsso, EVss1, AVss  | 0          |

| CLK                               | Output | Clock output                             | _                              | ×          |

| /RESET                            | Output | Reset signal                             | RESET                          | 0          |

| SI/RxD <sup>Notes1, 2</sup>       | Input  | Receive signal                           | TOOL0                          | 0          |

| SO/TxD Note2                      | Output | Transmit signal                          |                                |            |

| SCK                               | Output | Transfer clock                           | -                              | ×          |

Table 26-2. Pin Connection

Notes 1. This pin is not required to be connected when using PG-FP5 or FL-PR5.

2. Connect SI/RxD or SO/TxD when using QB-MINI2.

**Remark**  $\bigcirc$ : Be sure to connect the pin.

$\times$ : The pin does not have to be connected.

# 26.4 Connection of Pins on Board

To write the flash memory on-board, connectors that connect the dedicated flash memory programmer must be provided on the target system. First provide a function that selects the normal operation mode or flash memory programming mode on the board.

When the flash memory programming mode is set, all the pins not used for programming the flash memory are in the same status as immediately after reset. Therefore, if the external device does not recognize the state immediately after reset, the pins must be handled as described below.

#### 26.4.1 FLMD0 pin

#### (1) In flash memory programming mode

Directly connect this pin to a flash memory programmer when data is written by the flash memory programmer. This supplies a writing voltage of the VDD level to the FLMD0 pin.

The FLMD0 pin does not have to be pulled down externally because it is internally pulled down by reset. To pull it down externally, use a resistor of 1 k $\Omega$  to 200 k $\Omega$ .

#### (2) In normal operation mode

It is recommended to leave this pin open during normal operation.

The FLMD0 pin must always be kept at the Vss level before reset release but does not have to be pulled down externally because it is internally pulled down by reset. However, pulling it down must be kept selected (i.e., FLMDPUP = "0", default value) by using bit 7 (FLMDPUP) of the background event control register (BECTL) (see **26.5** (1) Back ground event control register). To pull it down externally, use a resistor of 200 k $\Omega$  or smaller.

Self programming and the rewriting of flash memory with the programmer can be prohibited using hardware, by directly connecting this pin to the Vss pin.

Caution The pins mounted depend on the product. Refer to Caution 2 at the beginning of this chapter.

| Parameter                                               | Symbol        | Conditions                            |                                       | MIN.      | TYP. | MAX.       | Unit |

|---------------------------------------------------------|---------------|---------------------------------------|---------------------------------------|-----------|------|------------|------|

| SCKp cycle time                                         | <b>t</b> ксү2 | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |                                       | 6/fмск    |      |            | ns   |

|                                                         |               | $1.8 V \le V_{DD} < 4.0 V$            | 0 16 MHz < fмск                       | 8/fмск    |      |            | ns   |

|                                                         |               |                                       | fмск ≤ 16 MHz                         | 6/fмск    |      |            | ns   |

| SCKp high-/low-level width                              | tкн2,<br>tк∟2 |                                       |                                       | tксү2/2   |      |            | ns   |

| SIp setup time<br>(to SCKp↑) <sup>Note 1</sup>          | tsik2         |                                       |                                       | 80        |      |            | ns   |

| SIp hold time<br>(from SCKp↑) <sup>№te 2</sup>          | tksi2         |                                       |                                       | 1/fмск+50 |      |            | ns   |

| Delay time from $\overline{\mathrm{SCKp}}\downarrow$ to | tkso2         | $C = 30 \text{ pF}^{Note 4}$          | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |           |      | 2/fмск+45  | ns   |

| SOp output <sup>Note 3</sup>                            |               |                                       | $2.7~V \leq V_{\text{DD}} < 4.0~V$    |           |      | 2/fмск+57  | ns   |