Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detalls                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | 78K/0R                                                                               |

| Core Size                  | 16-Bit                                                                               |

| Speed                      | 20MHz                                                                                |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                     |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                              |

| Number of I/O              | 41                                                                                   |

| Program Memory Size        | 32KB (32K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 1.5K x 8                                                                             |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                          |

| Data Converters            | A/D 11x10b                                                                           |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 48-TQFP                                                                              |

| Supplier Device Package    | 48-TQFP (7x7)                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f1001ga-haa-ax |

|                            |                                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

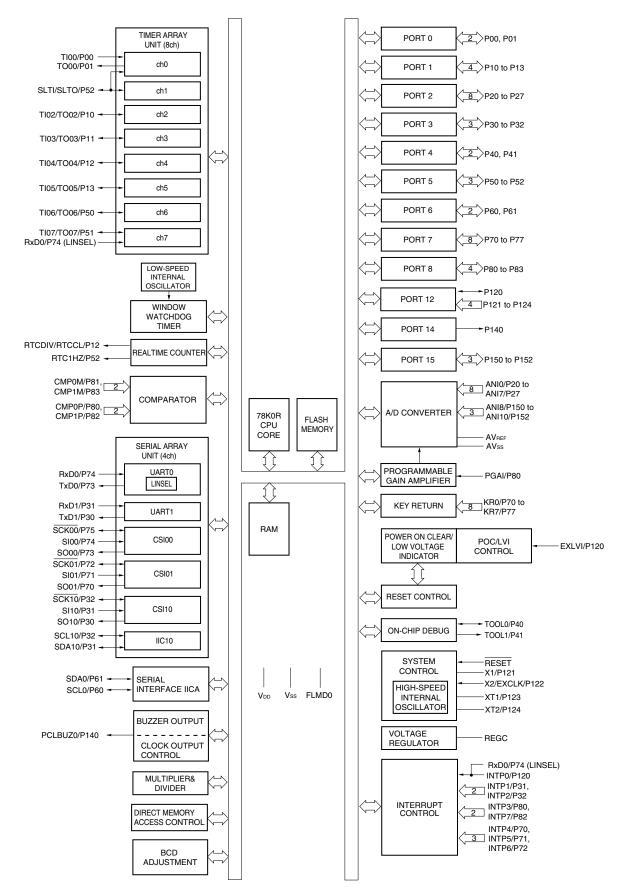

### 1.6.2 78K0R/KD3-L

RENESAS

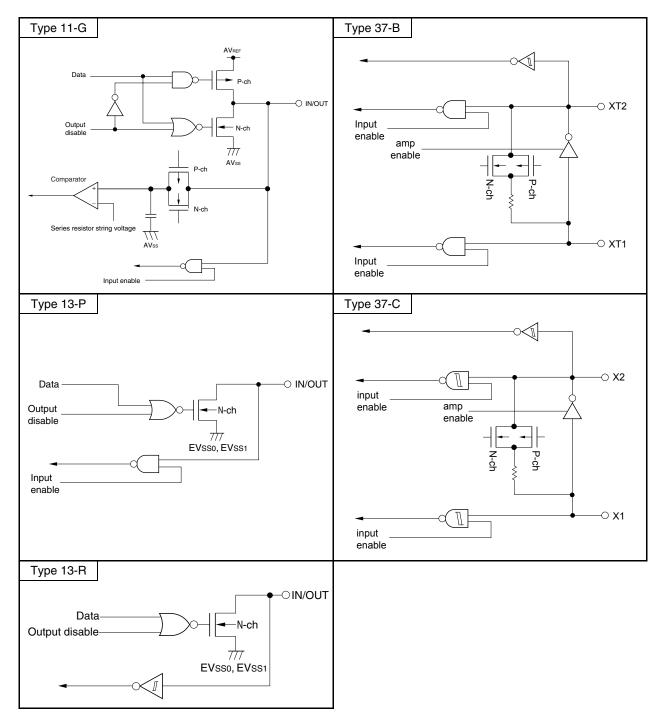

Figure 3-1. Pin I/O Circuit List (2/2)

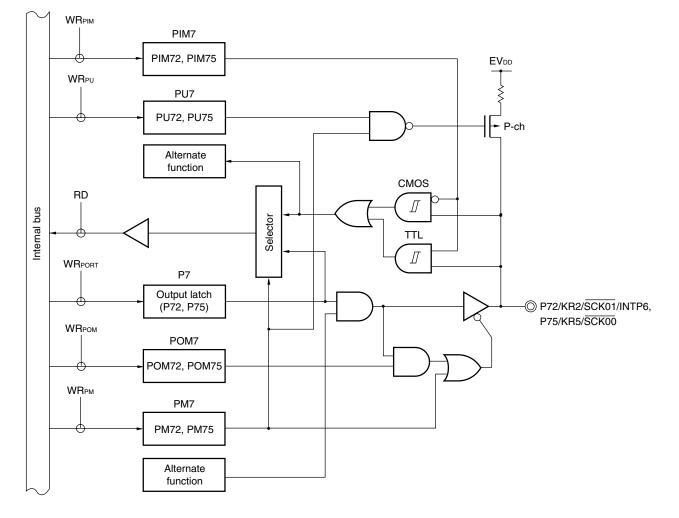

Figure 5-17. Block Diagram of P72 and P75

- P7: Port register 7

- PU7: Pull-up resistor option register 7

- PM7: Port mode register 7

- PIM7: Port input mode register 7

- POM7: Port output mode register 7

- RD: Read signal

- WR××: Write signal

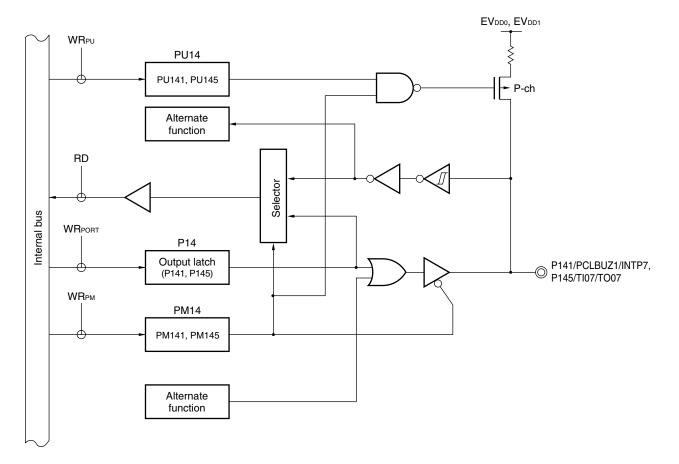

Remark With products not provided with an EVDD or EVss pin, replace EVDD with VDD, or replace EVss with Vss.

### (6) A/D port configuration register (ADPC)

This register switches the ANI0/P20 to ANI7/P27 and ANI8/P150 to ANI11/P153 pins to digital I/O of port or analog input of A/D converter.

The ADPC register can be set by an 8-bit memory manipulation instruction.

Reset signal generation sets this register to 10H.

#### Figure 5-41. Format of A/D Port Configuration Register (ADPC)

| Address | : F0017H | After reset: 10H | R/W |       |       |       |       |       |

|---------|----------|------------------|-----|-------|-------|-------|-------|-------|

| Symbol  | 7        | 6                | 5   | 4     | 3     | 2     | 1     | 0     |

| ADPC    | 0        | 0                | 0   | ADPC4 | ADPC3 | ADPC2 | ADPC1 | ADPC0 |

| ADPC4 | ADPC3 | ADPC2    | ADPC1 | ADPC0 |         | Analog input (A)/digital I/O (D) switching |        |       |        |      |      |      |      |      |      |      |

|-------|-------|----------|-------|-------|---------|--------------------------------------------|--------|-------|--------|------|------|------|------|------|------|------|

|       |       |          |       |       | Port 15 |                                            |        |       | Port 2 |      |      |      |      |      |      |      |

|       |       |          |       |       | ANI11   | ANI10                                      | ANI9   | ANI8  | ANI7   | ANI6 | ANI5 | ANI4 | ANI3 | ANI2 | ANI1 | ANI0 |

|       |       |          |       |       | /P153   | /P152                                      | /P151  | /P150 | /P27   | /P26 | /P25 | /P24 | /P23 | /P22 | /P21 | /P20 |

| 0     | 0     | 0        | 0     | 0     | А       | А                                          | А      | А     | А      | А    | А    | А    | А    | А    | А    | А    |

| 0     | 0     | 0        | 0     | 1     | А       | А                                          | А      | А     | А      | А    | А    | А    | А    | А    | А    | D    |

| 0     | 0     | 0        | 1     | 0     | А       | А                                          | А      | А     | А      | А    | А    | А    | А    | А    | D    | D    |

| 0     | 0     | 0        | 1     | 1     | А       | А                                          | А      | А     | А      | А    | А    | А    | А    | D    | D    | D    |

| 0     | 0     | 1        | 0     | 0     | А       | А                                          | А      | А     | А      | А    | А    | А    | D    | D    | D    | D    |

| 0     | 0     | 1        | 0     | 1     | А       | А                                          | А      | А     | А      | А    | А    | D    | D    | D    | D    | D    |

| 0     | 0     | 1        | 1     | 0     | А       | А                                          | А      | А     | А      | А    | D    | D    | D    | D    | D    | D    |

| 0     | 0     | 1        | 1     | 1     | А       | А                                          | А      | А     | А      | D    | D    | D    | D    | D    | D    | D    |

| 0     | 1     | 0        | 0     | 0     | А       | А                                          | А      | А     | D      | D    | D    | D    | D    | D    | D    | D    |

| 0     | 1     | 0        | 0     | 1     | А       | А                                          | А      | D     | D      | D    | D    | D    | D    | D    | D    | D    |

| 0     | 1     | 0        | 1     | 0     | А       | А                                          | D      | D     | D      | D    | D    | D    | D    | D    | D    | D    |

| 0     | 1     | 0        | 1     | 1     | А       | D                                          | D      | D     | D      | D    | D    | D    | D    | D    | D    | D    |

| 1     | 0     | 0        | 0     | 0     | D       | D                                          | D      | D     | D      | D    | D    | D    | D    | D    | D    | D    |

|       | Other | than the | above |       | Settir  | ng proh                                    | ibited |       |        |      |      |      |      |      |      |      |

Cautions 1. Set a channel to be used for A/D conversion in the input mode by using port mode register 2 and 15 (PM2, PM15).

- 2. Do not set the pin that is set by the ADPC register as digital I/O by the analog input channel specification register (ADS).

- 3. Be sure to first set the ADCEN bit of peripheral enable register 0 (PER0) to 1 when setting up the ADPC register. If ADCEN = 0, writing to the ADPC register is ignored and specified values are returned to the initial values.

Remark

P20/ANI0 to P27/ANI7, P150/ANI8, and P151/ANI9: 78K0R/KC3-L (40-pin, 44-pin)

P20/ANI0 to P27/ANI7, P150/ANI8 to P152/ANI10: 78K0R/KC3-L (48-pin), 78K0R/KD3-L

P20/ANI0 to P27/ANI7, P150/ANI8 to P153/ANI11: 78K0R/KE3-L

Figure 6-48. Block Diagram of P141 and P145

- P14: Port register 14

- PU14: Pull-up resistor option register 14

- PM14: Port mode register 14

- RD: Read signal

- WR x: Write signal

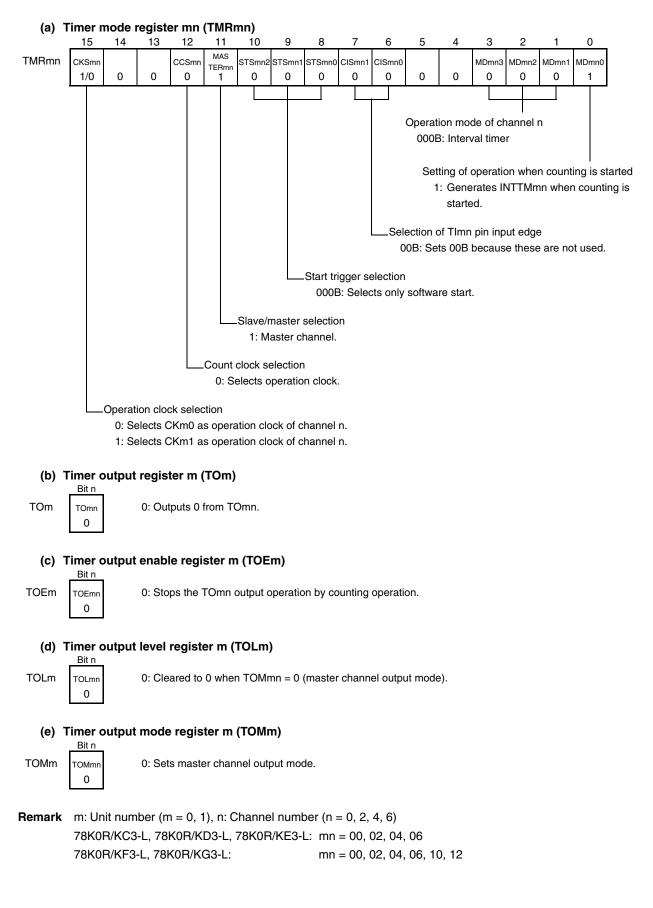

# 8.3 Registers Controlling Timer Array Unit

Timer array unit is controlled by the following registers.

- Peripheral enable registers 0, 2 (PER0, PER2) Note 1

- Timer clock select register m (TPSm)

- Timer mode register mn (TMRmn)

- Timer status register mn (TSRmn)

- Timer channel enable status register m (TEm)

- Timer channel start register m (TSm)

- Timer channel stop register m (TTm)

- Timer input select register m (TISm)

- Timer output enable register m (TOEm)

- Timer output register m (TOm)

- Timer output level register m (TOLm)

- Timer output mode register m (TOMm)

- Input switch control register (ISC)

- Noise filter enable registers 1, 2 (NFEN1, NFEN2)

- Port mode register (PMxx)<sup>Note 2</sup>

- Port register (Pxx) Note 2

- Notes 1. Set the PER2 register in the 78K0R/KC3-L, 78K0R/KD3-L, and 78K0R/KE3-L. Set the PER0 register in the 78K0R/KF3-L and 78K0R/KG3-L.

- 2. The port mode registers (PMxx) and port registers (Pxx) to be set differ depending on the product. for details, see 8.3 (15) Port mode registers 0, 1, 3 to 6, 13, 14 (PM0, PM1, PM3 to PM6, PM13, PM14).

- Remark

m: Unit number (m = 0, 1), n: Channel number (n = 0 to 7)

78K0R/KC3-L, 78K0R/KD3-L, 78K0R/KE3-L:

mn = 00 to 07

78K0R/KF3-L, 78K0R/KG3-L:

mn = 00 to 07, 10 to 13

## (5) Timer channel enable status register m (TEm)

The TEm register is used to enable or stop the timer operation of each channel.

When a bit of timer channel start register m (TSm) is set to 1, the corresponding bit of this register is set to 1. When a bit of timer channel stop register m (TTm) is set to 1, the corresponding bit of this register is cleared to 0. The TEm register can be read by a 16-bit memory manipulation instruction.

The lower 8 bits of the TEm register can be set with a 1-bit or 8-bit memory manipulation instruction with TEmL. Reset signal generation clears this register to 0000H.

#### Figure 8-13. Format of Timer Channel Enable Status register m (TEm)

| Address: F01 | B0H, F0 | )1B1H | After | reset: 0 | 000H | R  |   |   |      |      |      |      |      |      |      |      |

|--------------|---------|-------|-------|----------|------|----|---|---|------|------|------|------|------|------|------|------|

| Symbol       | 15      | 14    | 13    | 12       | 11   | 10 | 9 | 8 | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| TE0          | 0       | 0     | 0     | 0        | 0    | 0  | 0 | 0 | TE07 | TE06 | TE05 | TE04 | TE03 | TE02 | TE01 | TE00 |

|              |         |       |       |          |      |    |   |   |      |      |      |      |      |      |      |      |

| Address: F01 | D8H, F( | 01D9H | After | reset: C | 000H | R  |   |   |      |      |      |      |      |      |      |      |

| Symbol       | 15      | 14    | 13    | 12       | 11   | 10 | 9 | 8 | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| TE1          | 0       | 0     | 0     | 0        | 0    | 0  | 0 | 0 | 0    | 0    | 0    | 0    | TE13 | TE12 | TE11 | TE10 |

|              |         |       |       |          |      |    |   |   |      |      |      |      |      |      |      |      |

|              |         |       |       |          |      |    |   |   |      |      |      |      |      |      |      |      |

| TEmn | Indication of operation enable/stop status of channel n |

|------|---------------------------------------------------------|

| 0    | Operation is stopped.                                   |

| 1    | Operation is enabled.                                   |

Remark

m: Unit number (m = 0, 1), n: Channel number (n = 0 to 7)

78K0R/KC3-L, 78K0R/KD3-L, 78K0R/KE3-L:

mn = 00 to 07

78K0R/KF3-L, 78K0R/KG3-L:

mn = 00 to 07, 10 to 13

mn = 00 to 07

mn = 00 to 07

#### Figure 8-68. Example of Set Contents of Registers When PWM Function (Master Channel) Is Used

|                     | Software Operation                                                                                                                                                                                                                                                                                                                                                                                 | Hardware Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation<br>start  | Sets the TOEmp bit (slave) to 1 (only when operation is<br>resumed).<br>The TSmn (master) and TSmp (slave) bits of timer<br>channel start register m (TSm) are set to 1 at the same<br>time.<br>The TSmn and TSmp bits automatically return to 0<br>because they are trigger bits.                                                                                                                 | <ul> <li>TEmn = 1, TEmp = 1</li> <li>▶ When the master channel starts counting, INTTMmn is generated. Triggered by this interrupt, the slave channel also starts counting.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| During<br>operation | Set values of the TMRmn and TMRmp registers,<br>TOMmn, TOMmp, TOLmn, and TOLmp bits cannot be<br>changed.<br>Set values of the TDRmn and TDRmp registers can be<br>changed after INTTMmn of the master channel is<br>generated.<br>The TCRmn and TCRmp registers can always be read.<br>The TSRmn and TSRmp registers are not used.<br>Set values of the TOm and TOEm registers can be<br>changed. | The counter of the master channel loads the TDRmn<br>register value to timer/counter register mn (TCRmn), and<br>counts down. When the count value reaches TCRmn =<br>0000H, INTTMmn output is generated. At the same time<br>the value of the TDRmn register is loaded to the TCRmn<br>register, and the counter starts counting down again.<br>At the slave channel, the value of the TDRmp register is<br>loaded to the TCRmp register, triggered by INTTMmn of<br>the master channel, and the counter starts counting dow<br>The output level of TOmp becomes active one count clo<br>after generation of the INTTMmn output from the master<br>channel. It becomes inactive when TCRmp = 0000H, ar<br>the counting operation is stopped.<br>After that, the above operation is repeated. |

| Operation<br>stop   | The TTmn (master) and TTmp (slave) bits are set to 1 at<br>the same time.<br>The TTmn and TTmp bits automatically return to 0<br>because they are trigger bits.                                                                                                                                                                                                                                    | <ul> <li>TEmn, TEmp = 0, and count operation stops.</li> <li>The TCRmn and TCRmp registers hold count value a stop.</li> <li>The TOmp output is not initialized but holds current status.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                     | The TOEmp bit of slave channel is cleared to 0 and value                                                                                                                                                                                                                                                                                                                                           | The TOmp pin outputs the TOmp set level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| TAU<br>stop         | be held is set to the port register.<br>When holding the TOmp pin output level is not                                                                                                                                                                                                                                                                                                              | The TOmp pin output level is held by port function.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                     | The TAU0EN and TAU1EN bits of the PER0 and PER2                                                                                                                                                                                                                                                                                                                                                    | The TOmp pin output level goes into Hi-Z output state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                     | N.A.                                                                                                                                                                                                                                                                                                                                                                                               | Power-off status<br>All circuits are initialized and SFR of each channel is<br>also initialized.<br>(The TOmp bit is cleared to 0 and the TOmp pin is se<br>to port mode.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Figure 8-70. | <b>Operation Procedu</b> | re When PWM                             | Function Is | Used (2/2) |

|--------------|--------------------------|-----------------------------------------|-------------|------------|

|              | ••••••••                 | ••••••••••••••••••••••••••••••••••••••• |             |            |

**Remark** m: Unit number (m = 0, 1), n: Channel number (n = 0, 2, 4, 6)78K0R/KC3-L, 78K0R/KD3-L, 78K0R/KE3-L: mn = 00, 02, 04, 06 78K0R/KF3-L, 78K0R/KG3-L: mn = 00, 02, 04, 06, 10, 12 p: Slave channel number<sup>Note</sup> When m = 0: nWhen m = 1: n

> Note Since there is no function of timer I/O, the channel 1 in the 78K0R/KC3-L (40-pin) can not be used as the slave channel.

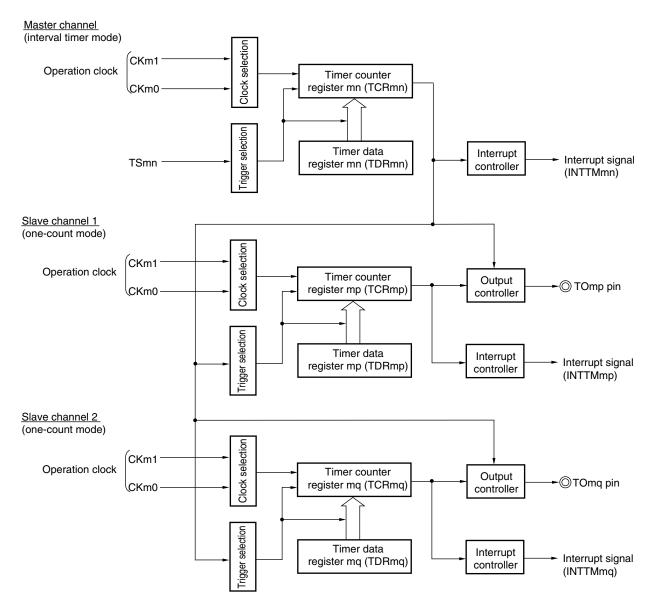

#### Figure 8-71. Block Diagram of Operation as Multiple PWM Output Function (output two types of PWMs)

- Remarkm: Unit number (m = 0, 1), n: Channel number (n = 0, 2, 4)78K0R/KC3-L, 78K0R/KD3-L, 78K0R/KE3-L:mn = 00, 02, 0478K0R/KF3-L, 78K0R/KG3-L:mn = 00, 02, 04, 10p: Slave channel number 1, q: Slave channel number  $2^{Note}$ When m = 0: n \leq 7When m = 1: n \leq 3(Where p and q are consecutive integers greater than n)

- **Note** Since there is no function of timer I/O, the channel 1 in the 78K0R/KC3-L (40-pin) can not be used as the slave channel.

# Figure 8-72. Example of Basic Timing of Operation as Multiple PWM Output Function (output two types of PWMs) (2/2)

Remarks1. m: Unit number (m = 0, 1), n: Channel number (n = 0, 2, 4)78K0R/KC3-L, 78K0R/KD3-L, 78K0R/KE3-L: mn = 00, 02, 0478K0R/KF3-L, 78K0R/KG3-L: mn = 00, 02, 04, 10p: Slave channel number 1, q: Slave channel number  $2^{Note}$ When m = 0: n \leq 7When m = 1: n \leq 3(Where p and q are consecutive integers greater than n)

- **Note** Since there is no function of timer I/O, channel 1 in the 78K0R/KC3-L (40-pin) can not used as slave channel.

- TSmn, TSmp, TSmq: Bit n, p, q of timer channel start register m (TSm)

TEmn, TEmp, TEmq: Bit n, p, q of timer channel enable status register m (TEm)

TCRmn, TCRmp, TCRmq: Timer/counter registers mn, mp, mq (TCRmn, TCRmp, TCRmq)

TDRmn, TDRmp, TDRmq: Timer data registers mn, mp, mq (TDRmn, TDRmp, TDRmq)

TOmn, TOmp, TOmq: TOmn, TOmp, and TOmq pins output signal

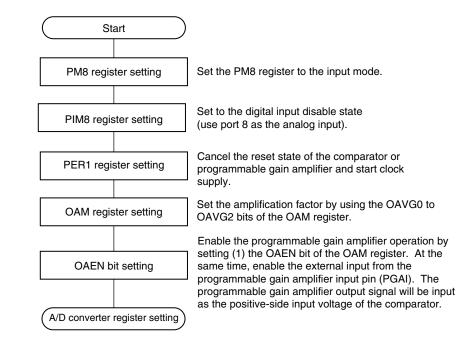

Perform the following settings before selecting the programmable gain amplifier output signal as the analog input by using the analog input channel specification register (ADS) of the A/D converter (refer to **13.4.1 Basic operations of A/D converter**).

Figure 10-13. Using the Programmable Gain Amplifier Output Voltage as the A/D Converter Analog Input

Caution Ensure that 3  $\mu$ s elapses before A/D conversion starts after setting the OAEN bit.

**Remark** n = 0, 1

# 13.4 A/D Converter Operations

#### 13.4.1 Basic operations of A/D converter

- <1> Set bit 5 (ADCEN) of peripheral enable register 0 (PER0) to 1 to start the supply of the input clock to the A/D converter.

- <2> Set the A/D conversion time by using bits 5 to 1 (FR2 to FR0, LV1, and LV0) of the A/D converter mode register (ADM), and set the operation mode by using bit 6 (ADMD) of the ADM register.

- <3> Set bit 0 (ADCE) of the ADM register to 1 to start the operation of the A/D voltage comparator.

- <4> Set the channels for A/D conversion to analog input by using the A/D port configuration register (ADPC) and set to input mode by using the port mode registers (PM2, PM15, and PM8).

- <5> Set the programmable gain amplifier operation to set the programmable gain amplifier output (PGAI pin) for the analog input channel (refer to **10.4.1 Starting comparator and programmable gain amplifier operation**).

- <6> Select one channel for A/D conversion using the analog input channel specification register (ADS).

- <7> Start the conversion operation by setting bit 7 (ADCS) of the ADM register to 1. (<8> to <14> are operations performed by hardware.)

- <8> The voltage input to the selected analog input channel is sampled by the sample & hold circuit.

- <9> When sampling has been done for a certain time, the sample & hold circuit is placed in the hold state and the sampled voltage is held until the A/D conversion operation has ended.

- <10> Bit 9 of the successive approximation register (SAR) is set. The series resistor string voltage tap is set to (1/2) AVREF by the tap selector.

- <11> The voltage difference between the series resistor string voltage tap and sampled voltage is compared by the voltage comparator. If the analog input is greater than (1/2) AVREF, the MSB bit of the SAR register remains set to 1. If the analog input is smaller than (1/2) AVREF, the MSB bit is reset to 0.

- <12> Next, bit 8 of the SAR register is automatically set to 1, and the operation proceeds to the next comparison. The series resistor string voltage tap is selected according to the preset value of bit 9, as described below.

- Bit 9 = 1: (3/4) AVREF

- Bit 9 = 0: (1/4) AVREF

The voltage tap and sampled voltage are compared and bit 8 of the SAR register is manipulated as follows.

- Sampled voltage  $\geq$  Voltage tap: Bit 8 = 1

- Sampled voltage < Voltage tap: Bit 8 = 0

- <13> Comparison is continued in this way up to bit 0 of the SAR register.

- <14> Upon completion of the comparison of 10 bits, an effective digital result value remains in the SAR register, and the result value is transferred to the A/D conversion result register (ADCR, ADCRH) and then latched.

At the same time, the A/D conversion end interrupt request (INTAD) can also be generated.

<15> Repeat steps <8> to <14>, until the ADCS bit is cleared to 0.

To stop the A/D converter, clear the ADCS bit to 0.

To restart A/D conversion from the status of ADCE = 1, start from <7>. To start A/D conversion again when ADCE = 0, set the ADCE bit to 1, wait for 1  $\mu$ s or longer, and start <7>. To change a channel of A/D conversion, start from <6>.

# Caution Make sure the period of <3> to <7> is 1 $\mu$ s or more.

**Remark** Two types of the A/D conversion result registers are available.

- ADCR register (16 bits): Store 10-bit A/D conversion value

- ADCRH register (8 bits): Store 8-bit A/D conversion value

<R>

Figure 14-28. Example of Contents of Registers for Master Transmission of 3-Wire Serial I/O (CSI00, CSI01, CSI10, CSI20, CSI40, CSI41) (2/2)

|        | 15                     | 14           | 13                   | 12           | 11            | 10                  | 9           | 8                     | 7          | 6           | 5            | 4          | 3          | 2                        | 1                      | 0           |

|--------|------------------------|--------------|----------------------|--------------|---------------|---------------------|-------------|-----------------------|------------|-------------|--------------|------------|------------|--------------------------|------------------------|-------------|

| OEm    | 0                      | 0            | 0                    | 0            | 0             | 0                   | 0           | 0                     | 0          | 0           | 0            | 0          | 0          | SOEm2<br>0/1<br>Note 2   | SOEm1<br>0/1<br>Note 1 | SOEm<br>0/1 |

|        |                        |              |                      |              |               |                     |             |                       |            |             |              |            |            |                          |                        |             |

| (f) Se | e <b>rial ch</b><br>15 | nannel<br>14 | l <b>start</b><br>13 | regist<br>12 | ter m (<br>11 | ( <b>SSm)</b><br>10 | 9 <b>Se</b> | e <b>ts on</b> l<br>8 | y the<br>7 | bits o<br>6 | f the t<br>5 | arget<br>4 | chanr<br>3 | nel to <sup>·</sup><br>2 | <b>1.</b><br>1         | 0           |

(e) Serial output enable register m (SOEm) ... Sets only the bits of the target channel to 1.

- Notes 1. Those bits are invalid while operating serial allay unit 1.2. Those bits are invalid while operating serial allay unit 2.

- Remarks 1.m: Unit number (m = 0 to 2), n: Channel number (n = 0 to 2), p: CSI number (p = 00, 01, 10, 20, 40, 41)<br/>78K0R/KC3-L, 78K0R/KD3-L, 78K0R/KE3-L:mn = 00 to 2), p: CSI number (p = 00, 01, 10, 20, 40, 41)<br/>mn = 00 to 02, p = 00, 01, 1078K0R/KF3-L ( $\mu$  PD78F1010, 78F1011, 78F1012):mn = 00 to 02, 10, p = 00, 01, 10, 20<br/>mn = 00 to 02, 10, 20, 21, p = 00,<br/>01, 10, 20, 40, 4178K0R/KG3-L ( $\mu$  PD78F1013, 78F1014):mn = 00 to 02, 10, p = 00, 01, 10, 20<br/>mn = 00 to 02, 10, 20, 21, p = 00,<br/>01, 10, 20, 40, 4178K0R/KG3-L ( $\mu$  PD78F1029, 78F1030):mn = 00 to 02, 10, 20, 21, p = 00,<br/>01, 10, 20, 40, 412.Im: Setting is fixed in the CSI master transmission mode,Setting disabled (set to the initial value)

- 2. []: Setting is fixed in the CSI master transmission mode, []: Setting disabled (set to the initial value)

×: Bit that cannot be used in this mode (set to the initial value when not used in any mode)

0/1: Set to 0 or 1 depending on the usage of the user

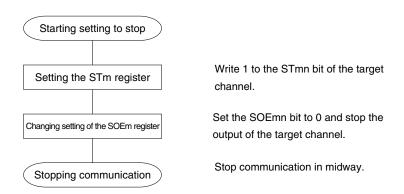

#### Figure 14-54. Procedure for Stopping Slave Transmission

**Remark** Even after communication is stopped, the pin level is retained. To resume the operation, re-set the SOm register (see Figure 14-55 Procedure for Resuming Slave Transmission).

| bl | <7>                                                                          | <6>                                                                                                                                                                                     | <5>                                                                                                                                  | <4>                                                                                                            | <3>                                                                                                           | <2>                                                                       | <1>                                                                            | <0>               |                |  |  |

|----|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------|-------------------|----------------|--|--|

| .0 | IICE                                                                         | LREL                                                                                                                                                                                    | WREL                                                                                                                                 | SPIE                                                                                                           | WTIM                                                                                                          | ACKE                                                                      | STT                                                                            | SPT               |                |  |  |

| ſ  | IICE                                                                         |                                                                                                                                                                                         |                                                                                                                                      |                                                                                                                | I <sup>2</sup> C op                                                                                           | peration enable                                                           | e                                                                              |                   |                |  |  |

| ŀ  | 0                                                                            | Stop operat                                                                                                                                                                             | tion. Reset th                                                                                                                       | e IICA statu                                                                                                   | us register (                                                                                                 | ICS) <sup>Note 1</sup> . Stop                                             | o internal op                                                                  | eration.          |                |  |  |

| Ī  | 1                                                                            | Enable ope                                                                                                                                                                              | ration.                                                                                                                              |                                                                                                                |                                                                                                               |                                                                           |                                                                                |                   |                |  |  |

|    | Be sure to s                                                                 | et this bit (1                                                                                                                                                                          | ) while the SC                                                                                                                       | CL0 and SD                                                                                                     | A0 lines are                                                                                                  | at high level.                                                            |                                                                                |                   |                |  |  |

|    | Condition fo                                                                 | or clearing (II                                                                                                                                                                         | CE = 0)                                                                                                                              |                                                                                                                | c                                                                                                             | Condition for s                                                           | etting (IICE                                                                   | = 1)              |                |  |  |

|    | Cleared by instruction     Set by instruction                                |                                                                                                                                                                                         |                                                                                                                                      |                                                                                                                |                                                                                                               |                                                                           |                                                                                |                   |                |  |  |

| ſ  | LREL <sup>Notes 2, 3</sup>                                                   |                                                                                                                                                                                         |                                                                                                                                      |                                                                                                                | Exit fron                                                                                                     | n communicati                                                             | ons                                                                            |                   |                |  |  |

| Ī  | 0                                                                            | Normal ope                                                                                                                                                                              | eration                                                                                                                              |                                                                                                                |                                                                                                               |                                                                           |                                                                                |                   |                |  |  |

|    | conditions a<br>• After a sto<br>• An addres<br>Condition for<br>• Automatic | to 0 after be<br>Its uses inc<br>The SCL0 a<br>The followin<br>0.<br>• STT • SF<br>y mode following<br>y mode following<br>tre met.<br>p condition is<br>s match or e<br>or clearing (L | eing executed<br>lude cases in<br>and SDA0 line<br>ng flags of IIC<br>PT • MSTS<br>pwing exit fro<br>s detected, re<br>extension cod | I.<br>which a loc<br>es are set to<br>A control re<br>• EXC • Co<br>om commun<br>estart is in m<br>e reception | ally irreleva<br>high imped<br>gister 0 (IIC<br>OI • TRC<br>nications rer<br>naster mode<br>occurs after<br>( | nt extension c<br>ance.<br>CTL0) and the<br>• ACKD • ST<br>nains in effec | ode has bee<br>e IICA status<br>D<br>et until the f<br>dition.<br>etting (LREL | e register (IICS) | are cleared to |  |  |

| L  | <ul> <li>Reset</li> </ul>                                                    |                                                                                                                                                                                         |                                                                                                                                      |                                                                                                                |                                                                                                               |                                                                           |                                                                                |                   |                |  |  |

|    | WREL <sup>Notes 2, 3</sup>                                                   |                                                                                                                                                                                         |                                                                                                                                      |                                                                                                                | Wai                                                                                                           | t cancellation                                                            |                                                                                |                   |                |  |  |

|    | 0                                                                            | Do not can                                                                                                                                                                              | cel wait                                                                                                                             |                                                                                                                |                                                                                                               |                                                                           |                                                                                |                   |                |  |  |

|    | 1                                                                            | Cancel wai                                                                                                                                                                              | t. This setting                                                                                                                      | g is automat                                                                                                   | ically cleare                                                                                                 | d after wait is                                                           | canceled.                                                                      |                   |                |  |  |

|    |                                                                              |                                                                                                                                                                                         | et (wait cance<br>e goes into th                                                                                                     |                                                                                                                |                                                                                                               |                                                                           | h clock puls                                                                   | e in the transmi  | ssion status   |  |  |

|    | Condition fo                                                                 | or clearing (V                                                                                                                                                                          | VREL = 0)                                                                                                                            |                                                                                                                | C                                                                                                             | Condition for s                                                           | etting (WRE                                                                    | L = 1)            |                |  |  |

|    | <ul><li>Automatic</li><li>Reset</li></ul>                                    | ally cleared                                                                                                                                                                            | after executio                                                                                                                       | n                                                                                                              |                                                                                                               | Set by instrue                                                            | ction                                                                          |                   |                |  |  |

| ſ  | (<br>2. T                                                                    | CLD and D<br>The signal (                                                                                                                                                               | AD bits of II                                                                                                                        | CA control<br>invalid whi                                                                                      | register 1<br>le IICE0 is                                                                                     | (IICCTL1) ai                                                              | re reset.                                                                      | IICA flag regi    | ster (IICF), a |  |  |

# Figure 15-6. Format of IICA Control Register 0 (IICCTL0) (1/4)

Caution If the operation of  $I^2C$  is enabled (IICE = 1) when the SCL0 line is high level, the SDA0 line is low level, and the digital filter is turned on (DFC bit of IICCTL1 register = 1), a start condition will be inadvertently detected immediately. In this case, set (1) the LREL bit by using a 1-bit memory manipulation instruction immediately after enabling operation of  $I^2C$  (IICE = 1).

# **CHAPTER 18 INTERRUPT FUNCTIONS**

The number of interrupt sources differs, depending on the product.

| <in 78k0r="" case="" kc3-l,<="" of="" th="" the=""><th>KD3-L, KE3-L&gt;</th></in> | KD3-L, KE3-L> |

|-----------------------------------------------------------------------------------|---------------|

|                                                                                   |               |

|            |          | 78K0R/KC3-L<br>(40-pin) | 78K0R/KC3-L<br>(44-pin) | 78K0R/KC3-L<br>(48-pin) | 78K0R/KD3-L | 78K0R/KE3-L |

|------------|----------|-------------------------|-------------------------|-------------------------|-------------|-------------|

| Maskable   | External | 8                       | 9                       | 9                       | 9           | 9           |

| interrupts | Internal | 22                      | 24                      | 25                      | 25          | 25          |

#### <In case of the 78K0R/KF3-L, KG3-L>

|            |          | 78K0R                              | /KF3-L                         | 78K0R/KG3-L                    |                                |  |  |

|------------|----------|------------------------------------|--------------------------------|--------------------------------|--------------------------------|--|--|

|            |          | (μ PD78F10xx : xx =<br>10, 11, 12) | (μ PD78F10xx : xx =<br>27, 28) | (μ PD78F10xx : xx =<br>13, 14) | (μ PD78F10xx : xx =<br>29, 30) |  |  |

| Maskable   | External |                                    | 1                              | 3                              |                                |  |  |

| interrupts | Internal | 33                                 | 35                             | 33                             | 35                             |  |  |

# **18.1 Interrupt Function Types**

The following two types of interrupt functions are used.

#### (1) Maskable interrupts

These interrupts undergo mask control. Maskable interrupts can be divided into four priority groups by setting the priority specification flag registers (PR00L, PR00H, PR01L, PR01H, PR02L, PR02H, PR10L, PR10H, PR11L, PR11H, PR12L, PR12H).

Multiple interrupt servicing can be applied to low-priority interrupts when high-priority interrupts are generated. If two or more interrupt requests, each having the same priority, are simultaneously generated, then they are processed according to the priority of vectored interrupt servicing. For the priority order, see **Table 18-1**.

A standby release signal is generated and STOP and HALT modes are released.

External interrupt requests and internal interrupt requests are provided as maskable interrupts.

#### (2) Software interrupt

This is a vectored interrupt generated by executing the BRK instruction. It is acknowledged even when interrupts are disabled. The software interrupt does not undergo interrupt priority control.

# 18.2 Interrupt Sources and Configuration

Interrupt sources include maskable interrupts and software interrupts. In addition, they also have up to five reset sources (see **Table 18-1**). The vector codes that store the program start address when branching due to the generation of a reset or various interrupt requests are two bytes each, so interrupts jump to a 64 K address of 00000H to 0FFFFH.

#### Figure 18-2. Format of Interrupt Request Flag Registers (IF0L, IF0H, IF1L, IF1H, IF2L) (2/2)

| XXIFX | Interrupt request flag                                   |  |  |

|-------|----------------------------------------------------------|--|--|

| 0     | No interrupt request signal is generated                 |  |  |

| 1     | Interrupt request is generated, interrupt request status |  |  |

- Cautions 1. Be sure to clear bit 0 of the IF0H register, bits 4 and 5 of the IF1H register (in case of 78K0R/KC3-L (40-pin), bits 1, 2, 4, and 5), and bits 5 to 7 of the IF2L register (in case of 78K0R/KC3-L (40-pin), bits 4 to 7) to 0.

- 2. When operating a timer, serial interface, or A/D converter after standby release, operate it once after clearing the interrupt request flag. An interrupt request flag may be set by noise.

- 3. When manipulating a flag of the interrupt request flag register, use a 1-bit memory manipulation instruction (CLR1). When describing in C language, use a bit manipulation instruction such as "IF0L.0 = 0;" or "\_asm("clr1 IF0L, 0");" because the compiled assembler must be a 1-bit memory manipulation instruction (CLR1).

If a program is described in C language using an 8-bit memory manipulation instruction such as "IF0L &= 0xfe;" and compiled, it becomes the assembler of three instructions.

mov a, IF0L and a, #0FEH mov IF0L, a

In this case, even if the request flag of another bit of the same interrupt request flag register (IF0L) is set to 1 at the timing between "mov a, IF0L" and "mov IF0L, a", the flag is cleared to 0 at "mov IF0L, a". Therefore, care must be exercised when using an 8-bit memory manipulation instruction in C language.

#### Caution The pins mounted depend on the product. Refer to Caution 2 at the beginning of this chapter.

# 30.2 Absolute Maximum Ratings

| Parameter              | Symbols         | Conditions                                                                                                    | Ratings                                                                                                             | Unit |

|------------------------|-----------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------|

| Supply voltage         | VDD             |                                                                                                               | –0.5 to +6.5                                                                                                        | V    |

|                        | EVDD            |                                                                                                               | –0.5 to +6.5                                                                                                        | V    |

|                        | Vss             |                                                                                                               | -0.5 to +0.3                                                                                                        | ٧    |

|                        | EVss            |                                                                                                               | -0.5 to +0.3                                                                                                        | ٧    |

|                        | AVREF           |                                                                                                               | -0.5 to V <sub>DD</sub> + 0.3 <sup>Note 1</sup>                                                                     | V    |

|                        | AVss            |                                                                                                               | -0.5 to + 0.3                                                                                                       | V    |

| REGC pin input voltage | VIREGC          | REGC                                                                                                          | $-0.3$ to + 3.6 and $-0.3$ to V_DD + $0.3^{\text{Note 2}}$                                                          | V    |

| Input voltage          | VI1             | P00, P01, P10 to P17, P30 to P33, P40 to P43, P50 to P53, P70 to P77, P120 to P124, P141, EXCLK, RESET, FLMD0 | -0.3 to EV_DD + 0.3 and -0.3 to V_DD + 0.3 $^{\text{Note 1}}$                                                       | V    |

|                        | VI2             | P60, P61 (N-ch open-drain)                                                                                    | -0.3 to +6.5                                                                                                        | V    |

|                        | Vı3             | P20 to P27, P80 to P83, P150 to P153                                                                          | -0.3 to AV <sub>REF</sub> + 0.3<br>and $-0.3$ to V <sub>DD</sub> + 0.3 <sup>Note 1</sup>                            | V    |

| Output voltage         | V <sub>01</sub> | P00, P01, P10 to P17, P30 to P33, P40 to P43, P50 to P53, P60, P61, P70 to P77, P120, P140, P141              | -0.3 to EV <sub>DD</sub> + 0.3 <sup>Note 1</sup>                                                                    | V    |

|                        | V <sub>02</sub> | P20 to P27, P80 to P83, P150 to P153                                                                          | -0.3 to AV <sub>REF</sub> + 0.3                                                                                     | V    |

| Analog input voltage   | Van             | ANI0 to ANI11, PGAI, CMP0M, CMP0P, CMP1M, CMP1P                                                               | $-0.3 \text{ to } AV_{\text{REF}} + 0.3^{\text{Note 1}}$ and $-0.3 \text{ to } V_{\text{DD}} + 0.3^{\text{Note 1}}$ | V    |

Notes 1. Must be 6.5 V or lower.

- **2.** Connect the REGC pin to Vss via a capacitor (0.47 to 1  $\mu$ F). This value regulates the absolute maximum rating of the REGC pin. Do not use this pin with voltage applied to it.

- Caution Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameter. That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions that ensure that the absolute maximum ratings are not exceeded.

- **Remark** Unless specified otherwise, the characteristics of alternate-function pins are the same as those of the port pins.

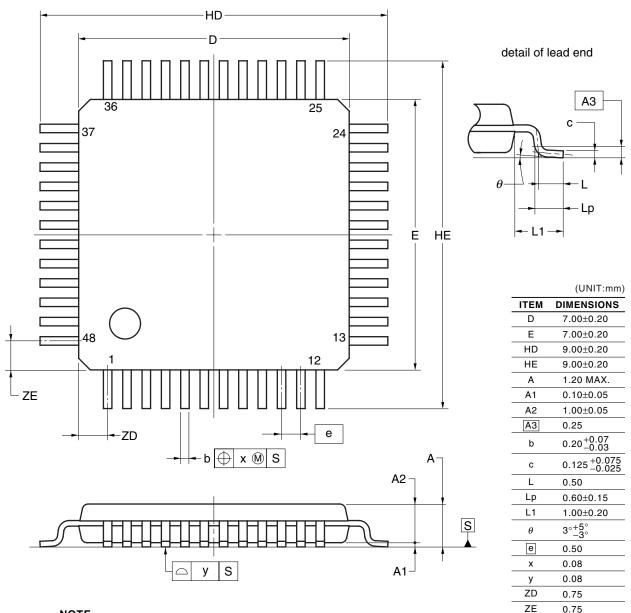

# 32.3 78K0R/KC3-L (48-pin products)

$\mu$  PD78F1001GA-HAA-AX, 78F1002GA-HAA-AX, 78F1003GA-HAA-AX

# 48-PIN PLASTIC TQFP (FINE PITCH) (7x7)

# NOTE

Each lead centerline is located within 0.08 mm of its true position at maximum material condition.

P48GA-50-HAA