# E. Renesas Electronics America Inc - UPD78F1002GA-HAA-AX Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detalls                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | 78K/0R                                                                               |

| Core Size                  | 16-Bit                                                                               |

| Speed                      | 20MHz                                                                                |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                     |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                              |

| Number of I/O              | 36                                                                                   |

| Program Memory Size        | 48KB (48K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 2K x 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                          |

| Data Converters            | A/D 10x10b                                                                           |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 48-TQFP                                                                              |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f1002ga-haa-ax |

|                            |                                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 5.2.2 Port 1

|                                |                                       | /KC3-L<br>)y: y = 0 to 3) | 78K0R/KC3-L (48-pin)<br>(μPD78F100y: y = 1 to 3) | 78K0R/KD3-L<br>(μPD78F100y: y = 4 to 6) | 78K0R/KE3-L<br>(μPD78F100y: y = 7 to 9) |  |  |

|--------------------------------|---------------------------------------|---------------------------|--------------------------------------------------|-----------------------------------------|-----------------------------------------|--|--|

|                                | 40-pin                                | 44-pin                    |                                                  |                                         |                                         |  |  |

| P10/TI02/TO02                  |                                       | V                         | $\checkmark$                                     | $\checkmark$                            | $\checkmark$                            |  |  |

| P11/TO00/TI03/<br>TO03         |                                       | N                         | $\checkmark$                                     | $\checkmark$                            | $\checkmark$                            |  |  |

| P12/TI04/TO04/<br>RTCDIV/RTCCL | P12/TI04/ √<br>TO04 <sup>Note 1</sup> |                           | $\checkmark$                                     | $\checkmark$                            | 1                                       |  |  |

| P13/TI05/TO05                  |                                       | V                         | $\checkmark$                                     | $\checkmark$                            | $\checkmark$                            |  |  |

| P14/TI06/TO06                  | _ <sup>N</sup>                        | ote 2                     | Note 2                                           | Note 2                                  | $\checkmark$                            |  |  |

| P15/TI07/TO07                  | _ <sup>N</sup>                        | lote 2                    | Note 2                                           | Note 2                                  | $\checkmark$                            |  |  |

| P16                            | -                                     | _                         | -                                                | -                                       | ν                                       |  |  |

| P17                            | -                                     | _                         | _                                                | _                                       | $\checkmark$                            |  |  |

Notes 1. 40-pin product of the 78K0R/KC3-L does not have a RTCDIV/RTCCL pin.

2. TI06/TO06 and TI07/TO07 are shared with P50 and P51, respectively, in products other than the 78K0R/KE3-L.

## **Remark** $\sqrt{}$ : Mounted

Port 1 is an I/O port with an output latch. Port 1 can be set to the input mode or output mode in 1-bit units using port mode register 1 (PM1). When the P10 to P17 pins are used as an input port, use of an on-chip pull-up resistor can be specified in 1-bit units by pull-up resistor option register 1 (PU1).

This port can also be used for timer I/O and real-time counter clock output.

Reset signal generation sets port 1 to input mode.

Figures 5-3 and 5-4 show block diagrams of port 1.

Caution To use P10/TI02/TO02, P11/TI03/TO03, P12/TI04/TO04/RTCDIV/RTCCL, P13/TI05/TO05, P14/TI06/TO06, or P15/TI07/TO07 as a general-purpose port, set bits 2 to 7 (TO02 to TO07) of timer output register 0 (TO0) and bits 2 to 7 (TOE02 to TOE07) of timer output enable register 0 (TOE0) to "0", which is the same as their default status setting.

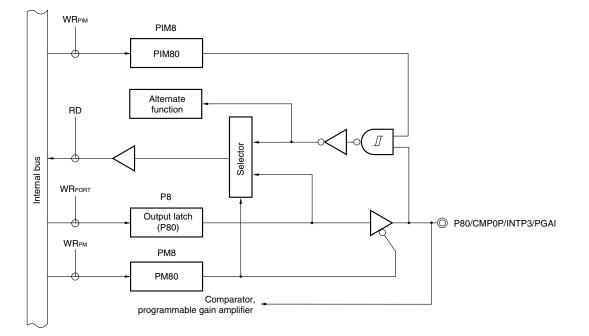

Figure 5-19. Block Diagram of P80

- P8: Port register 8

- PM8: Port mode register 8

- PIM8: Port input mode register 8

- RD: Read signal

- WR××: Write signal

## (6) A/D port configuration register (ADPC)

This register switches the ANI0/P20 to ANI7/P27 and ANI8/P150 to ANI11/P153 pins to digital I/O of port or analog input of A/D converter.

The ADPC register can be set by an 8-bit memory manipulation instruction.

Reset signal generation sets this register to 10H.

## Figure 5-41. Format of A/D Port Configuration Register (ADPC)

| Address | : F0017H | After reset: 10H | R/W |       |       |       |       |       |

|---------|----------|------------------|-----|-------|-------|-------|-------|-------|

| Symbol  | 7        | 6                | 5   | 4     | 3     | 2     | 1     | 0     |

| ADPC    | 0        | 0                | 0   | ADPC4 | ADPC3 | ADPC2 | ADPC1 | ADPC0 |

| ADPC4 | ADPC3 | ADPC2    | ADPC1 | ADPC0 | Analog input (A)/digital I/O (D) switching |         |        |       |        |      |      |      |      | I    |      |      |

|-------|-------|----------|-------|-------|--------------------------------------------|---------|--------|-------|--------|------|------|------|------|------|------|------|

|       |       |          |       |       |                                            | Por     | t 15   |       | Port 2 |      |      |      |      |      |      |      |

|       |       |          |       |       | ANI11                                      | ANI10   | ANI9   | ANI8  | ANI7   | ANI6 | ANI5 | ANI4 | ANI3 | ANI2 | ANI1 | ANI0 |

|       |       |          |       |       | /P153                                      | /P152   | /P151  | /P150 | /P27   | /P26 | /P25 | /P24 | /P23 | /P22 | /P21 | /P20 |

| 0     | 0     | 0        | 0     | 0     | А                                          | А       | А      | А     | А      | А    | А    | А    | А    | А    | А    | А    |

| 0     | 0     | 0        | 0     | 1     | А                                          | А       | А      | А     | А      | А    | А    | А    | А    | А    | А    | D    |

| 0     | 0     | 0        | 1     | 0     | А                                          | А       | А      | А     | А      | А    | А    | А    | А    | А    | D    | D    |

| 0     | 0     | 0        | 1     | 1     | А                                          | А       | А      | А     | А      | А    | А    | А    | А    | D    | D    | D    |

| 0     | 0     | 1        | 0     | 0     | А                                          | А       | А      | А     | А      | А    | А    | А    | D    | D    | D    | D    |

| 0     | 0     | 1        | 0     | 1     | А                                          | А       | А      | А     | А      | А    | А    | D    | D    | D    | D    | D    |

| 0     | 0     | 1        | 1     | 0     | А                                          | А       | А      | А     | А      | А    | D    | D    | D    | D    | D    | D    |

| 0     | 0     | 1        | 1     | 1     | А                                          | А       | А      | А     | А      | D    | D    | D    | D    | D    | D    | D    |

| 0     | 1     | 0        | 0     | 0     | А                                          | А       | А      | А     | D      | D    | D    | D    | D    | D    | D    | D    |

| 0     | 1     | 0        | 0     | 1     | А                                          | А       | А      | D     | D      | D    | D    | D    | D    | D    | D    | D    |

| 0     | 1     | 0        | 1     | 0     | А                                          | А       | D      | D     | D      | D    | D    | D    | D    | D    | D    | D    |

| 0     | 1     | 0        | 1     | 1     | А                                          | D       | D      | D     | D      | D    | D    | D    | D    | D    | D    | D    |

| 1     | 0     | 0        | 0     | 0     | D                                          | D       | D      | D     | D      | D    | D    | D    | D    | D    | D    | D    |

|       | Other | than the | above |       | Settir                                     | ng proh | ibited |       |        |      |      |      |      |      |      |      |

Cautions 1. Set a channel to be used for A/D conversion in the input mode by using port mode register 2 and 15 (PM2, PM15).

- 2. Do not set the pin that is set by the ADPC register as digital I/O by the analog input channel specification register (ADS).

- 3. Be sure to first set the ADCEN bit of peripheral enable register 0 (PER0) to 1 when setting up the ADPC register. If ADCEN = 0, writing to the ADPC register is ignored and specified values are returned to the initial values.

Remark

P20/ANI0 to P27/ANI7, P150/ANI8, and P151/ANI9: 78K0R/KC3-L (40-pin, 44-pin)

P20/ANI0 to P27/ANI7, P150/ANI8 to P152/ANI10: 78K0R/KC3-L (48-pin), 78K0R/KD3-L

P20/ANI0 to P27/ANI7, P150/ANI8 to P153/ANI11: 78K0R/KE3-L

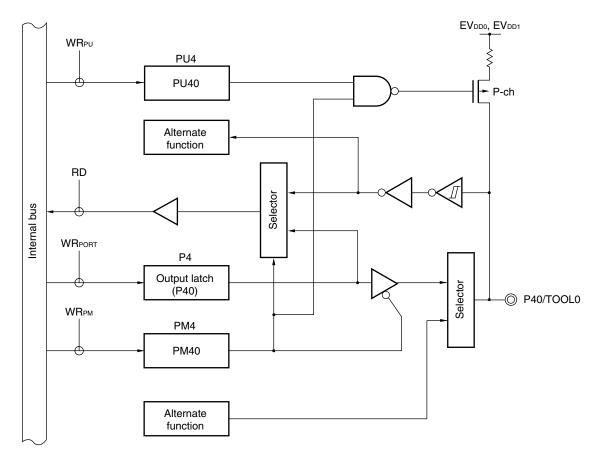

Figure 6-15. Block Diagram of P40

- P4: Port register 4

- PU4: Pull-up resistor option register 4

- PM4: Port mode register 4

- RD: Read signal

- WR××: Write signal

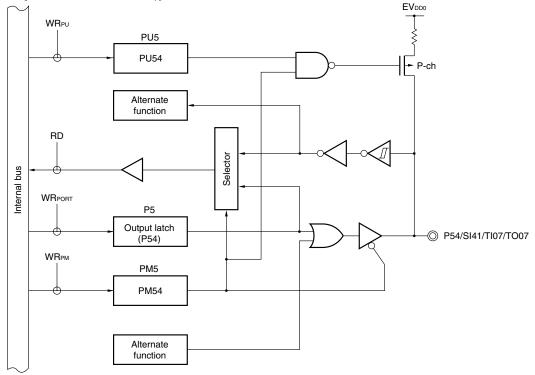

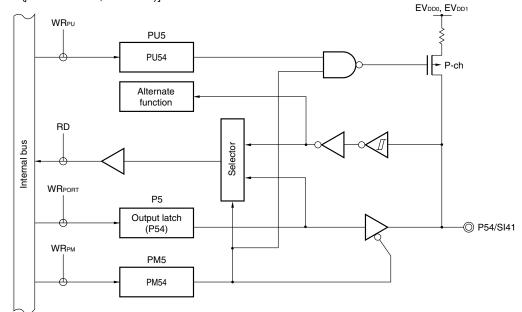

## Figure 6-30. Block Diagram of P54

## [78K0R/KG3-L (µ PD78F1029, 78F1030)]

- P5: Port register 5

- PU5: Pull-up resistor option register 5

- PM5: Port mode register 5

- RD: Read signal

- WR××: Write signal

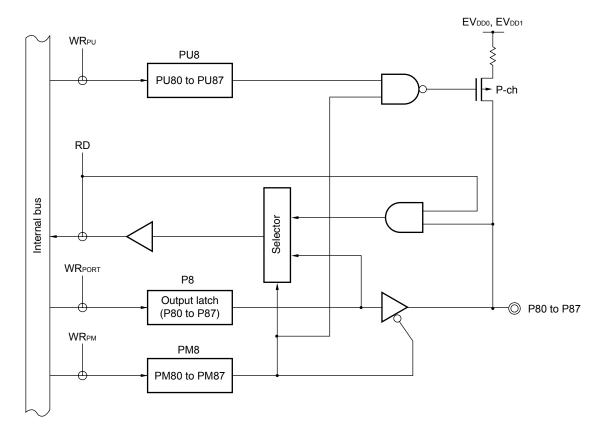

Figure 6-38. Block Diagram of P80 to P87

- P8: Port register 8

- PU8: Pull-up resistor option register 8

- PM8: Port mode register 8

- RD: Read signal

- WR××: Write signal

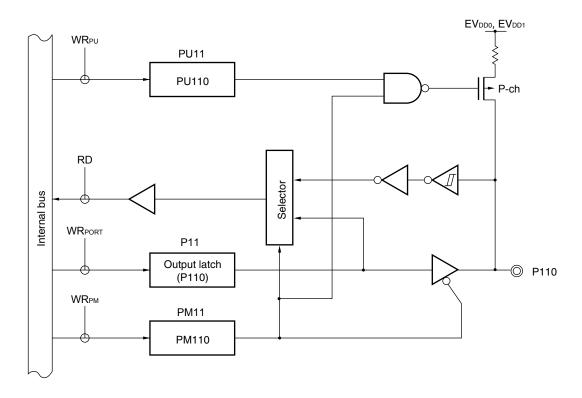

## 6.2.12 Port 11

|      | 78K0R/KF3-L<br>(μPD78F10xx: xx = 10 to 12, 27,28) | 78K0R/KG3-L<br>(μPD78F10xx: xx = 13, 14, 29, 30) |

|------|---------------------------------------------------|--------------------------------------------------|

| P110 | $\checkmark$                                      | $\checkmark$                                     |

| P111 | $\checkmark$                                      | $\checkmark$                                     |

Port 11 is an I/O port with an output latch. Port 11 can be set to the input mode or output mode in 1-bit units using port mode register 11 (PM11). When the P110 and P111 pins are used as an input port, use of an on-chip pull-up resistor can be specified in 1-bit units by pull-up resistor option register 11 (PU11).

Reset signal generation sets port 11 to input mode.

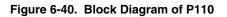

Figures 6-40 and 6-41 show a block diagram of port 11.

- P11: Port register 11

- PU11: Pull-up resistor option register 11

- PM11: Port mode register 11

- RD: Read signal

- WR××: Write signal

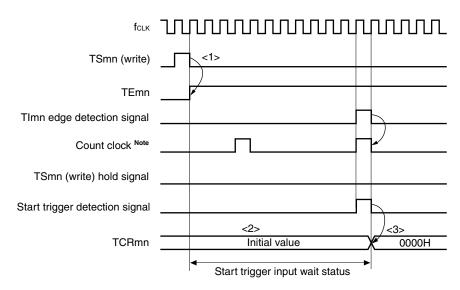

## (e) Start timing in capture & one-count mode

<1> Operation is enabled (TEmn = 1) by writing 1 to the TSmn bit.

<2> Enters the start trigger input wait status, and timer/counter register mn (TCRmn) holds the initial value.</3> On start trigger detection, 0000H is loaded to the TCRmn register and count starts.

Figure 8-19. Start Timing (In Capture & One-count Mode)

- **Note** When the capture & one-count mode is set, the operation clock (f<sub>MCK</sub>) is selected as count clock (CCSmn = 0).

- Caution An input signal sampling error is generated since operation starts upon start trigger detection (If the TImn pin input signal is used as a start trigger, an error of one count clock occurs.)

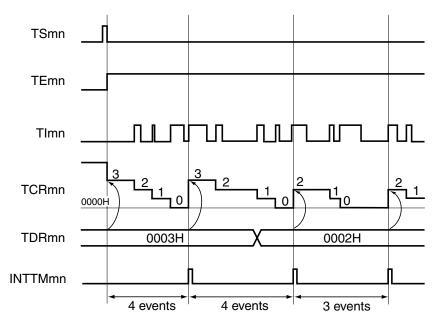

Figure 8-46. Example of Basic Timing of Operation as External Event Counter

- Remarks 1. m: Unit number (m = 0, 1), n: Channel number (n = 0 to 7)

78K0R/KC3-L (40-pin):

mn = 02 to 07

78K0R/KC3-L (44-pin, 48-pin):

mn = 00 to 07

78K0R/KD3-L, 78K0R/KE3-L:

mn = 00 to 07

78K0R/KF3-L, 78K0R/KG3-L:

mn = 00 to 07

78K0R/KF3-L, 78K0R/KG3-L:

mn = 00 to 07, 10 to 13

2.

TSmn:

Bit n of timer channel start register m (TSm)

TEmn:

Bit n of timer channel enable status register m (TEm)

TImn:

TImn pin input signal

- TCRmn: Timer/counter register mn (TCRmn)

- TDRmn: Timer data register mn (TDRmn)

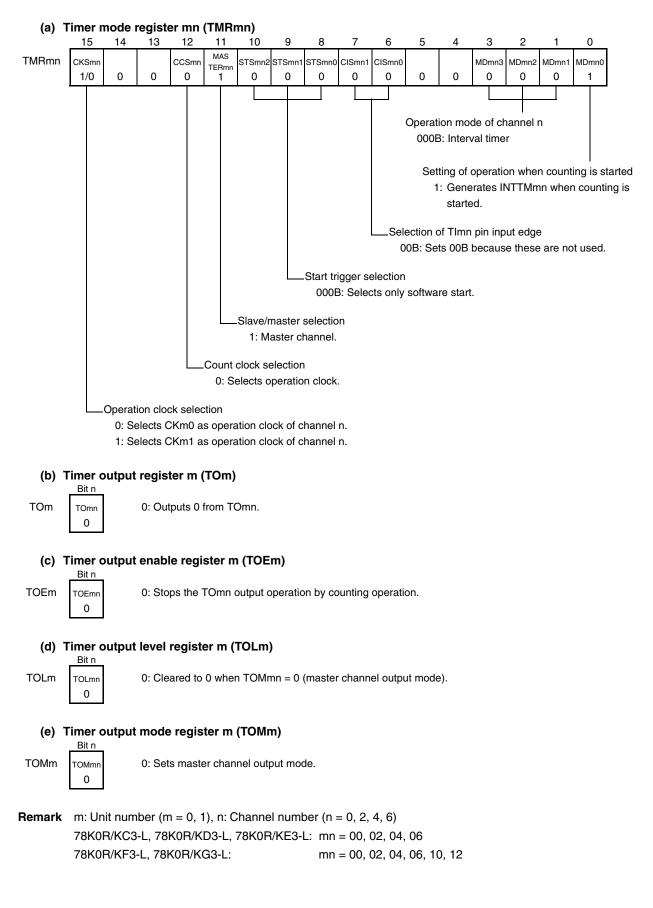

#### Figure 8-68. Example of Set Contents of Registers When PWM Function (Master Channel) Is Used

## (2) Scan mode

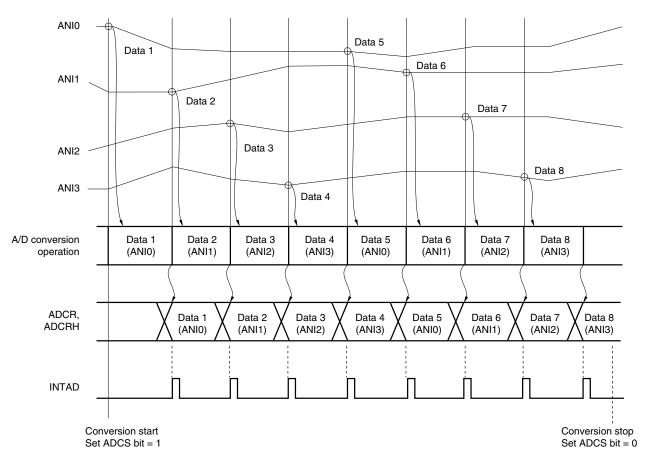

The four analog input channels of scans 0 to 3, which are specified by the analog input channel specification register (ADS), while the ADMD bit of the A/D converter mode register (ADM) is 1, are A/D converted successively. A/D conversion is performed in sequence, starting from the analog input channel specified by scan 0.

When A/D conversion of one analog input is complete, the conversion result is stored in the A/D conversion result register (ADCR) and the A/D conversion end interrupt request signal (INTAD) is generated.

The A/D conversion results of all the analog input channels are stored in the ADCR register. It is therefore recommended to save the contents of the ADCR register to RAM, once A/D conversion of one analog input channel has been completed.

After A/D conversion has been completed, A/D conversion is repeated successively, unless the ADCS bit is set to 0. If anything is written to the ADM or ADS register during conversion, A/D conversion is aborted. In this case, A/D conversion is started again from the analog input channel of scan 0.

Figure 13-15. Example of Scan Mode Operation Timing

| Item               | Config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | juration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                    | μ PD78F1010, 78F1011, 78F1012, 78F1013,<br>78F1014                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | μ PD78F1027, 78F1028, 78F1029, 78F1030                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| Shift register     | 8 bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Buffer register    | Lower 8 bits of serial data register mn (SDRmn) <sup>Note</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| Serial clock I/O   | SCK00, SCK01, SCK10, SCK20 pins (for 3-wire serial I/O), SCL10, SCL20 pins (for simplified I <sup>2</sup> C)                                                                                                                                                                                                                                                                                                                                                                                                                       | $\overline{SCK00}$ , $\overline{SCK01}$ , $\overline{SCK10}$ , $\overline{SCK20}$ , $\overline{SCK40}$ , $\overline{SCK41}$<br>pins (for 3-wire serial I/O), SCL10, SCL20 pins<br>(for simplified I <sup>2</sup> C)                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| Serial data input  | SI00, SI01, SI10, SI20 pins (for 3-wire serial I/O),<br>RxD0 to RxD2 pins (for UART), RxD3 pin (for<br>UART supporting LIN-bus)                                                                                                                                                                                                                                                                                                                                                                                                    | SI00, SI01, SI10, SI20, SI40, SI41 pins (for 3-<br>wire serial I/O), RxD0 to RxD2, RxD4 pins (for<br>UART), RxD3 pin (for UART supporting LIN-bus)                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| Serial data output | SO00, SO01, SO10, SO20 pins (for 3-wire serial I/O), TxD0 to TxD2 pins (for UART), TxD3 pin (for UART supporting LIN-bus), output controller                                                                                                                                                                                                                                                                                                                                                                                       | SO00, SO01, SO10, SO20, SO40, SO41 pins<br>(for 3-wire serial I/O), TxD0 to TxD2, TxD4 pins<br>(for UART), TxD3 pin (for UART supporting LIN-<br>bus), output controller                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| Serial data I/O    | SDA10, SDA20 pins (for simplified I <sup>2</sup> C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Control registers  | <registers block="" of="" setting="" unit=""> <ul> <li>Peripheral enable register 0 (PER0)</li> <li>Serial clock select register m (SPSm)</li> <li>Serial channel enable status register m (SEm)</li> <li>Serial channel start register m (SSm)</li> <li>Serial channel stop register m (STm)</li> <li>Serial output enable register m (SOEm)</li> <li>Serial output register m (SOM)</li> <li>Serial output level register m (SOLm)</li> <li>Input switch control register 0 (NFEN0)</li> </ul></registers>                       | <registers block="" of="" setting="" unit=""> <ul> <li>Peripheral enable registers 0, 1 (PER0, PER1)</li> <li>Serial clock select register m (SPSm)</li> <li>Serial channel enable status register m (SEm)</li> <li>Serial channel start register m (SSm)</li> <li>Serial channel stop register m (STm)</li> <li>Serial output enable register m (SOEm)</li> <li>Serial output register m (SOM)</li> <li>Serial output level register m (SOLm)</li> <li>Input switch control register (ISC)</li> <li>Noise filter enable register 0 (NFEN0)</li> </ul></registers> |  |  |  |  |  |  |

|                    | <registers channel="" each="" of=""><br/>• Serial data register mn (SDRmn)<br/>• Serial mode register mn (SMRmn)<br/>• Serial communication operation setting register mn (SCRmn)<br/>• Serial status register mn (SSRmn)<br/>• Serial flag clear trigger register mn (SIRmn)<br/>• Port input mode registers 0, 1, 14 (PIM0, PIM1, PIM14)<br/>• Port output mode registers 0, 1, 14 (POM0, POM1, POM14)<br/>• Port mode registers 0, 1, 4, 14 (PM0, PM1, PM4, PM14)<br/>• Port registers 0, 1, 4, 14 (P0, P1, P4, P14</registers> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

Table 14-1. Configuration of Serial Array Unit (2/2) (78K0R/KF3-L, 78K0R/KG3-L)

**Note** The lower 8 bits of serial data register mn (SDRmn) can be read or written as the following SFR, depending on the communication mode.

- CSIp communication ... SIOp (CSIp data register)

- UARTq reception ... RXDq (UARTq receive data register)

- UARTq transmission ... TXDq (UARTq transmit data register)

- IICr communication ... SIOr (IICr data register)

**Remark** m: Unit number (m = 0 to 2), n: Channel number (n = 0 to 3), p: CSI number (p = 00, 01, 10, 20, 40, 41), q: UART number (q = 0 to 4), r: IIC number (r = 10, 20)

#### Figure 14-8. Format of Serial Communication Operation Setting Register mn (SCRmn) (1/4)

Address: F0118H, F0119H (SCR00) to F011EH, F011FH (SCR03), After reset: 0087H R/W F0158H, F0159H (SCR10) to F015EH, F015FH (SCR13), F020CH F02

F020CH, F020DH (SCR20), F020EH, F020FH (SCR21)

| Symbol | 15  | 14  | 13  | 12  | 11 | 10  | 9   | 8   | 7   | 6 | 5   | 4   | 3 | 2   | 1   | 0   |

|--------|-----|-----|-----|-----|----|-----|-----|-----|-----|---|-----|-----|---|-----|-----|-----|

| SCRmn  | TXE | RXE | DAP | CKP | 0  | EOC | PTC | PTC | DIR | 0 | SLC | SLC | 0 | DLS | DLS | DLS |

|        | mn  | mn  | mn  | mn  |    | mn  | mn1 | mn0 | mn  |   | mn1 | mn0 |   | mn2 | mn1 | mn0 |

| TXE | RXE | Setting of operation mode of channel n |

|-----|-----|----------------------------------------|

| mn  | mn  |                                        |

| 0   | 0   | Disable communication.                 |

| 0   | 1   | Reception only                         |

| 1   | 0   | Transmission only                      |

| 1   | 1   | Transmission/reception                 |

| DAP    | CKP       | Selection of data and clock phase in CSI mode                       | Туре |

|--------|-----------|---------------------------------------------------------------------|------|

| mn     | mn        |                                                                     |      |

| 0      | 0         |                                                                     | 1    |

|        |           | SOp XD7XD6XD5XD4XD3XD2XD1XD0                                        |      |

|        |           | SIp input timing                                                    |      |

| 0      | 1         |                                                                     | 2    |

|        |           | SOp <u>XD7 XD6 XD5 XD4 XD3 XD2 XD1 XD0</u>                          |      |

|        |           | SIp input timing                                                    |      |

| 1      | 0         |                                                                     | 3    |

|        |           | SOp XD7 XD6 XD5 XD4 XD3 XD2 XD1 XD0                                 |      |

|        |           | SIp input timing                                                    |      |

| 1      | 1         |                                                                     | 4    |

|        |           | SOp XD7 XD6 XD5 XD4 XD3 XD2 XD1 XD0                                 |      |

|        |           | SIp input timing                                                    |      |

| Be sur | re to set | t DAPmn, CKPmn = 0, 0 in the UART mode and simplified $I^2$ C mode. |      |

| EOC    | Selection of masking of error interrupt signal (INTSREx (x = 0 to 3))                                           |  |  |  |  |  |  |  |

|--------|-----------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| mn     |                                                                                                                 |  |  |  |  |  |  |  |

| 0      | Masks error interrupt INTSREx (INTSRx is not masked).                                                           |  |  |  |  |  |  |  |

| 1      | Enables generation of error interrupt INTSREx (INTSRx is masked if an error occurs).                            |  |  |  |  |  |  |  |

| Set E0 | Set EOCmn = 0 in the CSI mode, simplified I <sup>2</sup> C mode, and during UART transmission <sup>Note</sup> . |  |  |  |  |  |  |  |

| Set E0 | Set EOCmn = 1 during UART reception.                                                                            |  |  |  |  |  |  |  |

**Note** When using CSI01 not with EOC01 = 0, error interrupt INTSRE0 may be generated.

#### Caution Be sure to clear bits 3, 6, and 11 to "0". Be sure to set bit 2 to "1".

(Remark is listed on the next page.)

#### (10) Serial channel enable status register m (SEm)

The SEm register indicates whether data transmission/reception operation of each channel is enabled or stopped. When 1 is written a bit of serial channel start register m (SSm), the corresponding bit of this register is set to 1.

When 1 is written a bit of serial channel stop register m (STm), the corresponding bit is cleared to 0.

Channel n that is enabled to operate cannot rewrite by software the value of the CKOmn bit (serial clock output of channel n) of serial output register m (SOm) to be described below, and a value reflected by a communication operation is output from the serial clock pin.

Channel n that stops operation can set the value of the CKOmn bit of the SOm register by software and output its value from the serial clock pin. In this way, any waveform, such as that of a start condition/stop condition, can be created by software.

The SEm register can be read by a 16-bit memory manipulation instruction.

The lower 8 bits of the SEm register can be set with an 1-bit or 8-bit memory manipulation instruction with SEmL. Reset signal generation clears the SEm register to 0000H.

## Figure 14-14. Format of Serial Channel Enable Status Register m (SEm)

Address: F0120H, F0121H (SE0), F0160H, F0161H (SE1), After reset: 0000H R

F0210H, F0211H (SE2)

| Symbol | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3                        | 2                        | 1        | 0        |

|--------|----|----|----|----|----|----|---|---|---|---|---|---|--------------------------|--------------------------|----------|----------|

| SEm    | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | SEm<br>3 <sup>Note</sup> | SEm<br>2 <sup>Note</sup> | SEm<br>1 | SEm<br>0 |

| SEm<br>n | Indication of operation enable/stop status of channel n |

|----------|---------------------------------------------------------|

| 0        | Operation stops                                         |

| 1        | Operation is enabled.                                   |

**Note** Those bits are invalid while operating serial allay unit 2.

```

Remark m: Unit number (m = 0 to 2), n: Channel number (n = 0 to 3)

78K0P/KC3 = 78K0P/KD3 = 78K0P/KE3 = mn = 00 to 03

```

| 78K0R/KC3-L, $78K0R/KD3-L$ , $78K0R/KE3-L$ :    | mn = 00 10 03                   |

|-------------------------------------------------|---------------------------------|

| 78K0R/KF3-L $\mu$ PD78F1010, 78F1011, 78F1012 : | mn = 00 to 03, 10 to 13         |

| 78K0R/KF3-L μPD78F1027, 78F1028 :               | mn = 00 to 03, 10 to 13, 20, 21 |

| 78K0R/KG3-L μPD78F1013, 78F1014 :               | mn = 00 to 03, 10 to 13         |

| 78K0R/KG3-L $\mu$ PD78F1029, 78F1030 :          | mn = 00 to 03, 10 to 13, 20, 21 |

|                                                 |                                 |

| SMRmn<br>Register | ů,         |            |            |            |            |            |                    |            | Operation Clock (fMCK) Note 1                               |                             |  |

|-------------------|------------|------------|------------|------------|------------|------------|--------------------|------------|-------------------------------------------------------------|-----------------------------|--|

| CKSmn             | PRS<br>m13 | PRS<br>m12 | PRS<br>m11 | PRS<br>m10 | PRS<br>m03 | PRS<br>m02 | PRS<br>m01         | PRS<br>m00 |                                                             | fclk = 20 MHz               |  |

| 0                 | Х          | Х          | Х          | Х          | 0          | 0          | 0                  | 0          | fclk                                                        | 20 MHz                      |  |

|                   | Х          | Х          | Х          | Х          | 0          | 0          | 0                  | 1          | fclk/2                                                      | 10 MHz                      |  |

|                   | Х          | Х          | Х          | Х          | 0          | 0          | 1                  | 0          | fclk/2 <sup>2</sup>                                         | 5 MHz                       |  |

|                   | Х          | Х          | Х          | Х          | 0          | 0          | 1                  | 1          | fclk/2 <sup>3</sup>                                         | 2.5 MHz                     |  |

|                   | Х          | Х          | Х          | Х          | 0          | 1          | 0                  | 0          | fclĸ/2⁴                                                     | 1.25 MHz                    |  |

|                   | Х          | Х          | Х          | Х          | 0          | 1          | 0                  | 1          | fclĸ/2⁵                                                     | 625 kHz                     |  |

|                   | Х          | Х          | Х          | Х          | 0          | 1          | 1                  | 0          | fclk/2 <sup>6</sup>                                         | 313 kHz                     |  |

|                   | Х          | Х          | Х          | Х          | 0          | 1          | 1                  | 1          | fclk/2 <sup>7</sup>                                         | 156 kHz                     |  |

|                   | Х          | Х          | Х          | Х          | 1          | 0          | 0                  | 0          | fclk/2 <sup>8</sup>                                         | 78.1 kHz                    |  |

|                   | Х          | Х          | Х          | Х          | 1          | 0          | 0                  | 1          | fclk/2 <sup>9</sup>                                         | 39.1 kHz                    |  |

|                   | Х          | Х          | Х          | Х          | 1          | 0          | 1                  | 0          | fclk/2 <sup>10</sup>                                        | 19.5 kHz                    |  |

|                   | Х          | Х          | Х          | Х          | 1          | 0          | 1                  | 1          | fclk/2 <sup>11</sup>                                        | 9.77 kHz                    |  |

|                   | Х          | Х          | Х          | Х          | 1          | 1          | 1                  | 1          | INTTM02 if $m = 0^{Note 2}$ , setting prohibited if $m = 1$ |                             |  |

| 1                 | 0          | 0          | 0          | 0          | Х          | Х          | Х                  | Х          | fclk                                                        | 20 MHz                      |  |

|                   | 0          | 0          | 0          | 1          | Х          | Х          | Х                  | Х          | fclк/2                                                      | 10 MHz                      |  |

|                   | 0          | 0          | 1          | 0          | Х          | Х          | Х                  | Х          | fclk/2 <sup>2</sup>                                         | 5 MHz                       |  |

|                   | 0          | 0          | 1          | 1          | Х          | Х          | Х                  | Х          | fclk/2 <sup>3</sup>                                         | 2.5 MHz                     |  |

|                   | 0          | 1          | 0          | 0          | Х          | Х          | Х                  | Х          | fc⊥ĸ/2⁴                                                     | 1.25 MHz                    |  |

|                   | 0          | 1          | 0          | 1          | Х          | Х          | Х                  | Х          | fc∟ĸ/2⁵                                                     | 625 kHz                     |  |

|                   | 0          | 1          | 1          | 0          | Х          | Х          | Х                  | Х          | fськ/2 <sup>6</sup>                                         | 313 kHz                     |  |

|                   | 0          | 1          | 1          | 1          | Х          | Х          | Х                  | Х          | fclk/2 <sup>7</sup>                                         | 156 kHz                     |  |

|                   | 1          | 0          | 0          | 0          | Х          | Х          | Х                  | Х          | fclk/2 <sup>8</sup>                                         | 78.1 kHz                    |  |

|                   | 1          | 0          | 0          | 1          | Х          | Х          | Х                  | Х          | fclk/2 <sup>9</sup>                                         | 39.1 kHz                    |  |

|                   | 1          | 0          | 1          | 0          | Х          | Х          | Х                  | Х          | fclk/2 <sup>10</sup>                                        | 19.5 kHz                    |  |

|                   | 1          | 0          | 1          | 1          | Х          | Х          | Х                  | Х          | fськ/2 <sup>11</sup>                                        | 9.77 kHz                    |  |

|                   | 1          | 1          | 1          | 1          | Х          | Х          | Х                  | Х          | INTTM02 if $m = 0^{Note 2}$ , se                            | tting prohibited if $m = 1$ |  |

| Other than above  |            |            |            |            |            |            | Setting prohibited |            |                                                             |                             |  |

Table 14-2. Selection of Operation Clock For 3-Wire Serial I/O

Notes 1. When changing the clock selected for fcLk (by changing the system clock control register (CKC) value), do so after having stopped (serial channel stop register m (STm) = 000FH) the operation of the serial array unit (SAU). When selecting INTTM02 for the operation clock, also stop the timer array unit 0 (timer channel stop register 0 (TT0) = 00FFH).

- 2. SAU0 can be operated at a fixed division ratio of the subsystem clock, regardless of the f<sub>CLK</sub> frequency (main system clock, sub system clock), by operating the interval timer for which f<sub>SUB</sub>/4<sup>Note 3</sup> has been selected as the count clock (setting the TIS02 bit of timer input select register 0 (TIS0) to 1) and selecting INTTM02 by using the SPS0 register in channel 2 of TAU0. When changing f<sub>CLK</sub>, however, SAU0 and TAU0 must be stopped as described in Note 1 above.

- 3. The 78K0R/KC3-L (40-pin) doesn't have the subsystem clock.

## Remarks 1. X: Don't care

| <b>2.</b> m: Unit number (m = 0 to 2), n: Channel number (n = 0 to 2) |                                             |                           |  |  |  |  |  |  |

|-----------------------------------------------------------------------|---------------------------------------------|---------------------------|--|--|--|--|--|--|

| 78                                                                    | 8K0R/KC3-L, 78K0R/KD3-L, 78K0R/KE3-L:       | mn = 00 to 02             |  |  |  |  |  |  |

| 78                                                                    | 8K0R/KF3-L (μ PD78F1010, 78F1011, 78F1012): | mn = 00 to 02, 10         |  |  |  |  |  |  |

| 78                                                                    | 8K0R/KF3-L (μ PD78F1027, 78F1028):          | mn = 00 to 02, 10, 20, 21 |  |  |  |  |  |  |

| 78                                                                    | 8K0R/KG3-L ( <i>µ</i> PD78F1013, 78F1014):  | mn = 00 to 02, 10         |  |  |  |  |  |  |

| 78                                                                    | 8K0R/KG3-L ( <i>µ</i> PD78F1029, 78F1030):  | mn = 00 to 02, 10, 20, 21 |  |  |  |  |  |  |

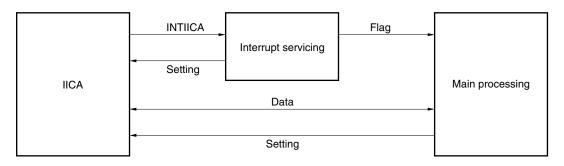

## (3) Slave operation

The processing procedure of the slave operation is as follows.

Basically, the slave operation is event-driven. Therefore, processing by the INTIICA interrupt (processing that must substantially change the operation status such as detection of a stop condition during communication) is necessary.

In the following explanation, it is assumed that the extension code is not supported for data communication. It is also assumed that the INTIICA interrupt servicing only performs status transition processing, and that actual data communication is performed by the main processing.

Therefore, data communication processing is performed by preparing the following three flags and passing them to the main processing instead of INTIICA.

## <1> Communication mode flag

This flag indicates the following two communication statuses.

- Clear mode: Status in which data communication is not performed

- Communication mode: Status in which data communication is performed (from valid address detection to stop condition detection, no detection of ACK from master, address mismatch)

## <2> Ready flag

This flag indicates that data communication is enabled. Its function is the same as the INTIICA interrupt for ordinary data communication. This flag is set by interrupt servicing and cleared by the main processing. Clear this flag by interrupt servicing when communication is started. However, the ready flag is not set by interrupt servicing when the first data is transmitted. Therefore, the first data is transmitted without the flag being cleared (an address match is interpreted as a request for the next data).

## <3> Communication direction flag

This flag indicates the direction of communication. Its value is the same as the TRC bit.

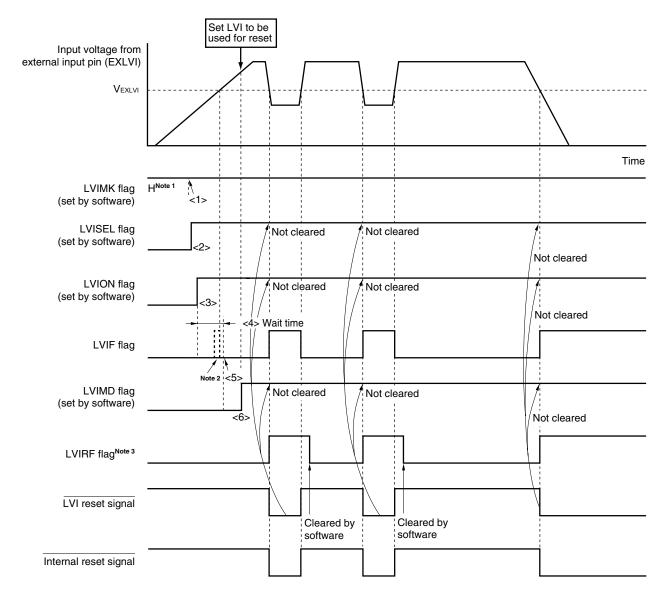

Figure 23-7. Timing of Low-Voltage Detector Internal Reset Signal Generation (Bit: LVISEL = 1)

- Notes 1. The LVIMK flag is set to "1" by reset signal generation.

- 2. The LVIIF flag of the interrupt request flag registers and the LVIF flag may be set (1).

- 3. LVIRF flag is bit 0 of the reset control flag register (RESF). For details of the RESF register, see CHAPTER 21 RESET FUNCTION.

- Remark <1> to <6> in Figure 23-7 above correspond to <1> to <6> in the description of "When starting operation" in 23.4.1 (2) When detecting level of input voltage from external input pin (EXLVI).

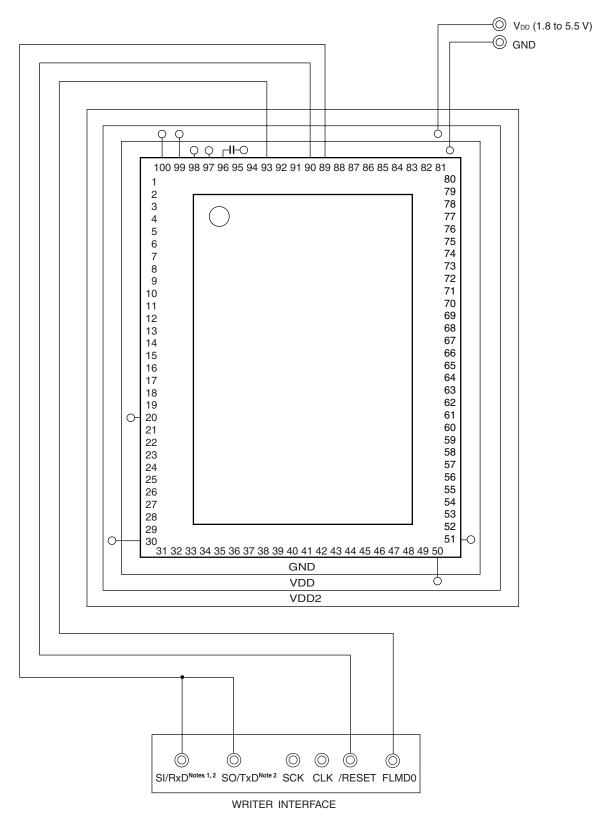

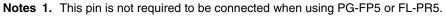

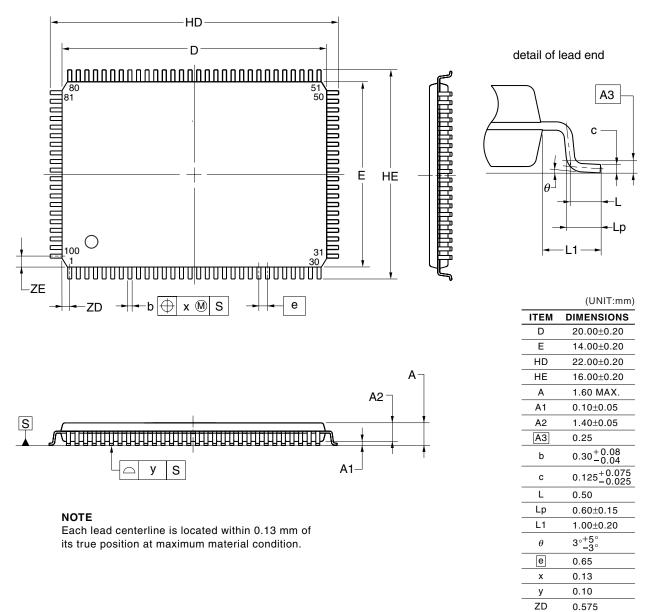

Figure 26-7. Example of Wiring Adapter for Flash Memory Writing (78K0R/KG3-L, LQFP (14x20))

2. Connect SI/RxD or SO/TxD when using QB-MINI2.

## 32.7 78K0R/KG3-L

$\mu$  PD78F1013GF-GAS-AX, 78F1014GF-GAS-AX, 78F1029GF-GAS-AX, 78F1030GF-GAS-AX

## 100-PIN PLASTIC LQFP (14x20)

ΖE

0.825 P100GF-65-GAS

<R>

<R>

## A.5 Debugging Tools (Hardware)

## A.5.1 When using in-circuit emulator

#### (1) QB-78K0RIX3 (compatible with 78K0R/KC3-L, 78K0R/KD3-L, 78K0R/KE3-L)

| QB-78K0RIX3<br>In-circuit emulator                   | This in-circuit emulator serves to debug hardware and software when developing application systems using the 78K0R/KC3-L, 78K0R/KD3-L, 78K0R/KE3-L microcontrollers. It supports to the integrated debugger (ID78K0R-QB). This emulator should be used in combination with a power supply unit and emulation probe, and the USB is used to connect this emulator to the host machine. |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QB-COMMON-PW->>> <sup>Note 1</sup>                   | This power supply unit can be used in common with the all products of in-circuit emulator IECUBE and the flash memory programmer PG-FP5.                                                                                                                                                                                                                                              |

| QB-144-CA-01<br>Check pin adapter                    | This check pin adapter is used in waveform monitoring using the oscilloscope, etc.                                                                                                                                                                                                                                                                                                    |

| QB-80-EP-01T<br>Emulation probe                      | This emulation probe is flexible type and used to connect the in-circuit emulator and target system.                                                                                                                                                                                                                                                                                  |

| QB-xxxx-EA-xxx Note 2<br>Exchange adapter            | This exchange adapter is used to perform pin conversion from the in-circuit emulator to target connector.                                                                                                                                                                                                                                                                             |

| QB-xxxx-YS-xxxx <sup>Note 2</sup><br>Space adapter   | This space adapter is used to adjust the height between the target system and in-circuit emulator.                                                                                                                                                                                                                                                                                    |

| QB-xxxx-YQ-xxx Note 2<br>YQ connector                | This YQ connector is used to connect the target connector and exchange adapter.                                                                                                                                                                                                                                                                                                       |

| QB-xxxx-HQ-Xxx <sup>Note 2</sup><br>Mount adapter    | This mount adapter is used to mount the target device with socket.                                                                                                                                                                                                                                                                                                                    |

| QB-xxxx-NQ-xxx <sup>Note 2</sup><br>Target connector | This target connector is used to mount on the target system.                                                                                                                                                                                                                                                                                                                          |

**Notes 1.** ×× differs depending on the target area of each product.

2. The part numbers of the exchange adapter, space adapter, YQ connector, mount adapter, and target connector and the packages of the target device are described below.

|                 | Package                                 | Exchange<br>Adapter | Space Adapter | YQ Connector | Mount Adapter | Target<br>Connector |

|-----------------|-----------------------------------------|---------------------|---------------|--------------|---------------|---------------------|

| 78K0R/<br>KC3-L | 40-pin plastic<br>WQFN<br>(K8-4B4 type) | QB-40K8-<br>EA-02T  | None          | None         | None          | QB-40K8-<br>NQ-01T  |

|                 | 44-pin plastic LQFP                     | QB-44GB-            | QB-44GB-      | QB-44GB-     | QB-44GB-      | QB-44GB-            |

|                 | (GB-GAF type)                           | EA-04T              | YS-01T        | YQ-01T       | HQ-01T        | NQ-01T              |

|                 | 48-pin plastic LQFP                     | QB-48GA-            | QB-48GA-      | QB-48GA-     | QB-48GA-      | QB-48GA-            |

|                 | (GA-HAA type)                           | EA-04T              | YS-01T        | YQ-01T       | HQ-01T        | NQ-01T              |

|                 | 48-pin plastic<br>WQFN<br>(K8-5B4 type) | QB-48K8-<br>EA-02T  | None          | None         | None          | QB-48K8-<br>NQ-01T  |

| 78K0R/          | 52-pin plastic LQFP                     | QB-52GB-            | QB-52GB-      | QB-52GB-     | QB-52GB-      | QB-52GB-            |

| KD3-L           | (GB-GAG type)                           | EA-04T              | YS-01T        | YQ-01T       | HQ-01T        | NQ-01T              |

| 78K0R/          | 64-pin plastic LQFP                     | QB-64GB-            | QB-64GB-      | QB-64GB-     | QB-64GB-      | QB-64GB-            |

| KE3-L           | (GB-GAH type)                           | EA-04T              | YS-01T        | YQ-01T       | HQ-01T        | NQ-01T              |

|                 | 64-pin plastic LQFP                     | QB-64GK-            | QB-64GK-      | QB-64GK-     | QB-64GK-      | QB-64GK-            |

|                 | (GK-GAJ type)                           | EA-04T              | YS-01T        | YQ-01T       | HQ-01T        | NQ-01T              |

|                 | 64-pin plastic TQFP                     | QB-64GA-            | QB-64GA-      | QB-64GA-     | QB-64GA-      | QB-64GA-            |

|                 | (GA-HAB type)                           | EA-01T              | YS-01T        | YQ-01T       | HQ-01T        | NQ-01T              |

|                 | 64-pin plastic FBGA<br>(F1-AN1 type)    | QB-64FC-<br>EA-01T  | None          | None         | None          | QB-64FC-<br>NQ-01T  |

|                 | 64-pin plastic FBGA<br>(F1-AA2 type)    | QB-64F1-<br>EA-03T  | None          | None         | None          | QB-64F1-<br>NQ-01T  |

(Remarks are listed on the next page or later.)