# E. Renesas Electronics America Inc - UPD78F1003GA-HAA-AX Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detalls                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | 78K/0R                                                                               |

| Core Size                  | 16-Bit                                                                               |

| Speed                      | 20MHz                                                                                |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                     |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                              |

| Number of I/O              | 36                                                                                   |

| Program Memory Size        | 64KB (64K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 3K x 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                          |

| Data Converters            | A/D 10x10b                                                                           |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 48-TQFP                                                                              |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f1003ga-haa-ax |

|                            |                                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### (2) AVss

This is the ground potential pin of A/D converter, programmable gain amplifier, comparator, P20 to P27, P150 to P153, and P80 to P83. Even when the A/D converter, programmable gain amplifier, and comparator are not used, always use this pin with the same potential as EVss or Vss.

## (3) VDD, EVDD

V<sub>DD</sub> is the positive power supply pin for P121 to P124 and other than ports (other than the RESET pin and FLMD0 pin) <sup>№te</sup>.

EV<sub>DD</sub> is the positive power supply pin for ports other than those of P20 to P27, P150 to P153, P80 to P83, and P121 to P124, as well as for the RESET pin and FLMD0 pin.

#### (4) Vss, EVss

Vss is the ground potential pin for P121 to P124 and other than ports (other than the RESET pin and FLMD0 pin) <sup>№te</sup>. EVss is the ground potential pin for ports other than those of P20 to P27, P150 to P153, P80 to P83, and P121 to P124, as well as for the RESET pin and FLMD0 pin.

**Note** With products not provided with an EVss pin, use Vss as the ground potential pin for port pins other than P20 to P27, P150 to P153, P80 to P83, as well as for pins other than those of ports.

## 2.2.14 RESET

This is the active-low system reset input pin.

When the external reset pin is not used, connect this pin directly to EVDD or via a resistor.

When the external reset pin is used, design the circuit based on  $V_{\mbox{\scriptsize DD}}.$

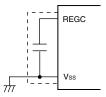

#### 2.2.15 REGC

This is the pin for connecting regulator output (2.4 V) stabilization capacitance for internal operation. Connect this pin to Vss via a capacitor (0.47 to 1  $\mu$ F).

Also, use a capacitor with good characteristics, since it is used to stabilize internal voltage.

Caution Keep the wiring length as short as possible for the broken-line part in the above figure.

**Note** With products not provided with an EV<sub>DD</sub> pin, use V<sub>DD</sub> as the positive power supply pin for port pins other than P20 to P27, P150 to P153, and P80 to P83, as well as for pins other than those of ports.

## 3.3 Pin I/O Circuits and Recommended Connection of Unused Pins

## 3.3.1 78K0R/KF3-L

Table 3-3 shows the types of pin I/O circuits and the recommended connections of unused pins. For I/O Circuit Type, see Figure 3-1. Pin I/O Circuit List.

| Pin Name                             | I/O Circuit Type | I/O | Recommended Connection of Unused Pins                                                                                                                                                                                                                                                     |

|--------------------------------------|------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P02/SO10/TxD1                        | 5-AG             | I/O | Input: Independently connect to EV_DD0 or EV_SS0 via a resistor.                                                                                                                                                                                                                          |

| P03/SI10/RxD1/SDA10                  | 5-AN             |     | Output: Leave open.                                                                                                                                                                                                                                                                       |

| P04/SCK10/SCL10                      |                  |     | <when n-ch="" open-drain=""><br/>Set the port output latch to 0 and leave open with low level out put.</when>                                                                                                                                                                             |

| P05/TI05/TO05                        | 8-R              | -   | Input: Independently connect to EV <sub>DD0</sub> or EV <sub>SS0</sub> via a resistor.                                                                                                                                                                                                    |

| P06/TI06/TO06                        |                  |     | Output: Leave open.                                                                                                                                                                                                                                                                       |

| P10/SCK00                            | 5-AN             |     | Input: Independently connect to EV <sub>DD0</sub> or EV <sub>SS0</sub> via a resistor.<br>Output: Leave open.                                                                                                                                                                             |

|                                      |                  |     | <when n-ch="" open-drain=""><br/>Set the port output latch to 0 and leave open with low level out put.</when>                                                                                                                                                                             |

| P11/SI00/RxD0                        |                  |     | Input: Independently connect to EV <sub>DD0</sub> or EV <sub>SS0</sub> via a resistor.<br>Output: Leave open.                                                                                                                                                                             |

| P12/SO00/TxD0                        | 5-AG             |     | Input: Independently connect to EV <sub>DD0</sub> or EV <sub>SS0</sub> via a resistor.<br>Output: Leave open.                                                                                                                                                                             |

|                                      |                  |     | <when n-ch="" open-drain=""><br/>Set the port output latch to 0 and leave open with low level out put.</when>                                                                                                                                                                             |

| P13/TxD3                             |                  |     | Input: Independently connect to EV <sub>DD0</sub> or EV <sub>SS0</sub> via a resistor.<br>Output: Leave open.                                                                                                                                                                             |

| P14/RxD3                             | 8-R              |     | Input: Independently connect to EV <sub>DD0</sub> or EV <sub>SS0</sub> via a resistor.                                                                                                                                                                                                    |

| P15/RTCDIV/RTCCL                     | 5-AG             |     | Output: Leave open.                                                                                                                                                                                                                                                                       |

| P16/TI01/TO01/INTP5                  | 8-R              |     |                                                                                                                                                                                                                                                                                           |

| P17/TI02/TO02                        |                  |     |                                                                                                                                                                                                                                                                                           |

| P20/ANI0 to P27/ANI7 <sup>Note</sup> | 11-G             |     | Input: Independently connect to AVREF or AVss via a resistor.<br>Output: Leave open.                                                                                                                                                                                                      |

| P30/RTC1HZ/INTP3                     | 8-R              |     | Input: Independently connect to EV <sub>DD0</sub> or EV <sub>SS0</sub> via a resistor.<br>Output: Leave open.                                                                                                                                                                             |

| P31/TI03/TO03/INTP4                  |                  |     | · · ·                                                                                                                                                                                                                                                                                     |

| P40/TOOL0                            |                  |     | <when debugging="" enabled="" is="" on-chip=""><br/>Pull this pin up (pulling it down is prohibited).<br/><when debugging="" disabled="" is="" on-chip=""><br/>Input: Independently connect to EV<sub>DD0</sub> or EV<sub>SS0</sub> via a resistor.<br/>Output: Leave open.</when></when> |

#### Table 3-3. Connection of Unused Pins (1/3)

Note P20/ANI0 to P27/ANI7 are set in the digital input port mode after release of reset.

#### 4.2.5 Extended special function registers (2nd SFRs: 2nd Special Function Registers)

Unlike a general-purpose register, each extended SFR (2nd SFR) has a special function.

Extended SFRs are allocated to the F0000H to F07FFH area. SFRs other than those in the SFR area (FFF00H to FFFFFH) are allocated to this area. An instruction that accesses the extended SFR area, however, is 1 byte longer than an instruction that accesses the SFR area.

Extended SFRs can be manipulated like general-purpose registers, using operation, transfer, and bit manipulation instructions. The manipulable bit units, 1, 8, and 16, depend on the SFR type.

Each manipulation bit unit can be specified as follows.

• 1-bit manipulation

Describe the symbol reserved by the assembler for the 1-bit manipulation instruction operand (laddr16.bit). This manipulation can also be specified with an address.

• 8-bit manipulation

Describe the symbol reserved by the assembler for the 8-bit manipulation instruction operand (!addr16). This manipulation can also be specified with an address.

• 16-bit manipulation

Describe the symbol reserved by the assembler for the 16-bit manipulation instruction operand (!addr16). When specifying an address, describe an even address.

Table 4-6 gives a list of the extended SFRs. The meanings of items in the table are as follows.

Symbol

Symbol indicating the address of an extended SFR. It is a reserved word in the RA78K0R, and is defined as an sfr variable using the #pragma sfr directive in the CC78K0R. When using the RA78K0R, ID78K0R-QB, and SM+ for 78K0R, symbols can be written as an instruction operand.

• R/W

Indicates whether the corresponding extended SFR can be read or written.

R/W: Read/write enable

- R: Read only

- W: Write only

- Manipulable bit units

"√" indicates the manipulable bit unit (1, 8, or 16). "−" indicates a bit unit for which manipulation is not possible.

After reset

Indicates each register status upon reset signal generation.

#### Caution Do not access addresses to which extended SFRs are not assigned.

Remark For SFRs in the SFR area, see 4.2.4 Special function registers (SFRs).

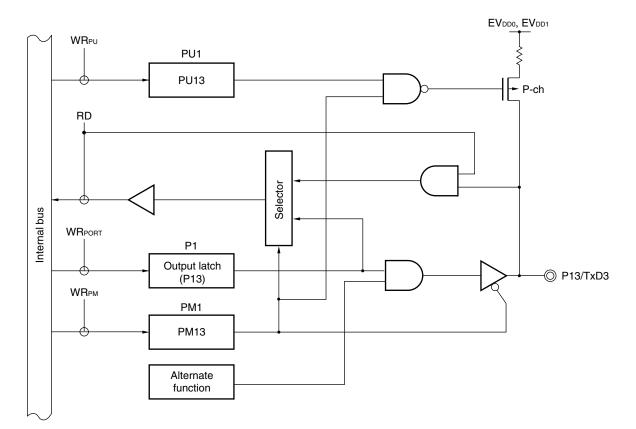

Figure 6-9. Block Diagram of P13

- P1: Port register 1

- PU1: Pull-up resistor option register 1

- PM1: Port mode register 1

- RD: Read signal

- WR××: Write signal

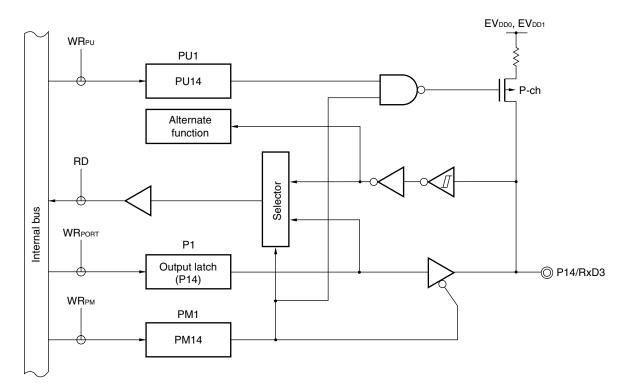

Figure 6-10. Block Diagram of P14

- P1: Port register 1

- PU1: Pull-up resistor option register 1

- PM1: Port mode register 1

- RD: Read signal

- WR×x: Write signal

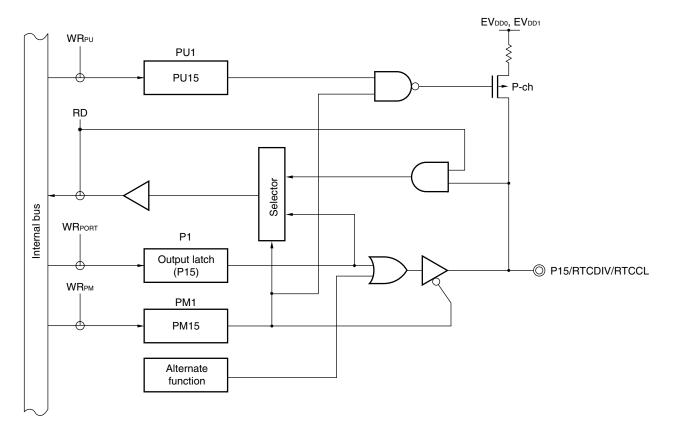

Figure 6-11. Block Diagram of P15

- P1: Port register 1

- PU1: Pull-up resistor option register 1

- PM1: Port mode register 1

- RD: Read signal

- WR××: Write signal

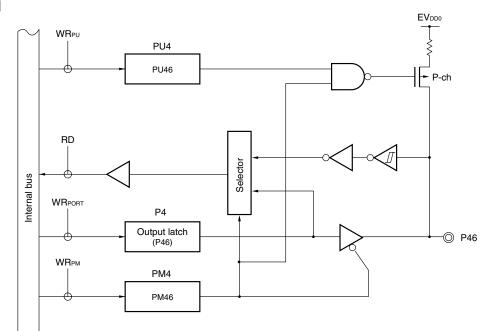

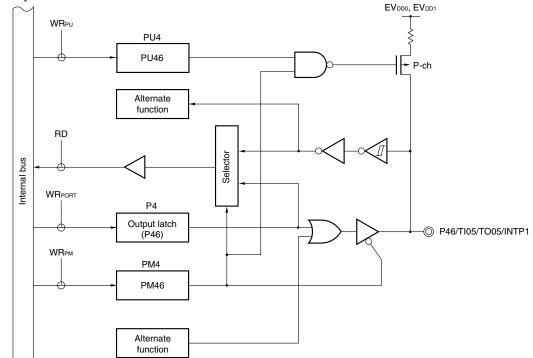

Figure 6-21. Block Diagram of P46

## [78K0R/KF3-L]

- P4: Port register 4

- PU4: Pull-up resistor option register 4

- PM4: Port mode register 4

- RD: Read signal

- WR××: Write signal

- **Notes 1.** The internal reset processing time includes the oscillation accuracy stabilization time of the internal high-speed oscillation clock.

- 2. When releasing a reset, confirm the oscillation stabilization time for the X1 clock using the oscillation stabilization time counter status register (OSTC).

- **3.** The microcontroller operates on the 8 MHz internal high-speed oscillation clock if 8 MHz or 20 MHz is selected for the internal high-speed oscillator by using the option byte or on the 1 MHz internal high-speed oscillation clock if 1 MHz is selected.

- 4. The 78K0R/KC3-L (40-pin) doesn't have the subsystem clock.

- 5. If the internal high-speed oscillator is set to 1 MHz by using the option byte, the 20 MHz internal high-speed oscillation clock cannot be used.

- Cautions 1. A voltage stabilization time (about 2.12 to 5.84 ms) is required after the supply voltage reaches 1.61 V (TYP.). If the time for the supply voltage to rise from 1.61 V (TYP.) to 2.07 V (TYP.) is shorter than the voltage stabilization time, reset processing is entered after the voltage stabilization time elapses.

- 2. It is not necessary to wait for the oscillation stabilization time when an external clock input from the EXCLK pin is used.

Table 7-4 shows transition of the CPU clock and examples of setting the SFR registers.

## Table 7-4. CPU Clock Transition and SFR Register Setting Examples (1/6)

#### (1) CPU operating with internal high-speed oscillation clock (B) after reset release (A)

| Status Transition | SFR Register Setting                                                      |

|-------------------|---------------------------------------------------------------------------|

| $(A) \to (B)$     | SFR registers do not have to be set (default status after reset release). |

## (2) CPU operating with high-speed system clock (C) after reset release (A)

(The CPU operates with the internal high-speed oscillation clock immediately after a reset release (B).)

| (Setting sequence of SFR registers)                                                                                |       |             |        |          |                       |                           |          |

|--------------------------------------------------------------------------------------------------------------------|-------|-------------|--------|----------|-----------------------|---------------------------|----------|

| Setting Flag of SFR Register                                                                                       | CM    | IC Register | Note 1 | CSC      | OSMC                  | OSTC                      | СКС      |

|                                                                                                                    |       |             |        | Register | Register              | Register                  | Register |

| Status Transition                                                                                                  | EXCLK | OSCSEL      | AMPH   | MSTOP    | FSEL                  |                           | MCM0     |

|                                                                                                                    | 0     | 1           | 0      | 0        | 0                     | Must be<br>checked        | 1        |

| $\begin{array}{l} (A) \rightarrow (B) \rightarrow (C) \\ (X1 \ clock: 10 \ MHz < f_{X} \leq 20 \ MHz) \end{array}$ | 0     | 1           | 1      | 0        | 1 <sup>Note 2</sup>   | Must be checked           | 1        |

| $(A) \rightarrow (B) \rightarrow (C)$<br>(external main clock)                                                     | 1     | 1           | ×      | 0        | 0/1 <sup>Note 2</sup> | Must not<br>be<br>checked | 1        |

**Notes 1.** The clock operation mode control register (CMC) can be written only once by an 8-bit memory manipulation instruction after reset release.

- 2. FSEL = 1 when  $f_{CLK} > 10 \text{ MHz}$ If a divided clock is selected and  $f_{CLK} \le 10 \text{ MHz}$ , use with FSEL = 0 is possible even if  $f_X > 10 \text{ MHz}$ .

- Caution Set the clock after the supply voltage has reached the operable voltage of the clock to be set (see CHAPTER 30 ELECTRICAL SPECIFICATIONS (78K0R/KC3-L, 78K0R/KD3-L, 78K0R/KE3-L) or CHAPTER 31 ELECTRICAL SPECIFICATIONS (78K0R/KF3-L, 78K0R/KG3-L)).

#### Remark ×: don't care

(3) CPU operating with subsystem clock (D) after reset release (A) (products other than 78K0R/KC3-L (40-pin)) (The CPU operates with the internal high-speed oscillation clock immediately after a reset release (B).)

| (Setting sequence of SFR registers) |         |                          |        |                 |                            |                 |

|-------------------------------------|---------|--------------------------|--------|-----------------|----------------------------|-----------------|

| Setting Flag of SFR Register        | С       | MC Register <sup>№</sup> | lote   | CSC<br>Register | Waiting for<br>Oscillation | CKC<br>Register |

| Status Transition                   | OSCSELS | AMPHS1                   | AMPHS0 | XTSTOP          | Stabilization              | CSS             |

| $(A) \to (B) \to (D)$               | 1       | 0/1                      | 0/1    | 0               | Necessary                  | 1               |

- **Note** The clock operation mode control register (CMC) can be written only once by an 8-bit memory manipulation instruction after reset release.

- **Remark** (A) to (K) in Table 7-4 correspond to (A) to (K) in Figure 7-19.

## Caution While timer output is enabled (TOEmn = 1), even if the output by timer interrupt of each timer (INTTMmn) contends with writing to the TOmn bit, output is normally done to the TOmn pin.

**Remark** m: Unit number (m = 0, 1), n: Channel number (n = 0 to 7)

However, in case of the timer output pin (TOmn), mn changes as below.

| 78K0R/KC3-L (40-pin):         | mn = 02 to 07           |

|-------------------------------|-------------------------|

| 78K0R/KC3-L (44-pin, 48-pin): | mn = 00 to 07           |

| 78K0R/KD3-L, 78K0R/KE3-L:     | mn = 00 to 07           |

| 78K0R/KF3-L, 78K0R/KG3-L:     | mn = 00 to 07, 10 to 13 |

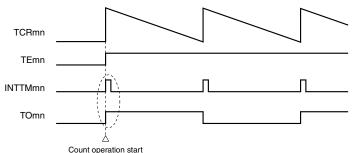

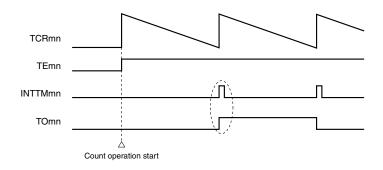

#### 8.5.5 Timer Interrupt and TOmn Pin Output at Operation Start

In the interval timer mode or capture mode, the MDmn0 bit in timer mode register mn (TMRmn) sets whether or not to generate a timer interrupt at count start.

When MDmn0 is set to 1, the count operation start timing can be known by the timer interrupt (INTTMmn) generation. In the other modes, neither timer interrupt at count operation start nor TOmn output is controlled.

Figure 8-38. When MDmn0 is set to 1

Figures 8-37 and 8-38 show operation examples when the interval timer mode (TOEmn = 1, TOMmn = 0) is set.

Count operation start

When MDmn0 is set to 1, a timer interrupt (INTTMmn) is output at count operation start, and TOmn performs a toggle operation.

Figure 8-39. When MDmn0 is set to 0

When MDmn0 is set to 0, a timer interrupt (INTTMmn) is not output at count operation start, and TOmn does not change either. After counting one cycle, INTTMmn is output and TOmn performs a toggle operation.

**Remark** m: Unit number (m = 0, 1), n: Channel number (n = 0 to 7)However, in case of the timer output pin (TOmn), mn changes as below. mn = 02 to 0778K0R/KC3-L (40-pin): mn = 00 to 0778K0R/KC3-L (44-pin, 48-pin): mn = 00 to 07 78K0R/KD3-L, 78K0R/KE3-L: 78K0R/KF3-L, 78K0R/KG3-L: mn = 00 to 07, 10 to 13

|                               | Software Operation                                                                                                                                                                                                         | Hardware Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TAU<br>default<br>setting     |                                                                                                                                                                                                                            | Power-off status<br>(Clock supply is stopped and writing to each register is<br>disabled.)                                                                                                                                                                                                                                                                                                                                                                                                               |

|                               | Sets the TAU0EN and TAU1EN bits of peripheral enable registers 0, 2 (PER0, PER2) to 1. Note                                                                                                                                | Power-on status. Each channel stops operating.<br>(Clock supply is started and writing to each register is<br>enabled.)                                                                                                                                                                                                                                                                                                                                                                                  |

|                               | Sets timer clock select register m (TPSm).<br>Determines clock frequencies of CKm0 and CKm1.                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Channel<br>default<br>setting | Sets timer mode register mn (TMRmn) (determines<br>operation mode of channel).<br>Clears the TOEmn bit to 0 and stops operation of TOmn.                                                                                   | Channel stops operating.<br>(Clock is supplied and some power is consumed.)                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Operation<br>start            | Sets the TSmn bit to 1.<br>The TSmn bit automatically returns to 0 because it is a<br>trigger bit.                                                                                                                         | TEmn = 1, and the TImn pin start edge detection wait status is set.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                               | Detects the TImn pin input count start valid edge.                                                                                                                                                                         | Clears timer/counter register mn (TCRmn) to 0000H and starts counting up.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| During<br>operation           | Set value of the TDRmn register can be changed.<br>The TCRmn register can always be read.<br>The TSRmn register is not used.<br>Set values of the TMRmn register, TOMmn, TOLmn,<br>TOmn, and TOEmn bits cannot be changed. | When the TImn pin start edge is detected, the counter<br>(TCRmn) counts up from 0000H. If a capture edge of the<br>TImn pin is detected, the count value is transferred to<br>timer data register mn (TDRmn) and INTTMmn is<br>generated.<br>If an overflow occurs at this time, the OVF bit of timer<br>status register mn (TSRmn) is set; if an overflow does not<br>occur, the OVF bit is cleared. The TCRmn register stops<br>the count operation until the next TImn pin start edge is<br>detected. |

| Operation<br>stop             | The TTmn bit is set to 1. The TTmn bit automatically returns to 0 because it is a trigger bit.                                                                                                                             | TEmn = 0, and count operation stops.<br>The TCRmn register holds count value and stops.<br>The OVF bit of the TSRmn register is also held.                                                                                                                                                                                                                                                                                                                                                               |

| TAU<br>stop                   | The TAU0EN and TAU1EN bits of the PER0 and PER2                                                                                                                                                                            | Power-off status<br>All circuits are initialized and SFR of each channel is<br>also initialized.                                                                                                                                                                                                                                                                                                                                                                                                         |

# Figure 8-60. Operation Procedure When Input Signal High-/Low-Level Width Measurement Function Is Used

Note 78K0R/KC3-L, 78K0R/KD3-L, 78K0R/KE3-L: TAU0EN bit of the PER2 register 78K0R/KF3-L, 78K0R/KG3-L:

TAU0EN or TAU1EN bit of the PER0 register

Remark m: Unit number (m = 0, 1), n: Channel number (n = 0 to 7) However, in case of the timer input pin (TImn) and the timer output pin (TOmn), mn changes as below. 78K0R/KC3-L (40-pin): mn = 02 to 07 78K0R/KC3-L (44-pin, 48-pin): mn = 00 to 07 78K0R/KD3-L, 78K0R/KE3-L: mn = 00 to 07 78K0R/KF3-L, 78K0R/KG3-L: mn = 00 to 07, 10 to 13

#### 13.4.2 Input voltage and conversion results

The relationship between the analog input voltage input to the analog input pins (ANI0 to ANI15, PGAI) and the theoretical A/D conversion result (stored in the 10-bit A/D conversion result register (ADCR)) is shown by the following expression.

$$SAR = INT \left(\frac{V_{AIN}}{AV_{REF}} \times 1024 + 0.5\right)$$

$$ADCR = SAR \times 64$$

or

(

$$\frac{\text{ADCR}}{64} - 0.5) \times \frac{\text{AV}_{\text{REF}}}{1024} \le \text{V}_{\text{AIN}} < (\frac{\text{ADCR}}{64} + 0.5) \times \frac{\text{AV}_{\text{REF}}}{1024}$$

where, INT(): Function which returns integer part of value in parentheses

VAIN: Analog input voltage

AVREF: AVREF pin voltage

- ADCR: A/D conversion result register (ADCR) value

- SAR: Successive approximation register

Figure 13-13 shows the relationship between the analog input voltage and the A/D conversion result.

SAR ADCR 1023 FFC0H FF80H 1022 1021 FF40H A/D conversion result З 00C0H 0080H 2 0040H 1 0 0000H 2043 1022 2045 1023 2047 1 3 2 1 5 3 2048 1024 2048 1024 2048 1024 2048 1024 2048 1024 2048 Input voltage/AVREF

Remark ANI0 to ANI9: 78K0R/KC3-L (40-pin, 44-pin) ANI0 to ANI10: 78K0R/KC3-L (48-pin) and 78K0R/KD3-L ANI0 to ANI11: 78K0R/KE3-L, 78K0R/KF3-L ANI0 to ANI15: 78K0R/KG3-L

RENESAS

The channels supporting 3-wire serial I/O (CSI00, CSI01, CSI10, CSI20, CSI40, CSI41) are channels 0 to 2 of SAU0, channel 0 of SAU1 (78K0R/KF3-L, 78K0R/KG3-L only), and channel 0 and 1 of SAU2 (78K0R/KF3-L ( $\mu$  PD78F1027, 78F1028), 78K0R/KG3-L ( $\mu$  PD78F1029, 78F1030) only).

• 78K0R/KC3-L, 78K0R/KD3-L, 78K0R/KE3-L

| Unit | Channel | Used as CSI | Used as UART               | Used as Simplified I <sup>2</sup> C |

|------|---------|-------------|----------------------------|-------------------------------------|

| 0    | 0       | CSI00       | UART0 (supporting LIN-bus) | _                                   |

|      | 1       | CSI01       |                            | _                                   |

|      | 2       | CSI10       | UART1                      | IIC10                               |

|      | 3       | _           |                            | _                                   |

• 78K0R/KF3-L, 78K0R/KG3-L

| Unit   | Channel | Used as CSI | Used as UART               | Used as Simplified I <sup>2</sup> C |

|--------|---------|-------------|----------------------------|-------------------------------------|

| 0      | 0       | CSI00       | UART0                      | _                                   |

|        | 1       | CSI01       |                            | _                                   |

|        | 2       | CSI10       | UART1                      | IIC10                               |

|        | 3       | -           |                            | _                                   |

| 1      | 0       | CSI20       | UART2                      | IIC20                               |

|        | 1       | -           |                            | -                                   |

|        | 2       | -           | UART3 (supporting LIN-bus) | _                                   |

|        | 3       | _           |                            | _                                   |

| 2 Note | 0       | CSI40       | UART4                      | _                                   |

|        | 1       | CSI41       |                            | -                                   |

**Note** Serial array unit 2 is only mounted in the  $\mu$  PD78F1027, 78F1028, 78F1029, and 78F1030.

3-wire serial I/O (CSI00, CSI01, CSI10, CSI20, CSI40, CSI41) performs the following six types of communication operations.

- Master transmission (See 14.5.1.)

- Master reception (See 14.5.2.)

- Master transmission/reception (See 14.5.3.)

- Slave transmission (See 14.5.4.)

- Slave reception (See 14.5.5.)

- Slave transmission/reception (See 14.5.6.)

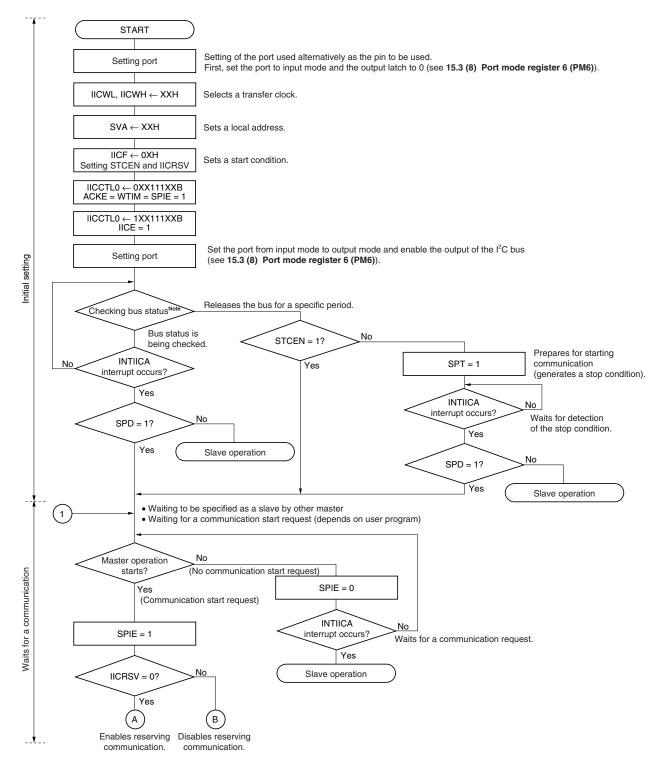

## (8) Port mode register 6 (PM6)

This register sets the input/output of port 6 in 1-bit units.

When using the P60/SCL0 pin as clock I/O and the P61/SDA0 pin as serial data I/O, clear PM60 and PM61, and the output latches of P60 and P61 to 0.

Set the IICE bit (bit 7 of IICA control register 0 (IICCTL0)) to 1 before setting the output mode because the P60/SCL0 and P61/SDA0 pins output a low level (fixed) when the IICE bit is 0.

The PM6 register can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation sets this register to FFH.

## Figure 15-12. Format of Port Mode Register 6 (PM6)

| Address: | FFF26H | After reset: | FFH R/W |   |   |   |      |      |

|----------|--------|--------------|---------|---|---|---|------|------|

| Symbol   | 7      | 6            | 5       | 4 | 3 | 2 | 1    | 0    |

| PM6      | 1      | 1            | 1       | 1 | 1 | 1 | PM61 | PM60 |

| [ | PM6n                             | P6n pin I/O mode selection (n = 0, 1) |  |  |  |  |  |  |

|---|----------------------------------|---------------------------------------|--|--|--|--|--|--|

|   | 0                                | Output mode (output buffer on)        |  |  |  |  |  |  |

|   | 1 Input mode (output buffer off) |                                       |  |  |  |  |  |  |

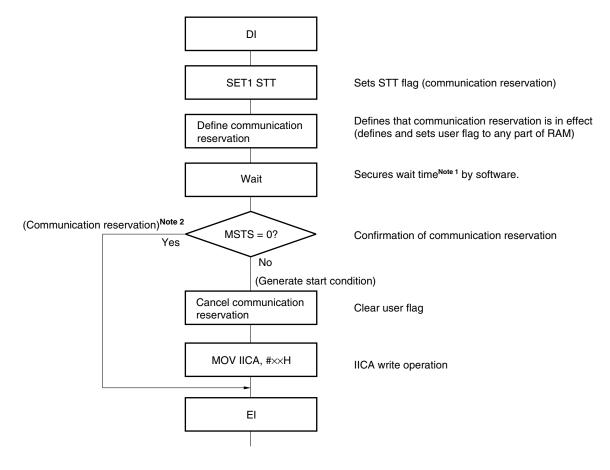

Figure 15-27. Communication Reservation Protocol

Notes 1. The wait time is calculated as follows.

(IICWL setting value + IICWH setting value + 4) + tF  $\times$  2  $\times$  fcLK [clocks]

- 2. The communication reservation operation executes a write to the IICA shift register (IICA) when a stop condition interrupt request occurs.

- Remark STT: Bit 1 of IICA control register 0 (IICCTL0)

- MSTS: Bit 7 of IICA status register (IICS)

- IICA: IICA shift register

- IICWL: IICA low-level width setting register

- IICWH: IICA high-level width setting register

- tF: SDA0 and SCL0 signal falling times

- fclk: CPU/peripheral hardware clock frequency

## (2) Master operation in multi-master system

**Note** Confirm that the bus is released (CLD bit = 1, DAD bit = 1) for a specific period (for example, for a period of one frame). If the SDA0 pin is constantly at low level, decide whether to release the l<sup>2</sup>C bus (SCL0 and SDA0 pins = high level) in conformance with the specifications of the product that is communicating.

RENESAS

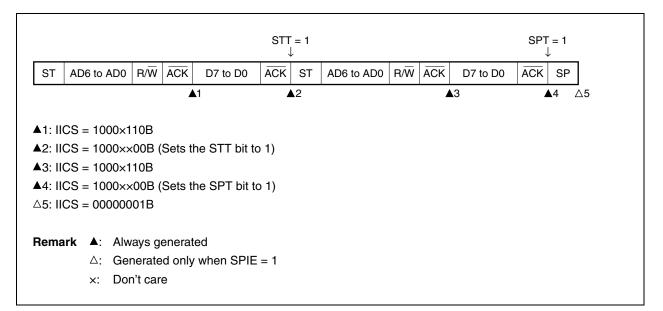

## (b) Start ~ Address ~ Data ~ Start ~ Address ~ Data ~ Stop (restart)

## (i) When WTIM = 0

|                                                     | STT = 1<br>↓                                                                                                                                                                                                                                                                                                                                                           |                                   |         |                    |     |    |            |     |     |          | SI  | PT = 1<br>↓ |    |

|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------|--------------------|-----|----|------------|-----|-----|----------|-----|-------------|----|

| ST                                                  | AD6 to A                                                                                                                                                                                                                                                                                                                                                               | D0 R/W                            | ACK     | D7 to D0           | ĀCK | ST | AD6 to AD0 | R/W | ĀCK | D7 to D0 | ACI | R SF        | 2  |

|                                                     |                                                                                                                                                                                                                                                                                                                                                                        |                                   |         | 1                  | 2   | 3  |            |     |     | <b>4</b> | ▲5  | ▲6          | ∆7 |

| ▲2: 110<br>▲3: 110<br>▲4: 110<br>▲5: 110<br>▲6: 110 |                                                                                                                                                                                                                                                                                                                                                                        |                                   |         |                    |     |    |            |     |     |          |     |             |    |

| Notes                                               | <ol> <li>Notes 1. To generate a start condition, set the WTIM bit to 1 and change the timing for generating the INTIICA interrupt request signal.</li> <li>Clear the WTIM bit to 0 to restore the original setting.</li> <li>To generate a stop condition, set the WTIM bit to 1 and change the timing for generating the INTIICA interrupt request signal.</li> </ol> |                                   |         |                    |     |    |            |     |     |          |     |             |    |

| Rema                                                | Δ:                                                                                                                                                                                                                                                                                                                                                                     | Always g<br>Generate<br>Don't car | ed only | ied<br>/ when SPIE | = 1 |    |            |     |     |          |     |             |    |

(ii) When WTIM = 1

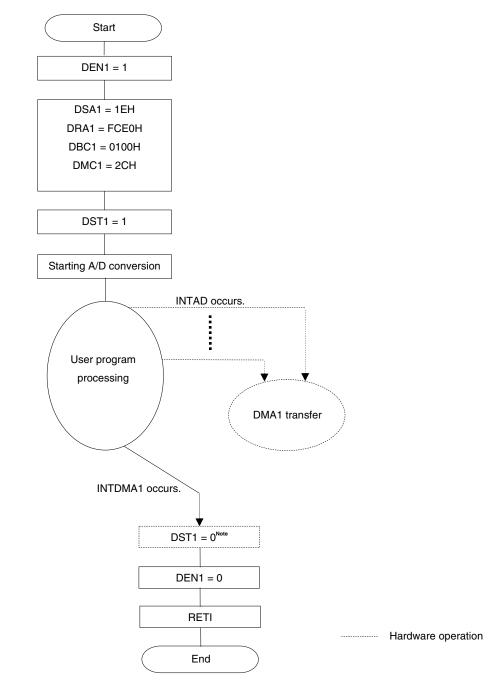

**Note** The DST1 flag is automatically cleared to 0 when a DMA transfer is completed.

Writing the DEN1 flag is enabled only when DST1 = 0. To terminate a DMA transfer without waiting for occurrence of the interrupt of DMA1 (INTDMA1), set the DST1 bit to 0 and then the DEN1 bit to 0 (for details, refer to **17.5.5 Forced termination by software**).

| Caution | The pins mounted depend | I on the product. Refer to Caution | a 2 at the beginning of this chapter. |

|---------|-------------------------|------------------------------------|---------------------------------------|

|---------|-------------------------|------------------------------------|---------------------------------------|

| •         |            | -    |                                               |                         |      |      | ,    |      |

|-----------|------------|------|-----------------------------------------------|-------------------------|------|------|------|------|

| Parameter | Symbol     |      | Conditions                                    |                         | MIN. | TYP. | MAX. | Unit |

| Supply    | DD2 Note 1 | HALT | $f_{SUB} = 32.768 \text{ kHz}^{Note 2},$      | V <sub>DD</sub> = 5.0 V |      | 0.9  | 2.9  | μA   |

| current   |            | mode | $T_A = -40 \text{ to } +50^{\circ}\text{C}$   | V <sub>DD</sub> = 3.0 V |      | 0.9  | 2.9  | μA   |

|           |            |      |                                               | V <sub>DD</sub> = 2.0 V |      | 0.9  | 2.9  | μA   |

|           |            |      | $f_{SUB} = 32.768 \text{ kHz}^{Note 2},$      | V <sub>DD</sub> = 5.0 V |      | 0.9  | 4.8  | μA   |

|           |            |      | $T_A = -40 \text{ to } +70^{\circ}\text{C}$   | V <sub>DD</sub> = 3.0 V |      | 0.9  | 4.8  | μA   |

|           |            |      |                                               | V <sub>DD</sub> = 2.0 V |      | 0.9  | 4.8  | μA   |

|           |            |      | $f_{SUB} = 32.768 \text{ kHz}^{Note 2},$      | V <sub>DD</sub> = 5.0 V |      | 0.9  | 7.1  | μA   |

|           |            |      | $T_A = -40 \text{ to } +85^{\circ}\text{C}$   | V <sub>DD</sub> = 3.0 V |      | 0.9  | 7.1  | μA   |

|           |            |      |                                               | V <sub>DD</sub> = 2.0 V |      | 0.9  | 7.1  | μA   |

|           | DD3        | STOP | $T_A = -40 \text{ to } +50^{\circ}\text{C}$   |                         |      | 0.33 | 2.1  | μA   |

|           |            | mode | $T_A = -40 \text{ to } +70^{\circ}\text{C}$   |                         |      | 0.33 | 4    | μA   |

|           |            |      | $T_{A} = -40 \text{ to } +85^{\circ}\text{C}$ |                         |      | 0.33 | 6.2  | μA   |

- **Notes 1.** Total current flowing into VDD, EVDD, and AVREF, including the input leakage current flowing when the level of the input pin is fixed to VDD or VSS. The maximum value includes the peripheral operation current. However, not including the current flowing into the A/D converter, programmable gain amplifier, comparator, LVI circuit, I/O port, and on-chip pull-up/pull-down resistors. During HALT instruction execution in flash memory.

- 2. When operating real-time counter (RTC) and setting ultra-low current consumption (AMPHS1 (bit2 of CMC register) = 1, OSMC = 82H). When internal high-speed oscillation, 20 MHz internal high-speed oscillation, and high-speed system clock are stopped. When watchdog timer is stopped. When RTCLPC = 1 (stops supply of subsystem clock to peripheral functions other than real-time counter). When output function of RTC is stopped.

- 3. Total current flowing into VDD, EVDD, and AVREF, including the input leakage current flowing when the level of the input pin is fixed to VDD or Vss. The maximum value includes the peripheral operation current. However, not including the current flowing into the A/D converter, programmable gain amplifier, comparator, LVI circuit, I/O port, and on-chip pull-up/pull-down resistors. When subsystem clock is stopped.

- Remarks 1. fsub: Subsystem clock frequency (XT1 clock oscillation frequency)

- 2. RTCLPC: bit 7 of the operation speed mode control register (OSMC)

- **3.** Temperature condition of the TYP. value is  $T_A = 25^{\circ}C$

Caution The pins mounted depend on the product. Refer to Caution 2 at the beginning of this chapter.

| Parameter                     | Symbol  | Conditions                                                                                                                                                                     | MIN.       | MAX.                | Unit |

|-------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------|------|

| SCLr clock frequency          | fscL    | $2.7 \text{ V} \leq \text{V}_{\text{DD}} \leq 5.5 \text{ V},$ $C_{\text{b}} = 100 \text{ pF}, \text{ R}_{\text{b}} = 3 \text{ k}\Omega$                                        |            | 400 <sup>Note</sup> | kHz  |

|                               |         | $\begin{array}{l} 1.8 \ V \leq V_{DD} < 2.7 \ V, \\ C_b = 100 \ pF, \ R_b = 5 \ k\Omega \end{array}$                                                                           |            | 300 <sup>Note</sup> | kHz  |

| Hold time when SCLr = "L"     | t∟ow    | $\label{eq:linear} \begin{array}{l} 2.7 \mbox{ V} \leq V_{DD} \leq 5.5 \mbox{ V}, \\ C_b = 100 \mbox{ pF}, \mbox{ R}_b = 3 \mbox{ k}\Omega \end{array}$                        | 1200       |                     | ns   |

|                               |         | $\label{eq:VDD} \begin{split} &1.8 \ V \leq V_{\text{DD}} < 2.7 \ V, \\ &C_{\text{b}} = 100 \ \text{pF}, \ R_{\text{b}} = 5 \ \text{k}\Omega \end{split}$                      | 1500       |                     | ns   |

| Hold time when SCLr = "H"     | tніgн   | $\label{eq:VDD} \begin{array}{l} 2.7 \ V \leq V_{\text{DD}} \leq 5.5 \ V, \\ C_{\text{b}} = 100 \ \text{pF}, \ R_{\text{b}} = 3 \ \text{k}\Omega \end{array}$                  | 1200       |                     | ns   |

|                               |         | $\label{eq:VDD} \begin{split} 1.8 \ V &\leq V_{\text{DD}} < 2.7 \ V, \\ C_{\text{b}} &= 100 \ \text{pF}, \ R_{\text{b}} = 5 \ \text{k}\Omega \end{split}$                      | 1500       |                     | ns   |

| Data setup time (reception)   | tsu:dat | $\label{eq:VDD} \begin{array}{l} 2.7 \; V \leq V_{\text{DD}} \leq 5.5 \; V, \\ C_{\text{b}} = 100 \; p\text{F}, \; R_{\text{b}} = 3 \; k\Omega \end{array}$                    | 1/fмск+120 |                     | ns   |

|                               |         | $\label{eq:VDD} \begin{split} 1.8 \ V &\leq V_{\text{DD}} < 2.7 \ V, \\ C_{\text{b}} &= 100 \ \text{pF}, \ R_{\text{b}} = 5 \ \text{k}\Omega \end{split}$                      | 1/fмск+230 |                     | ns   |

| Data hold time (transmission) | thd:dat | $\label{eq:VDD} \begin{array}{l} 2.7 \mbox{ V} \leq \mbox{ V}_{\mbox{DD}} \leq 5.5 \mbox{ V}, \\ C_{\mbox{b}} = 100 \mbox{ pF}, \mbox{ R}_{\mbox{b}} = 3  k\Omega \end{array}$ | 0          | 660                 | ns   |

|                               |         | $\label{eq:VDD} \begin{split} 1.8 \ V &\leq V_{\text{DD}} < 2.7 \ V, \\ C_{\text{b}} &= 100 \ \text{pF}, \ R_{\text{b}} = 5 \ \text{k}\Omega \end{split}$                      | 0          | 710                 | ns   |

#### (4) During communication at same potential (simplified $I^2C$ mode) (T<sub>A</sub> = -40 to +85°C, 2.7 V < V<sub>DD</sub> = EV<sub>DD0</sub> = EV<sub>DD1</sub> < 5.5 V, V<sub>SS</sub> = EV<sub>SS0</sub> = EV<sub>SS1</sub> = AV<sub>SS</sub> = 0 V)

**Note** The value must also be fmck/4 or more.

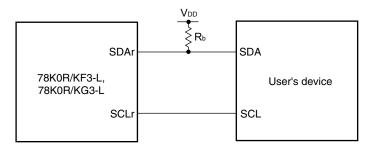

## Simplified I<sup>2</sup>C mode mode connection diagram (during communication at same potential)