# E. Renesas Electronics America Inc - UPD78F1007GA-HAB-AX Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | 78K/0R                                                                               |

| Core Size                  | 16-Bit                                                                               |

| Speed                      | 20MHz                                                                                |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                     |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                              |

| Number of I/O              | 50                                                                                   |

| Program Memory Size        | 32KB (32K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 1.5K x 8                                                                             |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                          |

| Data Converters            | A/D 12x10b                                                                           |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 64-TQFP                                                                              |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f1007ga-hab-ax |

|                            |                                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# (1) Port functions (2/2): 78K0R/KC3-L (40-pin)

| Function Name | I/O   | Function                                                                                                                                                     | After Reset           | Alternate Function   |  |

|---------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------|--|

| P80           | I/O   | Port 8.<br>3-bit I/O port.                                                                                                                                   | Analog input          | CMP0P/INTP3/<br>PGAI |  |

| P81           |       | Inputs/output can be specified in 1-bit units.                                                                                                               |                       | СМРОМ                |  |

| P83           |       | Inputs of P80, P81, and P83 can be set as comparator inputs or programmable gain amplifier inputs.                                                           |                       | CMP1M                |  |

| P120          | I/O   | Port 12.                                                                                                                                                     | Input port            | INTP0/EXLVI          |  |

| P121          | Input | 1-bit I/O port and 2-bit input port.                                                                                                                         |                       | X1                   |  |

| P122          |       | For only P120, input/output can be specified in 1-bit units.<br>For only P120, use of an on-chip pull-up resistor can be specified<br>by a software setting. |                       | X2/EXCLK             |  |

| P150, P151    | I/O   | Port 15.<br>2-bit I/O port.<br>Input/output can be specified in 1-bit units.                                                                                 | Digital input<br>port | ANI8, ANI9           |  |

| (1) Port functions | s (2/2): 78K0R/KD3-L |

|--------------------|----------------------|

|--------------------|----------------------|

| Function Name | I/O    | Function                                                                                                                                                     | After Reset           | Alternate Function   |

|---------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------|

| P70           | I/O    | Port 7.                                                                                                                                                      | Input port            | KR0/SO01/INTP4       |

| P71           |        | 8-bit I/O port.                                                                                                                                              |                       | KR1/SI01/INTP5       |

| P72           |        | Input of P71, P72, P74, and P75 can be set to TTL buffer.<br>Output of P70, P72, P73, and P75 can be set to N-ch open-drain                                  |                       | KR2/SCK01/INTP6      |

| P73           |        | output $(V_{DD} \text{ tolerance})$ .                                                                                                                        |                       | KR3/SO00/TxD0        |

| P74           |        | Input/output can be specified in 1-bit units.                                                                                                                |                       | KR4/SI00/RxD0        |

| P75           |        | Use of an on-chip pull-up resistor can be specified by a software                                                                                            |                       | KR5/SCK00            |

| P76           |        | setting.                                                                                                                                                     |                       | KR6                  |

| P77           |        |                                                                                                                                                              |                       | KR7                  |

| P80           | I/O    | Port 8.<br>4-bit I/O port.                                                                                                                                   | Analog input          | CMP0P/INTP3/<br>PGAI |

| P81           |        | Inputs/output can be specified in 1-bit units.<br>Inputs of P80 to P83 can be set as comparator inputs or<br>programmable gain amplifier inputs.             |                       | CMP0M                |

| P82           |        |                                                                                                                                                              |                       | CMP1P/INTP7          |

| P83           |        |                                                                                                                                                              |                       | CMP1M                |

| P120          | I/O    | Port 12.                                                                                                                                                     | Input port            | INTP0/EXLVI          |

| P121          | Input  | 1-bit I/O port and 4-bit input port.                                                                                                                         |                       | X1                   |

| P122          |        | For only P120, input/output can be specified in 1-bit units.<br>For only P120, use of an on-chip pull-up resistor can be specified<br>by a software setting. |                       | X2/EXCLK             |

| P123          |        |                                                                                                                                                              |                       | XT1                  |

| P124          |        |                                                                                                                                                              |                       | XT2                  |

| P140          | Output | Port 14.<br>1-bit output port.                                                                                                                               | Output port           | PCLBUZ0              |

| P150 to P152  | I/O    | Port 15.<br>3-bit I/O port.<br>Input/output can be specified in 1-bit units.                                                                                 | Digital input<br>port | ANI8 to ANI10        |

# 3.2 Description of Pin Functions

Remark The pins mounted depend on the product. See 1.4 Pin Configuration (Top View) and 3.1 Pin Function List.

### 3.2.1 P00 to P06 (port 0)

P00 to P06 function as an I/O port. These pins also function as timer I/O, serial interface data I/O, and clock I/O. Input to the P03 and P04 pins can be specified through a normal input buffer or a TTL input buffer in 1-bit units, using port input mode register 0 (PIM0).

Output from the P02 to P04 pins can be specified as normal CMOS output or N-ch open-drain output (V<sub>DD</sub> tolerance) in 1-bit units, using port output mode register 0 (POM0).

|                     | 78K0R/KF3-L                    | 78K0R/KG3-L                |

|---------------------|--------------------------------|----------------------------|

|                     | (µ PD78F10xx: xx = 10, 11, 12, | (μ PD78F10xx: xx = 13, 14, |

|                     | 27, 28)                        | 29, 30)                    |

| P00/TI00            | Note 1                         | $\checkmark$               |

| P01/TO00            | Note 1                         | $\checkmark$               |

| P02/SO10/TxD1       |                                |                            |

| P03/SI10/RxD1/SDA10 | $\checkmark$                   | $\checkmark$               |

| P04/SCK10/SCL10     | $\checkmark$                   | $\checkmark$               |

| P05/TI05/TO05       |                                | P05 <sup>Note 2</sup>      |

| P06/TI06/TO06       |                                | P06 <sup>Note 2</sup>      |

Notes 1. TI00 and TO00 are shared with P53 and P52, respectively, in the 78K0R/KF3-L.

2. TI05/TO05 and TI06/TO06 are shared with P46 and P131, respectively, in the 78K0R/KG3-L.

The following operation modes can be specified in 1-bit units.

### (1) Port mode

P00 to P06 function as an I/O port. P00 to P06 can be set to input or output port in 1-bit units using port mode register 0 (PM0). Use of an on-chip pull-up resistor can be specified by pull-up resistor option register 0 (PU0).

### (2) Control mode

P00 to P04 function as timer I/O, serial interface data I/O, and clock I/O.

### (a) TI00, TI05, and TI06

There are the pins for inputting an external count clock/capture trigger to 16-bit timers 00, 05, and 06.

### (b) TO00, TO05, and TO06

These are the timer output pins of 16-bit timers 00, 05, and 06.

### (c) SI10

This is a serial data input pin of serial interface CSI10.

# (d) SO10

This is a serial data output pin of serial interface CSI10.

| Address          | Special Function Register (SFR) Name               | Symbol        | Symbol R/W |       |              | Range        | After Reset | K              | Z              | K              | 즈            | Ā            | 조            | Ā            |

|------------------|----------------------------------------------------|---------------|------------|-------|--------------|--------------|-------------|----------------|----------------|----------------|--------------|--------------|--------------|--------------|

|                  |                                                    |               |            | 1-bit | 8-bit        | 16-bit       |             | KC3-L (40-pin) | KC3-L (44-pin) | KC3-L (48-pin) | KD3-L        | KE3-L        | KF3-L        | KG3-L        |

| F0158H           | Serial communication operation setting register 10 | SCR10         | R/W        | -     | -            | $\checkmark$ | 0087H       | -              | -              | -              | _            | -            | $\checkmark$ | $\checkmark$ |

| F0159H           |                                                    | 00544         | DAA        |       |              | 1            |             |                |                |                |              |              | /            |              |

| F015AH           | Serial communication operation setting register 11 | SCR11         | R/W        | -     | -            | $\checkmark$ | 0087H       | -              | -              | -              | -            | -            | V            | $\checkmark$ |

| F015BH           |                                                    | 00040         |            |       |              | 1            | 000711      |                |                |                |              |              | 1            | V            |

| F015CH           | Serial communication operation setting register 12 | SCR12         | R/W        | -     | -            | $\checkmark$ | 0087H       | -              | -              | -              | -            | -            | V            | N            |

| F015DH           | Serial communication operation                     | SCR13         |            |       |              |              | 0087H       |                |                |                |              |              |              | V            |

| F015EH<br>F015FH | setting register 13                                | 30113         | R/W        | -     | _            | v            | 0087 П      | _              |                | -              | _            | _            | v            | v            |

| F0160H           | Serial channel enable status                       | SE1L SE1      | R          |       |              |              | 0000H       | _              | _              |                | _            | _            |              |              |

| F0161H           | register 1                                         |               |            |       | _            | , v          | 000011      | _              | _              | _              | _            | _            | v<br>√       | V            |

| F0162H           | Serial channel start register 1                    | SS1L SS1      | R/W        |       |              |              | 0000H       | _              | _              | _              | _            | _            | √            |              |

| F0163H           | 0                                                  |               |            | _     | -            |              |             | _              | _              | -              | _            | _            | $\checkmark$ | $\checkmark$ |

| F0164H           | Serial channel stop register 1                     | ST1L ST1      | R/W        |       |              | $\checkmark$ | 0000H       | -              | _              | -              | -            | -            | $\checkmark$ | $\checkmark$ |

| F0165H           |                                                    | _             |            | _     | -            |              |             | -              | -              | -              | _            | _            | $\checkmark$ | $\checkmark$ |

| F0166H           | Serial clock select register 1                     | SPS1L SPS1    | R/W        | -     | $\checkmark$ | $\checkmark$ | 0000H       | -              | -              | -              | -            | _            | $\checkmark$ | $\checkmark$ |

| F0167H           |                                                    | -             |            | _     | -            |              |             | _              | -              | -              | -            |              | $\checkmark$ | $\checkmark$ |

| F0168H           | Serial output register 1                           | SO1           | R/W        | -     | -            | $\checkmark$ | 0F0FH       | -              | _              | -              | -            | -            | $\checkmark$ | $\checkmark$ |

| F0169H           |                                                    |               |            |       |              |              |             |                |                |                |              |              |              |              |

| F016AH           | Serial output enable register 1                    | SOE1L SOE1    | R/W        |       |              | $\checkmark$ | 0000H       | _              | -              | -              | -            | -            | $\checkmark$ | $\checkmark$ |

| F016BH           |                                                    | -             |            | -     | -            |              |             | -              | -              | -              | -            | -            | $\checkmark$ | $\checkmark$ |

| F0174H           | Serial output level register 1                     | SOL1L SOL1    | R/W        | -     |              | $\checkmark$ | 0000H       | -              | -              | -              | -            | -            | $\checkmark$ | $\checkmark$ |

| F0175H           |                                                    | _             |            | -     | -            |              |             | -              | -              | -              | -            | -            | $\checkmark$ | $\checkmark$ |

| F0180H           | Timer counter register 00                          | TCR00         | R          | -     | -            | $\checkmark$ | FFFFH       | $\checkmark$   | $\checkmark$   | V              | V            | V            | V            | $\checkmark$ |

| F0181H           |                                                    |               |            |       |              | 1            |             | ,              | ,              | ,              | ,            | ,            | ,            |              |

| F0182H           | Timer counter register 01                          | TCR01         | R          | -     | -            | $\checkmark$ | FFFFH       |                | $\checkmark$   | V              | $\checkmark$ | $\checkmark$ | V            |              |

| F0183H           | Timor counter register 00                          | TODAA         |            |       |              |              | FFFFU       | ./             | ./             | ./             | V            | V            |              |              |

| F0184H<br>F0185H | Timer counter register 02                          | TCR02         | R          | -     | -            | $\checkmark$ | FFFFH       | V              | V              | V              | N            | N            | V            | V            |

| F0185H           | Timer counter register 03                          | TCR03         | R          | _     |              |              | FFFFH       | V              |                |                |              |              |              | V            |

| F0187H           | Timer counter register Us                          | 101100        |            |       |              | v            |             | N              | V              | Ň              | v            | v            | v            | Ň            |

| F0188H           | Timer counter register 04                          | TCR04         | R          | _     | _            |              | FFFFH       |                |                | V              |              |              |              |              |

| F0189H           |                                                    |               |            |       |              | v            |             | Ň              | , v            | ľ              | v            | v            | Ň            | ľ            |

| F018AH           | Timer counter register 05                          | ster 05 TCR05 |            | _     | _            |              | FFFFH       |                |                |                |              |              |              |              |

| F018BH           |                                                    |               |            |       |              |              |             |                |                |                |              |              |              |              |

| F018CH           | Timer counter register 06                          | TCR06         | R          | _     | _            | $\checkmark$ | FFFFH       |                |                |                |              |              |              | $\checkmark$ |

| F018DH           | Ŭ                                                  |               |            |       |              |              |             | 1              |                |                |              |              |              |              |

| F018EH           | Timer counter register 07                          | TCR07         | R          | _     | _            | $\checkmark$ | FFFFH       |                |                | $\checkmark$   |              |              |              | $\checkmark$ |

| F018FH           | -                                                  |               |            |       |              |              |             | 1              |                |                |              |              |              |              |

# Table 4-6. Extended SFR (2nd SFR) List (4/8)

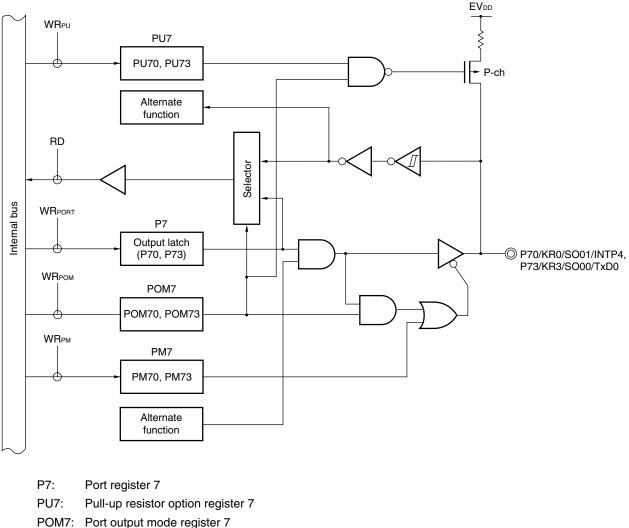

# Figure 5-15. Block Diagram of P70 and P73

- PM7: Port mode register 7

- RD: Read signal

- WR××: Write signal

Remark With products not provided with an EVDD or EVss pin, replace EVDD with VDD, or replace EVss with Vss.

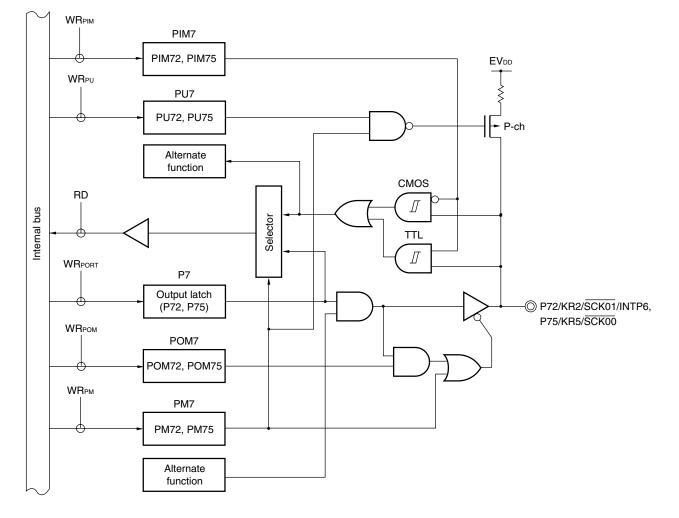

Figure 5-17. Block Diagram of P72 and P75

- P7: Port register 7

- PU7: Pull-up resistor option register 7

- PM7: Port mode register 7

- PIM7: Port input mode register 7

- POM7: Port output mode register 7

- RD: Read signal

- WR××: Write signal

Remark With products not provided with an EVDD or EVss pin, replace EVDD with VDD, or replace EVss with Vss.

| Symbol | 7   | 6        | 5          | 4           | 3         | 2            | 1                               | 0        | Address | After reset        | R/W                 |

|--------|-----|----------|------------|-------------|-----------|--------------|---------------------------------|----------|---------|--------------------|---------------------|

| P0     | 0   | P06      | P05        | P04         | P03       | P02          | 0                               | 0        | FFF00H  | 00H (output latch) | R/W                 |

|        |     | - L      | L          | 1           |           | L            |                                 |          | 4       |                    |                     |

| P1     | P17 | P16      | P15        | P14         | P13       | P12          | P11                             | P10      | FFF01H  | 00H (output latch) | R/W                 |

|        |     | 1        | l.         |             | l.        | l.           | l .                             |          |         |                    |                     |

| P2     | P27 | P26      | P25        | P24         | P23       | P22          | P21                             | P20      | FFF02H  | 00H (output latch) | R/W                 |

|        | E   |          |            |             |           |              |                                 |          |         |                    |                     |

| P3     | 0   | 0        | 0          | 0           | 0         | 0            | P31                             | P30      | FFF03H  | 00H (output latch) | R/W                 |

|        |     | -        | -          | -           | -         | -            |                                 |          |         |                    |                     |

| P4     | P47 | P46      | P45        | P44         | P43       | P42          | P41                             | P40      | FFF04H  | 00H (output latch) | R/W                 |

|        |     | -        | -          | _           | -         | -            | -                               |          |         |                    |                     |

| P5     | 0   | 0        | P55        | P54         | P53       | P52          | P51                             | P50      | FFF05H  | 00H (output latch) | R/W                 |

|        |     |          |            |             |           |              |                                 |          |         |                    |                     |

| P6     | P67 | P66      | P65        | P64         | P63       | P62          | P61                             | P60      | FFF06H  | 00H (output latch) | R/W                 |

|        | P   | 1        |            |             |           |              |                                 |          | L       |                    |                     |

| P7     | P77 | P76      | P75        | P74         | P73       | P72          | P71                             | P70      | FFF07H  | 00H (output latch) | R/W                 |

|        | r   | 1        | r          |             | r         | r            | r                               | T        | I       |                    |                     |

| P9     | 0   | 0        | 0          | 0           | 0         | 0            | P91                             | P90      | FFF09H  | 00H (output latch) | R/W                 |

|        | r   | Т        | 1          | 1           | 1         | 1            | 1                               | 1        | 1       |                    |                     |

| P11    | 0   | 0        | 0          | 0           | 0         | 0            | P111                            | P110     | FFF0BH  | 00H (output latch) | R/W                 |

|        | r   | Т        | 1          | 1           | 1         | 1            | 1                               | 1        | 1       |                    |                     |

| P12    | 0   | 0        | 0          | P124        | P123      | P122         | P121                            | P120     | FFF0CH  | Undefined          | R/W <sup>Note</sup> |

|        | r   | Т        | 1          | 1           | 1         | 1            | 1                               | 1        | 1       |                    |                     |

| P13    | 0   | 0        | 0          | 0           | 0         | 0            | 0                               | P130     | FFF0DH  | 00H (output latch) | R/W                 |

|        | r   | Т        | 1          | 1           | 1         | 1            | 1                               | 1        | Ì       |                    |                     |

| P14    | 0   | 0        | 0          | P144        | P143      | P142         | 0                               | P140     | FFF0EH  | 00H (output latch) | R/W                 |

|        | r   | T        |            |             |           |              |                                 | 1        | I       |                    |                     |

| P15    | 0   | 0        | 0          | 0           | P153      | P152         | P151                            | P150     | FFF0FH  | 00H (output latch) | R/W                 |

|        | r   |          |            |             |           |              |                                 |          |         |                    | -                   |

|        | Pmn |          |            |             | m =       | 0 to 7, 9, 1 | 9, 11 to 15; n = 0 to 7         |          |         |                    | _                   |

|        |     | Οι       | utput data | control (in | output mo | de)          | Input data read (in input mode) |          |         |                    |                     |

|        | 0   | Output 0 |            |             |           |              | Input low level                 |          |         |                    |                     |

|        | 1   | Output 1 |            |             |           |              | Input hig                       | ih level |         |                    |                     |

# Figure 6-54. Format of Port Register (78K0R/KF3-L)

Note P121 to P124 are read-only.

# (2) System clock control register (CKC)

This register is used to select a CPU/peripheral hardware clock and a division ratio. The CKC register can be set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation sets this register to 09H.

### Figure 7-5. Format of System Clock Control Register (CKC)

| Address: FF | FA4H Afte             | r reset: 09H | R/W <sup>Note 1</sup> |      |   |       |       |       |

|-------------|-----------------------|--------------|-----------------------|------|---|-------|-------|-------|

| Symbol      | <7>                   | <6>          | <5>                   | <4>  | 3 | 2     | 1     | 0     |

| СКС         | CLS <sup>Note 2</sup> | CSS          | MCS                   | MCM0 | 1 | MDIV2 | MDIV1 | MDIV0 |

|             |                       |              |                       |      |   |       |       |       |

| CLS <sup>Note 2</sup> | Status of CPU/peripheral hardware clock (fcLK) |  |  |  |

|-----------------------|------------------------------------------------|--|--|--|

| 0                     | lain system clock (f <sub>MAIN</sub> )         |  |  |  |

| 1                     | Subsystem clock divided by 2 (fsuB/2)          |  |  |  |

| MCS | Status of Main system clock (fmain)                                                                   |

|-----|-------------------------------------------------------------------------------------------------------|

| 0   | Internal high-speed oscillation clock (f_H) or 20 MHz internal high-speed oscillation clock (f_{H20}) |

| 1   | High-speed system clock (fмx)                                                                         |

| MCM0 | Main system clock (fmain) operation control                                                                                                                            |  |  |  |  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 0    | Selects the internal high-speed oscillation clock ( $f_{IH}$ ) or 20 MHz internal high-speed oscillation clock ( $f_{IH20}$ ) as the main system clock ( $f_{IMAIN}$ ) |  |  |  |  |

| 1    | Selects the high-speed system clock (f <sub>MX</sub> ) as the main system clock (f <sub>MAIN</sub> )                                                                   |  |  |  |  |

| CSS      | MDIV2      | MDIV1    | MDIV0 | Selection of CPU/peripheral<br>hardware clock (fcLk)    |

|----------|------------|----------|-------|---------------------------------------------------------|

| 0        | 0          | 0        | 0     | fmain                                                   |

|          | 0          | 0        | 1     | $f_{MAIN}/2$ (This is the default setting if MCM0 = 0.) |

|          | 0          | 1        | 0     | fmain/2 <sup>2</sup>                                    |

|          | 0          | 1        | 1     | fmain/2 <sup>3 Note 3</sup>                             |

|          | 1          | 0        | 0     | fmain/2 <sup>4 Note 3</sup>                             |

|          | 1          | 0        | 1     | fmain/2 <sup>5 Notes 3, 4</sup>                         |

| 1 Note 5 | ×          | ×        | ×     | fsue/2                                                  |

|          | Other that | an above |       | Setting prohibited                                      |

Notes 1. Bits 7 and 5 are read-only.

- 2. CLS bit is not provided in the 78K0R/KC3-L (40-pin). In the 78K0R/KC3-L (40-pin), bit 7 is fixed to 0.

- **3.** Setting is prohibited if the 1 MHz Internal high-speed oscillation clock frequency (fiH1) is selected as the main system clock (fMAIN).

- **4.** Setting is prohibited if the high-speed system clock (f<sub>MX</sub>) is selected as the main system clock (f<sub>MAIN</sub>) and if f<sub>MX</sub> < 4 MHz.

- 5. Changing the value of the MCM0 bit is prohibited while the CSS bit is set to 1.

(Remarks and Cautions are listed on the next page.)

| CPU                                                | Clock                                              | Condition Before Change                                                                                                                                                                                                                      | Processing After Change                                                    |

|----------------------------------------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| Before Change                                      | After Change                                       |                                                                                                                                                                                                                                              |                                                                            |

| Subsystem<br>clock <sup>Note</sup>                 | Internal high-<br>speed oscillation<br>clock       | Oscillation of internal high-speed oscillator<br>and selection of internal high-speed<br>oscillation clock as main system clock<br>• HIOSTOP = 0, MCS = 0                                                                                    | XT1 oscillation can be stopped (XTSTOP = 1)                                |

|                                                    | X1 clock                                           | <ul> <li>Stabilization of X1 oscillation and selection<br/>of high-speed system clock as main system<br/>clock</li> <li>OSCSEL = 1, EXCLK = 0, MSTOP = 0</li> <li>After elapse of oscillation stabilization time</li> <li>MCS = 1</li> </ul> |                                                                            |

|                                                    | External main<br>system clock                      | Enabling input of external clock from the<br>EXCLK pin and selection of high-speed<br>system clock as main system clock<br>• OSCSEL = 1, EXCLK = 1, MSTOP = 0<br>• MCS = 1                                                                   |                                                                            |

|                                                    | 20 MHz internal<br>high-speed<br>oscillation clock | Transition cannot be performed unless the<br>clock is changed to the internal high-speed<br>oscillation clock once.                                                                                                                          | -                                                                          |

| 20 MHz internal<br>high-speed<br>oscillation clock | Internal high-<br>speed oscillation<br>clock       | • SELDSC = 0<br>(Set when changing the clock.)                                                                                                                                                                                               | 20 MHz internal high-speed oscillation clock<br>can be stopped (DSCON = 0) |

|                                                    | X1 clock                                           | Transition cannot be performed unless the<br>clock is changed to the internal high-speed<br>oscillation clock once.                                                                                                                          | _                                                                          |

|                                                    | External main<br>system clock                      | Transition cannot be performed unless the<br>clock is changed to the internal high-speed<br>oscillation clock once.                                                                                                                          | _                                                                          |

|                                                    | Subsystem<br>clock <sup>Note</sup>                 | Transition cannot be performed unless the<br>clock is changed to the internal high-speed<br>oscillation clock once.                                                                                                                          | _                                                                          |

| Table 7-5. | Changing | CPU Clock (2/2) |

|------------|----------|-----------------|

|------------|----------|-----------------|

Note The 78K0R/KC3-L (40-pin) doesn't have the subsystem clock.

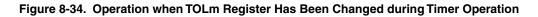

# (3) Operation of TOmn pin in slave channel output mode (TOMmn = 1)

### (a) When timer output level register m (TOLm) setting has been changed during timer operation

When the TOLm register setting has been changed during timer operation, the setting becomes valid at the generation timing of the TOmn pin change condition. Rewriting the TOLm register does not change the output level of the TOmn pin.

The operation when TOMmn is set to 1 and the value of the TOLm register is changed while the timer is operating (TEmn = 1) is shown below.

Remarks 1. Set:The output signal of the TOmn pin changes from inactive level to active level.Reset:The output signal of the TOmn pin changes from active level to inactive level.

| m: Unit number (m = 0, 1), n: Ch | nannel number (n = 0 to 7)                                                                                              |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| However, in case of the timer ou | tput pin (TOmn), mn changes as below.                                                                                   |

| 78K0R/KC3-L (40-pin):            | mn = 02 to 07                                                                                                           |

| 78K0R/KC3-L (44-pin, 48-pin):    | mn = 00 to 07                                                                                                           |

| 78K0R/KD3-L, 78K0R/KE3-L:        | mn = 00 to 07                                                                                                           |

| 78K0R/KF3-L, 78K0R/KG3-L:        | mn = 00 to 07, 10 to 13                                                                                                 |

|                                  | However, in case of the timer ou<br>78K0R/KC3-L (40-pin):<br>78K0R/KC3-L (44-pin, 48-pin):<br>78K0R/KD3-L, 78K0R/KE3-L: |

| Time of Alarm         |        | Day    |         |           |          |        | 12-Hour Display |      |      | 24-Hour Display |        |      |      |        |        |

|-----------------------|--------|--------|---------|-----------|----------|--------|-----------------|------|------|-----------------|--------|------|------|--------|--------|

|                       | Sunday | Monday | Tuesday | Wednesday | Thursday | Friday | Saturday        | Hour | Hour | Minute          | Minute | Hour | Hour | Minute | Minute |

|                       |        |        |         |           |          |        |                 | 10   | 1    | 10              | 1      | 10   | 1    | 10     | 1      |

|                       | W      | W      | W       | W         | W        | W      | W               |      |      |                 |        |      |      |        |        |

|                       | W      | W      | W       | W         | W        | W      | W               |      |      |                 |        |      |      |        |        |

|                       | 0      | 1      | 2       | 3         | 4        | 5      | 6               |      |      |                 |        |      |      |        |        |

| Every day, 0:00 a.m.  | 1      | 1      | 1       | 1         | 1        | 1      | 1               | 1    | 2    | 0               | 0      | 0    | 0    | 0      | 0      |

| Every day, 1:30 a.m.  | 1      | 1      | 1       | 1         | 1        | 1      | 1               | 0    | 1    | 3               | 0      | 0    | 1    | 3      | 0      |

| Every day, 11:59 a.m. | 1      | 1      | 1       | 1         | 1        | 1      | 1               | 1    | 1    | 5               | 9      | 1    | 1    | 5      | 9      |

| Monday through        | 0      | 1      | 1       | 1         | 1        | 1      | 0               | 3    | 2    | 0               | 0      | 1    | 2    | 0      | 0      |

| Friday, 0:00 p.m.     |        |        |         |           |          |        |                 |      |      |                 |        |      |      |        |        |

| Sunday, 1:30 p.m.     | 1      | 0      | 0       | 0         | 0        | 0      | 0               | 2    | 1    | 3               | 0      | 1    | 3    | 3      | 0      |

| Monday, Wednesday,    | 0      | 1      | 0       | 1         | 0        | 1      | 0               | 3    | 1    | 5               | 9      | 2    | 3    | 5      | 9      |

| Friday, 11:59 p.m.    |        |        |         |           |          |        |                 |      |      |                 |        |      |      |        |        |

Here is an example of setting the alarm.

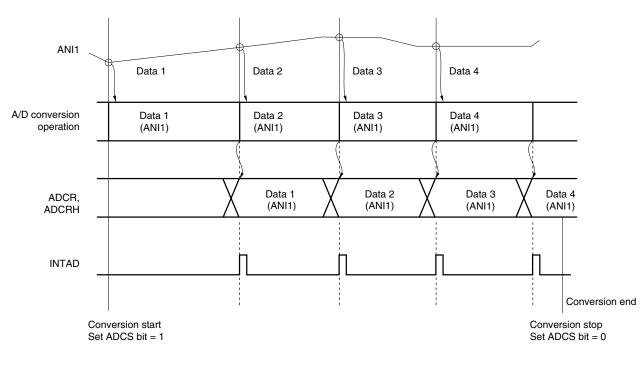

### 13.4.3 A/D converter operation modes

The select mode and scan mode are provided as the A/D converter operation modes.

# (1) Select mode

One analog input specified by the analog input channel specification register (ADS), while the ADMD bit of the A/D converter mode register (ADM) is 0, is A/D converted.

When A/D conversion is complete, the conversion result is stored in the A/D conversion result register (ADCR) and the A/D conversion end interrupt request signal (INTAD) is generated.

After A/D conversion has been completed, A/D conversion is repeated successively, unless the ADCS bit is set to 0. If anything is written to the ADM or ADS register during conversion, A/D conversion is aborted. In this case, A/D conversion is started again from the beginning.

Figure 13-14. Example of Select Mode Operation Timing

# Starting setting for resumption Manipulating target for communication (Essential) (Essential) Port manipulation mode register. (Selective) Changing setting of the SPSm register (Selective) Changing setting of the SMRmn register (Selective) Changing setting of the SCRmn register Clearing error flag (Selective) Changing setting of the SOEm register (Selective) Changing setting of the SOm register (Selective) data (SOmn). Changing setting of the SOEm register (Selective) Port manipulation (Essential) register. (Essential) Writing to the SSm register (Essential) Starting communication (Essential) Starting target for communication

### Figure 14-69. Procedure for Resuming Slave Transmission/Reception

Stop the target for communication or wait until the target completes its operation.

Disable data output of the target channel by setting a port register and a port mode register.

Re-set the register to change the operation clock setting.

Re-set the register to change serial mode register mn (SMRmn) setting.

Re-set the register to change serial communication operation setting register mn (SCRmn) setting.

If the FEF, PEF, and OVF flags remain set, clear them using serial flag clear trigger register mn (SIRmn).

Set the SOEmn bit to 0 to stop output from the target channel.

Set the initial output level of the serial data (SOmn).

Set the SOEmn bit to 1 and enable output from the target channel.

Enable data output of the target channel by setting a port register and a port mode register.

Set the SSmn bit of the target channel to 1 and set the SEmn bit to 1 (to enable operation).

Sets transmit data to the SIOp register (bits 7 to 0 of the SDRmn register) and wait for a clock from the master.

Starts the target for communication.

Caution Be sure to set transmit data to the SIOp register before the clock from the master is started.

### Figure 15-4. Format of Slave Address Register (SVA)

| Address: F | F0234H | After reset: | 00H R/ | W  |    |    |    |                   |

|------------|--------|--------------|--------|----|----|----|----|-------------------|

| Symbol     | 7      | 6            | 5      | 4  | 3  | 2  | 1  | 0                 |

| SVA        | A6     | A5           | A4     | A3 | A2 | A1 | A0 | 0 <sup>Note</sup> |

Note Bit 0 is fixed to 0.

### (3) SO latch

The SO latch is used to retain the SDA0 pin's output level.

### (4) Wakeup controller

This circuit generates an interrupt request (INTIICA) when the address received by this register matches the address value set to the slave address register (SVA) or when an extension code is received.

### (5) Serial clock counter

This counter counts the serial clocks that are output or input during transmit/receive operations and is used to verify that 8-bit data was transmitted or received.

### (6) Interrupt request signal generator

This circuit controls the generation of interrupt request signals (INTIICA).

An I<sup>2</sup>C interrupt request is generated by the following two triggers.

- Falling edge of eighth or ninth clock of the serial clock (set by the WTIM bit)

- Interrupt request generated when a stop condition is detected (set by the SPIE bit)

Remark

WTIM bit:

Bit 3 of IICA control register 0 (IICCTL0)

SPIE bit:

Bit 4 of IICA control register 0 (IICCTL0)

### (7) Serial clock controller

In master mode, this circuit generates the clock output via the SCL0 pin from a sampling clock.

### (8) Serial clock wait controller

This circuit controls the wait timing.

(9) ACK generator, stop condition detector, start condition detector, and ACK detector These circuits generate and detect each status.

### (10) Data hold time correction circuit

This circuit generates the hold time for data corresponding to the falling edge of the serial clock.

### (11) Start condition generator

This circuit generates a start condition when the STT bit is set to 1. However, in the communication reservation disabled status (IICRSV bit = 1), when the bus is not released (IICBSY bit = 1), start condition requests are ignored and the STCF bit is set to 1.

### (12) Stop condition generator

This circuit generates a stop condition when the SPT bit is set to 1.

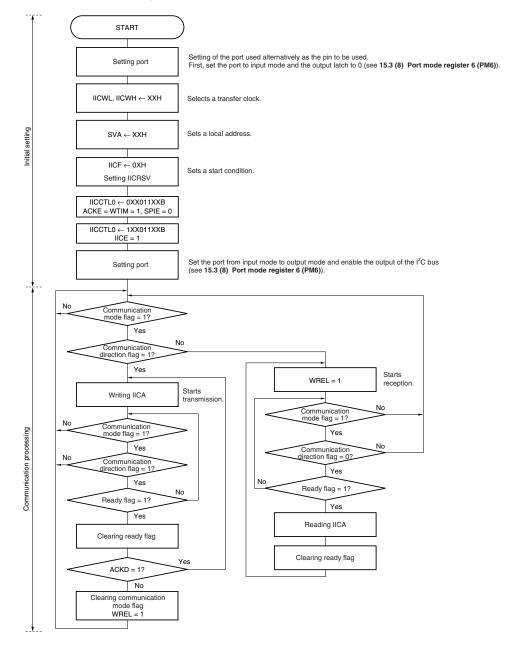

The main processing of the slave operation is explained next.

Start serial interface IICA and wait until communication is enabled. When communication is enabled, execute communication by using the communication mode flag and ready flag (processing of the stop condition and start condition is performed by an interrupt. Here, check the status by using the flags).

The transmission operation is repeated until the master no longer returns ACK. If ACK is not returned from the master, communication is completed.

For reception, the necessary amount of data is received. When communication is completed,  $\overline{ACK}$  is not returned as the next data. After that, the master generates a stop condition or restart condition. Exit from the communication status occurs in this way.

Figure 15-30. Slave Operation Flowchart (1)

**Remark** Conform to the specifications of the product that is in communication, regarding the transmission and reception formats.

RENESAS

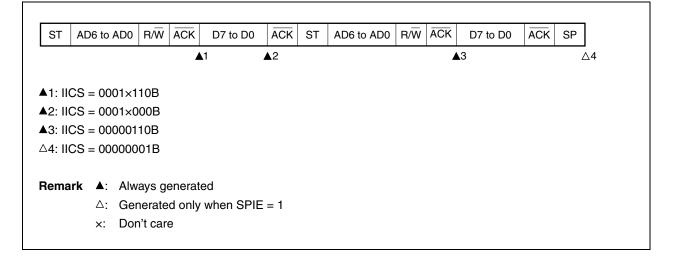

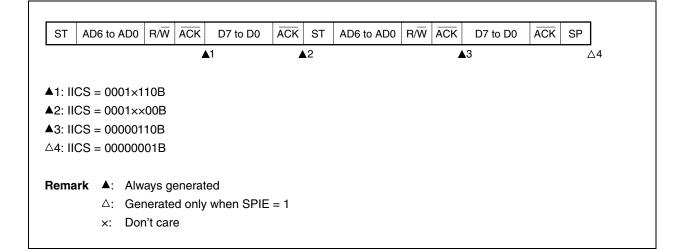

# (d) Start ~ Address ~ Data ~ Start ~ Address ~ Data ~ Stop

### (i) When WTIM = 0 (after restart, does not match address (= not extension code))

(ii) When WTIM = 1 (after restart, does not match address (= not extension code))

The meanings of <1> to <6> in (1) Start condition ~ address ~ data in Figure 15-32 are explained below.

- <R> <1> The start condition trigger is set by the master device (STT = 1) and a start condition (i.e. SCL0 = 1 changes SDA0 from 1 to 0) is generated once the bus data line goes low (SDA0). When the start condition is subsequently detected, the master device enters the master device communication status (MSTS = 1). The master device is ready to communicate once the bus clock line goes low (SCL0 = 0) after the hold time has elapsed.

- <2> The master device writes the address + W (transmission) to the IICA shift register (IICA) and transmits the slave address.

- <R> <3> In the slave device if the address received matches the address (SVA value) of a slave device<sup>Note</sup>, that slave device sends an ACK by hardware to the master device. The ACK is detected by the master device (ACKD = 1) at the rising edge of the 9th clock.

- <R> <4> The master device issues an interrupt (INTIICA: end of address transmission) at the falling edge of the 9th clock. The slave device whose address matched the transmitted slave address sets a wait status (SCL0 = 0) and issues an interrupt (INTIICA: address match)<sup>Note</sup>.

- <5> The master device writes the data to transmit to the IICA register and releases the wait status that it set by the master device.

- <6> If the slave device releases the wait status (WREL = 1), the master device starts transferring data to the slave device.

- **Note** If the transmitted address does not match the address of the slave device, the slave device does not return an ACK to the master device (NACK: SDA0 = 1). The slave device also does not issue the INTIICA interrupt (address match) and does not set a wait status. The master device, however, issues the INTIICA interrupt (end of address transmission) regardless of whether it receives an ACK or NACK.

- Remark <1> to <15> in Figure 15-32 represent the entire procedure for communicating data using the l<sup>2</sup>C bus.

Figure 15-32 (1) Start condition ~ address ~ data shows the processing from <1> to <6>, Figure 15-32

(2) Address ~ data ~ data shows the processing from <3> to <10>, and Figure 15-32 (3) Data ~ data ~ stop condition shows the processing from <7> to <15>.

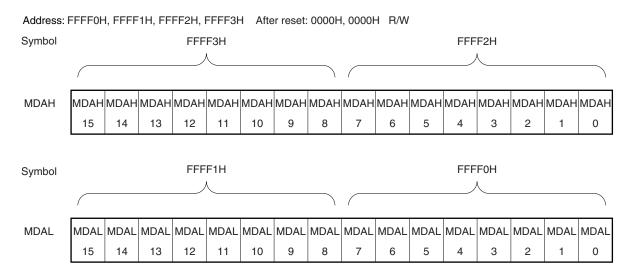

# (1) Multiplication/division data register A (MDAH, MDAL)

The MDAH and MDAL registers set the values that are used for a multiplication or division operation and store the operation result. They set the multiplier and multiplicand data in the multiplication mode, and set the dividend data in the division mode. Furthermore, the operation result (quotient) is stored in the MDAH and MDAL registers in the division mode.

The MDAH and MDAL registers can be set by a 16-bit manipulation instruction. Reset signal generation clears these registers to 0000H.

### Figure 16-2. Format of Multiplication/Division Data Register A (MDAH, MDAL)

- Cautions 1. Do not rewrite the MDAH and MDAL registers values during division operation processing (while the multiplication/division control register (MDUC) is 81H). The operation will be executed in this case, but the operation result will be an undefined value.

- 2. The MDAH and MDAL registers values read during division operation processing (while MDUC is 81H) will not be guaranteed.

The following table shows the functions of the MDAH and MDAL registers during operation execution.

| DIVMODE | Operation Mode      | Setting                        | Operation Result                 |

|---------|---------------------|--------------------------------|----------------------------------|

| 0       | Multiplication mode | MDAH: Multiplier               | _                                |

|         |                     | MDAL: Multiplicand             |                                  |

| 1       | Division mode       | MDAH: Divisor (higher 16 bits) | MDAH: Division result (quotient) |

|         |                     | MDAL: Dividend (lower 16 bits) | Higher 16 bits                   |

|         |                     |                                | MDAL: Division result (quotient) |

|         |                     |                                | Lower 16 bits                    |

Remark DIVMODE: Bit 7 of the multiplication/division control register (MDUC)

# 29.2 Operation List

|            | Mnemonic | Operands           | Bytes | Clocks |        | Operation                     |   | Flag | I  |

|------------|----------|--------------------|-------|--------|--------|-------------------------------|---|------|----|

| Group      |          |                    |       | Note 1 | Note 2 |                               | Z | AC   | CY |

| 8-bit data | MOV      | r, #byte           | 2     | 1      | -      | $r \leftarrow byte$           |   |      |    |

| transfer   |          | saddr, #byte       | 3     | 1      | -      | $(saddr) \leftarrow byte$     |   |      |    |

|            |          | sfr, #byte         | 3     | 1      | -      | $sfr \leftarrow byte$         |   |      |    |

|            |          | !addr16, #byte     | 4     | 1      | -      | $(addr16) \leftarrow byte$    |   |      |    |

|            |          | A, r Note 3        | 1     | 1      | -      | $A \leftarrow r$              |   |      |    |

|            |          | r, A Note 3        | 1     | 1      | -      | $r \leftarrow A$              |   |      |    |

|            |          | A, saddr           | 2     | 1      | -      | $A \gets (saddr)$             |   |      |    |

|            |          | saddr, A           | 2     | 1      | -      | $(saddr) \leftarrow A$        |   |      |    |

|            |          | A, sfr             | 2     | 1      | -      | $A \gets sfr$                 |   |      |    |

|            |          | sfr, A             | 2     | 1      | -      | $sfr \leftarrow A$            |   |      |    |

|            |          | A, !addr16         | 3     | 1      | 4      | $A \leftarrow (addr16)$       |   |      |    |

|            |          | !addr16, A         | 3     | 1      | -      | $(addr16) \leftarrow A$       |   |      |    |

|            |          | PSW, #byte         | 3     | 3      | -      | $PSW \gets byte$              | × | ×    | ×  |

|            |          | A, PSW             | 2     | 1      | -      | $A \leftarrow PSW$            |   |      |    |

|            |          | PSW, A             | 2     | 3      | -      | $PSW \gets A$                 | × | ×    | ×  |

|            |          | ES, #byte          | 2     | 1      | -      | $ES \leftarrow byte$          |   |      |    |

|            |          | ES, saddr          | 3     | 1      | -      | $ES \gets (saddr)$            |   |      |    |

|            |          | A, ES              | 2     | 1      | -      | $A \leftarrow ES$             |   |      |    |

|            |          | ES, A              | 2     | 1      | -      | $ES \gets A$                  |   |      |    |

|            |          | CS, #byte          | 3     | 1      | -      | $CS \gets byte$               |   |      |    |

|            |          | A, CS              | 2     | 1      | -      | $A \leftarrow CS$             |   |      |    |

|            |          | CS, A              | 2     | 1      | -      | $CS \gets A$                  |   |      |    |

|            |          | A, [DE]            | 1     | 1      | 4      | $A \leftarrow (DE)$           |   |      |    |

|            |          | [DE], A            | 1     | 1      | -      | $(DE) \leftarrow A$           |   |      |    |

|            |          | [DE + byte], #byte | 3     | 1      | -      | $(DE + byte) \leftarrow byte$ |   |      |    |

|            |          | A, [DE + byte]     | 2     | 1      | 4      | $A \leftarrow (DE + byte)$    |   |      |    |

|            |          | [DE + byte], A     | 2     | 1      | -      | $(DE + byte) \leftarrow A$    |   |      |    |

|            |          | A, [HL]            | 1     | 1      | 4      | $A \leftarrow (HL)$           |   |      |    |

|            |          | [HL], A            | 1     | 1      | -      | $(HL) \leftarrow A$           |   |      |    |

|            |          | [HL + byte], #byte | 3     | 1      | -      | $(HL + byte) \leftarrow byte$ |   |      |    |

Table 29-5.

Operation List (1/17)

**Notes 1.** When the internal RAM area, SFR area, or extended SFR area is accessed, or for an instruction with no data access.

2. When the program memory area is accessed.

3. Except r = A

**Remarks 1.** One instruction clock cycle is one cycle of the CPU clock (f<sub>CPU</sub>) selected by the system clock control register (CKC).

2. This number of clocks is for when the program is in the internal ROM (flash memory) area. When fetching an instruction from the internal RAM area, the number of clocks is twice the number of clocks plus 3, maximum.

Caution The pins mounted depend on the product. Refer to Caution 2 at the beginning of this chapter.

| Parameter                                                  | Symbol                  | C                                                                    | Conditions                                                 | MIN.            | TYP. | MAX.         | Unit |

|------------------------------------------------------------|-------------------------|----------------------------------------------------------------------|------------------------------------------------------------|-----------------|------|--------------|------|

| SCKp cycle time                                            | <b>t</b> ксү2           | $4.0 V \le V_{DD} \le 5.5 V$ ,                                       | 13.6 MHz < fмск                                            | 10/fмск         |      |              | ns   |

|                                                            |                         | $2.7V{\leq}V_b{\leq}4.0V$                                            | $6.8 \text{ MHz} < f_{MCK} \le 13.6 \text{ MHz}$           | 8/fмск          |      |              | ns   |

|                                                            |                         |                                                                      | fмск ≤6.8 MHz                                              | 6/fмск          |      |              | ns   |

|                                                            |                         | $2.7 \text{ V} \le \text{V}_{\text{DD}} < 4.0 \text{ V},$            | 18.5 MHz < fмск                                            | <b>16/f</b> мск |      |              | ns   |

|                                                            |                         | $2.3V\!\le\!V_{\rm b}\!\le\!2.7V$                                    | 14.8 MHz < fmck $\leq$ 18.5 MHz                            | 14/fмск         |      |              | ns   |

|                                                            |                         |                                                                      | 11.1 MHz < fmck $\leq$ 14.8 MHz                            | 12/fмск         |      |              | ns   |

|                                                            |                         |                                                                      | $7.4 \text{ MHz} < \text{fmck} \le 11.1 \text{ MHz}$       | 10/fмск         |      |              | ns   |

|                                                            | 3.7 MHz < fмск ≤ 7.4 MH |                                                                      | 3.7 MHz < fмск ≤ 7.4 MHz                                   | 8/fмск          |      |              | ns   |

|                                                            |                         |                                                                      | fмск ≤3.7 MHz                                              | 6/fмск          |      |              | ns   |

| SCKp high-/low-level                                       | tкн2,                   | $4.0 V \le V_{DD} \le 5.5 V, 2.0$                                    | $7 V \le V_b \le 4.0 V$                                    | fксү2/2 –       |      |              | ns   |

| width                                                      | tĸl2                    |                                                                      |                                                            | 20              |      |              |      |

|                                                            |                         | $2.7 \text{ V} \le \text{V}_{\text{DD}} < 4.0 \text{ V}, 2$          | $3 \text{ V} \leq \text{V}_{\text{b}} \leq 2.7 \text{ V}$  | fксү2/2 –<br>35 |      |              | ns   |

| SIp setup time<br>(to SCKp↑) <sup>№te 1</sup>              | tsik2                   |                                                                      |                                                            | 90              |      |              | ns   |

| SIp hold time<br>(from SCKp↑) <sup>Note 2</sup>            | tksi2                   |                                                                      |                                                            | 1/fмск + 50     |      |              | ns   |

| Delay time from $\overline{\mathrm{SCKp}} {\downarrow}$ to | tĸso2                   | $4.0 \ V \leq V_{DD} \leq 5.5 \ V, \ 2.7 \ V \leq V_b \leq 4.0 \ V,$ |                                                            |                 |      | 2/fмск + 120 | ns   |

| SOp output <sup>Note 3</sup>                               |                         | $C_b = 30 \text{ pF}, R_b = 1.4 \text{ k}$                           |                                                            |                 |      |              |      |

|                                                            |                         | $2.7~V \le V_{\text{DD}} < 4.0~V, 2$                                 | $3 \text{ V} \leq \text{V}_{\text{b}} \leq 2.7 \text{ V},$ |                 |      | 2/fмск + 230 | ns   |

|                                                            |                         | $C_b = 30 \text{ pF}, R_b = 2.7 \text{ k}$                           | Ω                                                          |                 |      |              |      |

# (7) Communication at different potential (2.5 V, 3 V) (CSI mode) (slave mode, SCKp... external clock input) (T<sub>A</sub> = -40 to +85°C, 2.7 V ≤ V<sub>DD</sub> = EV<sub>DD</sub> ≤ 5.5 V, V<sub>SS</sub> = EV<sub>SS</sub> = AV<sub>SS</sub> = 0 V)

(Notes, Caution and Remarks are given on the next page.)