# E. Renesas Electronics America Inc - UPD78F1007GB-GAH-AX Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | 78K/0R                                                                               |

| Core Size                  | 16-Bit                                                                               |

| Speed                      | 20MHz                                                                                |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                     |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                              |

| Number of I/O              | 50                                                                                   |

| Program Memory Size        | 32KB (32K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 1.5K x 8                                                                             |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                          |

| Data Converters            | A/D 12x10b                                                                           |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 64-LQFP                                                                              |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f1007gb-gah-ax |

|                            |                                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.7 Outline of Functions

## 1. 7. 1 78K0R/KC3-L, 78K0R/KD3-L, 78K0R/KE3-L

|                                 | Item                                                                                         |                                                                                                                                                          |                  |             |                              | 78K           | 0R/K0       | C3-L        |               |             |             |               | 78K         | 0R/KI       | 03-L          | 78K         | OR/KE       | (1/2<br>E3-L  |

|---------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------|------------------------------|---------------|-------------|-------------|---------------|-------------|-------------|---------------|-------------|-------------|---------------|-------------|-------------|---------------|

|                                 |                                                                                              |                                                                                                                                                          | 40-              | pin         |                              |               | 44-         | pin         |               |             | 48-pin      | 1             |             |             |               |             |             |               |

|                                 |                                                                                              | μ PD78F1000                                                                                                                                              | μ PD78F1001      | μ PD78F1002 | μ PD78F1003                  | μ PD78F1000   | μ PD78F1001 | μ PD78F1002 | μ PD78F1003   | μ PD78F1001 | μ PD78F1002 | μ PD78F1003   | μ PD78F1004 | μ PD78F1005 | μ PD78F1006   | μ PD78F1007 | μ PD78F1008 | μ PD78F1009   |

| Internal<br>memory              | Flash memory<br>(KB)                                                                         | 16                                                                                                                                                       | 32               | 48          | 64                           | 16            | 32          | 48          | 64            | 32          | 48          | 64            | 32          | 48          | 64            | 32          | 48          | 64            |

|                                 | RAM (KB)                                                                                     | 1                                                                                                                                                        | 1.5              | 2           | 3/2<br>Note 1                | 1             | 1.5         | 2           | 3/2<br>Note 1 | 1.5         | 2           | 3/2<br>Note 1 | 1.5         | 2           | 3/2<br>Note 1 | 1.5         | 2           | 3/2<br>Note 1 |

| Memory spac                     | e                                                                                            | 1 ME                                                                                                                                                     | }                |             |                              |               |             |             |               |             |             |               |             |             |               |             |             |               |

| Main system<br>clock            | High-speed system<br>clock                                                                   |                                                                                                                                                          | -                |             | nic) os<br>5 = 2.7           |               |             |             |               | •           |             | •             | ıt (EX      | CLK)        |               |             |             |               |

|                                 | Internal high-speed oscillation clock                                                        |                                                                                                                                                          | nal os<br>Iz (TY |             | on<br>MHz                    | (TYP.)        | ): Vdd      | = 1.8       | to 5.5        | v           |             |               |             |             |               |             |             |               |

|                                 | 20 MHz internal high-<br>speed oscillation<br>clock                                          |                                                                                                                                                          | nal os<br>Hz (T  |             | on<br>Vdd =                  | 2.7 to        | 5.5 V       |             |               |             |             |               |             |             |               |             |             |               |

| Subsystem cl                    | <ul> <li>XT1 (crystal) oscillation</li> <li>32.768 kHz (TYP.): VDD = 1.8 to 5.5 V</li> </ul> |                                                                                                                                                          |                  |             |                              |               |             |             |               |             |             |               |             |             |               |             |             |               |

| Internal low-s<br>(dedicated to | peed oscillation clock<br>WDT)                                                               | Internal oscillation<br>30 kHz (TYP.): VDD = 1.8 to 5.5 V                                                                                                |                  |             |                              |               |             |             |               |             |             |               |             |             |               |             |             |               |

| General-purp                    | ose register                                                                                 | 8 bits $\times$ 32 registers (8 bits $\times$ 8 registers $\times$ 4 banks)                                                                              |                  |             |                              |               |             |             |               |             |             |               |             |             |               |             |             |               |

| Minimum inst                    | ruction execution time                                                                       | 0.05                                                                                                                                                     | <i>μ</i> s (Η    | igh-sp      | eed s                        | ystem         | clock       | : fмx =     | 20 M          | Hz op       | eratio      | า)            |             |             |               |             |             |               |

|                                 |                                                                                              |                                                                                                                                                          |                  | _           |                              | 61 <i>µ</i> : | s (Sub      | syste       | m cloo        | k: fsue     | 3 = 32      | .768 k        | Hz op       | eratio      | n)            |             |             |               |

| Instruction se                  | t                                                                                            | • Mu                                                                                                                                                     | ultiplic         | ation       | n, 16-b<br>(8 bits<br>on (Se | ×8 bi         | ts)         | , and       | Boole         | an op       | eratior     | n), etc       |             |             |               |             |             |               |

| I/O port                        | Total                                                                                        |                                                                                                                                                          | 3                | 33          |                              |               | 3           | 37          |               |             | 41          |               |             | 45          |               |             | 55          |               |

|                                 | CMOS I/O                                                                                     |                                                                                                                                                          | 3                | 31          |                              |               | 3           | 33          |               |             | 34          |               |             | 38          |               |             | 48          |               |

|                                 | CMOS input                                                                                   |                                                                                                                                                          |                  | 2           |                              |               |             | 4           |               |             | 4           |               |             | 4           |               |             | 4           |               |

|                                 | CMOS output                                                                                  |                                                                                                                                                          |                  | _           |                              |               | -           |             |               | 1           |             |               | 1           |             |               | 1           |             |               |

|                                 | N-ch open-drain I/O<br>(6 V tolerance)                                                       |                                                                                                                                                          |                  | _           |                              |               |             | _           |               |             | 2           |               |             | 2           |               |             | 2           |               |

| Timer                           | 16-bit timer                                                                                 |                                                                                                                                                          |                  |             |                              |               |             |             | 8             | chann       | els         |               |             |             |               |             |             |               |

|                                 | Watchdog timer                                                                               |                                                                                                                                                          |                  |             |                              |               |             |             | 1             | chanı       | nel         |               |             |             |               |             |             |               |

|                                 | Real-time counter (RTC)                                                                      |                                                                                                                                                          | -                | -           |                              |               |             |             |               |             | 1           | chanr         | iel         |             |               |             |             |               |

|                                 | Timer output                                                                                 | 6 8<br>(PWM outputs: 6 <sup>Note 2</sup> ) (PWM outputs: 7 <sup>Note 2</sup> )                                                                           |                  |             |                              |               |             |             |               |             |             |               |             |             |               |             |             |               |

|                                 | RTC output                                                                                   | <ul> <li>2</li> <li>1 Hz (subsystem clock: fsuB = 32.768 kHz)</li> <li>512 Hz, 16.384 kHz, or 32.768 kHz (subsystem clock: fsuB = 32.768 kHz)</li> </ul> |                  |             |                              |               |             |             |               |             |             |               |             |             |               |             |             |               |

Notes 1. This is 2 KB when the self-programming function is used.

2. The number of outputs varies, depending on the setting.

## 2.1.1 78K0R/KC3-L (40-pin products)

## (1) Port functions (1/2): 78K0R/KC3-L (40-pin)

| Function Name       | I/O | Function                                                                                                                                                                   | After Reset           | Alternate Function        |

|---------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------------|

| P10                 | I/O | Port 1.                                                                                                                                                                    | Input port            | TI02/TO02                 |

| P11                 |     | 4-bit I/O port.                                                                                                                                                            |                       | TI03/TO03                 |

| P12                 |     | Input/output can be specified in 1-bit units.<br>Use of an on-chip pull-up resistor can be specified by a software                                                         |                       | TI04/TO04                 |

| P13                 |     | setting.                                                                                                                                                                   |                       | TI05/TO05                 |

| P20 to P27          | I/O | Port 2.<br>8-bit I/O port.<br>Input/output can be specified in 1-bit units.                                                                                                | Digital input<br>port | ANI0 to ANI7              |

| P30                 | I/O | Port 3.<br>3-bit I/O port.                                                                                                                                                 | Input port            | SO10/TxD1                 |

| P31                 |     | Input of P31 and P32 can be set to TTL buffer.<br>Output of P30 to P32 can be set to N-ch open-drain output ( $V_{DD}$ tolerance).                                         |                       | SI10/RxD1/SDA10/<br>INTP1 |

| P32                 |     | Input/output can be specified in 1-bit units.<br>Use of an on-chip pull-up resistor can be specified by a software<br>setting.                                             |                       | SCK10/SCL10/<br>INTP2     |

| P40 <sup>Note</sup> | I/O | Port 4.<br>2-bit I/O port.                                                                                                                                                 | Input port            | TOOL0                     |

| P41                 |     | Input/output can be specified in 1-bit units.<br>Use of an on-chip pull-up resistor can be specified by a software setting.                                                |                       | TOOL1                     |

| P50                 | I/O | Port 5.                                                                                                                                                                    | Input port            | TI06/TO06                 |

| P51                 |     | <ul><li>2-bit I/O port.</li><li>Input/output can be specified in 1-bit units.</li><li>Use of an on-chip pull-up resistor can be specified by a software setting.</li></ul> |                       | TI07/TO07                 |

| P70                 | I/O | Port 7.                                                                                                                                                                    | Input port            | KR0/SO01/INTP4            |

| P71                 | 1   | 6-bit I/O port.                                                                                                                                                            |                       | KR1/SI01/INTP5            |

| P72                 |     | Input of P71, P72, P74, and P75 can be set to TTL buffer.<br>Output of P70, P72, P73, and P75 can be set to N-ch open-drain                                                |                       | KR2/SCK01/INTP6           |

| P73                 |     | output (VDD tolerance).                                                                                                                                                    |                       | KR3/SO00/TxD0             |

| P74                 |     | Input/output can be specified in 1-bit units.                                                                                                                              |                       | KR4/SI00/RxD0             |

| P75                 |     | Use of an on-chip pull-up resistor can be specified by a software setting.                                                                                                 |                       | KR5/SCK00                 |

Note If on-chip debugging is enabled by using an option byte, be sure to pull up the P40/TOOL0 pin externally.

## 2.2.16 FLMD0

This is a pin for setting flash memory programming mode. Perform either of the following processing.

## (a) In normal operation mode

It is recommended to leave this pin open during normal operation.

The FLMD0 pin must always be kept at the Vss level before reset release but does not have to be pulled down externally because it is internally pulled down by reset. However, pulling it down must be kept selected (i.e., FLMDPUP = "0", default value) by using bit 7 (FLMDPUP) of the background event control register (BECTL) (see **26.5 (1) Back ground event control register**). To pull it down externally, use a resistor of 200 k $\Omega$  or smaller. Self programming and the rewriting of flash memory with the programmer can be prohibited using hardware, by directly connecting this pin to the Vss pin.

## (b) In self programming mode

It is recommended to leave this pin open when using the self programming function. To pull it down externally, use a resistor of 100 k $\Omega$  to 200 k $\Omega$ .

In the self programming mode, the setting is switched to pull up in the self programming library.

## (c) In flash memory programming mode

Directly connect this pin to a flash memory programmer when data is written by the flash memory programmer. This supplies a writing voltage of the  $V_{DD}$  level to the FLMD0 pin.

The FLMD0 pin does not have to be pulled down externally because it is internally pulled down by reset. To pull it down externally, use a resistor of 1 k $\Omega$  to 200 k $\Omega$ .

## 3.3 Pin I/O Circuits and Recommended Connection of Unused Pins

## 3.3.1 78K0R/KF3-L

Table 3-3 shows the types of pin I/O circuits and the recommended connections of unused pins. For I/O Circuit Type, see Figure 3-1. Pin I/O Circuit List.

| Pin Name                             | I/O Circuit Type | I/O | Recommended Connection of Unused Pins                                                                                                                                                                                                                                                     |

|--------------------------------------|------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P02/SO10/TxD1                        | 5-AG             | I/O | Input: Independently connect to EV_DD0 or EV_SS0 via a resistor.                                                                                                                                                                                                                          |

| P03/SI10/RxD1/SDA10                  | 5-AN             |     | Output: Leave open.                                                                                                                                                                                                                                                                       |

| P04/SCK10/SCL10                      |                  |     | <when n-ch="" open-drain=""><br/>Set the port output latch to 0 and leave open with low level out put.</when>                                                                                                                                                                             |

| P05/TI05/TO05                        | 8-R              | -   | Input: Independently connect to EV <sub>DD0</sub> or EV <sub>SS0</sub> via a resistor.                                                                                                                                                                                                    |

| P06/TI06/TO06                        |                  |     | Output: Leave open.                                                                                                                                                                                                                                                                       |

| P10/SCK00                            | 5-AN             |     | Input: Independently connect to EV <sub>DD0</sub> or EV <sub>SS0</sub> via a resistor.<br>Output: Leave open.                                                                                                                                                                             |

|                                      |                  |     | <when n-ch="" open-drain=""><br/>Set the port output latch to 0 and leave open with low level out put.</when>                                                                                                                                                                             |

| P11/SI00/RxD0                        |                  |     | Input: Independently connect to EV <sub>DD0</sub> or EV <sub>SS0</sub> via a resistor.<br>Output: Leave open.                                                                                                                                                                             |

| P12/SO00/TxD0                        | 5-AG             |     | Input: Independently connect to EV <sub>DD0</sub> or EV <sub>SS0</sub> via a resistor.<br>Output: Leave open.                                                                                                                                                                             |

|                                      |                  |     | <when n-ch="" open-drain=""><br/>Set the port output latch to 0 and leave open with low level out put.</when>                                                                                                                                                                             |

| P13/TxD3                             |                  |     | Input: Independently connect to EV <sub>DD0</sub> or EV <sub>SS0</sub> via a resistor.<br>Output: Leave open.                                                                                                                                                                             |

| P14/RxD3                             | 8-R              |     | Input: Independently connect to EV <sub>DD0</sub> or EV <sub>SS0</sub> via a resistor.                                                                                                                                                                                                    |

| P15/RTCDIV/RTCCL                     | 5-AG             |     | Output: Leave open.                                                                                                                                                                                                                                                                       |

| P16/TI01/TO01/INTP5                  | 8-R              |     |                                                                                                                                                                                                                                                                                           |

| P17/TI02/TO02                        |                  |     |                                                                                                                                                                                                                                                                                           |

| P20/ANI0 to P27/ANI7 <sup>Note</sup> | 11-G             |     | Input: Independently connect to AVREF or AVss via a resistor.<br>Output: Leave open.                                                                                                                                                                                                      |

| P30/RTC1HZ/INTP3                     | 8-R              |     | Input: Independently connect to EV <sub>DD0</sub> or EV <sub>SS0</sub> via a resistor.<br>Output: Leave open.                                                                                                                                                                             |

| P31/TI03/TO03/INTP4                  |                  |     | · · ·                                                                                                                                                                                                                                                                                     |

| P40/TOOL0                            |                  |     | <when debugging="" enabled="" is="" on-chip=""><br/>Pull this pin up (pulling it down is prohibited).<br/><when debugging="" disabled="" is="" on-chip=""><br/>Input: Independently connect to EV<sub>DD0</sub> or EV<sub>SS0</sub> via a resistor.<br/>Output: Leave open.</when></when> |

#### Table 3-3. Connection of Unused Pins (1/3)

Note P20/ANI0 to P27/ANI7 are set in the digital input port mode after release of reset.

### 4.2.5 Extended special function registers (2nd SFRs: 2nd Special Function Registers)

Unlike a general-purpose register, each extended SFR (2nd SFR) has a special function.

Extended SFRs are allocated to the F0000H to F07FFH area. SFRs other than those in the SFR area (FFF00H to FFFFFH) are allocated to this area. An instruction that accesses the extended SFR area, however, is 1 byte longer than an instruction that accesses the SFR area.

Extended SFRs can be manipulated like general-purpose registers, using operation, transfer, and bit manipulation instructions. The manipulable bit units, 1, 8, and 16, depend on the SFR type.

Each manipulation bit unit can be specified as follows.

• 1-bit manipulation

Describe the symbol reserved by the assembler for the 1-bit manipulation instruction operand (laddr16.bit). This manipulation can also be specified with an address.

• 8-bit manipulation

Describe the symbol reserved by the assembler for the 8-bit manipulation instruction operand (!addr16). This manipulation can also be specified with an address.

• 16-bit manipulation

Describe the symbol reserved by the assembler for the 16-bit manipulation instruction operand (!addr16). When specifying an address, describe an even address.

Table 4-6 gives a list of the extended SFRs. The meanings of items in the table are as follows.

Symbol

Symbol indicating the address of an extended SFR. It is a reserved word in the RA78K0R, and is defined as an sfr variable using the #pragma sfr directive in the CC78K0R. When using the RA78K0R, ID78K0R-QB, and SM+ for 78K0R, symbols can be written as an instruction operand.

• R/W

Indicates whether the corresponding extended SFR can be read or written.

R/W: Read/write enable

- R: Read only

- W: Write only

- Manipulable bit units

"√" indicates the manipulable bit unit (1, 8, or 16). "−" indicates a bit unit for which manipulation is not possible.

After reset

Indicates each register status upon reset signal generation.

### Caution Do not access addresses to which extended SFRs are not assigned.

Remark For SFRs in the SFR area, see 4.2.4 Special function registers (SFRs).

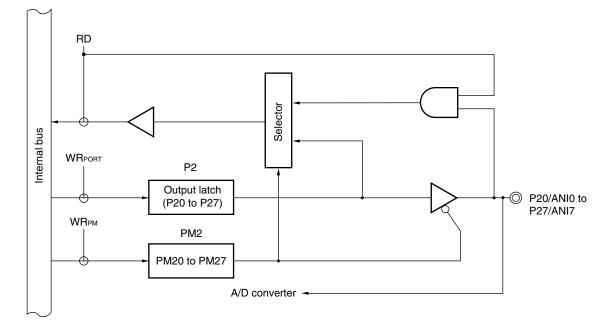

Figure 5-5. Block Diagram of P20 to P27

P2: Port register 2

PM2: Port mode register 2

RD: Read signal

WR××: Write signal

## 5.2.9 Port 8

|                          | 78K0R/KC3-L<br>(µPD78F100y: y = 0 to 3) |        |              |              |              |  | 78K0R/KC3-L (48-pin)<br>(μPD78F100y: y = 1 to 3) | 78K0R/KD3-L<br>(μPD78F100y: y = 4 to 6) | 78K0R/KE3-L<br>(μPD78F100y: y = 7 to 9) |

|--------------------------|-----------------------------------------|--------|--------------|--------------|--------------|--|--------------------------------------------------|-----------------------------------------|-----------------------------------------|

|                          | 40-pin                                  | 44-pin |              |              |              |  |                                                  |                                         |                                         |

| P80/CMP0P/<br>INTP3/PGAI | 1                                       |        | $\checkmark$ | $\checkmark$ | $\checkmark$ |  |                                                  |                                         |                                         |

| P81/CMP0M                | -                                       | V      | $\checkmark$ | $\checkmark$ |              |  |                                                  |                                         |                                         |

| P82/CMP1P/<br>INTP7      | _                                       | V      | $\checkmark$ | $\checkmark$ | V            |  |                                                  |                                         |                                         |

| P83/CMP1M                | -                                       | V      | $\checkmark$ | $\checkmark$ |              |  |                                                  |                                         |                                         |

### **Remark** $\sqrt{:}$ Mounted

Port 8 is an I/O port with an output latch. Port 8 can be set to the input mode or output mode in 1-bit units using port mode register 8 (PM8).

Inputs to the P80 to P83 pins must be enabled or disabled in 1-bit units using port input mode register 8 (PIM8).

This port can also be used for an input voltage on the (+) sides of comparators 0 and 1, an input voltage on the (-) sides of comparators 0 and 1, an external interrupt request input, and a programmable gain amplifier input.

Reset signal generation sets port 8 to analog input mode.

Figures 5-19 to 5-21 show block diagrams of port 8.

Caution In the case of the 78K0R/KC3-L (40-pin), be sure to clear bit2 of the PM8 register to "0" after the reset release.

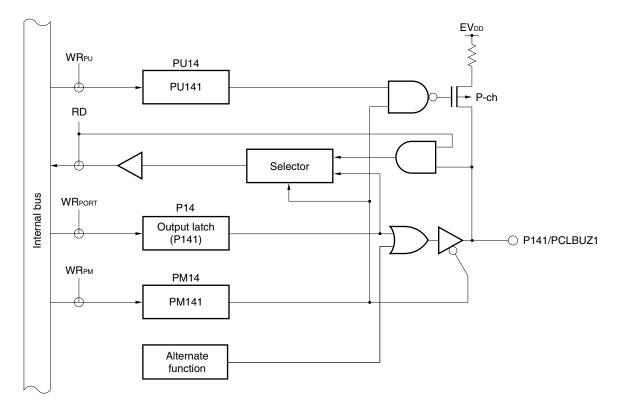

Figure 5-26. Block Diagram of P141

- P14: Port register 14

- PU14: Pull-up resistor option register 14

- PM14: Port mode register 14

- RD: Read signal

- WR××: Write signal

| Symbol | 7    | 6        | 5          | 4           | 3      | 2           | 1           | 0         | Address | After reset | R/W    |

|--------|------|----------|------------|-------------|--------|-------------|-------------|-----------|---------|-------------|--------|

| PM0    | 1    | 1        | 1          | 1           | 1      | 1           | PM01        | PM00      | FFF20H  | FFH         | R/W    |

|        |      | ī        | r          | r           | r      | T           | r           | 1         |         |             |        |

| PM1    | 1    | 1        | 1          | 1           | PM13   | PM12        | PM11        | PM10      | FFF21H  | FFH         | R/W    |

|        |      |          |            |             |        |             |             |           |         |             |        |

| PM2    | PM27 | PM26     | PM25       | PM24        | PM23   | PM22        | PM21        | PM20      | FFF22H  | FFH         | R/W    |

| PM3    | 1    | 1        | 1          | 1           | 1      | PM32        | PM31        | PM30      | FFF23H  | FFH         | R/W    |

| 1 1010 |      | 1        | I          | 1           | 1      | 1 10102     | 1 10101     | 1 1000    | 1112011 |             | 11/ VV |

| PM4    | 1    | 1        | 1          | 1           | 1      | 1           | PM41        | PM40      | FFF24H  | FFH         | R/W    |

|        |      |          |            |             |        |             |             |           |         |             |        |

| PM5    | 1    | 1        | 1          | 1           | 1      | PM52        | PM51        | PM50      | FFF25H  | FFH         | R/W    |

|        | -    | ī        | T          | r           | r      | T           | r           | 1         |         |             |        |

| PM6    | 1    | 1        | 1          | 1           | 1      | 1           | PM61        | PM60      | FFF26H  | FFH         | R/W    |

|        |      |          |            |             |        |             |             |           |         |             |        |

| PM7    | PM77 | PM76     | PM75       | PM74        | PM73   | PM72        | PM71        | PM70      | FFF27H  | FFH         | R/W    |

| PM8    | 1    | 1        | 1          | 1           | PM83   | PM82        | PM81        | PM80      | FFF28H  | FFH         | R/W    |

| I WO   |      |          | I          | 1           | 1 1000 | 1 10102     |             | 1 1000    | 1112011 |             | 11/ VV |

| PM12   | 1    | 1        | 1          | 1           | 1      | 1           | 1           | PM120     | FFF2CH  | FFH         | R/W    |

|        |      |          | I          | I           | l      | l           | I           |           |         |             |        |

| PM15   | 1    | 1        | 1          | 1           | 1      | PM152       | PM151       | PM150     | FFF2FH  | FFH         | R/W    |

|        |      | I        |            |             |        |             |             |           |         |             |        |

|        | PMmn |          |            |             |        | Pmn pin I/C |             |           |         |             |        |

|        |      | <u> </u> |            |             |        | n = 0 to 8, | 12, 15; n = | = 0 to 7) |         |             |        |

|        | 0    |          | ode (outpu |             | 1)     |             |             |           |         |             |        |

|        | 1    | Input mo | de (output | butter off) |        |             |             |           |         |             |        |

### Figure 5-30. Format of Port Mode Register (78K0R/KD3-L)

Caution Be sure to set bits 2 to 7 of the PM0 register, bits 4 to 7 of the PM1 register, bits 3 to 7 of the PM3 register, bits 2 to 7 of the PM4 register, bits 3 to 7 of the PM5 register, bits 2 to 7 of the PM6 register, bits 4 to 7 of the PM8 register, bits 1 to 7 of the PM12 register, and bits 3 to 7 of the PM15 register to 1.

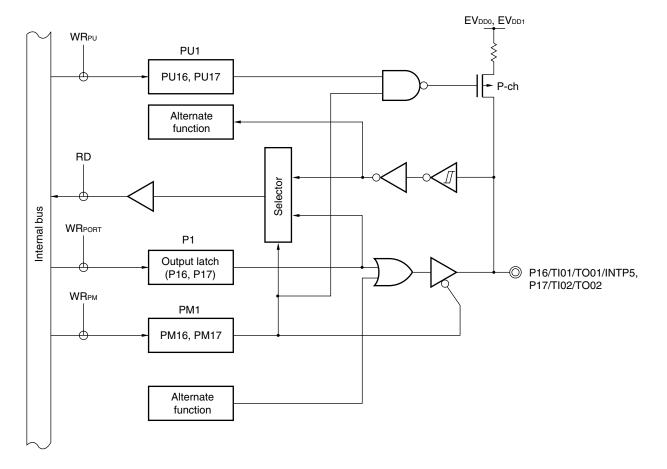

Figure 6-12. Block Diagram of P16 and P17

- P1: Port register 1

- PU1: Pull-up resistor option register 1

- PM1: Port mode register 1

- RD: Read signal

- WR××: Write signal

| Timer operation mode     | Operation when TSmn = 1 is set                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interval timer mode      | No operation is carried out from start trigger detection (TSmn=1) until count clock generation.                                                                                                                                                                                                                                                                                                                                           |

|                          | The first count clock loads the value of the TDRmn register to the TCRmn register and the subsequent count clock performs count down operation (see <b>8.3 (6) (a) Start timing in interval timer mode</b> ).                                                                                                                                                                                                                             |

| Event counter mode       | <ul> <li>Writing 1 to the TSmn bit loads the value of the TDRmn register to the TCRmn register.</li> <li>The subsequent count clock performs count down operation.</li> <li>The external trigger detection selected by the STSmn2 to STSmn0 bits in the TMRmn register does not start count operation (see 8.3 (6) (b) Start timing in event counter mode).</li> </ul>                                                                    |

| Capture mode             | No operation is carried out from start trigger detection until count clock generation.<br>The first count clock loads 0000H to the TCRmn register and the subsequent count clock performs count up operation (see <b>8.3 (6) (c) Start timing in capture</b>                                                                                                                                                                              |

| One-count mode           | mode).         The waiting-for-start-trigger state is entered by writing 1 to the TSmn bit while the timer is stopped (TEmn = 0).         No operation is carried out from start trigger detection until count clock generation.         The first count clock loads the value of the TDRmn register to the TCRmn register and the subsequent count clock performs count down operation (see 8.3 (6) (d) Start timing in one-count mode). |

| Capture & one-count mode | The waiting-for-start-trigger state is entered by writing 1 to the TSmn bit while the timer is stopped (TEmn = 0).<br>No operation is carried out from start trigger detection until count clock generation.<br>The first count clock loads 0000H to the TCRmn register and the subsequent count clock performs count up operation (see 8.3 (6) (e) Start timing in capture & one-count mode).                                            |

## Table 8-4. Operations from Count Operation Enabled State to Timer/counter Register mn (TCRmn) Count Start

Operation is resumed.

|                     | Software Operation                                                                                                                                                                                                                                                                                                                                                                                                                              | Hardware Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation<br>start  | (Sets the TOEmp and TOEmq (slave) bits to 1 only when<br>resuming operation.)<br>The TSmn bit (master), and TSmp and TSmq (slave) bits<br>of timer channel start register m (TSm) are set to 1 at the<br>same time.<br>The TSmn, TSmp, and TSmq bits automatically return<br>to 0 because they are trigger bits.                                                                                                                                | TEmn = 1, TEmp, TEmq = 1<br>When the master channel starts counting, INTTMmn is<br>generated. Triggered by this interrupt, the slave<br>channel also starts counting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| During<br>operation | Set values of the TMRmn, TMRmp, TMRmq registers,<br>TOMmn, TOMmp, TOMmq, TOLmn, TOLmp, and TOLmq<br>bits cannot be changed.<br>Set values of the TDRmn, TDRmp, and TDRmq registers<br>can be changed after INTTMmn of the master channel is<br>generated.<br>The TCRmn, TCRmp, and TCRmq registers can always<br>be read.<br>The TSRmn, TSRmp, and TSRmq registers are not used.<br>Set values of the TOm and TOEm registers can be<br>changed. | The counter of the master channel loads the TDRmn<br>register value to timer/counter register mn (TCRmn) and<br>counts down. When the count value reaches TCRmn =<br>0000H, INTTMmn output is generated. At the same time,<br>the value of the TDRmn register is loaded to the TCRmn<br>register, and the counter starts counting down again.<br>At the slave channel 1, the values of the TDRmp register<br>are transferred to the TCRmp register, triggered by<br>INTTMmn of the master channel, and the counter starts<br>counting down. The output levels of TOmp become active<br>one count clock after generation of the INTTMmn output<br>from the master channel. It becomes inactive when<br>TCRmp = 0000H, and the counting operation is stopped.<br>At the slave channel 2, the values of the TDRmq register<br>are transferred to TCRmq regster, triggered by INTTMmn<br>of the master channel, and the counter starts counting<br>down. The output levels of TOmg become active one cou-<br>clock after generation of the INTTMmn output from the<br>master channel. It becomes inactive when TCRmq =<br>0000H, and the counter starts counting<br>down. The output levels of TOmg become active one cou-<br>clock after generation of the INTTMmn output from the<br>master channel. It becomes inactive when TCRmq =<br>0000H, and the counting operation is stopped.<br>After that, the above operation is repeated. |

| Operation<br>stop   | The TTmn bit (master), TTmp, and TTmq (slave) bits are<br>set to 1 at the same time.<br>The TTmn, TTmp, and TTmq bits automatically return<br>to 0 because they are trigger bits.                                                                                                                                                                                                                                                               | TEmn, TEmp, TEmq = 0, and count operation stops.<br>The TCRmn, TCRmp, and TCRmq registers hold count<br>value and stop.<br>The TOmp and TOmq output are not initialized but hold<br>current status.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                     | The TOEmp and TOEmq bits of slave channels are cleared to 0 and value is set to the TOmp and TOmq bits.                                                                                                                                                                                                                                                                                                                                         | The TOmp and TOmq pins output the TOmp and TOmq set levels.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| TAU<br>stop         | To hold the TOmp and TOmq pin output levels<br>Clears the TOmp and TOmq bits to 0 after<br>the value to be held is set to the port register.<br>When holding the TOmp and TOmq pin output levels are<br>not necessary<br>Switches the port mode register to input mode.                                                                                                                                                                         | The TOmp and TOmq pin output levels are held by port<br>function.<br>The TOmp and TOmq pin output levels go into Hi-Z outp<br>state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                     | The TAU0EN and TAU1EN bits of the PER0 and PER2<br>registers are cleared to 0. Note                                                                                                                                                                                                                                                                                                                                                             | Power-off status<br>All circuits are initialized and SFR of each channel is<br>also initialized.<br>(The TOmp and TOmq bits are cleared to 0 and the<br>TOmp and TOmq pins are set to port mode.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

## Figure 8-75. Operation Procedure When Multiple PWM Output Function Is Used (2/3)

Note 78K0R/KC3-L, 78K0R/KD3-L, 78K0R/KE3-L: TAU0EN bit of the PER2 register 78K0R/KF3-L, 78K0R/KG3-L:

TAU0EN or TAU1EN bit of the PER0 register

(Remark is listed on the next page.)

## 10.2 Configurations of Comparator and Programmable Gain Amplifier

The comparators and programmable gain amplifiers consist of the following hardware.

## Table 10-1. Configurations of Comparator and Programmable Gain Amplifier

| Item              | Configuration                                                                  |

|-------------------|--------------------------------------------------------------------------------|

| Control registers | Peripheral enable register 1 (PER1)                                            |

|                   | Programmable gain amplifier control register (OAM)                             |

|                   | Comparator 0 and 1 control registers (C0CTL, C1CTL)                            |

|                   | Comparator 0 and 1 internal reference voltage setting registers (C0RVM, C1RVM) |

|                   | Port input mode register 8 (PIM8)                                              |

|                   | Port mode register 8 (PM8)                                                     |

## 10.3 Registers Controlling Comparators and Programmable Gain Amplifiers

The comparators and programmable gain amplifiers use the following eight registers.

- Peripheral enable register 1 (PER1)

- Programmable gain amplifier control register (OAM)

- Comparator 0 and 1 control registers (C0CTL, C1CTL)

- Comparator 0 and 1 internal reference voltage setting registers (C0RVM, C1RVM)

- Port input mode register 8 (PIM8)

- Port mode register 8 (PM8)

## 14.1 Functions of Serial Array Unit

Each serial interface supported by the 78K0R/Kx3-L has the following features.

## 14.1.1 3-wire serial I/O (CSI00, CSI01, CSI10, CSI20, CSI40, CSI41)

Data is transmitted or received in synchronization with the serial clock ( $\overline{SCK}$ ) output from the master channel.

3-wire serial communication is clocked communication performed by using three communication lines: one for the serial clock ( $\overline{SCK}$ ), one for transmitting serial data (SO), one for receiving serial data (SI).

For details about the settings, see 14.5 Operation of 3-Wire Serial I/O (CSI00, CSI01, CSI10, CSI20, CSI40, CSI41) Communication.

[Data transmission/reception]

- Data length of 7 or 8 bits

- Phase control of transmit/receive data

- MSB/LSB first selectable

- Level setting of transmit/receive data

[Clock control]

- Master/slave selection

- Phase control of I/O clock

- Setting of transfer period by prescaler and internal counter of each channel

- Maximum transfer rate

- During master communication: Max. fcLk/4, during slave communication: Max. fMck/6 Note

[Interrupt function]

• Transfer end interrupt/buffer empty interrupt

[Error detection flag]

- Overrun error

- Note Use the clocks within a range satisfying the SCK cycle time (tκcr) characteristics (see CHAPTER 30 ELECTRICAL SPECIFICATIONS (78K0R/KC3-L, 78K0R/KD3-L, 78K0R/KE3-L) or CHAPTER 31 ELECTRICAL SPECIFICATIONS (78K0R/KF3-L, 78K0R/KG3-L)).

## 14.1.3 Simplified I<sup>2</sup>C (IIC10, IIC20)

This is a clocked communication function to communicate with two or more devices by using two lines: serial clock (SCL) and serial data (SDA). This simplified I<sup>2</sup>C is designed for single communication with a device such as EEPROM, flash memory, or A/D converter, and therefore, it functions only as a master.

Make sure by using software, as well as operating the control registers, that the AC specifications of the start and stop conditions are observed.

For details about the settings, see 14.8 Operation of Simplified I<sup>2</sup>C (IIC10, IIC20)

[Data transmission/reception]

- Master transmission, master reception (only master function with a single master)

- ACK output function<sup>Note</sup> and ACK detection function

- Data length of 8 bits (When an address is transmitted, the address is specified by the higher 7 bits, and the least significant bit is used for R/W control.)

- Manual generation of start condition and stop condition

[Interrupt function]

- Transfer end interrupt

- [Error detection flag]

- Parity error (ACK error)

- \* [Functions not supported by simplified I<sup>2</sup>C]

- Slave transmission, slave reception

- Arbitration loss detection function

- Wait detection functions

- **Note** When receiving the last data, ACK will not be output if 0 is written to the SOEmn bit (serial output enable register m (SOEm)) and serial communication data output is stopped. See the processing flow in **14.8.3 (2)** for details.

**Remark** To use an I<sup>2</sup>C bus of full function, see **CHAPTER 15 SERIAL INTERFACE IICA**.

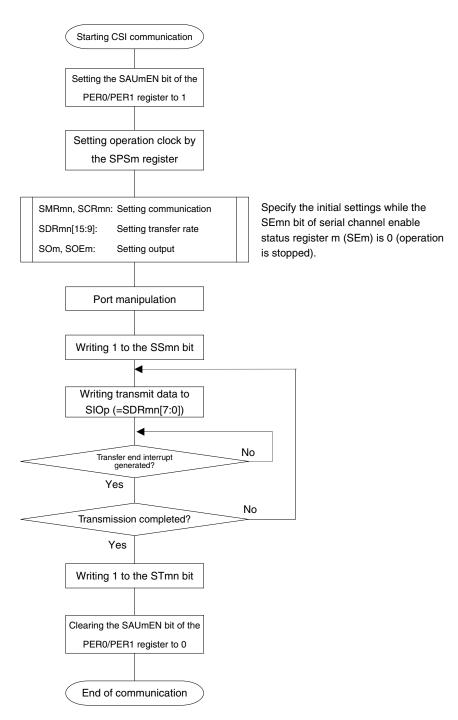

#### Figure 14-33. Flowchart of Master Transmission (in Single-Transmission Mode)

Caution After setting the SAUmEN bit of peripheral enable register 0/1 (PER0/PER1) to 1, be sure to set serial clock select register m (SPSm) after 4 or more f<sub>CLK</sub> clocks have elapsed.

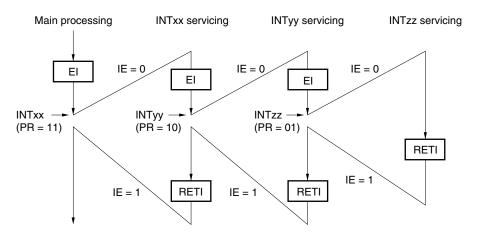

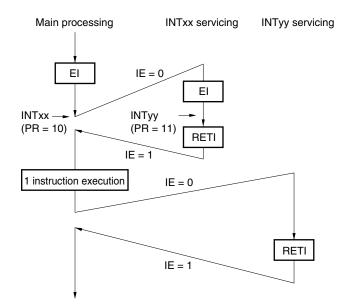

#### Figure 18-15. Examples of Multiple Interrupt Servicing (1/2)

#### Example 1. Multiple interrupt servicing occurs twice

During servicing of interrupt INTxx, two interrupt requests, INTyy and INTzz, are acknowledged, and multiple interrupt servicing takes place. Before each interrupt request is acknowledged, the El instruction must always be issued to enable interrupt request acknowledgment.

#### Example 2. Multiple interrupt servicing does not occur due to priority control

Interrupt request INTyy issued during servicing of interrupt INTxx is not acknowledged because its priority is lower than that of INTxx, and multiple interrupt servicing does not take place. The INTyy interrupt request is held pending, and is acknowledged following execution of one main processing instruction.

PR = 00: Specify level 0 with  $\times$  PR1 $\times$  = 0,  $\times$  PR0 $\times$  = 0 (higher priority level)

- PR = 01: Specify level 1 with  $\times$  PR1 $\times$  = 0,  $\times$  PR0 $\times$  = 1

- PR = 10: Specify level 2 with  $\times$  PR1 $\times$  = 1,  $\times$  PR0 $\times$  = 0

- PR = 11: Specify level 3 with  $\times$  PR1 $\times$  = 1,  $\times$  PR0 $\times$  = 1 (lower priority level)

- IE = 0: Interrupt request acknowledgment is disabled

- IE = 1: Interrupt request acknowledgment is enabled.

Caution The pins mounted depend on the product. Refer to Caution 2 at the beginning of this chapter.

## **30.6 Peripheral Functions Characteristics**

#### 30.6.1 Serial array unit

## (1) During communication at same potential (UART mode) (dedicated baud rate generator output) ( $T_A = -40$ to $+85^{\circ}C$ , 1.8 V $\leq$ V<sub>DD</sub> = EV<sub>DD</sub> $\leq$ 5.5 V, V<sub>SS</sub> = EV<sub>SS</sub> = AV<sub>SS</sub> = 0 V)

| Parameter     | Symbol | Conditions                                                   | MIN. | TYP. | MAX.   | Unit |

|---------------|--------|--------------------------------------------------------------|------|------|--------|------|

| Transfer rate |        | $1.8~V \leq V_{\text{DD}} \leq 5.5~V$                        |      |      | fмск/6 | bps  |

|               |        | fclk = 20 MHz, fmck = fclk,<br>2.7 V $\leq$ Vdd $\leq$ 5.5 V |      |      | 3.3    | Mbps |

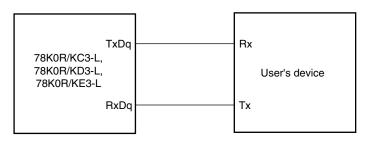

### UART mode connection diagram (during communication at same potential)

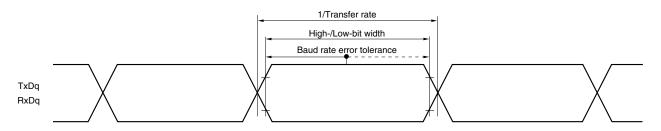

### UART mode bit width (during communication at same potential) (reference)

## Caution Select the normal input buffer for the RxDq pin and the normal output mode for the TxDq pin by using port input mode register g (PIMg) and port output mode register g (POMg).

- **Remarks 1.** q: UART number (q = 0, 1), g: PIM and POM number (g = 3, 7)

- fMCK: Serial array unit operation clock frequency (Operation clock to be set by the CKS0n bit of serial mode register 0n (SMR0n). n: Channel number (n = 0 to 3))

Caution The pins mounted depend on the product. Refer to Caution 2 at the beginning of this chapter.

| (5) Communication at different potential (2.5 V, 3 V) (UART mode) (dedicated baud rate g                                                                                                                  | enerator output) (1/2) |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| $(T_A = -40 \text{ to } +85^{\circ}\text{C}, 1.8 \text{ V} \le \text{V}_{DD} = \text{EV}_{DD0} = \text{EV}_{DD1} \le 5.5 \text{ V}, \text{ V}_{SS} = \text{EV}_{SS0} = \text{EV}_{SS1} = \text{AV}_{SS1}$ | = 0 V)                 |

| Parameter     | Symbol |           | Condition                              | MIN.                       | TYP. | MAX. | Unit           |      |

|---------------|--------|-----------|----------------------------------------|----------------------------|------|------|----------------|------|

| Transfer rate |        | reception | $4.0~V \leq V_{\text{DD}} \leq 5.5~V,$ |                            |      |      | <b>f</b> мск/6 | bps  |

|               |        |           | $2.7~V \leq V_b \leq 4.0~V$            | fclк = 20 MHz, fмcк = fclк |      |      | 3.3            | Mbps |

|               |        |           | $2.7~V \leq V_{\text{DD}} < 4.0~V,$    |                            |      |      | <b>f</b> мск/6 | bps  |

|               |        |           | $2.3~V \leq V_b \leq 2.7~V$            | fclк = 20 MHz, fмcк = fclк |      |      | 3.3            | Mbps |

## Caution Select the TTL input buffer for the RxDq pin and the N-ch open drain output (VDD tolerance) mode for the TxDq pin by using port input mode register g (PIMg) and port output mode register g (POMg).

- Remarks 1. V<sub>b</sub>[V]: Communication line voltage

- **2.** q: UART number (q = 0 to 2, 4), g: PIM and POM number (g = 0, 1, 14)

- **3.** fMCK: Serial array unit operation clock frequency

(Operation clock to be set by the CKSmn bit of serial mode register mn (SMRmn). m: Unit number (m = 0 to 2), n: Channel number (n = 0 to 3))

- **4.** V<sub>IH</sub> and V<sub>IL</sub> below are observation points for the AC characteristics of the serial array unit when communicating at different potentials in UART mode.

$4.0 \ V \leq V_{DD} \leq 5.5 \ V, \ 2.7 \ V \leq V_b \leq 4.0 \ V; \ V_{IH} = 2.2 \ V, \ V_{IL} = 0.8 \ V \\ 2.7 \ V \leq V_{DD} < 4.0 \ V, \ 2.3 \ V \leq V_b \leq 2.7 \ V; \ V_{IH} = 2.0 \ V, \ V_{IL} = 0.5 \ V$

## Caution The pins mounted depend on the product. Refer to Caution 2 at the beginning of this chapter.

| Parameter                                                | Symbol | Conditions                                                                                           | MIN.         | TYP. | MAX. | Unit |

|----------------------------------------------------------|--------|------------------------------------------------------------------------------------------------------|--------------|------|------|------|

| SCKp cycle time                                          | tксү1  | $4.0 \ V \leq V_{\text{DD}} \leq 5.5 \ V, \ 2.7 \ V \leq V_{\text{b}} \leq 4.0 \ V,$                 | 400 Note 1   |      |      | ns   |

|                                                          |        | $C_b = 30 \text{ pF}, \text{ R}_b = 1.4 \text{ k}\Omega$                                             |              |      |      |      |

|                                                          |        | $2.7 \ V \le V_{\text{DD}} < 4.0 \ V, \ 2.3 \ V \le V_{\text{b}} < 2.7 \ V,$                         | 800 Note 1   |      |      | ns   |

|                                                          |        | $C_b = 30 \text{ pF},  \text{R}_b = 2.7  \text{k}\Omega$                                             |              |      |      |      |

| SCKp high-level width                                    | tкнı   | $4.0 \ V \le V_{\text{DD}} \le 5.5 \ V, \ 2.7 \ V \le V_{\text{b}} \le 4.0 \ V,$                     | tксү1/2 – 75 |      |      | ns   |

|                                                          |        | $C_b = 30 \text{ pF},  \text{R}_b = 1.4  \text{k}\Omega$                                             |              |      |      |      |

|                                                          |        | $2.7 \ V \leq V_{\text{DD}} < 4.0 \ V, \ 2.3 \ V \leq V_{\text{b}} < 2.7 \ V,$                       | tксү1/2 –    |      |      | ns   |

|                                                          |        | $C_b = 30 \text{ pF}, \text{ R}_b = 2.7 \text{ k}\Omega$                                             | 170          |      |      |      |

| SCKp low-level width                                     | tĸL1   | $4.0 \ V \leq V_{\text{DD}} \leq 5.5 \ V, \ 2.7 \ V \leq V_{\text{b}} \leq 4.0 \ V,$                 | tксү1/2 – 20 |      |      | ns   |

|                                                          |        | $C_b = 30 \text{ pF},  \text{R}_b = 1.4  \text{k}\Omega$                                             |              |      |      |      |

|                                                          |        | $2.7 \text{ V} \leq V_{\text{DD}} < 4.0 \text{ V}, 2.3 \text{ V} \leq V_{\text{b}} < 2.7 \text{ V},$ | tксү1/2 – 35 |      |      | ns   |

|                                                          |        | $C_b = 30 \text{ pF}, \text{ R}_b = 2.7 \text{ k}\Omega$                                             |              |      |      |      |

| Slp setup time<br>(to SCKp↑) <sup>Note 2</sup>           | tsik1  | $4.0 \ V \le V_{\text{DD}} \le 5.5 \ V, \ 2.7 \ V \le V_{\text{b}} \le 4.0 \ V,$                     | 150          |      |      | ns   |

|                                                          |        | $C_b = 30 \text{ pF},  \text{R}_b = 1.4  \text{k}\Omega$                                             |              |      |      |      |

|                                                          |        | $2.7 \ V \leq V_{\text{DD}} < 4.0 \ V, \ 2.3 \ V \leq V_{\text{b}} < 2.7 \ V,$                       | 275          |      |      | ns   |

|                                                          |        | $C_b = 30 \text{ pF}, \text{ R}_b = 2.7 \text{ k}\Omega$                                             |              |      |      |      |

| SIp hold time<br>(from SCKp <sup>↑</sup> ) Note 2        | tksii  | $4.0 \ V \leq V_{\text{DD}} \leq 5.5 \ V, \ 2.7 \ V \leq V_{\text{b}} \leq 4.0 \ V,$                 | 30           |      |      | ns   |

|                                                          |        | $C_b = 30 \text{ pF}, \text{ R}_b = 1.4 \text{ k}\Omega$                                             |              |      |      |      |

|                                                          |        | $2.7 \ V \leq V_{\text{DD}} < 4.0 \ V, \ 2.3 \ V \leq V_{\text{b}} < 2.7 \ V,$                       | 30           |      |      | ns   |

|                                                          |        | $C_b = 30 \text{ pF}, \text{ R}_b = 2.7 \text{ k}\Omega$                                             |              |      |      |      |

| Delay time from SCKp↓ to<br>SOp output <sup>Note 2</sup> | tkso1  | $4.0 \ V \leq V_{\text{DD}} \leq 5.5 \ V, \ 2.7 \ V \leq V_{\text{b}} \leq 4.0 \ V,$                 |              |      | 120  | ns   |

|                                                          |        | $C_b = 30 \text{ pF}, \text{ R}_b = 1.4 \text{ k}\Omega$                                             |              |      |      |      |

|                                                          |        | $2.7 \ V \leq V_{\text{DD}} < 4.0 \ V, \ 2.3 \ V \leq V_{\text{b}} < 2.7 \ V,$                       |              |      | 215  | ns   |

|                                                          |        | $C_b = 30 \text{ pF},  \text{R}_b = 2.7  \text{k}\Omega$                                             |              |      |      |      |

## (6) Communication at different potential (2.5 V, 3 V) (CSI mode) (master mode, $\overline{SCKp}$ ... internal clock (1/2) (T<sub>A</sub> = -40 to +85°C, 2.7 V ≤ V<sub>DD</sub> = EV<sub>DD0</sub> = EV<sub>DD1</sub> ≤ 5.5 V, V<sub>SS</sub> = EV<sub>SS0</sub> = EV<sub>SS1</sub> = AV<sub>SS</sub> = 0 V)

**Notes 1.** The value must also be 4/fclk or more.

**2.** When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1.

Caution Select the TTL input buffer for the SIp pin and the N-ch open drain output (V<sub>DD</sub> tolerance) mode for the SOp pin and SCKp pin by using port input mode register g (PIMg) and port output mode register g (POMg).

**Remarks 1.** p: CSI number (p = 01, 10, 20, 40, 41), g: PIM and POM number (g = 0, 1, 14)

- **2.** m: Unit number (m = 0 to 2), n: Channel number (n = 0 to 2)

- R<sub>b</sub>[Ω]:Communication line (SCKp, SOp) pull-up resistance,

C<sub>b</sub>[F]: Communication line (SCKp, SOp) load capacitance, V<sub>b</sub>[V]: Communication line voltage

- **4.** V<sub>IH</sub> and V<sub>IL</sub> below are observation points for the AC characteristics of the serial array unit when communicating at different potentials in CSI mode.

$4.0~V \leq V_{\text{DD}} \leq 5.5~V,~2.7~V \leq V_{\text{b}} \leq 4.0~V;~V\text{ih}$  = 2.2 V, ViL = 0.8 V

$2.7~V \leq V_{\text{DD}} < 4.0~V,~2.3~V \leq V_{\text{b}} \leq 2.7~V;~V\text{ih} = 2.0~V,~V\text{il} = 0.5~V$