Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                     |

|----------------------------|-------------------------------------------------------------------------------------|

| Product Status             | Active                                                                              |

| Core Processor             | 78K/0R                                                                              |

| Core Size                  | 16-Bit                                                                              |

| Speed                      | 20MHz                                                                               |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                    |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                             |

| Number of I/O              | 50                                                                                  |

| Program Memory Size        | 48KB (48K x 8)                                                                      |

| Program Memory Type        | FLASH                                                                               |

| EEPROM Size                | -                                                                                   |

| RAM Size                   | 2K x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                         |

| Data Converters            | A/D 12x10b                                                                          |

| Oscillator Type            | Internal                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                   |

| Mounting Type              | Surface Mount                                                                       |

| Package / Case             | 64-VFBGA                                                                            |

| Supplier Device Package    | -                                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f1008f1-an1-a |

|                            |                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Conventions | Data significance:<br>Active low representations: | Higher digits on the left and lower digits on the righ $\overline{\times \times}$ (overscore over pin and signal name) |                  |  |

|-------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------------|--|

|             | Note:                                             | Footnote for item marked with <b>Note</b> in the text                                                                  |                  |  |

|             | Caution:                                          | Information requiring particular attention                                                                             |                  |  |

|             | Remark:                                           | Supplementary information                                                                                              |                  |  |

|             | Numerical representations:                        | Binary                                                                                                                 | ···×××× or ××××B |  |

|             |                                                   | Decimal                                                                                                                | ···××××          |  |

|             |                                                   | Hexadecimal                                                                                                            | ···××××H         |  |

|             |                                                   |                                                                                                                        |                  |  |

Related DocumentsThe related documents indicated in this publication may include preliminary versions.However, preliminary versions are not marked as such.

#### **Documents Related to Devices**

| Document Name                                                                       | Document No. |

|-------------------------------------------------------------------------------------|--------------|

| 78K0R/Kx3-L User's Manual                                                           | This manual  |

| 78K0R Microcontroller Instructions User's Manual                                    | U17792E      |

| 78K0R Microcontroller Self Programming Library Type02 User's Manual <sup>Note</sup> | U19193E      |

Note This document is classified under engineering management. Contact an Renesas Electronics sales representative.

#### Documents Related to Development Tools (Software) (User's Manuals)

| Document Name                            | Document No. |         |

|------------------------------------------|--------------|---------|

| CC78K0R Ver. 2.00 C Compiler             | Operation    | U18549E |

|                                          | Language     | U18548E |

| RA78K0R Ver. 1.20 Assembler Package      | Operation    | U18547E |

|                                          | Language     | U18546E |

| SM+ System Simulator                     | Operation    | U18010E |

| PM+ Ver. 6.30                            |              | U18416E |

| ID78K0R-QB Ver. 3.20 Integrated Debugger | Operation    | U17839E |

#### Documents Related to Development Tools (Hardware) (User's Manuals)

| Document Name                                                                                                                        | Document No.      |

|--------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| QB-MINI2 On-Chip Debug Emulator with Programming Function                                                                            | U18371E           |

| QB-78K0RIX3 In-Circuit Emulator (compatible with 78K0R/KC3-L, 78K0R/KD3-L, and 78K0R/KE3-L)                                          | U19228E           |

| QB-78K0RKX3C In-Circuit Emulator (compatible with 78K0R/KF3-L and 78K0R/KG3-L (µ PD78F1010, 78F1011, 78F1012, 78F1013, and 78F1014)) | U19324E           |

| QB-78F1030 In-Circuit Emulator (compatible with 78K0R/KF3-L and 78K0R/KG3-L (µ PD78F1027, 78F1028, 78F1029, and 78F1030))            | Under development |

#### **Documents Related to Flash Memory Programming**

| Document Name                                | Document No. |

|----------------------------------------------|--------------|

| PG-FP5 Flash Memory Programmer User's Manual | R02UT0008E   |

Caution The related documents listed above are subject to change without notice. Be sure to use the latest version of each document when designing.

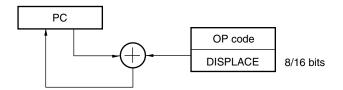

#### 4.3 Instruction Address Addressing

#### 4.3.1 Relative addressing

#### [Function]

Relative addressing stores in the program counter (PC) the result of adding a displacement value included in the instruction word (signed complement data: -128 to +127 or -32768 to +32767) to the program counter (PC)'s value (the start address of the next instruction), and specifies the program address to be used as the branch destination. Relative addressing is applied only to branch instructions.

#### Figure 4-26. Outline of Relative Addressing

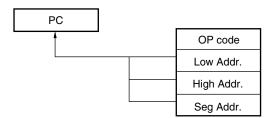

#### 4.3.2 Immediate addressing

#### [Function]

Immediate addressing stores immediate data of the instruction word in the program counter, and specifies the program address to be used as the branch destination.

For immediate addressing, CALL !!addr20 or BR !!addr20 is used to specify 20-bit addresses and CALL !addr16 or BR !addr16 is used to specify 16-bit addresses. 0000 is set to the higher 4 bits when specifying 16-bit addresses.

#### Figure 4-27. Example of CALL !!addr20/BR !!addr20

#### Figure 4-28. Example of CALL !addr16/BR !addr16

| PC | PCs       | РСн | PC∟ |            |

|----|-----------|-----|-----|------------|

|    | <u> </u>  | ł   | 1   | OP code    |

|    | ا<br>0000 |     |     | Low Addr.  |

|    |           |     |     | High Addr. |

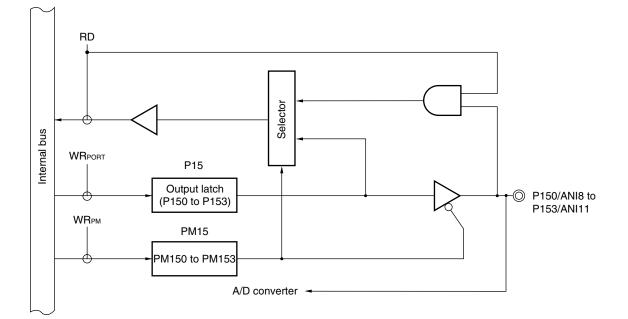

Figure 5-27. Block Diagram of P150 to P153

- P15: Port register 15

- PM15: Port mode register 15

RD: Read signal

WR xx: Write signal

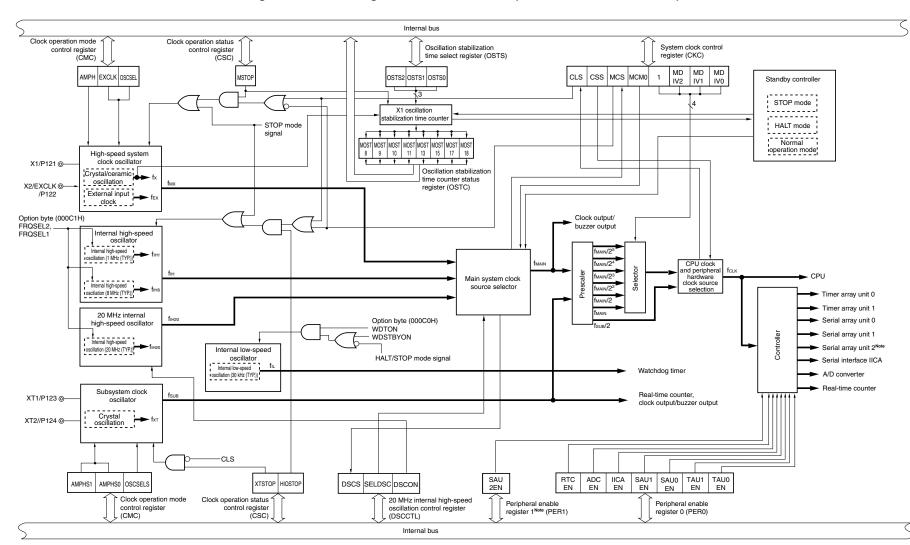

Figure 7-3. Block Diagram of Clock Generator (78K0R/KF3-L, 78K0R/KG3-L)

**Note** Those are only mounted in the  $\mu$  PD78F1027, 78F1028, 78F1029, and 78F1030. (**Remark** is listed on the next page.)

| Address: FF | FA3H Afte | r reset: 07H | R/W   |                                                   |             |                     |                  |        |

|-------------|-----------|--------------|-------|---------------------------------------------------|-------------|---------------------|------------------|--------|

| Symbol      | 7         | 6            | 5     | 4                                                 | 3           | 2                   | 1                | 0      |

| OSTS        | 0         | 0            | 0     | 0                                                 | 0           | OSTS2               | OSTS1            | OSTS0  |

|             |           |              |       |                                                   |             |                     |                  |        |

|             | OSTS2     | OSTS1        | OSTS0 |                                                   | Oscillation | n stabilization tin | ne selection     |        |

|             |           |              |       |                                                   |             | fx = 10 MHz         | fx =             | 20 MHz |

|             | 0         | 0            | 0     | 2 <sup>8</sup> /fx 25.6 μs                        |             | Setting             | prohibited       |        |

|             | 0         | 0            | 1     | 2 <sup>9</sup> /fx 51.2 μs                        |             | 25.6 <i>μ</i> s     |                  |        |

|             | 0         | 1            | 0     | 2 <sup>10</sup> /fx 102.4 μs 5                    |             | 51.2 <i>μ</i> s     |                  |        |

|             | 0         | 1            | 1     | 2 <sup>11</sup> /fx                               | 2           | 04.8 <i>µ</i> s     | 102.4 <i>µ</i> : | S      |

|             | 1         | 0            | 0     | 2 <sup>13</sup> /f <sub>x</sub> 819.2 μs 409.6 μs |             | S                   |                  |        |

|             | 1         | 0            | 1     | 2 <sup>15</sup> /fx 3.27 ms 1.64 m                |             | 1.64 ms             | ;                |        |

|             | 1         | 1            | 0     | 2 <sup>17</sup> /fx                               | 1           | 3.11 ms             | 6.55 ms          |        |

|             | 1         | 1            | 1     | 2 <sup>18</sup> /fx                               | 2           | 6.21 ms             | 13.11 m          | IS     |

#### Figure 7-8. Format of Oscillation Stabilization Time Select Register (OSTS)

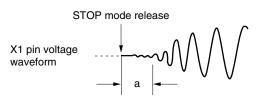

Cautions 1. To set the STOP mode when the X1 clock is used as the CPU clock, set the OSTS register before executing the STOP instruction.

- 2. Setting the oscillation stabilization time to 20  $\mu$ s or less is prohibited.

- 3. Change the setting of the OSTS register before setting the MSTOP bit of the clock operation status control register (CSC) to 0.

- 4. Do not change the value of the OSTS register during the X1 clock oscillation stabilization time.

- 5. The oscillation stabilization time counter counts up to the oscillation stabilization time set by the OSTS register.

In the following cases, set the oscillation stabilization time of the OSTS register to the value greater than the count value which is to be checked by the OSTC register after the oscillation starts.

- If the X1 clock starts oscillation while the internal high-speed oscillation clock or subsystem clock is being used as the CPU clock.

- If the STOP mode is entered and then released while the internal high-speed oscillation clock is being used as the CPU clock with the X1 clock oscillating. (Note, therefore, that only the status up to the oscillation stabilization time set by the OSTS register is set to the OSTC register after the STOP mode is released.)

- 6. The X1 clock oscillation stabilization wait time does not include the time until clock oscillation starts ("a" below).

**Remark** fx: X1 clock oscillation frequency

#### Table 7-4. CPU Clock Transition and SFR Register Setting Examples (4/6)

# (9) CPU clock changing from high-speed system clock (C) to subsystem clock (D) (products other than 78K0R/KC3-L (40-pin))

| (Setting sequence of SFR registers) |              |                         |              |

|-------------------------------------|--------------|-------------------------|--------------|

| Setting Flag of SFR Register        | CSC Register | Waiting for Oscillation | CKC Register |

| Status Transition                   | XTSTOP       | Stabilization           | CSS          |

| $(C) \to (D)$                       | 0            | Necessary               | 1            |

Unnecessary if the CPU is operating with the subsystem clock

## (10) CPU clock changing from subsystem clock (D) to internal high-speed oscillation clock (B) (products other than 78K0R/KC3-L (40-pin))

| (Setting sequence of SFR registers) |                              |              |              |     |  |

|-------------------------------------|------------------------------|--------------|--------------|-----|--|

|                                     | Setting Flag of SFR Register | CSC Register | CKC Register |     |  |

| Status Transition                   |                              | HIOSTOP      | MCM0         | CSS |  |

| $(D) \to (B)$                       |                              | 0            | 0            | 0   |  |

|                                     |                              |              |              |     |  |

Unnecessary if the CPU is operating with the internal high-speed oscillation clock Unnecessary if this register is already set

Remark (A) to (K) in Table 7-4 correspond to (A) to (K) in Figure 7-19.

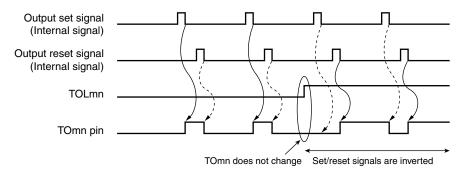

#### (3) Operation of TOmn pin in slave channel output mode (TOMmn = 1)

#### (a) When timer output level register m (TOLm) setting has been changed during timer operation

When the TOLm register setting has been changed during timer operation, the setting becomes valid at the generation timing of the TOmn pin change condition. Rewriting the TOLm register does not change the output level of the TOmn pin.

The operation when TOMmn is set to 1 and the value of the TOLm register is changed while the timer is operating (TEmn = 1) is shown below.

Remarks 1. Set:The output signal of the TOmn pin changes from inactive level to active level.Reset:The output signal of the TOmn pin changes from active level to inactive level.

| . m: Unit number (m = 0, 1), n: Channel number (n = 0 to 7)           |                                                                                                                         |  |  |  |  |  |

|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| However, in case of the timer output pin (TOmn), mn changes as below. |                                                                                                                         |  |  |  |  |  |

| 78K0R/KC3-L (40-pin):                                                 | mn = 02 to 07                                                                                                           |  |  |  |  |  |

| 78K0R/KC3-L (44-pin, 48-pin):                                         | mn = 00 to 07                                                                                                           |  |  |  |  |  |

| 78K0R/KD3-L, 78K0R/KE3-L:                                             | mn = 00 to 07                                                                                                           |  |  |  |  |  |

| 78K0R/KF3-L, 78K0R/KG3-L:                                             | mn = 00 to 07, 10 to 13                                                                                                 |  |  |  |  |  |

|                                                                       | However, in case of the timer ou<br>78K0R/KC3-L (40-pin):<br>78K0R/KC3-L (44-pin, 48-pin):<br>78K0R/KD3-L, 78K0R/KE3-L: |  |  |  |  |  |

#### CHAPTER 11 CLOCK OUTPUT/BUZZER OUTPUT CONTROLLER

The number of output pins of the clock output and buzzer output controllers differs, depending on the product. Furthermore, 44-pin product of the 78K0R/KC3-L are not provided with clock output and buzzer output controllers.

| Output pin | KC3-L<br>(40-pin) | KC3-L<br>(44-pin) | KC3-L<br>(48-pin) | KD3-L        | KE3-L        | KF3-L        | KG3-L        |

|------------|-------------------|-------------------|-------------------|--------------|--------------|--------------|--------------|

| PCLBUZ0    | -                 | -                 |                   | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| PCLBUZ1    | _                 | _                 | _                 | _            |              |              |              |

#### 11.1 Functions of Clock Output/Buzzer Output Controller

The clock output controller is intended for carrier output during remote controlled transmission and clock output for supply to peripheral ICs.

Buzzer output is a function to output a square wave of buzzer frequency.

One pin can be used to output a clock or buzzer sound.

Two output pins, PCLBUZ0 and PCLBUZ1, are available.

The PCLBUZn pin outputs a clock selected by clock output select register n (CKSn).

Figure 11-1 shows the block diagram of clock output/buzzer output controller.

Remark n = 0: 78K0R/KC3-L (48-pin), 78K0R/KD3-L

n = 0, 1: 78K0R/KE3-L, 78K0R/KF3-L, 78K0R/KG3-L

#### (18) Port mode registers 0, 1, 3, 4, 5, 7, and 14 (PM0, PM1, PM3, PM4, PM5, PM7, PM14)

These registers set input/output of ports 0, 1, 3, 4, 5, 7, and 14 in 1-bit units. The port pins that are shared with the serial data I/O pin or serial clock output I/O pin differ depending on the product. When using the serial array unit, set the following port mode registers according to the product used.

| 78K0R/KC3-L, 78K0R/KD3-L, 78K0R/KE3-L       | : PM3, PM7                 |

|---------------------------------------------|----------------------------|

| 78K0R/KF3-L (μ PD78F1010, 78F1011, 78F1012) | : PM0, PM1, PM4, PM14      |

| 78K0R/KF3-L (μ PD78F1027, 78F1028)          | : PM0, PM1, PM4, PM5, PM14 |

| 78K0R/KG3-L (μ PD78F1013, 78F1014)          | : PM0, PM1, PM4, PM14      |

| 78K0R/KF3-L (μ PD78F1029, 78F1030)          | : PM0, PM1, PM4, PM5, PM14 |

When using the ports (such as P30/SO10/TxD1, P31/SI10/RxD1/SDA10/INTP1) to be shared with the serial data output pin or serial clock output pin for serial data output or serial clock output, set the port mode register (PMxx) bit corresponding to each port to 0. And set the port register (Pxx) bit corresponding to each port to 1

Example: When using P30/SO10/TxD1 for serial data output or serial clock output Set the PM30 bit of the port mode register 3 to 0. Set the P30 bit of the port register 3 to 0.

When using the ports (such as P31/SI10/RxD1/SDA10/INTP1, P32/SCK10/SCL10/INTP2) to be shared with the serial data input pin or serial clock input pin for serial data input or serial clock input, set the port mode register (PMxx) bit corresponding to each port to 1. At this time, the port register (Pxx) bit may be 0 or 1.

Example: When using P31/SI10/RxD1/SDA10/INTP1 for serial data input or serial clock input Set the PM31 bit of port mode register 3 to 1. Set the P31 bit of port register 3 to 0 or 1.

The PM0, PM1, PM3, PM4, PM5, PM7, and PM14 registers can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation sets the PM0, PM1, PM3, PM4, PM5, PM7, and PM14 registers to FFH.

#### 14.4.1 Stopping the operation by units

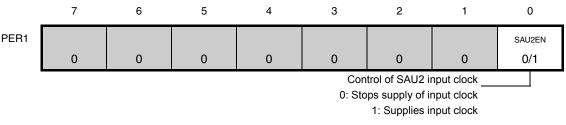

The stopping of the operation by units is set by using peripheral enable registers 0 and 1 (PER0, PER1).

The PER0 register and the PER1 register are used to enable or disable supplying the clock to the peripheral hardware. Clock supply to a hardware macro that is not used is stopped in order to reduce the power consumption and noise.

To stop the operation of serial array unit 0, clear bit 2 (SAU0EN) of the PER0 register to 0. In the 78K0R/KF3-L ( $\mu$  PD78F1010, 78F1011, 78F1012) and 78K0R/KG3-L ( $\mu$  PD78F1013, 78F1014), to stop the operation of serial array unit 1, clear bit 3 (SAU1EN) of the PER0 register to 0.

Furthermore, in the 78K0R/KF3-L ( $\mu$  PD78F1027, 78F1028) and 78K0R/KG3-L ( $\mu$  PD78F1029, 78F1030), to stop the operation of serial array unit 2, clear bit 0 (SAU2EN) of the PER1 register to 0.

#### Figure 14-26. Peripheral Enable Register 0 (PER0) Setting When Stopping the Operation by Units

#### (a) Peripheral enable register 0 (PER0) ... Set only the bit of SAUm to be stopped to 0.

1: Supplies input clock

Notes 1. That is not provided in 40-pin product of the 78K0R/KC3-L.

- 2. That is not provided in 40-pin and 44-pin products of the 78K0R/KC3-L.

- 3. 78K0R/KF3-L and 78K0R/KG3-L only.

#### (b) Peripheral enable register 1 (PER1) ... Set only the bit of SAU2 to be stopped to 0.

Cautions 1. If SAUmEN = 0, writing to a control register of serial array unit m is ignored, and, even if the register is read, only the default value is read

Note that this does not apply to the following registers.

78K0R/KC3-L, 78K0R/KD3-L, 78K0R/KE3-L:

ISC, NFEN0, PIM3, PIM7, POM3, POM7, PM3, PM7, P3, and P7 registers.

78K0R/KF3-L (μ PD78F1010, 78F1011, 78F1012), 78K0R/KG3-L (μ PD78F1013, 78F1014):

ISC, NFEN0, PIM0, PIM1, PIM14, POM0, POM1, POM14, PM0, PM1, PM4, PM14, P0, P1, P4, and P14 registers.

78K0R/KF3-L (μ PD78F1027, 78F1028), 78K0R/KG3-L (μ PD78F1029, 78F1030):

ISC, NFEN0, PIM0, PIM1, PIM14, POM0, POM1, POM14, PM0, PM1, PM4, PM5, PM14, P0, P1, P4, P5, and P14 registers.

(Caution 2 and Remark is listed on the next page.)

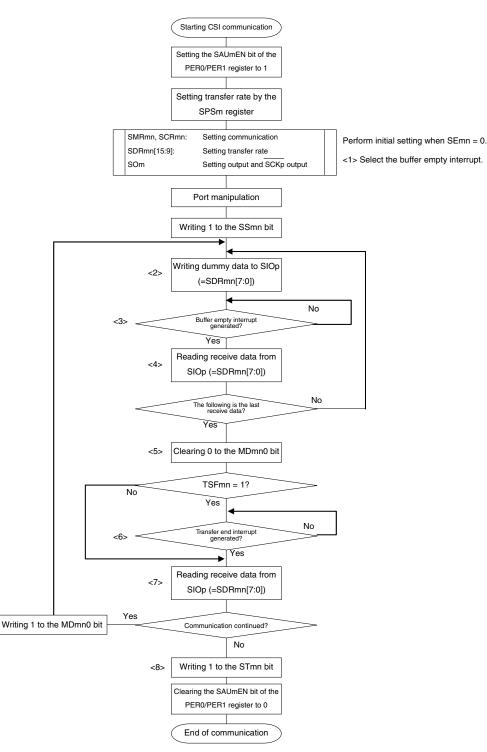

#### Figure 14-43. Flowchart of Master Reception (in Continuous Reception Mode)

- Caution After setting the PER0/PER1 register to 1, be sure to set the SPSm register after 4 or more clocks have elapsed.

- **Remark** <1> to <8> in the figure correspond to <1> to <8> in **Figure 14-42 Timing Chart of Master Reception** (in Continuous Reception Mode).

| SE           | MD  | MD  | SOE | SO            | СКО           | TXE | RXE | PM          | P04         | PM03        | P03         | PM02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | P02         | Operation mode                          |                     | Pin Function                      |                   |

|--------------|-----|-----|-----|---------------|---------------|-----|-----|-------------|-------------|-------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------------------------------|---------------------|-----------------------------------|-------------------|

| 02<br>Note 1 | 022 | 021 | 02  | 02            | 02            | 02  | 02  | 04          |             | Note 2      | Note 2      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |                                         | SCK10/<br>SCL10/P04 | SI10/SDA10/<br>RxD1/P03<br>Note 2 | SO10/<br>TxD1/P02 |

| 0            | 0   | 0   | 0   | 1             | 1             | 0   | 0   | ×<br>Note 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ×<br>Note 3 | Operation stop                          | P04                 | P03                               | P02               |

|              | 0   | 1   |     |               |               |     |     | Note 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | NOLE 5      | mode                                    |                     | P03/RxD1                          |                   |

|              | 1   | 0   |     |               |               |     |     |             |             |             |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |                                         |                     | P03                               |                   |

| 1            | 0   | 0   | 0   | 1             | 1             | 0   | 1   | 1           | ×           | 1           | ×           | × X Note 3 Xote |             | SI10                                    | P02                 |                                   |                   |

|              |     |     | 1   | 0/1<br>Note 4 | 1             | 1   | 0   | 1           | ×           | ×<br>Note 3 | ×<br>Note 3 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1           | Slave CSI10<br>transmission             | SCK10<br>(input)    | P03                               | SO10              |

|              |     |     | 1   | 0/1<br>Note 4 | 1             | 1   | 1   | 1           | ×           | 1           | ×           | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1           | Slave CSI10<br>transmission /reception  | SCK10<br>(input)    | SI10                              | SO10              |

|              |     |     | 0   | 1             | 0/1<br>Note 4 | 0   | 1   | 0           | 1           | 1           | ×           | ×<br>Note 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ×<br>Note 3 | Master CSI10<br>reception               | SCK10<br>(output)   | SI10                              | P02               |

|              |     |     | 1   | 0/1<br>Note 4 | 0/1<br>Note 4 | 1   | 0   | 0           | 1           | ×<br>Note 3 | ×<br>Note 3 | 0 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             | Master CSI10<br>transmission            | SCK10<br>(output)   | P03                               | SO10              |

|              |     |     | 1   | 0/1<br>Note 4 | 0/1<br>Note 4 | 1   | 1   | 0           | 1           | 1           | ×           | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1           | Master CSI10<br>transmission /reception | SCK10<br>(output)   | SI10                              | SO10              |

|              | 0   | 1   | 1   | 0/1<br>Note 4 | 1             | 1   | 0   | ×<br>Note 3 | ×<br>Note 3 | ×<br>Note 3 | ×<br>Note 3 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1           | UART1<br>transmission Note 5            | P04                 | P03/RxD1                          | TxD1              |

| 0            | 1   | 0   | 0   | 0/1<br>Note 6 | 0/1<br>Note 6 | 0   | 0   | 0           | 1           | 0           | 1           | ×<br>Note 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ×<br>Note 3 | IIC10                                   | SCL10               | SDA10                             | P02               |

|              |     |     |     |               |               | 1   | 0   |             |             |             |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             | start condition                         |                     |                                   |                   |

|              |     |     |     |               |               | 0   | 1   |             |             |             |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |                                         |                     |                                   |                   |

| 1            |     |     | 1   | 0/1<br>Note 4 | 0/1<br>Note 4 | 1   | 0   | 0           | 1           | 0           | 1           | ×<br>Note 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ×<br>Note 3 | IIC10 address field<br>transmission     | SCL10               | SDA10                             | P02               |

|              |     |     | 1   | 0/1<br>Note 4 | 0/1<br>Note 4 | 1   | 0   | 0           | 1           | 0           | 1           | ×<br>Note 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ×<br>Note 3 | IIC10 data<br>transmission              | SCL10               | SDA10                             | P02               |

|              |     |     | 1   | 0/1<br>Note 4 | 0/1<br>Note 4 | 0   | 1   | 0           | 1           | 0           | 1           | ×<br>Note 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ×<br>Note 3 | IIC10 data reception                    | SCL10               | SDA10                             | P02               |

| 0            |     |     | 0   | 0/1           | 0/1           | 0   | 0   | 0           | 1           | 0           | 1           | ×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ×           | IIC10                                   | SCL10               | SDA10                             | P02               |

|              |     |     |     | Note 7        | Note 7        | 1   | 0   |             |             |             |             | Note 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Note 3      | stop condition                          |                     |                                   |                   |

| 1            |     |     |     |               |               | 0   | 1   |             |             |             |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |                                         |                     |                                   |                   |

# Table 14-11. Relationship between register settings and pins(Channel 2 of unit 0: CSI10, UART1 transmission, IIC10)

**Notes 1.** Serial channel enable register 0 (SE0) is a read-only status register which is set using serial channel statrt register 0 (SS0) and serial channel stop register 0 (ST0).

When channel 3 of unit 0 is set to UART1 reception, this pin becomes an RxD1 function pin (refer to Table 14-12). In this case, operation stop mode or UART1 transmission must be selected for channel 2 of unit 0.

**3.** This pin can be set as a port function pin.

This is 0 or 1, depending on the communication operation. For details, refer to 14.3 (12) Serial output register m (SOm).

5. When using UART1 transmission and reception in a pair, set channel 3 of unit 0 to UART1 reception (refer to **Table 14-12**).

**6.** Set the CKO02 bit to 1 before a start condition is generated. Clear the SO02 bit from 1 to 0 when the start condition is generated.

**7.** Set the CKO02 bit to 1 before a stop condition is generated. Clear the SO02 bit from 0 to 1 when the stop condition is generated.

Remark X: Don't care

#### Table 14-17. Relationship between register settings and pins (Channel 0 of unit 2: CSI40, UART4 transmission)

| SE           | MD  | MD  | SOE | SO            | СКО           | TXE | RXE | PM          | P50         | PM           | Note 2      |             | P52         | Operation mode                             |                         | Pin Functio                                       | n                          |

|--------------|-----|-----|-----|---------------|---------------|-----|-----|-------------|-------------|--------------|-------------|-------------|-------------|--------------------------------------------|-------------------------|---------------------------------------------------|----------------------------|

| 20<br>Note 1 | 202 | 201 | 20  | 20            | 20            | 20  | 20  | 50          |             | 51<br>Note 2 | Hold I      | 52          |             |                                            | SCK40/<br>INTP1/<br>P50 | SI40/<br>RxD4/<br>INTP2/<br>P51 <sup>Note 2</sup> | SO40/<br>TxD4/<br>TO00/P52 |

| 0            | 0   | 0   | 0   | 1             | 1             | 0   | 0   | ×<br>Note 3 | ×<br>Note 3 | ×<br>Note 3  | ×<br>Note 3 | ×<br>Note 3 | ×<br>Note 3 | Operation stop<br>mode                     | INTP1/<br>P50           | INTP2/<br>P51                                     | TO00/P52                   |

|              | 0   | 1   |     |               |               |     |     |             |             |              |             |             |             |                                            |                         | INTP2/<br>P51/RxD4                                |                            |

| 1            | 0   | 0   | 0   | 1             | 1             | 0   | 1   | 1           | ×           | 1            | ×           | ×<br>Note 3 | ×<br>Note 3 | Slave CSI40 reception                      | SCK40<br>(input)        | SI40                                              | TO00/P52                   |

|              |     |     | 1   | 0/1<br>Note 4 | 1             | 1   | 0   | 1           | ×           | ×<br>Note 3  | ×<br>Note 3 | 0           | 1           | Slave CSI40<br>transmission                | SCK40<br>(input)        | INTP2/P51                                         | SO40                       |

|              |     |     | 1   | 0/1<br>Note 4 | 1             | 1   | 1   | 1           | ×           | 1            | ×           | 0           | 1           | Slave CSI40<br>transmission/<br>reception  | SCK40<br>(input)        | SI40                                              | SO40                       |

|              |     |     | 0   | 1             | 0/1<br>Note 4 | 0   | 1   | 0           | 1           | 1            | ×           | ×<br>Note 3 | ×<br>Note 3 | Master CSI40<br>reception                  | SCK40<br>(output)       | SI40                                              | TO00/P52                   |

|              |     |     | 1   | 0/1<br>Note 4 | 0/1<br>Note 4 | 1   | 0   | 0           | 1           | ×<br>Note 3  | ×<br>Note 3 | 0           | 1           | Master CSI40<br>transmission               | SCK40<br>(output)       | INTP2/P51                                         | SO40                       |

|              |     |     | 1   | 0/1<br>Note 4 | 0/1<br>Note 4 | 1   | 1   | 0           | 1           | 1            | ×           | 0           | 1           | Master CSI40<br>transmission/<br>reception | SCK40<br>(output)       | SI40                                              | SO40                       |

|              | 0   | 1   | 1   | 0/1<br>Note 4 | 1             | 1   | 0   | ×<br>Note 3 | ×<br>Note 3 | ×<br>Note 3  | ×<br>Note 3 | 0           | 1           | UART4<br>transmission <sup>Note 5</sup>    | INTP1/<br>P50           | INTP2/<br>P51/RxD4                                | TxD4                       |

#### (µPD78F1027, 78F1028, 78F1029, 78F1030 only)

- **Notes 1.** Serial channel enable register 2 (SE2) is a read-only status register which is set using serial channel start register 2 (SS2) and serial channel stop register 2 (ST2).

- When channel 1 of unit 2 is set to UART4 reception, this pin becomes an RxD4 function pin (refer to Table 14-18). In this case, operation stop mode or UART4 transmission must be selected for channel 0 of unit 2.

- 3. This pin can be set as a port function pin.

- This is 0 or 1, depending on the communication operation. For details, refer to 14.3 (12) Serial output register m (SOm).