Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                     |

|----------------------------|-------------------------------------------------------------------------------------|

| Product Status             | Active                                                                              |

| Core Processor             | 78K/0R                                                                              |

| Core Size                  | 16-Bit                                                                              |

| Speed                      | 20MHz                                                                               |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                    |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                             |

| Number of I/O              | 50                                                                                  |

| Program Memory Size        | 64KB (64K x 8)                                                                      |

| Program Memory Type        | FLASH                                                                               |

| EEPROM Size                | -                                                                                   |

| RAM Size                   | 3K x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                         |

| Data Converters            | A/D 12x10b                                                                          |

| Oscillator Type            | Internal                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                   |

| Mounting Type              | Surface Mount                                                                       |

| Package / Case             | 64-VFBGA                                                                            |

| Supplier Device Package    | -                                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f1009f1-an1-a |

|                            |                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Function Name        | I/O    | Function                                                                                                                                           | After Reset | Alternate Function       |

|----------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------------------|

| TxD0                 | Output | Serial data output from UART0                                                                                                                      | Input port  | P12/SO00                 |

| TxD1                 |        | Serial data output from UART1                                                                                                                      |             | P02/SO10                 |

| TxD2                 |        | Serial data output from UART2                                                                                                                      |             | P144/SO20                |

| TxD3                 |        | Serial data output from UART3                                                                                                                      |             | P13                      |

| TxD4 <sup>Note</sup> |        | Serial data output from UART4                                                                                                                      |             | P52/SO40 <sup>Note</sup> |

| X1                   | _      | Resonator connection for main system clock                                                                                                         | Input port  | P121                     |

| X2                   | _      |                                                                                                                                                    | Input port  | P122/EXCLK               |

| EXCLK                | Input  | External clock input for main system clock                                                                                                         | Input port  | P122/X2                  |

| XT1                  | _      | Resonator connection for subsystem clock                                                                                                           | Input port  | P123                     |

| XT2                  | _      |                                                                                                                                                    | Input port  | P124                     |

| Vdd                  | -      | Positive power supply (P121 to P124 and other than ports (excluding RESET and FLMD0 pins))                                                         | _           | -                        |

| EVDD0, EVDD1         | -      | Positive power supply for ports (other than P20 to P27, P121 to P124, P150 to P157), and $\overrightarrow{\text{RESET}}$ and FLMD0 pins            | -           | -                        |

| AVREF                | -      | <ul> <li>A/D converter reference voltage input</li> <li>Positive power supply for P20 to P27, P150 to P157, and A/D converter</li> </ul>           | _           | _                        |

| Vss                  | -      | Ground potential (P121 to P124 and other than ports (excluding RESET and FLMD0 pins))                                                              | _           | -                        |

| EVsso, EVssi         | -      | Ground potential for ports (other than P20 to P27, P121 to P124, and P150 to P157), and RESET and FLMD0 pins                                       | _           | -                        |

| AVss                 | _      | Ground potential for A/D converter, P20 to P27, and P150 to P157. Use this pin with the same potential as $EV_{SS0}$ , $EV_{SS1}$ , and $V_{SS}$ . | -           | _                        |

| FLMD0                | _      | Flash memory programming mode setting                                                                                                              | -           | _                        |

| TOOL0                | I/O    | Data I/O for flash memory programmer/debugger                                                                                                      | Input port  | P40                      |

| TOOL1                | Output | Clock output for debugger                                                                                                                          | Input port  | P41                      |

# (2) Non-port functions (3/3): 78K0R/KG3-L

**Note** SO40 and TxD4 are only mounted in the  $\mu$  PD78F1029 and 78F1030.

The following operation modes can be specified in 1-bit units.

# (1) Port mode

P50 to P57 function as an I/O port. P50 to P57 can be set to input or output port in 1-bit units using port mode register 5 (PM5). Use of an on-chip pull-up resistor can be specified by pull-up resistor option register 5 (PU5).

# (2) Control mode

P50 to P57 function as serial interface data I/O, clock I/O, external interrupt request input, timer I/O, and clock/buzzer output.

### (a) INTP1, INTP2, INTP7

These are the external interrupt request input pins for which the valid edge (rising edge, falling edge, or both rising and falling edges) can be specified.

# (b) TI00, TI07

These are the pins for inputting an external count clock/capture trigger to 16-bit timers 00 and 07.

### (c) TO00, TO07

These are the timer output pins of 16-bit timers 00 and 07.

# (d) PCLBUZ1

This is a clock/buzzer output pin.

### (e) SI40, SI41

These are the serial data input pins of serial interface CSI40 and CSI41.

### (f) SO40, SO41

These are the serial data output pin of serial interface CSI40 and CSI41.

### (g) <u>SCK40</u>, <u>SCK41</u>

These are the serial clock I/O pins of serial interface CSI40 and CSI41.

### (h) RxD4

This is a serial data input pin of serial interface UART4.

# (i) TxD4

This is a serial data output pins of serial interface UART4.

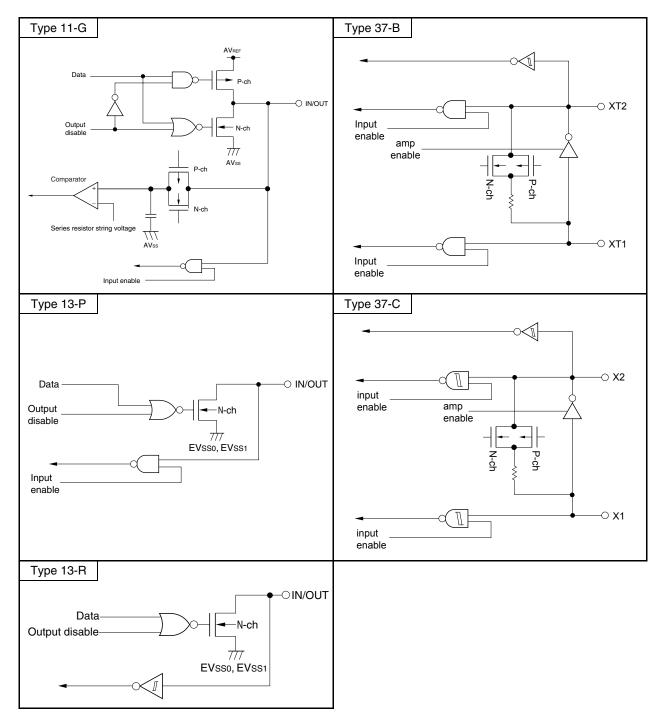

Figure 3-1. Pin I/O Circuit List (2/2)

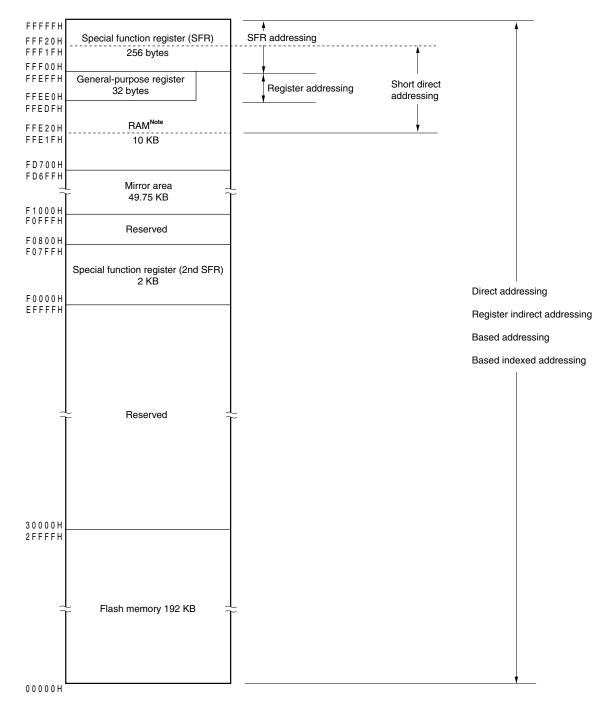

# Figure 4-18. Correspondence Between Data Memory and Addressing (µPD78F1027, 78F1029)

Note While using the self-programming function, the area FFE20H to FFEFFH cannot be used as stack memory.

The count value can be read by reading timer/counter register mn (TCRmn).

The count value is set to FFFFH in the following cases.

- When the reset signal is generated

- When the TAU0EN bit (in case of TAU0) or TAU1EN bit (in case of TAU1) of peripheral enable registers 0, 2 (PER0, PER2) are cleared

- When counting of the slave channel has been completed in the PWM output mode

- When counting of the master/slave channel has been completed in the one-shot pulse output mode

- When counting of the slave channel has been completed in the multiple PWM output mode

The count value is cleared to 0000H in the following cases.

- When the start trigger is input in the capture mode

- When capturing has been completed in the capture mode

# Caution The count value is not captured to timer data register mn (TDRmn) even when the TCRmn register is read.

The TCRmn register read value differs as follows according to operation mode changes and the operating status.

| Operation Mode               | Count Mode | ٦                                                                      | Timer/counter register m                                                                    | n (TCRmn) Read Value <sup>№</sup>                                                        | te                                                           |

|------------------------------|------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------|

|                              |            | Value if the<br>operation mode<br>was changed after<br>releasing reset | Value if the<br>operation mode was<br>changed after count<br>operation paused<br>(TTmn = 1) | Value if the<br>Operation was<br>restarted after count<br>operation paused<br>(TTmn = 1) | Value when waiting<br>for a start trigger<br>after one count |

| Interval timer<br>mode       | Count down | FFFFH                                                                  | Undefined                                                                                   | Stop value                                                                               | -                                                            |

| Capture mode                 | Count up   | 0000H                                                                  | Undefined                                                                                   | Stop value                                                                               | -                                                            |

| Event counter mode           | Count down | FFFFH                                                                  | Undefined                                                                                   | Stop value                                                                               | _                                                            |

| One-count mode               | Count down | FFFFH                                                                  | Undefined                                                                                   | Stop value                                                                               | FFFFH                                                        |

| Capture & one-<br>count mode | Count up   | 0000H                                                                  | Undefined                                                                                   | Stop value                                                                               | Capture value of<br>TDRmn register + 1                       |

Table 8-2.

Timer/counter Register mn (TCRmn) Read Value in Various Operation Modes

**Note** This indicates the value read from the TCRmn register when channel n has stopped operating as a timer (TEmn = 0) and has been enabled to operate as a counter (TSmn = 1). The read value is held in the TCRmn register until the count operation starts.

Remark

m: Unit number (m = 0, 1), n: Channel number (n = 0 to 7)

78K0R/KC3-L, 78K0R/KD3-L, 78K0R/KE3-L:

mn = 00 to 07

78K0R/KF3-L, 78K0R/KG3-L:

mn = 00 to 07, 10 to 13

mn = 00 to 07

mn = 00 to 07<

# (11) Timer output level register m (TOLm)

The TOLm register is a register that controls the timer output level of each channel.

The setting of the inverted output of channel n by this register is reflected at the timing of set or reset of the timer output signal while the timer output is enabled (TOEmn = 1) in the slave channel output mode (TOMmn = 1). In the master channel output mode (TOMmn = 0), this register setting is invalid.

The TOLm register can be set by a 16-bit memory manipulation instruction.

The lower 8 bits of the TOLm register can be set with an 8-bit memory manipulation instruction with TOLmL. Reset signal generation clears this register to 0000H.

# Figure 8-24. Format of Timer Output Level register m (TOLm)

| Address: F01 | BCH, F  | 01BDH   | After                                      | reset: (  | 0000H  | R/W |   |   |     |     |     |     |     |     |     |     |

|--------------|---------|---------|--------------------------------------------|-----------|--------|-----|---|---|-----|-----|-----|-----|-----|-----|-----|-----|

| Symbol       | 15      | 14      | 13                                         | 12        | 11     | 10  | 9 | 8 | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| TOL0         | 0       | 0       | 0                                          | 0         | 0      | 0   | 0 | 0 | TOL |

|              |         |         |                                            |           |        |     |   |   | 07  | 06  | 05  | 04  | 03  | 02  | 01  | 00  |

|              |         |         |                                            |           |        |     |   |   |     |     |     |     |     |     |     |     |

| Address: F01 | E4H, F( | 01E5H   | After                                      | reset: 0  | 000H   | R/W |   |   |     |     |     |     |     |     |     |     |

| Symbol       | 15      | 14      | 13                                         | 12        | 11     | 10  | 9 | 8 | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| TOL1         | 0       | 0       | 0 0 0 0 0 0 0 0 0 0 0 TOL TOL TOL TOL      |           |        |     |   |   |     |     |     |     |     |     |     |     |

|              |         |         |                                            |           |        |     |   |   |     |     |     |     | 13  | 12  | 11  | 10  |

|              | -       |         |                                            |           |        |     |   |   |     |     |     |     |     |     |     |     |

|              | TOL     |         | Control of timer output level of channel n |           |        |     |   |   |     |     |     |     |     |     |     |     |

|              | mn      |         |                                            |           |        |     |   |   |     |     |     |     |     |     |     |     |

|              | 0       | Positiv | ositive logic output (active-high)         |           |        |     |   |   |     |     |     |     |     |     |     |     |

|              | 1       | Inverte | d outpu                                    | ut (activ | e-low) |     |   |   |     |     |     |     |     |     |     |     |

### Caution Be sure to clear bits 15 to 8 of the TOL0 register and bits 15 to 4 of the TOL1 register to "0".

**Remarks 1.** If the value of this register is rewritten during timer operation, the timer output is inverted when the timer output signal changes next, instead of immediately after the register value is rewritten.

m: Unit number (m = 0, 1), n: Channel number (n = 0 to 7)

78K0R/KC3-L, 78K0R/KD3-L, 78K0R/KE3-L: mn = 00 to 07

78K0R/KF3-L, 78K0R/KG3-L: mn = 00 to 07, 10 to 13

# (12) Timer output mode register m (TOMm)

The TOMm register is used to control the timer output mode of each channel.

When a channel is used for the independent channel operation function, set the corresponding bit of the channel to be used to 0.

When a channel is used for the simultaneous channel operation function (PWM output, one-shot pulse output, or multiple PWM output), set the corresponding bit of the master channel to 0 and the corresponding bit of the slave channel to 1.

The setting of each channel n by this register is reflected at the timing when the timer output signal is set or reset while the timer output is enabled (TOEmn = 1).

The TOMm register can be set by a 16-bit memory manipulation instruction.

The lower 8 bits of the TOMm register can be set with an 8-bit memory manipulation instruction with TOMmL. Reset signal generation clears this register to 0000H.

### Figure 8-25. Format of Timer Output Mode register m (TOMm)

Address: F01BEH, F01BFH After reset: 0000H R/W

| Symbol | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|----|----|----|----|----|----|---|---|-----|-----|-----|-----|-----|-----|-----|-----|

| TOM0   | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | TOM | ТОМ |

|        |    |    |    |    |    |    |   |   | 07  | 06  | 05  | 04  | 03  | 02  | 01  | 00  |

|        |    |    |    |    |    |    |   |   |     |     |     |     |     |     |     |     |

#### Address: F01E6, F01E7H After reset: 0000H R/W

| Symbol | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3         | 2         | 1  | 0         |

|--------|----|----|----|----|----|----|---|---|---|---|---|---|-----------|-----------|----|-----------|

| TOM1   | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 |   | 0 | 0 | ТОМ<br>13 | TOM<br>12 | 11 | TOM<br>10 |

| TOM<br>mn | Control of timer output mode of channel n                                                                                                                                                       |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0         | Master channel output mode (to produce toggle output by timer interrupt request signal (INTTMmn))                                                                                               |

| 1         | Slave channel output mode (output is set by the timer interrupt request signal (INTTMmn) of the master channel, and reset by the timer interrupt request signal (INTTMmp) of the slave channel) |

### Caution Be sure to clear bits 15 to 8 of the TOM0 register and bits 15 to 4 of the TOM1 register to "0".

Remarkm: Unit number (m = 0, 1), n: Channel number (n = 0 to 7)78K0R/KC3-L, 78K0R/KD3-L, 78K0R/KE3-L:mn = 00 to 0778K0R/KF3-L, 78K0R/KG3-L:mn = 00 to 07, 10 to 13p: Slave channel number Notemn = 0, 2, 4, 6, n \leq 7When m = 0: Master channel n = 0, 2, n \leq 3(where p is a consecutive integer greater than n)

**Note** Since there is no function of timer I/O, the channel 1 in the 78K0R/KC3-L (40-pin) can not be used as the slave channel.

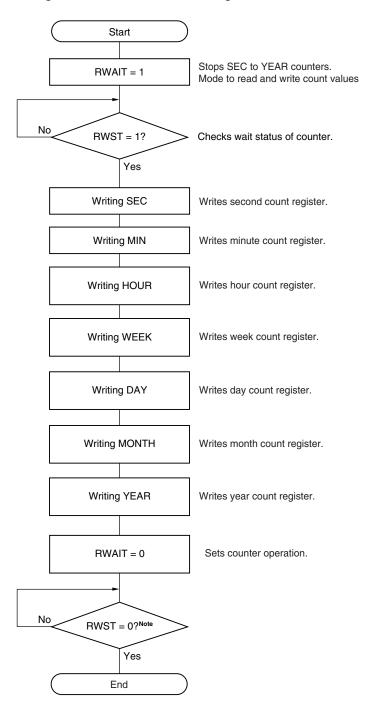

#### Figure 9-21. Procedure for Writing Real-Time Counter

**Note** Be sure to confirm that RWST = 0 before setting STOP mode.

- Caution Complete the series of operations of setting the RWAIT bit to 1 to clearing the RWAIT bit to 0 within 1 second.

- **Remark** The second count register (SEC), minute count register (MIN), hour count register (HOUR), week count register (WEEK), day count register (DAY), month count register (MONTH), and year count register (YEAR) may be written in any sequence.

All the registers do not have to be set and only some registers may be written.

| Address: FF | FA5H (CKS0 | ), FFFA6H (C | KS1) After    | reset: 00H   | R/W                   |                |                        |                                       |

|-------------|------------|--------------|---------------|--------------|-----------------------|----------------|------------------------|---------------------------------------|

| Symbol      | <7>        | 6            | 5             | 4            | 3                     | 2              | 1                      | 0                                     |

| CKSn        | PCLOEn     | 0            | 0             | 0            | CSEL                  | n CCSn         | 2 CCSn1                | CCSn0                                 |

|             |            |              |               |              |                       |                |                        |                                       |

|             | PCLOEn     |              | PCL           | .BUZn pin ou | tput enab             | e/disable spec | cification             |                                       |

|             | 0          | Output disat | ole (default) |              |                       |                |                        |                                       |

|             | 1          | Output enab  | le            |              |                       |                |                        |                                       |

|             |            |              |               | -            | 1                     |                |                        |                                       |

|             | CSELn      | CCSn2        | CCSn1         | CCSn0        |                       | PCLBUZn pin    | output clock se        | lection                               |

|             |            |              |               |              |                       | fmain =        | fmain =                | fmain =                               |

|             |            |              |               |              |                       | 5 MHz          | 10 MHz                 | 20 MHz                                |

|             | 0          | 0            | 0             | 0            | fmain                 | 5 MHz          | 10 MHz <sup>Note</sup> | Setting<br>prohibited <sup>Note</sup> |

|             | 0          | 0            | 0             | 1            | fmain/2               | 2.5 MHz        | 5 MHz                  | 10 MHz <sup>Note</sup>                |

|             | 0          | 0            | 1             | 0            | fmain/2 <sup>2</sup>  | 1.25 MHz       | 2.5 MHz                | 5 MHz                                 |

|             | 0          | 0            | 1             | 1            | fmain/2 <sup>3</sup>  | 625 kHz        | 1.25 MHz               | 2.5 MHz                               |

|             | 0          | 1            | 0             | 0            | fmain/2 <sup>4</sup>  | 312.5 kHz      | 625 kHz                | 1.25 MHz                              |

|             | 0          | 1            | 0             | 1            | fmain/2 <sup>11</sup> | 2.44 kHz       | 4.88 kHz               | 9.76 kHz                              |

|             | 0          | 1            | 1             | 0            | fmain/2 <sup>12</sup> | 1.22 kHz       | 2.44 kHz               | 4.88 kHz                              |

|             | 0          | 1            | 1             | 1            | fmain/2 <sup>13</sup> | 610 Hz         | 1.22 kHz               | 2.44 kHz                              |

|             | 1          | 0            | 0             | 0            | fsuв                  |                | 32.768 kHz             |                                       |

|             | 1          | 0            | 0             | 1            | fsuв/2                |                | 16.384 kHz             |                                       |

|             | 1          | 0            | 1             | 0            | fsub/2 <sup>2</sup>   |                | 8.192 kHz              |                                       |

|             | 1          | 0            | 1             | 1            | fsue/2 <sup>3</sup>   |                | 4.096 kHz              |                                       |

|             | 1          | 1            | 0             | 0            | fsub/24               |                | 2.048 kHz              |                                       |

|             | 1          | 1            | 0             | 1            | fs∪B/2⁵               |                | 1.024 kHz              |                                       |

|             | 1          | 1            | 1             | 0            | fsub/26               |                | 512 Hz                 |                                       |

|             | 1          | 1            | 1             | 1            | fsub/27               |                | 256 Hz                 |                                       |

# Figure 11-2. Format of Clock Output Select Register n (CKSn)

**Note** Use the output clock within a range of 10 MHz. Furthermore, when using the output clock at  $V_{DD} < 2.7$  V, use it within 5 MHz.

Cautions 1. Change the output clock after disabling clock output (PCLOEn = 0).

- To shift to STOP mode when the main system clock is selected (CSELn = 0), set PCLOEn = 0 before executing the STOP instruction. When the subsystem clock is selected (CSELn = 1), PCLOEn = 1 can be set because the clock can be output in STOP mode.

- **Remarks 1.** n = 0: 78K0R/KC3-L (48-pin), 78K0R/KD3-L

- n = 0, 1: 78K0R/KE3-L, 78K0R/KF3-L, 78K0R/KG3-L

- 2. fMAIN: Main system clock frequency

- 3. fsub: Subsystem clock frequency

# CHAPTER 14 SERIAL ARRAY UNIT

Each serial array unit has four serial channels, each of which can be used for 3-wire serial (CSI), UART, and simplified I2C communication.

Function assignment of each channel supported by the 78K0R/Kx3-L is as shown below.

• 78K0R/KC3-L, 78K0R/KD3-L, 78K0R/KE3-L

|   | Unit | Channel | Used as CSI | Used as UART               | Used as Simplified I <sup>2</sup> C |

|---|------|---------|-------------|----------------------------|-------------------------------------|

| ( | )    | 0       | CSI00       | UART0 (supporting LIN-bus) | -                                   |

|   |      | 1       | CSI01       |                            | -                                   |

|   |      | 2       | CSI10       | UART1                      | IIC10                               |

|   |      | 3       | _           |                            | _                                   |

• 78K0R/KF3-L, 78K0R/KG3-L

| Unit   | Channel | Used as CSI | Used as UART               | Used as Simplified I <sup>2</sup> C |

|--------|---------|-------------|----------------------------|-------------------------------------|

| 0      | 0       | CSI00       | UART0                      | -                                   |

|        | 1       | CSI01       |                            | _                                   |

|        | 2       | CSI10       | UART1                      | IIC10                               |

|        | 3       | -           |                            | -                                   |

| 1      | 0       | CSI20       | UART2                      | IIC20                               |

|        | 1       | -           |                            | -                                   |

|        | 2       | -           | UART3 (supporting LIN-bus) | -                                   |

|        | 3       | -           |                            | -                                   |

| 2 Note | 0       | CSI40       | UART4                      | _                                   |

|        | 1       | CSI41       |                            | _                                   |

**Note** Serial array unit 2 is only mounted in the  $\mu$  PD78F1027, 78F1028, 78F1029, and 78F1030.

When "UART0" is used for channels 0 and 1 of the unit 0, CSI00 and CSI01 cannot be used, but CSI10, UART1, or IIC10 can be used.

# (14) Input switch control register (ISC)

The ISC1 and ISC0 bits of the ISC register are used to realize a LIN-bus communication operation by UARTk in coordination with an external interrupt and the timer array unit 0.

When bit 0 is set to 1, the input signal of the serial data input (RxDk) pin is selected as an external interrupt (INTP0) that can be used to detect a wakeup signal.

When bit 1 is set to 1, the input signal of the serial data input (RxDk) pin is selected as a timer input, so that wake up signal can be detected, the low width of the sync break field, and the pulse width of the sync field can be measured by the timer.

The ISC2 bit is set to select the P52/SLTI/SLTO pin as the timer I/O pin of timer channels 0 and 1 (78K0R/KC3-L (44-pin, 48-pin), 78K0R/KD3-L, 78K0R/KE3-L only).

The ISC register can be set by a 1-bit or 8-bit memory manipulation instruction.

0

Reset signal generation clears the ISC register to 00H.

0

# Figure 14-18. Format of Input Switch Control Register (ISC)

4

Address: FFF3CH After reset: 00H R/W

Symbol ISC

| ISC2 Note 1             |                            | Selecting P52/SLTI/SL      | ΓΟ Pin as Timer I/Ο Pin |            |

|-------------------------|----------------------------|----------------------------|-------------------------|------------|

|                         | Char                       | nnel 0                     | Chan                    | inel 1     |

|                         | Input pin                  | Output pin                 | Input pin               | Output pin |

| 0                       | P00/T100 <sup>Note 2</sup> | P01/TO00 <sup>Note 2</sup> | P52/SLTI                | P52/SLTO   |

| 1                       | P52/SLTI                   | P52/SLTO                   | -                       | -          |

| Other than<br>the above | Setting prohibited         |                            |                         |            |

3 2 0 ISC2<sup>Note 1</sup>

| ISC1 | Switching channel 7 input of timer array unit 0                                                                                                                           |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | Uses the input signal of the TI07 pin as a timer input (normal operation).                                                                                                |

| 1    | Input signal of the RxDk pin is used as timer input (detects the wakeup signal and measures the low width of the sync break field and the pulse width of the sync field). |

| ISC0 | Switching external interrupt (INTP0) input                                                  |  |  |  |  |  |

|------|---------------------------------------------------------------------------------------------|--|--|--|--|--|

| 0    | Uses the input signal of the INTP0 pin as an external interrupt (normal operation).         |  |  |  |  |  |

| 1    | Uses the input signal of the RxDk pin as an external interrupt (detects the wakeup signal). |  |  |  |  |  |

Notes 1. 78K0R/KC3-L (44-pin, 48-pin), 78K0R/KD3-L, 78K0R/KE3-L only.

- 78K0R/KD3-L and 78K0R/KE3-L only. Only the P52/SLTI/SLTO pin can be assigned to channels 0 and 1 in the 78K0R/KC3-L (44-pin, 48-pin).

- Caution Be sure to clear bits 7 to 3 to "0" in the 78K0R/KC3-L (44-pin, 48-pin), 78K0R/KD3-L, and 78K0R/KE3-L. Be sure to clear bits 7 to 2 to "0" in the 78K0R/KC3-L (40-pin). Be sure to clear bits 7 to 2 to "0" in the 78K0R/KF3-L and 78K0R/KG3-L.

Remark

78K0R/KC3-L, 78K0R/KD3-L, 78K0R/KE3-L:

k = 0 (RxD0)

78K0R/KF3-L, 78K0R/KG3-L:

k = 3 (RxD3)

k = 3 (RxD

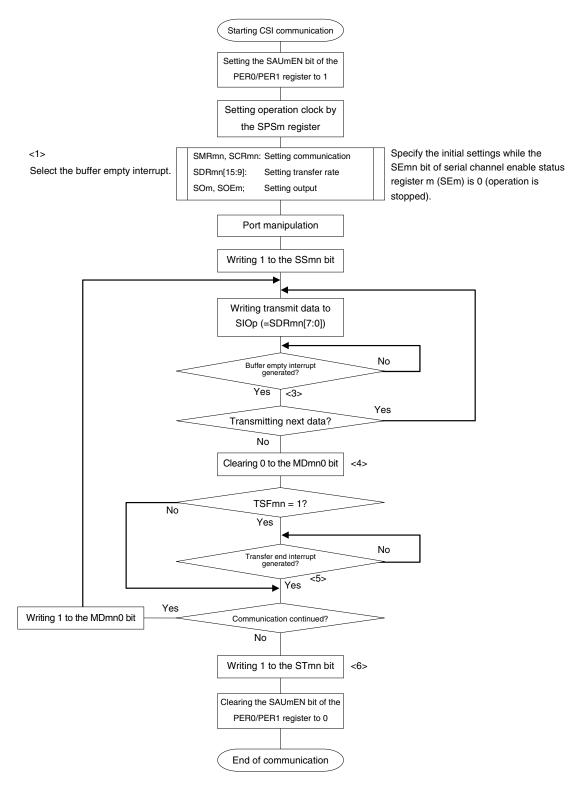

### Figure 14-35. Flowchart of Master Transmission (in Continuous Transmission Mode)

- Caution After setting the SAUmEN bit of peripheral enable register 0/1 (PER0/PER1) to 1, be sure to set serial clock select register m (SPSm) after 4 or more fcLK clocks have elapsed.

- **Remark** <1> to <6> in the figure correspond to <1> to <6> in Figure 14-34 Timing Chart of Master Transmission (in Continuous Transmission Mode).

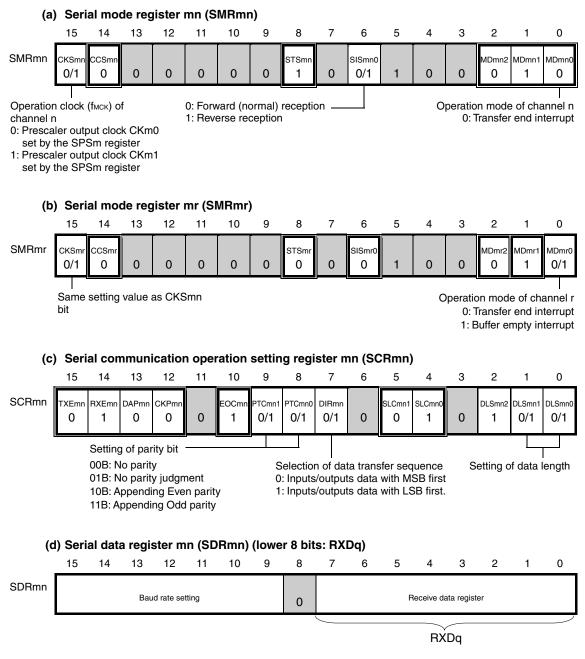

# (1) Register setting

# Figure 14-83. Example of Contents of Registers for UART Reception of UART (UART0 to UART4) (1/2)

Caution For the UART reception, be sure to set SMRmr of channel r that is to be paired with channel n.

(Remarks are listed on the next page.)

Π

Δ

IIC operation stop CKOmn bit

Step condition

SOmn bit

Δ

Δ

SOmn bit manipulation manipulation

manipulation

# (2) Processing flow

Figure 14-106. Timing Chart of Data Reception

| SSn              | nn                            |                                                       |        |

|------------------|-------------------------------|-------------------------------------------------------|--------|

| STr              | nn                            |                                                       |        |

| SEn              | nn                            |                                                       |        |

| SOEn             | nn "H"                        |                                                       |        |

| TXEm<br>RXEm     | n, TXEmn=1/RXEmn=0            | TXEmn=0/RXEmn=1                                       |        |

| SDRn             |                               | Dummy data (FFH)                                      | ve dat |

| SCLr outp        | out                           |                                                       |        |

| SDAr outp        | put                           |                                                       |        |

| SDAr inp         |                               | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |        |

| Sh<br>register n | nift                          | X X X X Shift operation X X X X                       |        |

| •                | Cr                            | η                                                     |        |

|                  |                               |                                                       |        |

| TSFn             |                               |                                                       |        |

| (b) W            | hen receiving last data       |                                                       |        |

| STmn             |                               | П                                                     |        |

| SEmn             |                               |                                                       |        |

| SOEmn -          | Output is enabled by serial   | Output is stopped by serial communication operation   |        |

| TXEmn,           | communication operation       | TXEmn = 0/RXEmn = 1                                   |        |

| RXEmn -<br>SDRmn | Dummy data (FFH) Receive data | Dummy data (FFH)                                      | data   |

| - CLr output     |                               |                                                       | Juli   |

| DAr output       |                               |                                                       |        |

| SDAr input       |                               | <u>X D6 X D5 X D4 X D3 X D2 X D1 X D0 X</u>           |        |

#### m: Unit number (m = 0, 1), n: Channel number (n = 0, 2), r: IIC number (r = 10, 20) Remark 78K0R/KC3-L, 78K0R/KD3-L, 78K0R/KE3-L: mn = 02, r = 10 78K0R/KF3-L, 78K0R/KG3-L: mn = 02, 10, r = 10, 20

Π

Shift register mn

> INTIICr TSFmn

Reception of last byte

# CHAPTER 15 SERIAL INTERFACE IICA

**Remark** 40-pin and 44-pin products of the 78K0R/KC3-L are not provided with serial interface IICA.

# **15.1 Functions of Serial Interface IICA**

Serial interface IICA has the following three modes.

# (1) Operation stop mode

This mode is used when serial transfers are not performed. It can therefore be used to reduce power consumption.

#### (2) I<sup>2</sup>C bus mode (multimaster supported)

This mode is used for 8-bit data transfers with several devices via two lines: a serial clock (SCL0) line and a serial data bus (SDA0) line.

This mode complies with the I<sup>2</sup>C bus format and the master device can generated "start condition", "address", "transfer direction specification", "data", and "stop condition" data to the slave device, via the serial data bus. The slave device automatically detects these received status and data by hardware. This function can simplify the part of application program that controls the I<sup>2</sup>C bus.

Since the SCL0 and SDA0 pins are used for open drain outputs, serial interface IICA requires pull-up resistors for the serial clock line and the serial data bus line.

### (3) Wakeup mode

The STOP mode can be released by generating an interrupt request signal (INTIICA) when an extension code from the master device or a local address has been received while in STOP mode. This can be set by using the WUP bit of IICA control register 1 (IICCTL1).

Figure 15-1 shows a block diagram of serial interface IICA.

| Figure 15-6. | Format of IICA Control Register 0 (IICCTL0) (2/4) |

|--------------|---------------------------------------------------|

|--------------|---------------------------------------------------|

| SPIE <sup>Note 1</sup>    | errupt request when stop condition is detected      |                                                                 |  |  |  |  |

|---------------------------|-----------------------------------------------------|-----------------------------------------------------------------|--|--|--|--|

| 0                         | Disable                                             |                                                                 |  |  |  |  |

| 1                         | Enable                                              |                                                                 |  |  |  |  |

| If the WUP                | bit of IICA control register 1 (IICCTL1) is 1, no s | stop condition interrupt will be generated even if $SPIE = 1$ . |  |  |  |  |

| Condition for             | or clearing (SPIE = 0)                              | Condition for setting (SPIE = 1)                                |  |  |  |  |

| Cleared by                | y instruction                                       | Set by instruction                                              |  |  |  |  |

| <ul> <li>Reset</li> </ul> |                                                     |                                                                 |  |  |  |  |

| WTIM <sup>Note 1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Control of wait and interrupt request generation                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Interrupt request is generated at the eighth clock's falling edge.<br>Master mode: After output of eight clocks, clock output is set to low level and wait is set.<br>Slave mode: After input of eight clocks, the clock is set to low level and wait is set for master device.                              |  |  |  |  |  |  |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <ul> <li>Interrupt request is generated at the ninth clock's falling edge.</li> <li>Master mode: After output of nine clocks, clock output is set to low level and wait is set.</li> <li>Slave mode: After input of nine clocks, the clock is set to low level and wait is set for master device.</li> </ul> |  |  |  |  |  |  |

| An interrupt is generated at the falling edge of the ninth clock during address transfer independently of the setting of this bit. The setting of this bit is valid when the address transfer is completed. When in master mode, a wait is inserted at the falling edge of the ninth clock during address transfers. For a slave device that has received a local address, a wait is inserted at the falling edge of the falling edge of the ninth clock after an acknowledge (ACK) is issued. However, when the slave device has received an extension code, a wait is inserted at the falling edge of the eighth clock. |                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| Condition for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Condition for clearing (WTIM = 0) Condition for setting (WTIM = 1)                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| Cleared by instruction     Set by instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| Condition for clearing ( $W   IW = 0$ ) | Condition for setting ( $W   IW = 1$ ) |

|-----------------------------------------|----------------------------------------|

| Cleared by instruction                  | Set by instruction                     |

| • Reset                                 |                                        |

|                                         |                                        |

| ACKE <sup>Notes 1, 2</sup>                             | Acknowledgment control                      |                                                |  |  |  |  |

|--------------------------------------------------------|---------------------------------------------|------------------------------------------------|--|--|--|--|

| 0                                                      | Disable acknowledgment.                     |                                                |  |  |  |  |

| 1                                                      | Enable acknowledgment. During the ninth clo | ock period, the SDA0 line is set to low level. |  |  |  |  |

| Condition for                                          | or clearing (ACKE = 0)                      | Condition for setting (ACKE = 1)               |  |  |  |  |

| <ul><li>Cleared by instruction</li><li>Reset</li></ul> |                                             | Set by instruction                             |  |  |  |  |

Notes 1. The signal of this bit is invalid while IICE0 is 0. Set this bit during that period.

2. The set value is invalid during address transfer and if the code is not an extension code. When the device serves as a slave and the addresses match, an acknowledgment is generated regardless of the set value.

# (3) Priority specification flag registers (PR00L, PR00H, PR01L, PR01H, PR02L, PR10L, PR10H, PR11L, PR11H, PR12L)

The priority specification flag registers are used to set the corresponding maskable interrupt priority level.

A priority level is set by using the PR0xy and PR1xy registers in combination (xy = 0L, 0H, 1L, 1H, or 2L).

The PR00L, PR00H, PR01L, PR01H, PR02L, PR10L, PR10H, PR11L, PR11H, and PR12L registers can be set by a 1-bit or 8-bit memory manipulation instruction. If the PR00L and PR00H, PR01L and PR01H, PR10L and PR10H, and PR11L and PR11H registers are combined to form 16-bit registers PR00, PR01, PR10, and PR11, they can be set by a 16-bit memory manipulation instruction. Using the PR02L register as the PR02 register and the PR12L register can be set also by using a 16-bit memory manipulation instruction. Reset signal generation sets these registers to FFH.

**Remark** If an instruction that writes data to this register is executed, the number of instruction execution clocks increases by 2 clocks.

# Figure 18-4. Format of Priority Specification Flag Registers (PR00L, PR00H, PR01L, PR01H, PR02L, PR10L, PR10H, PR11L, PR11H, PR12L) (1/2)

| Address: FFFE8H After reset: FFH R/W |            |            |          |         |         |         |         |         |  |  |  |

|--------------------------------------|------------|------------|----------|---------|---------|---------|---------|---------|--|--|--|

| Symbol                               | <7>        | <6>        | <5>      | <4>     | <3>     | <2>     | <1>     | <0>     |  |  |  |

| PR00L                                | PPR05      | PPR04      | PPR03    | PPR02   | PPR01   | PPR00   | LVIPR0  | WDTIPR0 |  |  |  |

|                                      |            |            |          |         |         |         |         |         |  |  |  |

| Address: FFFECH After reset: FFH R/W |            |            |          |         |         |         |         |         |  |  |  |

| Symbol                               | <7>        | <6>        | <5>      | <4>     | <3>     | <2>     | <1>     | <0>     |  |  |  |

| PR10L                                | PPR15      | PPR14      | PPR13    | PPR12   | PPR11   | PPR10   | LVIPR1  | WDTIPR1 |  |  |  |

|                                      |            |            |          |         |         |         |         |         |  |  |  |

| Address: FFI                         | FE9H After | reset: FFH | R/W      |         |         |         |         |         |  |  |  |

| Symbol                               | <7>        | <6>        | <5>      | <4>     | <3>     | <2>     | <1>     | 0       |  |  |  |

| PR00H                                | SREPR00    | SRPR00     | STPR00   | DMAPR01 | DMAPR00 | CMPPR01 | CMPPR00 | 1       |  |  |  |

|                                      |            | CSIPR001   | CSIPR000 |         |         |         |         |         |  |  |  |

|                                      |            |            |          |         |         |         |         |         |  |  |  |

| Address: FFI                         | EDH After  | reset: FFH | R/W      |         |         |         |         |         |  |  |  |

| Symbol                               | <7>        | <6>        | <5>      | <4>     | <3>     | <2>     | <1>     | 0       |  |  |  |

| PR10H                                | SREPR10    | SRPR10     | STPR10   | DMAPR11 | DMAPR10 | CMPPR11 | CMPPR10 | 1       |  |  |  |

|                                      |            | CSIPR101   | CSIPR100 |         |         |         |         |         |  |  |  |

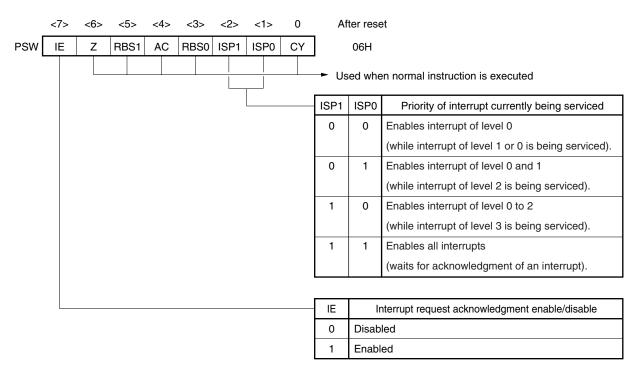

# (5) Program status word (PSW)

The program status word is a register used to hold the instruction execution result and the current status for an interrupt request. The IE flag that sets maskable interrupt enable/disable and the ISP0 and ISP1 flags that controls multiple interrupt servicing are mapped to the PSW.

Besides 8-bit read/write, this register can carry out operations using bit manipulation instructions and dedicated instructions (EI and DI). When a vectored interrupt request is acknowledged, if the BRK instruction is executed, the contents of the PSW are automatically saved into a stack and the IE flag is reset to 0. If a maskable interrupt request is acknowledged, the contents of the priority specification flag of the acknowledged interrupt are transferred to the ISP0 and ISP1 flags. The PSW contents are also saved into the stack with the PUSH PSW instruction. They are restored from the stack with the RETI, RETB, and POP PSW instructions.

Reset signal generation sets PSW to 06H.

# Figure 18-11. Configuration of Program Status Word

| Instruction         | Mnemonic | Operands                 | Bytes | Clo                   | cks    | Operation                                                                           |   | Flag | J  |

|---------------------|----------|--------------------------|-------|-----------------------|--------|-------------------------------------------------------------------------------------|---|------|----|

| Group               |          |                          |       | Note 1                | Note 2 |                                                                                     |   | AC   | CY |

| Stack<br>manipulate | PUSH     | PSW                      | 2     | 1                     | -      | $(SP - 1) \leftarrow PSW, (SP - 2) \leftarrow 00H,$<br>$SP \leftarrow SP - 2$       |   |      |    |

|                     |          | rp                       | 1     | 1                     | _      | $(SP - 1) \leftarrow rp_{H}, (SP - 2) \leftarrow rp_{L},$<br>$SP \leftarrow SP - 2$ |   |      |    |

|                     | POP      | PSW                      | 2     | 3                     | _      | $PSW \gets (SP + 1),  SP \gets SP + 2$                                              | R | R    | R  |

|                     |          | rp                       | 1     | 1                     | -      | $rp_{L} \leftarrow (SP),  rp_{H} \leftarrow (SP + 1),  SP \leftarrow SP + 2$        |   |      |    |

|                     | MOVW     | SP, #word                | 4     | 1                     | -      | $SP \gets word$                                                                     |   |      |    |

|                     |          | SP, AX                   | 2     | 1                     | -      | $SP \gets AX$                                                                       |   |      |    |

|                     |          | AX, SP                   | 2     | 1                     | -      | $AX \gets SP$                                                                       |   |      |    |

|                     |          | HL, SP                   | 3     | 1                     | -      | $HL \leftarrow SP$                                                                  |   |      |    |

|                     |          | BC, SP                   | 3     | 1                     | -      | $BC \leftarrow SP$                                                                  |   |      |    |

|                     |          | DE, SP                   | 3     | 1                     | -      | $DE \leftarrow SP$                                                                  |   |      |    |

|                     | ADDW     | SP, #byte                | 2     | 1                     | -      | $SP \leftarrow SP + byte$                                                           |   |      |    |

|                     | SUBW     | SP, #byte                | 2     | 1                     | -      | $SP \leftarrow SP$ – byte                                                           |   |      |    |

| Unconditio          | BR       | AX                       | 2     | 3                     | -      | $PC \gets CS, AX$                                                                   |   |      |    |

| nal branch          |          | \$addr20                 | 2     | 3                     | -      | $PC \leftarrow PC + 2 + jdisp8$                                                     |   |      |    |

|                     |          | \$!addr20                | 3     | 3                     | -      | $PC \leftarrow PC + 3 + jdisp16$                                                    |   |      |    |

|                     |          | !addr16                  | 3     | 3                     | -      | PC ← 0000, addr16                                                                   |   |      |    |

|                     |          | !!addr20                 | 4     | 3                     | -      | $PC \leftarrow addr20$                                                              |   |      |    |

| Conditional         | BC       | \$addr20                 | 2     | 2/4 <sup>Note 3</sup> | -      | $PC \leftarrow PC + 2 + jdisp8$ if $CY = 1$                                         |   |      |    |

| branch              | BNC      | \$addr20                 | 2     | 2/4 <sup>Note 3</sup> | -      | $PC \leftarrow PC + 2 + jdisp8$ if $CY = 0$                                         |   |      |    |

|                     | BZ       | \$addr20                 | 2     | 2/4 <sup>Note 3</sup> | -      | $PC \leftarrow PC + 2 + jdisp8$ if $Z = 1$                                          |   |      |    |

|                     | BNZ      | \$addr20                 | 2     | 2/4 <sup>Note 3</sup> | -      | $PC \leftarrow PC + 2 + jdisp8 \text{ if } Z = 0$                                   |   |      |    |

|                     | BH       | \$addr20                 | 3     | 2/4 <sup>Note 3</sup> | -      | $PC \gets PC\text{+}3\text{+}jdisp8 \text{ if } (Z \lor CY)\text{=}0$               |   |      |    |

|                     | BNH      | \$addr20                 | 3     | 2/4 <sup>Note 3</sup> | -      | $PC \gets PC\text{+}3\text{+}jdisp8 \text{ if } (Z \lor CY)\text{=}1$               |   |      |    |

|                     | BT       | saddr.bit, \$addr20      | 4     | 3/5 <sup>Note 3</sup> | -      | $PC \leftarrow PC + 4 + jdisp8$ if (saddr).bit = 1                                  |   |      |    |

|                     |          | sfr.bit, \$addr20        | 4     | 3/5 <sup>Note 3</sup> | -      | $PC \leftarrow PC + 4 + jdisp8$ if sfr.bit = 1                                      |   |      |    |

|                     |          | A.bit, \$addr20          | 3     | 3/5 <sup>Note 3</sup> | _      | $PC \leftarrow PC + 3 + jdisp8$ if A.bit = 1                                        |   |      |    |

|                     |          | PSW.bit, \$addr20        | 4     | 3/5 <sup>Note 3</sup> | _      | $PC \leftarrow PC + 4 + jdisp8$ if PSW.bit = 1                                      |   |      |    |

|                     |          | [HL].bit, \$addr20       | 3     | 3/5 <sup>Note 3</sup> | 6/7    | $PC \leftarrow PC + 3 + jdisp8$ if (HL).bit = 1                                     |   |      |    |

|                     |          | ES:[HL].bit,<br>\$addr20 | 4     | 4/6 <sup>Note 3</sup> | 7/8    | $PC \leftarrow PC + 4 + jdisp8$<br>if (ES, HL).bit = 1                              |   |      |    |

**Notes 1.** When the internal RAM area, SFR area, or extended SFR area is accessed, or for an instruction with no data access.

- 2. When the program memory area is accessed.

- 3. This indicates the number of clocks "when condition is not met/when condition is met".

2. This number of clocks is for when the program is in the internal ROM (flash memory) area. When fetching an instruction from the internal RAM area, the number of clocks is twice the number of clocks plus 3, maximum.

**Remarks 1.** One instruction clock cycle is one cycle of the CPU clock (fcPU) selected by the system clock control register (CKC).

# Caution The pins mounted depend on the product. Refer to Caution 2 at the beginning of this chapter.

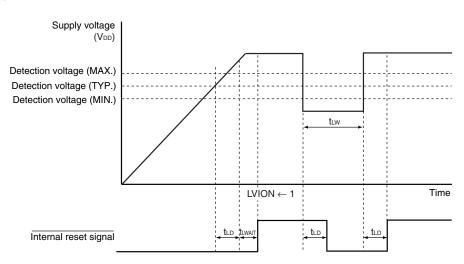

#### 30.6.9 LVI circuit characteristics

#### (TA = -40 to +85°C, VPDR $\leq$ VDD = EVDD $\leq$ 5.5 V, Vss = EVss = 0 V)

|              | Parameter                                 | Symbol         | Conditions                                     | MIN. | TYP. | MAX. | Unit |

|--------------|-------------------------------------------|----------------|------------------------------------------------|------|------|------|------|

| Detection    | Supply voltage level                      | VLVIO          |                                                | 4.12 | 4.22 | 4.32 | V    |

| voltage      |                                           | VLVI1          |                                                | 3.97 | 4.07 | 4.17 | V    |

|              |                                           | VLVI2          |                                                | 3.82 | 3.92 | 4.02 | V    |

|              |                                           | VLVI3          |                                                | 3.66 | 3.76 | 3.86 | V    |

|              |                                           | VLVI4          |                                                | 3.51 | 3.61 | 3.71 | V    |

|              |                                           | VLVI5          |                                                | 3.35 | 3.45 | 3.55 | V    |

|              |                                           | VLVI6          |                                                | 3.20 | 3.30 | 3.40 | V    |

|              |                                           | VLVI7          |                                                | 3.05 | 3.15 | 3.25 | V    |

|              |                                           | VLVI8          |                                                | 2.89 | 2.99 | 3.09 | V    |

|              |                                           | VLVI9          |                                                | 2.74 | 2.84 | 2.94 | V    |

|              |                                           | VLVI10         |                                                | 2.58 | 2.68 | 2.78 | V    |

|              |                                           | VLVI11         |                                                | 2.43 | 2.53 | 2.63 | V    |

|              |                                           | VLVI12         |                                                | 2.28 | 2.38 | 2.48 | V    |

|              |                                           | VLVI13         |                                                | 2.12 | 2.22 | 2.32 | V    |

|              |                                           | VLVI14         |                                                | 1.97 | 2.07 | 2.17 | V    |

|              |                                           | VLVI15         |                                                | 1.81 | 1.91 | 2.01 | V    |

|              | External input pinNote 1                  | VEXLVI         | EXLVI < V_DD, 1.8 V $\leq$ VDD $\leq$ 5.5 V    | 1.11 | 1.21 | 1.31 | V    |

|              | Power supply voltage on power application | VPUPLVI        | When LVI default start function enabled is set | 1.87 | 2.07 | 2.27 | V    |

| Minimum pu   | lse width                                 | t∟w            |                                                | 200  |      |      | μs   |

| Detection de | elay time                                 | tld            |                                                |      |      | 200  | μs   |

| Operation st | abilization wait time <sup>Note 2</sup>   | <b>t</b> lwait |                                                |      |      | 10   | μs   |

Notes 1. The EXLVI/P120/INTP0 pin is used.

2. Time required from setting bit 7 (LVION) of the low-voltage detection register (LVIM) to 1 to operation stabilization

$\label{eq:keylinear} \begin{array}{ll} \mbox{Remark} & V_{LVI(n-1)} > V_{LVIn} \mbox{:} n = 1 \mbox{ to } 15 \end{array}$

### **LVI Circuit Timing**