# E. Renesas Electronics America Inc - UPD78F1009GB-GAH-AX Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2000                       |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Not For New Designs                                                                  |

| Core Processor             | 78K/0R                                                                               |

| Core Size                  | 16-Bit                                                                               |

| Speed                      | 20MHz                                                                                |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                     |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                              |

| Number of I/O              | 50                                                                                   |

| Program Memory Size        | 64KB (64K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 3K x 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                          |

| Data Converters            | A/D 12x10b                                                                           |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 64-LQFP                                                                              |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f1009gb-gah-ax |

|                            |                                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## How to Use This Manual

| Readers                 | This manual is intended for user engineers who wish to understand the functions of the 78K0R/Kx3-L and design and develop application systems and programs for these devices.                 |                                                          |  |  |  |  |  |  |  |  |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--|--|--|--|--|--|--|--|

|                         | The target products are as follows.                                                                                                                                                           |                                                          |  |  |  |  |  |  |  |  |

|                         | <ul> <li>78K0R/KC3-L: μPD78F1000, 78F100</li> </ul>                                                                                                                                           | 01 78E1002 78E1003                                       |  |  |  |  |  |  |  |  |

|                         | <ul> <li>78K0R/KD3-L: μPD78F1004, 78F100</li> </ul>                                                                                                                                           |                                                          |  |  |  |  |  |  |  |  |

|                         | <ul> <li>78K0R/KE3-L: μPD78F1007, 78F100</li> </ul>                                                                                                                                           |                                                          |  |  |  |  |  |  |  |  |

|                         |                                                                                                                                                                                               |                                                          |  |  |  |  |  |  |  |  |

|                         | • 78K0R/KF3-L: μPD78F1010, 78F101                                                                                                                                                             |                                                          |  |  |  |  |  |  |  |  |

|                         | <ul> <li>78K0R/KG3-L: μPD78F1013, 78F10</li> </ul>                                                                                                                                            | 14, 76-1029, 76-1030                                     |  |  |  |  |  |  |  |  |

| Purpose                 | This manual is intended to give users an                                                                                                                                                      | n understanding of the functions described in the        |  |  |  |  |  |  |  |  |

|                         | Organization below.                                                                                                                                                                           |                                                          |  |  |  |  |  |  |  |  |

| Organization            | The 78K0R/Kx3-L manual is separated edition (common to the 78K0R Microcontr                                                                                                                   | into two parts: this manual and the instructions oller). |  |  |  |  |  |  |  |  |

|                         | 78K0R/Kx3-L                                                                                                                                                                                   | 78K0R Microcontroller                                    |  |  |  |  |  |  |  |  |

|                         | User's Manual                                                                                                                                                                                 | User's Manual                                            |  |  |  |  |  |  |  |  |

|                         | (This Manual)                                                                                                                                                                                 | Instructions                                             |  |  |  |  |  |  |  |  |

|                         |                                                                                                                                                                                               |                                                          |  |  |  |  |  |  |  |  |

|                         | Pin functions                                                                                                                                                                                 | CPU functions                                            |  |  |  |  |  |  |  |  |

|                         | <ul> <li>Internal block functions</li> </ul>                                                                                                                                                  | Instruction set                                          |  |  |  |  |  |  |  |  |

|                         | Interrupts                                                                                                                                                                                    | <ul> <li>Explanation of each instruction</li> </ul>      |  |  |  |  |  |  |  |  |

|                         | <ul> <li>Other on-chip peripheral functions</li> </ul>                                                                                                                                        |                                                          |  |  |  |  |  |  |  |  |

|                         | Electrical specifications                                                                                                                                                                     |                                                          |  |  |  |  |  |  |  |  |

| How to Read This Manual |                                                                                                                                                                                               | manual have general knowledge of electrical              |  |  |  |  |  |  |  |  |

|                         | engineering, logic circuits, and microcontro                                                                                                                                                  |                                                          |  |  |  |  |  |  |  |  |

|                         | To gain a general understanding of fun                                                                                                                                                        |                                                          |  |  |  |  |  |  |  |  |

|                         | $\rightarrow$ Read this manual in the order of the <b>CONTENTS</b> . The mark " <r>" shows major revised points. The revised points can be easily searched by copying an "<r>" in the</r></r> |                                                          |  |  |  |  |  |  |  |  |

|                         | PDF file and specifying it in the "Fine                                                                                                                                                       | d what:" field.                                          |  |  |  |  |  |  |  |  |

|                         | How to interpret the register format:                                                                                                                                                         |                                                          |  |  |  |  |  |  |  |  |

|                         | → For a bit number enclosed in angle brackets, the bit name is defined as a reserved<br>word in the RA78K0R, and is defined as an sfr variable using the #pragma sfr                          |                                                          |  |  |  |  |  |  |  |  |

|                         | directive in the CC78K0R.                                                                                                                                                                     |                                                          |  |  |  |  |  |  |  |  |

|                         | To know details of the 78K0R Microcor                                                                                                                                                         |                                                          |  |  |  |  |  |  |  |  |

|                         | $\rightarrow$ Refer to the separate document <b>78</b><br>(U17792E).                                                                                                                          | KOR Microcontroller Instructions User's Manual           |  |  |  |  |  |  |  |  |

|                         |                                                                                                                                                                                               |                                                          |  |  |  |  |  |  |  |  |

## CONTENTS

| CHAPT | TER 1 OUTLINE                                               |    |

|-------|-------------------------------------------------------------|----|

| 1.1   | Features                                                    |    |

| 1.2   | Applications                                                | 24 |

| 1.3   | Ordering Information                                        | 24 |

| 1.4   | Pin Configuration (Top View)                                | 25 |

|       | 1.4.1 78K0R/KC3-L                                           | 25 |

|       | 1.4.2 78K0R/KD3-L                                           |    |

|       | 1.4.3 78K0R/KE3-L                                           |    |

|       | 1.4.4 78K0R/KF3-L                                           |    |

|       | 1.4.5 78K0R/KG3-L                                           | 32 |

| 1.5   | Pin Identification                                          | 35 |

| 1.6   | Block Diagram                                               |    |

|       | 1.6.1 78K0R/KC3-L                                           |    |

|       | 1.6.2 78K0R/KD3-L                                           | 39 |

|       | 1.6.3 78K0R/KE3-L                                           | 40 |

|       | 1.6.4 78K0R/KF3-L                                           | 41 |

|       | 1.6.5 78K0R/KG3-L                                           | 42 |

| 1.7   | Outline of Functions                                        | 43 |

|       | 1. 7. 1 78K0R/KC3-L, 78K0R/KD3-L, 78K0R/KE3-L               | 43 |

|       | 1. 7. 2 78K0R/KF3-L, 78K0R/KG3-L                            | 45 |

| СНАРТ | TER 2 PIN FUNCTIONS (78K0R/KC3-L, 78K0R/KD3-L, 78K0R/KE3-L) | 47 |

| 2.1   | Pin Function List                                           | 47 |

|       | 2.1.1 78K0R/KC3-L (40-pin products)                         | 48 |

|       | 2.1.2 78K0R/KC3-L (44-pin and 48-pin products)              | 52 |

|       | 2.1.3 78K0R/KD3-L                                           | 57 |

|       | 2.1.4 78K0R/KE3-L                                           | 62 |

| 2.2   | Description of Pin Functions                                | 67 |

|       | 2.2.1 P00, P01 (port 0)                                     | 67 |

|       | 2.2.2 P10 to P17 (port 1)                                   | 68 |

|       | 2.2.3 P20 to P27 (port 2)                                   | 69 |

|       | 2.2.4 P30 to P33 (port 3)                                   | 70 |

|       | 2.2.5 P40 to P43 (port 4)                                   | 71 |

| Pin Name             | I/O Circuit Type | I/O | Recommended Connection of Unused Pins                                                                                                                                                                                        |

|----------------------|------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P60/SCL0<br>P61/SDA0 | 13-R             | I/O | Input: Independently connect to EV <sub>DD</sub> or EV <sub>SS</sub> via a resistor, or connect directly to EV <sub>SS</sub> .                                                                                               |

| POI/SDAU             |                  |     | Output: Set the port output latch to 0 and leave open with low level out put.                                                                                                                                                |

| P70/KR0/SO01/INTP4   | 8-R              |     | Input: Independently connect to EVDD or EVSS via a resistor.<br>Output: Leave open.<br><when n-ch="" open-drain=""><br/>Set the port output latch to 0 and leave open with low level out put.</when>                         |

| P71/KR1/SI01/INTP5   | 5-AN             |     | Input: Independently connect to EV <sub>DD</sub> or EV <sub>SS</sub> via a resistor.<br>Output: Leave open.                                                                                                                  |

| P72/KR2/SCK01/INTP6  |                  |     | Input: Independently connect to EVDD or EVSS via a resistor.                                                                                                                                                                 |

| P73/KR3/SO00/TxD0    | 8-R              |     | Output: Leave open.<br><when n-ch="" open-drain=""><br/>Set the port output latch to 0 and leave open with low level out put.</when>                                                                                         |

| P74/KR4/SI00/RxD0    | 5-AN             |     | Input: Independently connect to EVDD or EVSS via a resistor.<br>Output: Leave open.                                                                                                                                          |

| P75/KR5/SCK00        |                  |     | Input: Independently connect to EV <sub>DD</sub> or EV <sub>SS</sub> via a resistor.<br>Output: Leave open.<br><when n-ch="" open-drain=""><br/>Set the port output latch to 0 and leave open with low level out put.</when> |

| P76/KR6              | 8-R              |     | Input: Independently connect to EVDD or EVSS via a resistor.                                                                                                                                                                 |

| P77/KR7              |                  |     | Output: Leave open.                                                                                                                                                                                                          |

| P80/CMP0P/INTP3/PGAI | 11-J             | ]   | Input: Independently connect to AVREF or AVss via a resistor.                                                                                                                                                                |

| P81/CMP0M            | 11-H             | ]   | Output: Leave open.                                                                                                                                                                                                          |

| P82/CMP1P/INTP7      | 11-I             | ]   |                                                                                                                                                                                                                              |

| P83/CMP1M            | 11-H             | ]   |                                                                                                                                                                                                                              |

| P120/INTP0/EXLVI     | 8-R              |     | Input: Independently connect to EV <sub>DD</sub> or EV <sub>SS</sub> via a resistor.<br>Output: Leave open.                                                                                                                  |

Table 2-3. Connection of Unused Pins (2/3)

Remark With products not provided with an EVDD or EVss pin, replace EVDD with VDD, or replace EVss with Vss.

| Symbol | 7    | 6    | 5    | 4    | 3      | 2         | 1           | 0           | Address | After reset | R/W |

|--------|------|------|------|------|--------|-----------|-------------|-------------|---------|-------------|-----|

| PU0    | 0    | 0    | 0    | 0    | 0      | 0         | PU01        | PU00        | F0030H  | 00H         | R/W |

|        |      |      |      |      | -      |           | _           |             |         |             |     |

| PU1    | PU17 | PU16 | PU15 | PU14 | PU13   | PU12      | PU11        | PU10        | F0031H  | 00H         | R/W |

|        |      |      |      |      |        |           |             |             |         |             |     |

| PU3    | 0    | 0    | 0    | 0    | PU33   | PU32      | PU31        | PU30        | F0033H  | 00H         | R/W |

|        |      |      |      |      |        |           |             |             |         |             |     |

| PU4    | 0    | 0    | 0    | 0    | PU43   | PU42      | PU41        | PU40        | F0034H  | 00H         | R/W |

|        |      |      |      |      |        |           |             |             |         |             |     |

| PU5    | 0    | 0    | 0    | 0    | PU53   | PU52      | PU51        | PU50        | F0035H  | 00H         | R/W |

|        |      |      |      |      |        |           |             |             |         |             |     |

| PU7    | PU77 | PU76 | PU75 | PU74 | PU73   | PU72      | PU71        | PU70        | F0037H  | 00H         | R/W |

|        |      |      |      |      |        |           |             |             |         |             |     |

| PU12   | 0    | 0    | 0    | 0    | 0      | 0         | 0           | PU120       | F003CH  | 00H         | R/W |

|        |      |      |      |      |        |           |             |             |         |             |     |

| PU14   | 0    | 0    | 0    | 0    | 0      | 0         | PU141       | 0           | F003EH  | 00H         | R/W |

|        |      |      |      |      |        |           |             |             |         |             |     |

|        | PUmn |      |      |      | Pmn pi | n on-chip | pull-up res | istor selec | tion    |             |     |

## Figure 5-38. Format of Pull-up Resistor Option Register (78K0R/KE3-L)

| PUmn | Pmn pin on-chip pull-up resistor selection |  |  |  |  |  |  |  |  |

|------|--------------------------------------------|--|--|--|--|--|--|--|--|

|      | (m = 0, 1, 3 to 5, 7, 12, 14 ; n = 0 to 7) |  |  |  |  |  |  |  |  |

| 0    | On-chip pull-up resistor not connected     |  |  |  |  |  |  |  |  |

| 1    | On-chip pull-up resistor connected         |  |  |  |  |  |  |  |  |

| Address: FF | FA0H Afte       | r reset: 00H  | R/W             |                            |                                      |               |                      |      |  |  |  |

|-------------|-----------------|---------------|-----------------|----------------------------|--------------------------------------|---------------|----------------------|------|--|--|--|

| Symbol      | 7               | 6             | 5 4             |                            | 3                                    | 2             | 1                    | 0    |  |  |  |

| CMC         | EXCLK           | OSCSEL        | 0               | OSCSELS<br>Note            | 0                                    | AMPHS1        | AMPHS0               | AMPH |  |  |  |

|             | EXCLK           | OSCSEL        |                 | system clock<br>ation mode | X1/P                                 | 121 pin       | X2/EXCLK/P122 pin    |      |  |  |  |

|             | 0               | 0             | Input port m    | ode                        | Input port                           | Input port    |                      |      |  |  |  |

|             | 0               | 1             | X1 oscillatio   | n mode                     | Crystal/ceramic resonator connection |               |                      |      |  |  |  |

|             | 1               | 0             | Input port m    | ode                        | Input port                           |               |                      |      |  |  |  |

|             | 1               | 1             | External clo    | ck input mode              | Input port                           |               | External clock input |      |  |  |  |

|             |                 |               |                 |                            |                                      |               |                      |      |  |  |  |

|             | OSCSELS<br>Note | Subsystem     | i clock pin ope | eration mode               | XT1/F                                | P123 pin      | XT2/P124 pin         |      |  |  |  |

|             | 0               | Input port m  | ode             |                            | Input port                           |               |                      |      |  |  |  |

|             | 1               | XT1 oscillati | on mode         |                            | Crystal res                          | onator connec | ction                |      |  |  |  |

|             |                 |               |                 |                            |                                      |               |                      |      |  |  |  |

|             | AMPHS1          | AMPHS0        |                 | XT1 os                     | scillator oscillation mode selection |               |                      |      |  |  |  |

|             | 0               | 0             |                 |                            |                                      |               |                      |      |  |  |  |

## Figure 7-4. Format of Clock Operation Mode Control Register (CMC)

| AMPHS1 | AMPHS0 | XT1 oscillator oscillation mode selection   |

|--------|--------|---------------------------------------------|

| 0      | 0      | Low power consumption oscillation (default) |

| 0      | 1      | Normal oscillation                          |

| 1      | 0      | Ultra-low power consumption oscillation     |

| 1      | 1      |                                             |

| AMPH | Control of X1 clock oscillation frequency  |

|------|--------------------------------------------|

| 0    | $2 \text{ MHz} \le f_x \le 10 \text{ MHz}$ |

| 1    | $10 \text{ MHz} < f_X \le 20 \text{ MHz}$  |

Note OSCSELS bit is not provided in the 78K0R/KC3-L (40-pin). In the 78K0R/KC3-L (40-pin), bit 4 is fixed to 0.

Cautions 1. The CMC register can be written only once after reset release, by an 8-bit memory manipulation instruction.

- 2. After reset release, set the CMC register before X1 or XT1 oscillation is started as set by the clock operation status control register (CSC).

- 3. Be sure to set the AMPH bit to 1 if the X1 clock oscillation frequency exceeds 10 MHz.

- 4. When the CMC register is used at the default value (00H), be sure to set 00H to this register after reset release in order to prevent malfunctioning during a program loop.

- 5. The XT1 oscillator is a circuit with low amplification in order to achieve low-power consumption. Note the following points when designing the circuit.

- Pins and circuit boards include parasitic capacitance. Therefore, perform oscillation evaluation using a circuit board to be actually used and confirm that there are no problems.

- When using the ultra-low power consumption oscillation (AMPHS1 = 1) as the mode of the XT1 oscillator, use the recommended resonators described in CHAPTER 30 ELECTRICAL SPECIFICATIONS (78K0R/KC3-L, 78K0R/KD3-L, 78K0R/KE3-L) or CHAPTER 31 ELECTRICAL SPECIFICATIONS (78K0R/KF3-L, 78K0R/KG3-L).

(Cautions and Remark are given on the next page.)

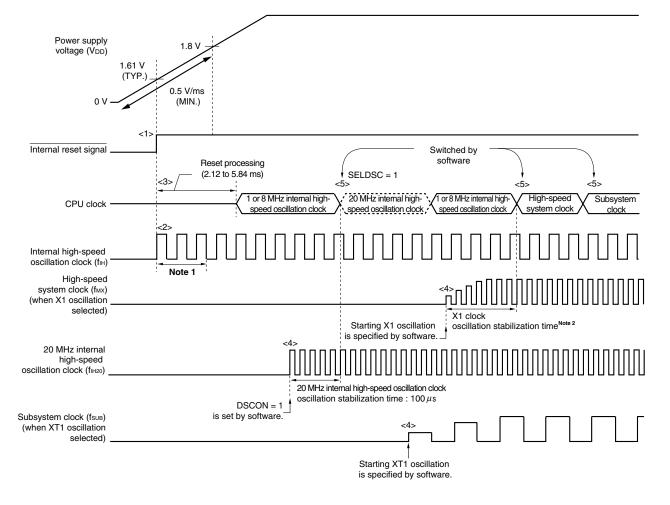

## Figure 7-16. Clock Generator Operation When Power Supply Voltage Is Turned On (When LVI Default Start Function Stopped Is Set (Option Byte: LVIOFF = 1))

- <1> When the power is turned on, an internal reset signal is generated by the power-on-clear (POC) circuit.

- <2> When the power supply voltage exceeds 1.61 V (TYP.), the reset is released and the internal high-speed oscillator <sup>Note 3</sup> automatically starts oscillation.

- <3> The CPU starts operation on the internal high-speed oscillation clock <sup>Note 3</sup> after a reset processing such as waiting for the voltage of the power supply or regulator to stabilize has been performed after reset release.

- <4> Set the start of oscillation of the X1 or XT1 clock <sup>Note 4</sup> via software (see **7.6.4 Example of setting X1 oscillation clock** and **7.6.5 Example of setting XT1 oscillation clock**). Switch to oscillation using the 20 MHz internal high-speed oscillation clock after confirming that the power supply voltage is at least 2.7 V and setting the DSCON bit to 1 by using software.

- <5> When switching the CPU clock to the X1 or XT1 clock, wait for the clock oscillation to stabilize, and then set switching via software (see 7.6.4 Example of setting X1 oscillation clock and 7.6.5 Example of setting XT1 oscillation clock).

Switch to the 20 MHz internal high-speed oscillation clock by setting the DSCON bit (bit 0 of the 20 MHz internal high-speed oscillation control register (DSCCTL)), waiting for 100  $\mu$ s, and then setting the SELDSC bit to 1 by using software <sup>Note 5</sup>.

(Notes and Cautions are listed on the next page.)

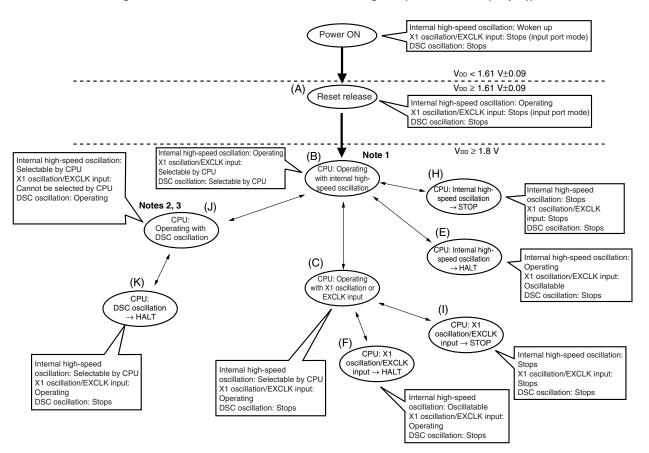

## 7.6.6 CPU clock status transition diagram

Figure 7-18 and Figure 7-19 show the CPU clock status transition diagram of this product.

- **Notes 1.** After reset release, an operation at one of the following operating frequencies is started, because  $f_{CLK} = f_{IH}/2$  has been selected by setting the system clock control register (CKC) to 09H.

- When 1 MHz has been selected by using the option byte: 500 kHz (1 MHz/2)

- When 8 MHz or 20 MHz has been selected by using the option byte: 4 MHz (8 MHz/2)

- 2. Specify 20 MHz internal oscillation after checking that VDD is at least 2.7 V.

- 3. 20 MHz internal oscillation cannot be used if 1 MHz internal oscillation is selected by using the option byte.

- Remarks 1. If the low-power-supply detector (LVI) is set to ON by default by the option bytes, the reset will not be released until the power supply voltage (VDD) exceeds 2.07 V±0.2 V.

After the reset operation, the status will shift to (B) in the above figure.

- After the reset operation, the status will shift to (B) in the above lig

- 2. DSC: 20 MHz internal high-speed oscillation clock

## (2) Timer clock select register m (TPSm)

The TPSm register is a 16-bit register that is used to select two types of operation clocks (CKm0, CKm1) that are commonly supplied to each channel. CKm1 is selected by bits 7 to 4 of the TPSm register, and CKm0 is selected by bits 3 to 0.

Rewriting of the TPSm register during timer operation is possible only in the following cases.

If the PRSm00 to PRSm03 bits can be rewritten:

All channels for which CKm0 is selected as the operation clock (CKSmn = 0) are stopped (TEmn = 0). If the PRSm10 to PRSm13 bits can be rewritten:

All channels for which CKm1 is selected as the operation clock (CKSmn = 1) are stopped (TEmn = 0).

The TPSm register can be set by a 16-bit memory manipulation instruction.

The lower 8 bits of the TPSm register can be set with an 8-bit memory manipulation instruction with TPSmL. Reset signal generation clears this register to 0000H.

## 8.6 Channel Input (TImn Pin) Control

#### 8.6.1 TImn edge detection circuit

#### (1) Edge detection basic operation timing

Edge detection circuit sampling is done in accordance with the operation clock (fmcк).

## Figure 8-40. Edge Detection Basic Operation Timing

| fc∟ĸ                                                |  |

|-----------------------------------------------------|--|

| Operation clock (fмск)                              |  |

| Synchronized (noise filter)<br>internal TImn signal |  |

| Rising edge detection internal trigger              |  |

| Falling edge detection internal trigger             |  |

**Remark** m: Unit number (m = 0, 1), n: Channel number (n = 0 to 7)

However, in case of the timer input pin (TImn) and the timer output pin (TOmn), mn changes as below.

78K0R/KC3-L (40-pin):

mn = 02 to 07

78K0R/KC3-L (44-pin, 48-pin):

mn = 00 to 07

78K0R/KD3-L, 78K0R/KE3-L:

mn = 00 to 07

78K0R/KF3-L, 78K0R/KG3-L:

mn = 00 to 07, 10 to 13

## CHAPTER 12 WATCHDOG TIMER

## 12.1 Functions of Watchdog Timer

The watchdog timer operates on the internal low-speed oscillation clock.

The watchdog timer is used to detect an inadvertent program loop. If a program loop is detected, an internal reset signal is generated.

Program loop is detected in the following cases.

- If the watchdog timer counter overflows

- If a 1-bit manipulation instruction is executed on the watchdog timer enable register (WDTE)

- If data other than "ACH" is written to the WDTE register

- If data is written to the WDTE register during a window close period

When a reset occurs due to the watchdog timer, bit 4 (WDRF) of the reset control flag register (RESF) is set to 1. For details of the RESF register, see **CHAPTER 21 RESET FUNCTION**.

When 75% of the overflow time is reached, an interval interrupt can be generated.

## <R>

## Table 13-2. A/D Conversion Time Selection (2/3)

| A/D C | Converter | Mode R | legister ( | ADM) | Mode            |                  | Conversion Time Selection |                                              |                    |                    |             |  |  |  |

|-------|-----------|--------|------------|------|-----------------|------------------|---------------------------|----------------------------------------------|--------------------|--------------------|-------------|--|--|--|

| FR2   | FR1       | FR0    | LV1        | LV0  |                 | fclk = 2<br>MHz  |                           | fclk = 5 MHz                                 | fclk = 10 MHz      | fclk = 20 MHz      | Clock (fad) |  |  |  |

| 0     | 0         | 0      | 0          | 0    | Normal          | <b>342/f</b> ськ | Setting                   | Setting prohibited 34.2 $\mu$ s 17.1 $\mu$ s |                    | 17.1 <i>µ</i> s    | fclк/20     |  |  |  |

| 0     | 0         | 1      |            |      |                 | 172/fськ         | prohibited                | 34.4 <i>µ</i> s                              | 17.2 <i>µ</i> s    | 8.6 <i>µ</i> s     | fclк/10     |  |  |  |

| 0     | 1         | 0      |            |      |                 | 138/fclк         |                           | 27.6 <i>µ</i> s                              | 13.8 <i>µ</i> s    | Setting prohibited | fськ/8      |  |  |  |

| 0     | 1         | 1      |            |      |                 | 104/fclк         | 52.0 <i>µ</i> s           | 20.8 <i>µ</i> s                              | 10.4 <i>µ</i> s    |                    | fс∟к/6      |  |  |  |

| 1     | 0         | 0      |            |      |                 | <b>70/f</b> ськ  | 35.0 <i>µ</i> s           | 14.0 <i>µ</i> s                              | Setting prohibited |                    | fс∟к/4      |  |  |  |

| 1     | 0         | 1      |            |      |                 | <b>53/f</b> ськ  | 26.5 <i>μ</i> s           | 10.6 <i>µ</i> s                              |                    |                    | fс∟к/З      |  |  |  |

| 1     | 1         | 0      |            |      |                 | <b>36/f</b> ськ  | 18.0 <i>µ</i> s           | Setting prohibited                           |                    |                    | fськ/2      |  |  |  |

| 1     | 1         | 1      |            |      |                 | <b>19/f</b> ськ  | 9.5 <i>μ</i> s            |                                              |                    |                    | fclк        |  |  |  |

| ×     | ×         | ×      | 0          | 1    | Low-<br>voltage | Setting p        | Setting prohibited        |                                              |                    |                    |             |  |  |  |

| ×     | ×         | ×      | 1          | 0    | High<br>speed 1 | Setting p        | rohibited                 |                                              |                    |                    | -           |  |  |  |

| 0     | 0         | 0      | 1          | 1    | High            | <b>342/f</b> ськ | Setting                   | Setting prohibited                           | 34.2 <i>µ</i> s    | 17.1 <i>µ</i> s    | fclк/20     |  |  |  |

| 0     | 0         | 1      |            |      | speed 2         | 172/fclк         | prohibited                | 34.4 <i>µ</i> s                              | 17.2 <i>µ</i> s    | 8.6 <i>µ</i> s     | fclк/10     |  |  |  |

| 0     | 1         | 0      |            |      |                 | 138/fclк         |                           | 27.6 <i>µ</i> s                              | 13.8 <i>µ</i> s    | 6.9 <i>µ</i> s     | fськ/8      |  |  |  |

| 0     | 1         | 1      |            |      |                 | 104/fськ         | 52.0 <i>µ</i> s           | 20.8 <i>µ</i> s                              | 10.4 <i>µ</i> s    | 5.2 <i>μ</i> s     | fс∟к/6      |  |  |  |

| 1     | 0         | 0      |            |      |                 | 70/fclк          | 35.0 <i>µ</i> s           | 14.0 <i>µ</i> s                              | 7.0 <i>µ</i> s     | 3.5 <i>μ</i> s     | fськ/4      |  |  |  |

| 1     | 0         | 1      |            |      |                 | <b>53/f</b> ськ  | 26.5 <i>µ</i> s           | 10.6 <i>µ</i> s                              | 5.3 <i>μ</i> s     | Setting prohibited | fськ/3      |  |  |  |

| 1     | 1         | 0      |            |      |                 | <b>36/f</b> ськ  | 18.0 <i>µ</i> s           | 7.2 <i>μ</i> s                               | 3.6 <i>µ</i> s     |                    | fськ/2      |  |  |  |

| 1     | 1         | 1      |            |      |                 | <b>19/f</b> ськ  | 9.5 <i>μ</i> s            | 3.8 <i>µ</i> s                               | Setting prohibited |                    | fclк        |  |  |  |

## (2) 2.7 V $\leq$ AV<sub>REF</sub> $\leq$ 5.5 V

Cautions 1. When rewriting the FR2 to FR0, LV1, and LV0 bits to other than the same data, stop A/D conversion once (ADCS = 0) beforehand.

2. The above conversion time does not include clock frequency errors. Select conversion time, taking clock frequency errors into consideration.

**Remark** fclk: CPU/peripheral hardware clock frequency

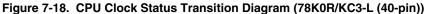

## (5) Full-scale error

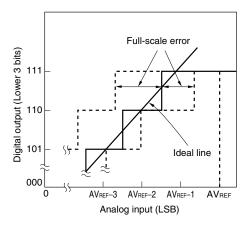

This shows the difference between the actual measurement value of the analog input voltage and the theoretical value (Full-scale -3/2LSB) when the digital output changes from 1.....110 to 1.....111.

## (6) Integral linearity error

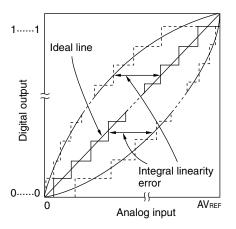

This shows the degree to which the conversion characteristics deviate from the ideal linear relationship. It expresses the maximum value of the difference between the actual measurement value and the ideal straight line when the zero-scale error and full-scale error are 0.

## (7) Differential linearity error

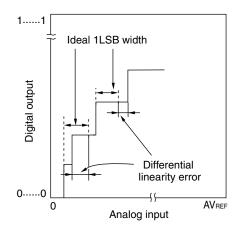

While the ideal width of code output is 1LSB, this indicates the difference between the actual measurement value and the ideal value.

#### Figure 13-20. Integral Linearity Error

## Figure 13-19. Full-Scale Error

#### Figure 13-21. Differential Linearity Error

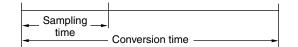

### (8) Conversion time

This expresses the time from the start of sampling to when the digital output is obtained. The sampling time is included in the conversion time in the characteristics table.

### (9) Sampling time

This is the time the analog switch is turned on for the analog voltage to be sampled by the sample & hold circuit.

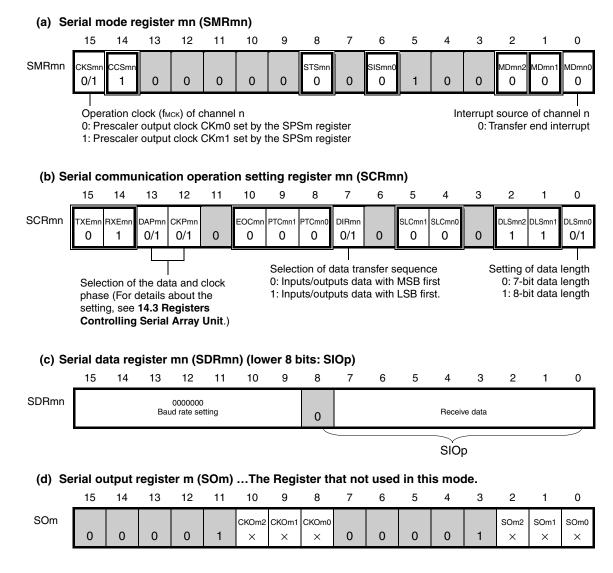

### Figure 14-8. Format of Serial Communication Operation Setting Register mn (SCRmn) (3/4)

Address: F0118H, F0119H (SCR00) to F011EH, F011FH (SCR03), After reset: 0087H R/W F0158H, F0159H (SCR10) to F015EH, F015FH (SCR13), F020CH, F020DH (SCR20), F020EH, F020FH (SCR21)

| Symbol | 15  | 14  | 13  | 12  | 11 | 10  | 9   | 8   | 7   | 6 | 5   | 4   | 3 | 2   | 1   | 0   |

|--------|-----|-----|-----|-----|----|-----|-----|-----|-----|---|-----|-----|---|-----|-----|-----|

| SCRmn  | TXE | RXE | DAP | CKP | 0  | EOC | PTC | PTC | DIR | 0 | SLC | SLC | 0 | DLS | DLS | DLS |

|        | mn  | mn  | mn  | mn  |    | mn  | mn1 | mn0 | mn  |   | mn1 | mn0 |   | mn2 | mn1 | mn0 |

| PTC   | PTC                                                                               | Setting of parity b                | bit in UART mode        |  |  |  |  |

|-------|-----------------------------------------------------------------------------------|------------------------------------|-------------------------|--|--|--|--|

| mn1   | mn0                                                                               | Transmission                       | Reception               |  |  |  |  |

| 0     | 0                                                                                 | Does not output the parity bit.    | Receives without parity |  |  |  |  |

| 0     | 1                                                                                 | Outputs 0 parity <sup>Note</sup> . | No parity judgment      |  |  |  |  |

| 1     | 0                                                                                 | Outputs even parity.               | Judged as even parity.  |  |  |  |  |

| 1     | 1                                                                                 | Outputs odd parity.                | Judges as odd parity.   |  |  |  |  |

| Be su | Be sure to set PTCmn1, PTCmn0 = 0, 0 in the CSI mode and simplified $I^2$ C mode. |                                    |                         |  |  |  |  |

| DIR   | Selection of data transfer sequence in CSI and UART modes  |  |  |  |  |  |  |

|-------|------------------------------------------------------------|--|--|--|--|--|--|

| mn    |                                                            |  |  |  |  |  |  |

| 0     | Inputs/outputs data with MSB first.                        |  |  |  |  |  |  |

| 1     | Inputs/outputs data with LSB first.                        |  |  |  |  |  |  |

| Be su | Be sure to clear DIRmn = 0 in the simplified $l^2$ C mode. |  |  |  |  |  |  |

| SLC<br>mn1 | SLC<br>mn0                                                                                                                                             | Setting of stop bit in UART mode |  |  |  |  |  |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--|--|--|--|--|--|

| 0          | 0                                                                                                                                                      | No stop bit                      |  |  |  |  |  |  |

| 0          | 1                                                                                                                                                      | Stop bit length = 1 bit          |  |  |  |  |  |  |

| 1          | 0                                                                                                                                                      | Stop bit length = 2 bits         |  |  |  |  |  |  |

| 1          | 1                                                                                                                                                      | Setting prohibited               |  |  |  |  |  |  |

| transfe    | When the transfer end interrupt is selected, the interrupt is generated when all stop bits have been completely transferred.                           |                                  |  |  |  |  |  |  |

|            | Set 1 bit (SLCmn1, SLCmn0 = 0, 1) during UART reception and in the simplified $I^2C$ mode.<br>Set no stop bit (SLCmn1, SLCmn0 = 0, 0) in the CSI mode. |                                  |  |  |  |  |  |  |

**Note** 0 is always added regardless of the data contents.

#### Caution Be sure to clear bits 3, 6, and 11 to "0". Be sure to set bit 2 to "1".

| Remark | m: Unit number (m = 0 to 2), n: Channel number (n = 0 to 3 | )                               |

|--------|------------------------------------------------------------|---------------------------------|

|        | 78K0R/KC3-L, 78K0R/KD3-L, 78K0R/KE3-L:                     | mn = 00 to 03                   |

|        | 78K0R/KF3-L $\mu$ PD78F1010, 78F1011, 78F1012 :            | mn = 00 to 03, 10 to 13         |

|        | 78K0R/KF3-L μPD78F1027, 78F1028 :                          | mn = 00 to 03, 10 to 13, 20, 21 |

|        | 78K0R/KG3-L μ PD78F1013, 78F1014 :                         | mn = 00 to 03, 10 to 13         |

|        | 78K0R/KG3-L μ PD78F1029, 78F1030 :                         | mn = 00 to 03, 10 to 13, 20, 21 |

1

TTL input buffer

## (16) Port input mode registers 0, 1, 3, 7, 14 (PIM0, PIM1, PIM3, PIM7, PIM14)

These registers set the input buffer of ports 0, 1, 3, 7, and 14 in 1-bit units. The port input mode registers to be set differ depending on the product.

78K0R/KC3-L, 78K0R/KD3-L, 78K0R/KE3-L: PIM3, PIM7 78K0R/KF3-L, 78K0R/KG3-L: PIM0, PIM1, PIM14

The PIM0, PIM1, PIM3, PIM7, and PIM14 registers can be set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation clears the PIM0, PIM1, PIM3, PIM7, and PIM14 registers to 00H.

## Figure 14-20. Format of Port Input Mode Registers 3 and 7 (PIM3 and PIM7) (78K0R/KC3-L, 78K0R/KD3-L, 78K0R/KE3-L)

| Address F004 | I3H After re                        | set: 00H | R/W                                                       |       |   |       |       |   |  |  |  |

|--------------|-------------------------------------|----------|-----------------------------------------------------------|-------|---|-------|-------|---|--|--|--|

| Symbol       | 7                                   | 6        | 5                                                         | 4     | 3 | 2     | 1     | 0 |  |  |  |

| PIM3         | 0                                   | 0        | 0                                                         | 0     | 0 | PIM32 | PIM31 | 0 |  |  |  |

| Address F004 | Address F0047H After reset: 00H R/W |          |                                                           |       |   |       |       |   |  |  |  |

| Symbol       | 7                                   | 6        | 5                                                         | 4     | 3 | 2     | 1     | 0 |  |  |  |

| PIM7         | 0                                   | 0        | PIM75                                                     | PIM74 | 0 | PIM72 | PIM71 | 0 |  |  |  |

|              |                                     |          |                                                           |       |   |       |       |   |  |  |  |

| PIMmn        |                                     |          | Pmn pin input buffer selection (m = 3, 7; n = 1, 2, 4, 5) |       |   |       |       |   |  |  |  |

|              | 0 Normal input buffer               |          |                                                           |       |   |       |       |   |  |  |  |

## Figure 14-21. Format of Port Input Mode Registers 0, 1, and 14 (PIM0, PIM1, PIM14) (78K0R/KF3-L, 78K0R/KG3-L)

| Address F004 | 10H After re | eset: 00H F  | R/W      |                 |                  |                 |       |       |

|--------------|--------------|--------------|----------|-----------------|------------------|-----------------|-------|-------|

| Symbol       | 7            | 6            | 5        | 4               | 3                | 2               | 1     | 0     |

| PIM0         | 0            | 0            | 0        | PIM04           | PIM03            | 0               | 0     | 0     |

|              |              |              |          |                 |                  |                 |       |       |

| Address F004 | 11H After re | eset: 00H F  | R/W      |                 |                  |                 |       |       |

| Symbol       | 7            | 6            | 5        | 4               | 3                | 2               | 1     | 0     |

| PIM1         | 0            | 0            | 0        | 0               | 0                | 0               | PIM11 | PIM10 |

|              |              |              |          |                 |                  |                 |       |       |

| Address F004 | 1EH After re | eset: 00H F  | R/W      |                 |                  |                 |       |       |

| Symbol       | 7            | 6            | 5        | 4               | 3                | 2               | 1     | 0     |

| PIM14        | 0            | 0            | 0        | 0               | PIM143           | PIM142          | 0     | 0     |

|              |              |              |          |                 |                  |                 |       |       |

|              | PIMmn        |              | Pmn      | pin input buffe | r selection (m = | 0, 1, 14; n = 0 | to 4) |       |

|              | 0            | Normal input | t buffer |                 |                  |                 |       |       |

|              | 1            | TTL input bu | ıffer    |                 |                  |                 |       |       |

## (1) Register setting

## Figure 14-60. Example of Contents of Registers for Slave Reception of 3-Wire Serial I/O (CSI00, CSI01, CSI10, CSI20, CSI40, CSI41) (1/2)

Notes 1. Those bits are invalid while operating serial allay unit 1.

2. Those bits are invalid while operating serial allay unit 2.

(Remark is listed on the next page.)

<R>

| SE           | MD  | MD  | SOE | SO            | СКО           | TXE |    | PM          | P142        |               | P143<br>Note 2 | PM          | P144        | Operation mode                         |                      | Pin Function                       |                    |

|--------------|-----|-----|-----|---------------|---------------|-----|----|-------------|-------------|---------------|----------------|-------------|-------------|----------------------------------------|----------------------|------------------------------------|--------------------|

| 10<br>Note 1 | 102 | 101 | 10  | 10            | 10            | 10  | 10 | 142         |             | 143<br>Note 2 | Note 2         | 144         |             |                                        | SCK20/<br>SCL20/P142 | SI20/SDA20/<br>RxD2/P143<br>Note 2 | SO20/<br>TxD2/P144 |

| 0            | 0   | 0   | 0   | 1             | 1             | 0   | 0  | ×<br>Note 3 | ×<br>Note 3 | ×<br>Note 3   | ×<br>Note 3    | ×<br>Note 3 | ×<br>Note 3 | Operation stop                         | P142                 | P143                               | P144               |

|              | 0   | 1   |     |               |               |     |    | Note 3      | Note 3      | Note 3        | Note 3         | Note 3      | Note 3      | mode                                   |                      | P143/RxD2                          |                    |

|              | 1   | 0   |     |               |               |     |    |             |             |               |                |             |             |                                        |                      | P143                               |                    |

| 1            | 0   | 0   | 0   | 1             | 1             | 0   | 1  | 1           | ×           | 1             | ×              | ×<br>Note 3 | ×<br>Note 3 | Slave CSI20<br>reception               | SCK20<br>(input)     | SI20                               | P144               |

|              |     |     | 1   | 0/1<br>Note 4 | 1             | 1   | 0  | 1           | ×           | ×<br>Note 3   | ×<br>Note 3    | 0           | 1           | Slave CSI20<br>transmission            | SCK20<br>(input)     | P143                               | SO20               |

|              |     |     | 1   | 0/1<br>Note 4 | 1             | 1   | 1  | 1           | ×           | 1             | ×              | 0           | 1           | Slave CSI20<br>transmission/reception  | SCK20<br>(input)     | SI20                               | SO20               |

|              |     |     | 0   | 1             | 0/1<br>Note 4 | 0   | 1  | 0           | 1           | 1             | ×              | ×<br>Note 3 | ×<br>Note 3 | Master CSI20<br>reception              | SCK20<br>(output)    | SI20                               | P144               |

|              |     |     | 1   | 0/1<br>Note 4 | 0/1<br>Note 4 | 1   | 0  | 0           | 1           | ×<br>Note 3   | ×<br>Note 3    | 0           | 1           | Master CSI20<br>transmission           | SCK20<br>(output)    | P143                               | SO20               |

|              |     |     | 1   | 0/1<br>Note 4 | 0/1<br>Note 4 | 1   | 1  | 0           | 1           | 1             | ×              | 0           | 1           | Master CSI20<br>transmission/reception | SCK20<br>(output)    | SI20                               | SO20               |

|              | 0   | 1   | 1   | 0/1<br>Note 4 | 1             | 1   | 0  | ×<br>Note 3 | ×<br>Note 3 | ×<br>Note 3   | ×<br>Note 3    | 0           | 1           | UART2<br>transmission Note 5           | P142                 | P143/RxD2                          | TxD2               |

| 0            | 1   | 0   | 0   | 0/1<br>Note 6 | 0/1<br>Note 6 | 0   | 0  | 0           | 1           | 0             | 1              | ×<br>Note 3 | ×<br>Note 3 | IIC20                                  | SCL20                | SDA20                              | P144               |

|              |     |     |     | NOLE O        | Note o        | 1   | 0  |             |             |               |                | Note 5      | Note 5      | start condition                        |                      |                                    |                    |

|              |     |     |     |               |               | 0   | 1  |             |             |               |                |             |             |                                        |                      |                                    |                    |

| 1            |     |     | 1   | 0/1<br>Note 4 | 0/1<br>Note 4 | 1   | 0  | 0           | 1           | 0             | 1              | imesNote 3  | imesNote 3  | IIC20 address field<br>transmission    | SCL20                | SDA20                              | P144               |

|              |     |     | 1   | 0/1<br>Note 4 | 0/1<br>Note 4 | 1   | 0  | 0           | 1           | 0             | 1              | ×<br>Note 3 | ×<br>Note 3 | IIC20 data<br>transmission             | SCL20                | SDA20                              | P144               |

|              |     |     | 1   | 0/1<br>Note 4 | 0/1<br>Note 4 | 0   | 1  | 0           | 1           | 0             | 1              | ×<br>Note 3 | ×<br>Note 3 | IIC20 data reception                   | SCL20                | SDA20                              | P144               |

| 0            | ]   |     | 0   | 0/1           | 0/1           | 0   | 0  | 0           | 1           | 0             | 1              | ×           | ×           | IIC20                                  | SCL20                | SDA20                              | P144               |

|              |     |     |     | Note 7        | Note 7        | 1   | 0  |             |             |               |                | Note 3      | Note 3      | stop condition                         |                      |                                    |                    |

|              |     |     |     |               |               | 0   | 1  |             |             |               |                |             |             |                                        |                      |                                    |                    |

# Table 14-13. Relationship between register settings and pins(Channel 0 of unit 1: CSI20, UART2 transmission, IIC20)

**Notes 1.** Serial channel enable register 1 (SE1) is a read-only status register which is set using serial channel statrt register 1 (SS1) and serial channel stop register 1 (ST1).

When channel 1 of unit 1 is set to UART2 reception, this pin becomes an RxD2 function pin (refer to Table 14-14). In this case, operation stop mode or UART2 transmission must be selected for channel 0 of unit 1.

**3.** This pin can be set as a port function pin.

This is 0 or 1, depending on the communication operation. For details, refer to 14.3 (12) Serial output register m (SOm).

- 5. When using UART2 transmission and reception in a pair, set channel 1 of unit 1 to UART2 reception (refer to Table 14-14).

- **6.** Set the CKO10 bit to 1 before a start condition is generated. Clear the SO10 bit from 1 to 0 when the start condition is generated.

- **7.** Set the CKO10 bit to 1 before a stop condition is generated. Clear the SO10 bit from 0 to 1 when the stop condition is generated.

Remark X: Don't care

## 18.4 Registers Controlling Interrupt Functions (78K0R/KF3-L, 78K0R/KG3-L)

The following 6 types of registers are used to control the interrupt functions.

- Interrupt request flag registers (IF0L, IF0H, IF1L, IF1H, IF2L, IF2H)

- Interrupt mask flag registers (MK0L, MK0H, MK1L, MK1H, MK2L, MK2H)

- Priority specification flag registers (PR00L, PR00H, PR01L, PR01H, PR02L, PR02H, PR10L, PR10H, PR11L, PR11H, PR12L, PR12H)

- External interrupt rising edge enable registers (EGP0, EGP1)

- External interrupt falling edge enable registers (EGN0, EGN1)

- Program status word (PSW)

Table 18-4 shows a list of interrupt request flags, interrupt mask flags, and priority specification flags corresponding to interrupt request sources.

| Interrupt                  | Interrupt Request         | Flag     | Interrupt Mask F          | lag      | Priority Specificatio                | n Flag   |

|----------------------------|---------------------------|----------|---------------------------|----------|--------------------------------------|----------|

| Source                     |                           | Register |                           | Register |                                      | Register |

| INTWDTI                    | WDTIIF                    | IF0L     | WDTIMK                    | MKOL     | WDTIPR0, WDTIPR1                     | PR00L,   |

| INTLVI                     | LVIIF                     |          | LVIMK                     |          | LVIPR0, LVIPR1                       | PR10L    |

| INTP0                      | PIF0                      |          | PMK0                      |          | PPR00, PPR10                         |          |

| INTP1                      | PIF1                      |          | PMK1                      |          | PPR01, PPR11                         |          |

| INTP2                      | PIF2                      |          | PMK2                      |          | PPR02, PPR12                         |          |

| INTP3                      | PIF3                      |          | РМК3                      |          | PPR03, PPR13                         |          |

| INTP4                      | PIF4                      |          | PMK4                      |          | PPR04, PPR14                         |          |

| INTP5                      | PIF5                      |          | PMK5                      |          | PPR05, PPR15                         |          |

| INTST3                     | STIF3                     | IF0H     | STMK3                     | МКОН     | STPR03, STPR13                       | PR00H,   |

| INTSR3                     | SRIF3                     |          | SRMK3                     |          | SRPR03, SRPR13                       | PR10H    |

| INTSRE3                    | SREIF3                    |          | SREMK3                    |          | SREPR03, SREPR13                     |          |

| INTDMA0                    | DMAIF0                    |          | DMAMK0                    |          | DMAPR00, DMAPR10                     |          |

| INTDMA1                    | DMAIF1                    |          | DMAMK1                    |          | DMAPR01, DMAPR11                     |          |

| INTST0 <sup>Note 1</sup>   | STIF0 <sup>Note 1</sup>   |          | STMK0 <sup>Note 1</sup>   |          | STPR00, STPR10 <sup>Note 1</sup>     |          |

| INTCSI00 <sup>Note 1</sup> | CSIIF00 <sup>Note 1</sup> |          | CSIMK00 <sup>Note 1</sup> |          | CSIPR000, CSIPR100 <sup>Note 1</sup> |          |

| INTSR0 <sup>Note 2</sup>   | SRIF0 <sup>Note 2</sup>   |          | SRMK0 <sup>Note 2</sup>   |          | SRPR00, SRPR10 <sup>Note 2</sup>     |          |

| INTCSI01 <sup>Note 2</sup> | CSIIF01 <sup>Note 2</sup> |          | CSIMK01 <sup>Note 2</sup> |          | CSIPR001, CSIPR101 <sup>Note 2</sup> |          |

| INTSRE0                    | SREIF0                    |          | SREMK0                    |          | SREPR00, SREPR10                     |          |

### Table 18-4. Flags Corresponding to Interrupt Request Sources (1/3)

**Notes 1.** Do not use UART0 and CSI00 at the same time because they share flags for the interrupt request sources. If one of the interrupt sources INTST0 and INTCSI00 is generated, bit 5 of the IF0H register is set to 1. Bit 5 of the MK0H, PR00H, and PR10H registers supports these three interrupt sources.

2. Do not use UART0 and CSI01 at the same time because they share flags for the interrupt request sources. If one of the interrupt sources INTSR0 and INTCSI01 is generated, bit 6 of the IF0H register is set to 1. Bit 6 of the MK0H, PR00H, and PR10H registers supports these three interrupt sources.

| Interrupt                | Interrupt Request       | Flag     | Interrupt Mask F        | lag      | Priority Specification             | n Flag   |

|--------------------------|-------------------------|----------|-------------------------|----------|------------------------------------|----------|

| Source                   |                         | Register |                         | Register |                                    | Register |

| INTP11                   | PIF11                   | IF2H     | PMK11                   | MK2H     | PPR011, PPR111                     | PR02H,   |

| INTSRE4 <sup>Note</sup>  | SREIF4 <sup>Note</sup>  |          | SREMK4 <sup>Note</sup>  |          | SREPR04, SREPR14 <sup>Note</sup>   | PR12H    |

| INTTM10                  | TMIF10                  |          | TMMK10                  |          | TMPR010, TMPR110                   |          |

| INTTM11                  | TMIF11                  |          | TMMK11                  |          | TMPR011, TMPR111                   |          |

| INTTM12                  | TMIF12                  |          | TMMK12                  |          | TMPR012, TMPR112                   |          |

| INTSRE2                  | SREIF2                  |          | SREMK2                  |          | SREPR02, SREPR12                   |          |

| INTMD                    | MDIF                    |          | MDMK                    |          | MDPR0, MDPR1                       |          |

| INTST4 <sup>Note</sup>   | STIF4 <sup>Note</sup>   |          | STMK4 <sup>Note</sup>   |          | STPR04, STPR14 <sup>Note</sup>     |          |

| INTCSI40 <sup>Note</sup> | CSIIF40 <sup>Note</sup> |          | CSIMK40 <sup>Note</sup> |          | CSIPR040, CSIPR140 <sup>Note</sup> |          |

| INTSR4 <sup>Note</sup>   | SRIF4 <sup>Note</sup>   |          | SRMK4 <sup>Note</sup>   | ]        | SRPR04, SRPR14 <sup>Note</sup>     |          |

| INTCSI41 <sup>Note</sup> | CSIIF41 <sup>Note</sup> |          | CSIMK41 <sup>Note</sup> |          | CSIPR041, CSIPR141 <sup>Note</sup> |          |

Table 18-4. Flags Corresponding to Interrupt Request Sources (3/3)

**Note** Those are only mounted in the  $\mu$  PD78F1027, 78F1028, 78F1029, and 78F1030.

|                                | STOP Mode                            | e Setting                | When STOP Instruction Is Executed While CPU Is Operating on Main System Clock                                                                                           |                 |  |  |  |  |  |

|--------------------------------|--------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|--|--|

| Ite                            | m                                    |                          | When CPU Is Operating on<br>Internal High-Speed     When CPU Is Operating on<br>X1 Clock (fx)     When CPU Is Operating on<br>External Main System Clock<br>(fex)       |                 |  |  |  |  |  |

| Sy                             | stem clock                           |                          | Clock supply to the CPU is stop                                                                                                                                         | ped             |  |  |  |  |  |

|                                | Main system clock                    | fін                      | Stopped                                                                                                                                                                 |                 |  |  |  |  |  |

|                                |                                      | fx                       |                                                                                                                                                                         |                 |  |  |  |  |  |

|                                |                                      | fex                      |                                                                                                                                                                         |                 |  |  |  |  |  |

|                                | Subsystem<br>clock <sup>Note 1</sup> | fхт                      | Status before STOP mode was                                                                                                                                             | set is retained |  |  |  |  |  |

| fı∟                            |                                      |                          | Set by bits 0 (WDSTBYON) and 4 (WDTON) of option byte (000C0H)<br>• WDTON = 0: Stops<br>• WDTON = 1 and WDSTBYON = 1: Oscillates<br>• WDTON = 1 and WDSTBYON = 0: Stops |                 |  |  |  |  |  |

| CP                             | U                                    |                          | Operation stopped                                                                                                                                                       |                 |  |  |  |  |  |

| Fla                            | sh memory                            |                          | Operation stopped                                                                                                                                                       |                 |  |  |  |  |  |

| RA                             | М                                    |                          | The value is retained                                                                                                                                                   |                 |  |  |  |  |  |

| Po                             | rt (latch)                           |                          | Status before STOP mode was set is retained                                                                                                                             |                 |  |  |  |  |  |

| Tin                            | ner array unit                       |                          | Operation disabled                                                                                                                                                      |                 |  |  |  |  |  |

| Re                             | al-time counter (RTC                 | ) <sup>Note 1</sup>      | Operable                                                                                                                                                                |                 |  |  |  |  |  |

| Wa                             | atchdog timer                        |                          | Set by bits 0 (WDSTBYON) and 4 (WDTON) of option byte (000C0H)<br>• WDTON = 0: Stops<br>• WDTON = 1 and WDSTBYON = 1: Operates<br>• WDTON = 1 and WDSTBYON = 0: Stops   |                 |  |  |  |  |  |

| Clo                            | ock output/buzzer out                | put Note 2               | Operable only when subsystem clock is selected as the count clock                                                                                                       |                 |  |  |  |  |  |

| A/[                            | D converter                          |                          | Operation disabled                                                                                                                                                      |                 |  |  |  |  |  |

| Pro                            | ogrammable gain amp                  | lifier <sup>Note 3</sup> |                                                                                                                                                                         |                 |  |  |  |  |  |

| Co                             | mparator Note 3                      |                          |                                                                                                                                                                         |                 |  |  |  |  |  |

| Se                             | rial array unit (SAU)                |                          |                                                                                                                                                                         |                 |  |  |  |  |  |

| Se                             | rial interface (IICA) <sup>№</sup>   | ote 2                    | Wakeup by address match operable                                                                                                                                        |                 |  |  |  |  |  |

| Mu                             | ltiplier/divider                     |                          | Operation disabled                                                                                                                                                      |                 |  |  |  |  |  |

| DMA controller                 |                                      |                          |                                                                                                                                                                         |                 |  |  |  |  |  |

| Power-on-clear function        |                                      |                          | Operable                                                                                                                                                                |                 |  |  |  |  |  |

| Low-voltage detection function |                                      |                          |                                                                                                                                                                         |                 |  |  |  |  |  |

| Ex                             | ternal interrupt                     |                          |                                                                                                                                                                         |                 |  |  |  |  |  |

| Ke                             | y interrupt function                 |                          |                                                                                                                                                                         |                 |  |  |  |  |  |

#### Table 20-2. Operating Statuses in STOP Mode

Notes 1. Those are not mounted onto 40-pin product of the 78K0R/KC3-L.

2. Those are not mounted onto 40-pin and 44-pin products of the 78K0R/KC3-L.

3. 78K0R/KC3-L, 78K0R/KD3-L, 78K0R/KE3-L only.

Remark fin: Internal high-speed oscillation clock

- fx: X1 clock

- fex: External main system clock

- fxT: XT1 clock

- fil: Internal low-speed oscillation clock

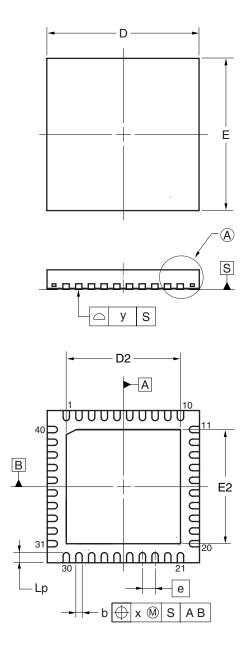

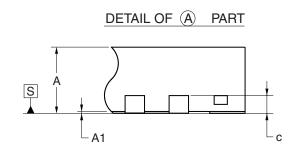

## CHAPTER 32 PACKAGE DRAWINGS

## 32.1 78K0R/KC3-L (40-pin products)

μ PD78F1000K8-4B4-AX, 78F1001K8-4B4-AX, 78F1002K8-4B4-AX, 78F1003K8-4B4-AX (Under development)

## 40-PIN PLASTIC WQFN(6x6)

|      | (UNIT:mm)          |

|------|--------------------|

| ITEM | DIMENSIONS         |

| D    | $6.00 \pm 0.05$    |

| Е    | $6.00\!\pm\!0.05$  |

| D2   | 4.50               |

| E2   | 4.50               |

| А    | 0.75±0.05          |

| A1   | 0.00 to 0.02       |

| b    | 0.25 + 0.05 - 0.07 |

| С    | 0.20±0.05          |

| е    | 0.50               |

| Lp   | 0.40±0.10          |

| х    | 0.05               |

| У    | 0.05               |

|      | P40K8-50-4B4       |