# E. Renesas Electronics America Inc - UPD78F1009GK-GAJ-AX Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | 78K/0R                                                                               |

| Core Size                  | 16-Bit                                                                               |

| Speed                      | 20MHz                                                                                |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                     |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                              |

| Number of I/O              | 50                                                                                   |

| Program Memory Size        | 64KB (64K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 3K x 8                                                                               |

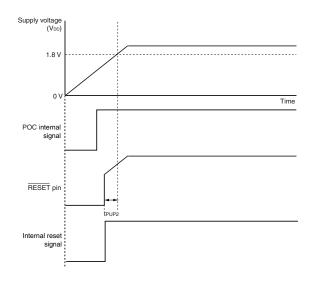

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                          |

| Data Converters            | A/D 12x10b                                                                           |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 64-LQFP                                                                              |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f1009gk-gaj-ax |

|                            |                                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.2.12 P150 to P153 (port 15)

P150 to P153 function as an I/O port. These pins also function as A/D converter analog input.

|            | 78K0R/KC3-L<br>(μPD78F100y: y = 0 to | 78K0R/KC3-L (48-pin)<br>3) (μPD78F100y: y = 1 to 3) | 78K0R/KD3-L<br>(μPD78F100y: y = 4 to 6) | 78K0R/KE3-L<br>(µPD78F100y: y = 7 to 9) |  |

|------------|--------------------------------------|-----------------------------------------------------|-----------------------------------------|-----------------------------------------|--|

|            | 40-pin 44-pin                        |                                                     |                                         |                                         |  |

| P150/ANI8  | $\checkmark$                         | $\checkmark$                                        | $\checkmark$                            | $\checkmark$                            |  |

| P151/ANI9  | $\checkmark$                         | $\checkmark$                                        | $\checkmark$                            | $\checkmark$                            |  |

| P152/ANI10 | -                                    | $\checkmark$                                        | $\checkmark$                            | $\checkmark$                            |  |

| P153/ANI11 | -                                    | -                                                   | -                                       | $\checkmark$                            |  |

# **Remark** $\sqrt{}$ : Mounted

The following operation modes can be specified in 1-bit units.

#### (1) Port mode

P150 to P153 function as an I/O port. P150 to P153 can be set to input or output port in 1-bit units using port mode register 15 (PM15).

#### (2) Control mode

P150 to P153 function as the A/D converter analog input pins (ANI8 to ANI11). When using these pins as the analog input pins, see **13.6 (5)** ANI0/P20 to ANI7/P27 and ANI8/P150 to ANI15/P157.

# Caution ANI8/P150 to ANI11/P153 are set in the digital input (general-purpose port) mode after release of reset.

|       | 78K0R/KC3-L<br>(µPD78F100y: y = 0 to 3) |        |              |              | 78K0R/KE3-L<br>(µPD78F100y: y = 7 to 9) |  |

|-------|-----------------------------------------|--------|--------------|--------------|-----------------------------------------|--|

|       | 40-pin                                  | 44-pin |              |              |                                         |  |

| AVREF | ١                                       | l.     | $\checkmark$ | $\checkmark$ |                                         |  |

| AVss  | ١                                       | l.     | $\checkmark$ | $\checkmark$ |                                         |  |

| VDD   | ١                                       | 1      | $\checkmark$ | $\checkmark$ | $\checkmark$                            |  |

| EVDD  | -                                       | -      | -            | _            | $\checkmark$                            |  |

| Vss   | ١                                       | 1      | $\checkmark$ | $\checkmark$ | $\checkmark$                            |  |

| EVss  | -                                       | _      | _            | _            |                                         |  |

#### 2.2.13 AVREF, AVSS, VDD, EVDD, VSS, EVSS

#### (1) AVREF

This is the A/D converter and comparator reference voltage input pin and the positive power supply pin of P20 to P27, P150 to P153, P80 to P83, A/D converter, programmable gain amplifier, and comparator.

When all pins of port 2, port 15, and port 8 are used as the analog port pins, make the potential of AV<sub>REF</sub> be such that  $1.8 \text{ V} \leq \text{AV}_{\text{REF}} \leq \text{V}_{\text{DD}}$ . When one or more of the pins of port 2, port 15, and port 8 are used as the digital port pins or when the A/D converter, programmable gain amplifier, and comparator are not used, make AV<sub>REF</sub> the same potential as EV<sub>DD</sub> or V<sub>DD</sub>.

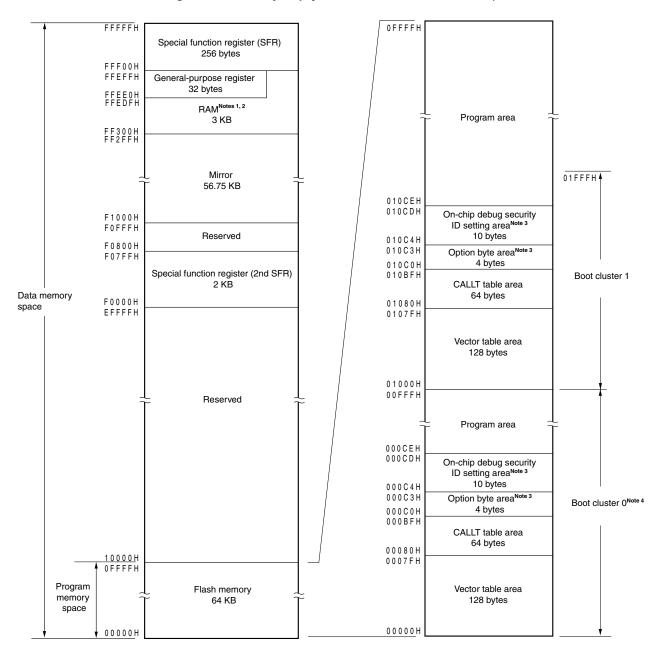

- **Notes 1.** While using the self-programming function, the area FFE20H to FFEFFH cannot be used as stack memory. Furthermore, the areas of FF300H to FF6FFH also cannot be used with the  $\mu$ PD78F1003, 78F1006 and 78F1009.

- 2. Instructions can be executed from the RAM area excluding the general-purpose register area.

- **3.** When boot swap is not used: Set the option bytes to 000C0H to 000C3H, and the on-chip debug security IDs to 000C4H to 000CDH.

- When boot swap is used:Set the option bytes to 000C0H to 000C3H and 010C0H to 010C3H, and the<br/>on-chip debug security IDs to 000C4H to 000CDH and 010C4H to 010CDH.

- 4. Writing boot cluster 0 can be prohibited depending on the setting of security (see 26.7 Security Setting).

# 4.2.3 ES and CS registers

The ES register is used for data access and the CS register is used to specify the higher address when a branch instruction is executed.

The default value of the ES register after reset is 0FH, and that of the CS register is 00H.

|    | 7 | 6 | 5 | 4 | 3   | 2   | 1   | 0   |

|----|---|---|---|---|-----|-----|-----|-----|

| ES | 0 | 0 | 0 | 0 | ES3 | ES2 | ES1 | ES0 |

|    |   |   |   |   |     |     |     |     |

|    | 7 | 6 | 5 | 4 | 3   | 2   | 1   | 0   |

| CS | 0 | 0 | 0 | 0 | CS3 | CP2 | CP1 | CP0 |

# Figure 4-25. Configuration of ES and CS Registers

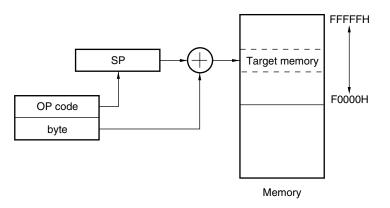

# 4.4.7 Based addressing

# [Function]

Based addressing uses the contents of a register pair specified with the instruction word as a base address, and 8bit immediate data or 16-bit immediate data as offset data. The sum of these values is used to specify the target address.

# [Operand format]

| Identifier | Description                                                                                 |

|------------|---------------------------------------------------------------------------------------------|

| -          | [HL + byte], [DE + byte], [SP + byte] (only the space from F0000H to FFFFFH is specifiable) |

| _          | word[B], word[C] (only the space from F0000H to FFFFFH is specifiable)                      |

| _          | word[BC] (only the space from F0000H to FFFFH is specifiable)                               |

| _          | ES:[HL + byte], ES:[DE + byte] (higher 4-bit addresses are specified by the ES register)    |

| _          | ES:word[B], ES:word[C] (higher 4-bit addresses are specified by the ES register)            |

| _          | ES:word[BC] (higher 4-bit addresses are specified by the ES register)                       |

Figure 4-39. Example of [SP+byte]

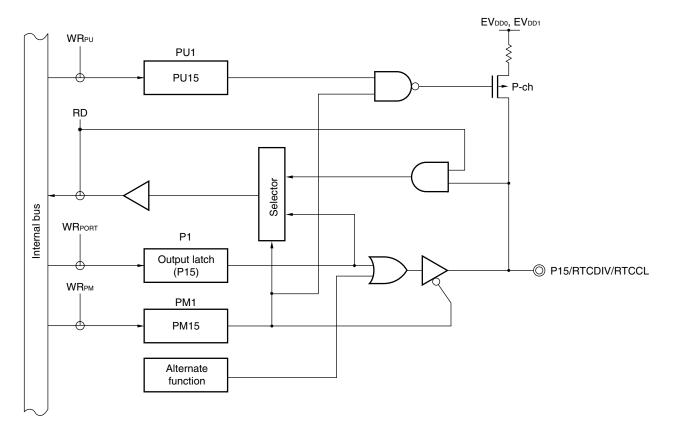

Figure 6-11. Block Diagram of P15

- P1: Port register 1

- PU1: Pull-up resistor option register 1

- PM1: Port mode register 1

- RD: Read signal

- WR××: Write signal

| Symbol | 15  | 14  | 13  | 12  | 11                   | 10 | 9        | 8        | 7        | 6                   | 5        | 4     | 3                  | 2        | 1         | 0   |

|--------|-----|-----|-----|-----|----------------------|----|----------|----------|----------|---------------------|----------|-------|--------------------|----------|-----------|-----|

| TPSm   | 0   | 0   | 0   | 0   | 0                    | 0  | 0        | 0        | PRS      | PRS                 | PRS      | PRS   | PRS                | PRS      | S PRS     | PRS |

|        |     |     |     |     |                      |    |          |          | m13      | m12                 | m11      | m10   | m03                | m02      | 2 m01     | m00 |

|        |     | -   |     |     |                      |    |          |          |          |                     |          |       |                    |          |           |     |

|        | PRS | PRS | PRS | PRS |                      |    |          | Sele     | ction o  | f operati           | on clocl | (CKm  | k) <sup>Note</sup> |          |           |     |

|        | mk3 | mk2 | mk1 | mk0 |                      |    | fc       | lk = 2 N | 1Hz      | fclk =              | 5 MHz    | fclk  | = 10 MI            | Ηz       | fclк = 20 | MHz |

|        | 0   | 0   | 0   | 0   | fclĸ                 |    | 2 N      | 1Hz      |          | 5 MHz               |          | 10 M  | Hz                 | 2        | 20 MHz    |     |

|        | 0   | 0   | 0   | 1   | fclк/2               |    | 1 N      | 1Hz      |          | 2.5 MH              | z        | 5 MH  | lz                 |          | 10 MHz    |     |

|        | 0   | 0   | 1   | 0   | fclk/2 <sup>2</sup>  |    | 500      | ) kHz    |          | 1.25 MH             | Ηz       | 2.5 N | /Hz                | Į        | 5 MHz     |     |

|        | 0   | 0   | 1   | 1   | fclk/2 <sup>3</sup>  |    | 250      | ) kHz    |          | 625 kHz             |          | 1.25  | 1.25 MHz           |          | 2.5 MHz   |     |

|        | 0   | 1   | 0   | 0   | fcLĸ/2⁴              |    | 125      | 5 kHz    |          | 312.5 kHz 625 kHz   |          |       | 1.25 MHz           |          |           |     |

|        | 0   | 1   | 0   | 1   | fс∟к/2⁵              |    | 62.      | 5 kHz    |          | 156.2 kHz 312.5 kHz |          | (     | 625 kHz            |          |           |     |

|        | 0   | 1   | 1   | 0   | fclk/2 <sup>6</sup>  |    | 31.      | 25 kHz   |          | 78.1 kHz 156.2 kHz  |          | :     | 312.5 kHz          | Z        |           |     |

|        | 0   | 1   | 1   | 1   | fclk/2 <sup>7</sup>  |    | 15.      | 62 kHz   |          | 39.1 kHz 78.1 kHz   |          |       | 156.2 kHz          |          |           |     |

|        | 1   | 0   | 0   | 0   | fclk/2 <sup>8</sup>  |    | 7.8      | 1 kHz    |          | 19.5 kHz 3          |          | 39.1  | 39.1 kHz           |          | 78.1 kHz  |     |

|        | 1   | 0   | 0   | 1   | fclк/2 <sup>9</sup>  |    | 3.9      | 1 kHz    |          | 9.76 kH             | z        | 19.5  | kHz                | ;        | 39.1 kHz  |     |

|        | 1   | 0   | 1   | 0   | fclк/2 <sup>10</sup> |    | 1.95 kHz |          | 4.88 kH  | z                   | 9.76     | kHz   |                    | 19.5 kHz |           |     |

|        | 1   | 0   | 1   | 1   | fclк/2 <sup>11</sup> |    | 976      | 976 Hz   |          | 2.44 kH             | z        | 4.88  | kHz                | ę        | 9.76 kHz  |     |

|        | 1   | 1   | 0   | 0   | fclк/2 <sup>12</sup> |    | 488 Hz   |          | 1.22 kHz |                     | 2.44 kHz |       | 4                  | 4.88 kHz |           |     |

|        | 1   | 1   | 0   | 1   | fclк/2 <sup>13</sup> |    | 244      | l Hz     |          | 610 Hz              |          | 1.22  | kHz                | 2        | 2.44 kHz  |     |

|        | 1   | 1   | 1   | 0   | fclк/2 <sup>14</sup> |    | 122      | 2 Hz     |          | 305 Hz              |          | 610 I | Ηz                 |          | 1.22 kHz  |     |

|        | 1   | 1   | 1   | 1   | fclк/2 <sup>15</sup> |    | 61       | Hz       |          | 153 Hz              |          | 305 I | Ηz                 | (        | 610 Hz    |     |

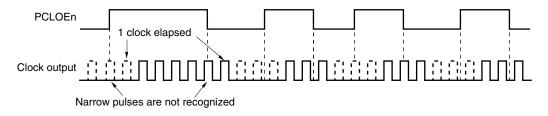

# Figure 8-10. Format of Timer Clock Select register m (TPSm)

Note When changing the clock selected for fcLK (by changing the system clock control register (CKC) value), stop timer array unit (TTm = 00FFH).

The timer array unit must also be stopped if the operating clock specified by using the CKSmn bit (fmck), the valid edge of the signal input from the TImn pin, or the subsystem clock divided by 4 (fsub/4) is selected as the count clock (ftclk).

Caution Be sure to clear bits 15 to 8 to "0".

Address: F01B6H, F01B7H (TPS0) After reset: 0000H R/W

F01DEH, F01DFH (TPS1)

Remarks 1. fcLK: CPU/peripheral hardware clock frequency

**2.** m: Unit number (m = 0, 1), k = 0, 178K0R/KC3-L, 78K0R/KD3-L, 78K0R/KE3-L: m = 0 78K0R/KF3-L, 78K0R/KG3-L: m = 0, 1

# (3) Operation of TOmn pin in slave channel output mode (TOMmn = 1)

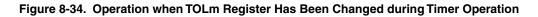

#### (a) When timer output level register m (TOLm) setting has been changed during timer operation

When the TOLm register setting has been changed during timer operation, the setting becomes valid at the generation timing of the TOmn pin change condition. Rewriting the TOLm register does not change the output level of the TOmn pin.

The operation when TOMmn is set to 1 and the value of the TOLm register is changed while the timer is operating (TEmn = 1) is shown below.

Remarks 1. Set:The output signal of the TOmn pin changes from inactive level to active level.Reset:The output signal of the TOmn pin changes from active level to inactive level.

| m: Unit number (m = 0, 1), n: Channel number (n = 0 to 7)             |                                                                                                                         |  |  |  |  |  |  |  |  |  |

|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| However, in case of the timer output pin (TOmn), mn changes as below. |                                                                                                                         |  |  |  |  |  |  |  |  |  |

| 78K0R/KC3-L (40-pin): mn = 02 to 07                                   |                                                                                                                         |  |  |  |  |  |  |  |  |  |

| 78K0R/KC3-L (44-pin, 48-pin):                                         | mn = 00 to 07                                                                                                           |  |  |  |  |  |  |  |  |  |

| 78K0R/KD3-L, 78K0R/KE3-L:                                             | mn = 00 to 07                                                                                                           |  |  |  |  |  |  |  |  |  |

| 78K0R/KF3-L, 78K0R/KG3-L:                                             | mn = 00 to 07, 10 to 13                                                                                                 |  |  |  |  |  |  |  |  |  |

|                                                                       | However, in case of the timer ou<br>78K0R/KC3-L (40-pin):<br>78K0R/KC3-L (44-pin, 48-pin):<br>78K0R/KD3-L, 78K0R/KE3-L: |  |  |  |  |  |  |  |  |  |

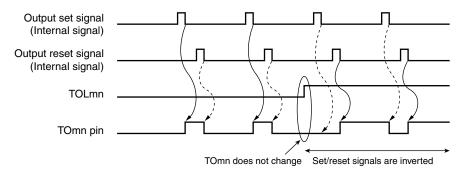

#### Figure 8-63. Example of Set Contents of Registers When One-Shot Pulse Output Function Is Used (Master Channel)

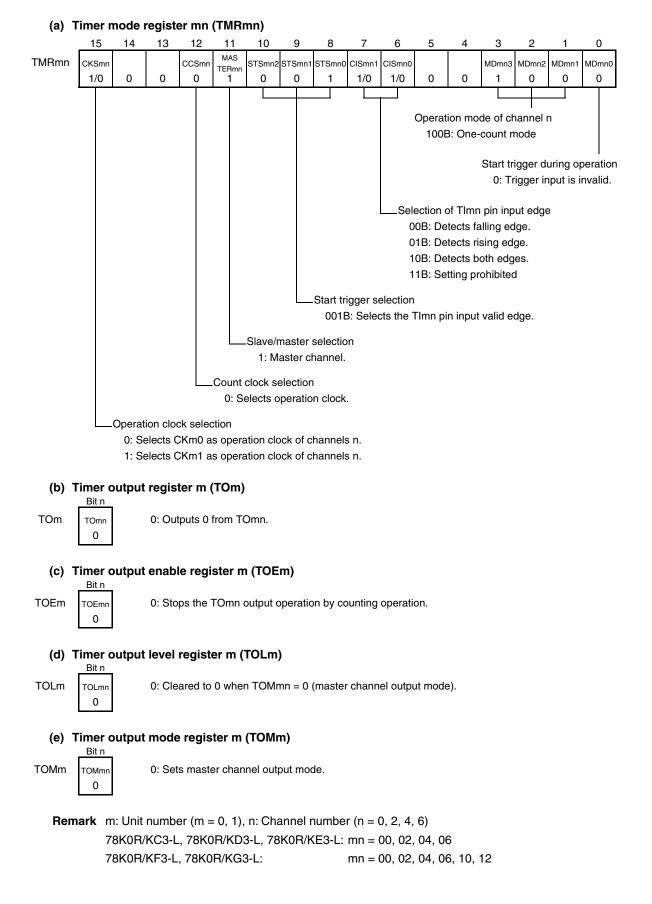

# 11.4 Operations of Clock Output/Buzzer Output Controller

One pin can be used to output a clock or buzzer sound.

The PCLBUZ0 pin outputs a clock/buzzer selected by the clock output select register 0 (CKS0).

The PCLBUZ1 pin outputs a clock/buzzer selected by the clock output select register 1 (CKS1).

# 11.4.1 Operation as output pin

The PCLBUZn pin is output as the following procedure.

- <1> Select the output frequency with bits 0 to 3 (CCSn0 to CCSn2, CSELn) of the clock output select register (CKSn) of the PCLBUZn pin (output in disabled status).

- <2> Set bit 7 (PCLOEn) of the CKSn register to 1 to enable clock/buzzer output.

- Remarks 1. The controller used for outputting the clock starts or stops outputting the clock one clock after enabling or disabling clock output (PCLOEn bit) is switched. At this time, pulses with a narrow width are not output. Figure 11-4 shows enabling or stopping output using the PCLOEn bit and the timing of outputting the clock.

- **2.** n = 0: 78K0R/KC3-L (48-pin), 78K0R/KD3-L

- n = 0, 1: 78K0R/KE3-L, 78K0R/KF3-L, 78K0R/KG3-L

#### Figure 11-4. Remote Control Output Application Example

# (8) Port mode registers 2, 15, and 8 Note (PM2, PM15, PM8 Note)

When using the ANI0/P20 to ANI7/P27, ANI8/P150 to ANI15/P157, and PGAI/P80 pins for analog input port, set the PM20 to PM27, PM150 to PM157, and PM80 bits to 1. The output latches of P20 to P27, P150 to P157, and P80 at this time may be 0 or 1.

If the PM20 to PM27, PM150 to PM157, and PM80 bits are set to 0, they cannot be used as analog input port pins. The PM2, PM15, and PM8 register can be set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation sets these registers to FFH.

Note Port mode register 8 is set only in the 78K0R/KC3-L, 78K0R/KD3-L, and 78K0R/KE3-L.

# Caution If a pin is set as an analog input port, not the pin level but "0" is always read.

Remark

P20/ANI0 to P27/ANI7, P150/ANI8, P151/ANI9:

78K0R/KC3-L (40-pin, 44-pin)

P20/ANI0 to P27/ANI7, P150/ANI8 to P152/ANI10:

78K0R/KC3-L (48-pin) and 78K0R/KD3-L

P20/ANI0 to P27/ANI7, P150/ANI8 to P153/ANI11:

78K0R/KE3-L, 78K0R/KF3-L

P20/ANI0 to P27/ANI7, P150/ANI8 to P153/ANI11:

78K0R/KE3-L, 78K0R/KF3-L

P20/ANI0 to P27/ANI7, P150/ANI8 to P157/ANI15:

78K0R/KE3-L, 78K0R/KF3-L

| Figure 13-11   | Formats of Port Mo   | de Registers 2-15  | and 8 (PM2 PM       | 15, PM8) (78K0R/KE3-L)                      |

|----------------|----------------------|--------------------|---------------------|---------------------------------------------|

| 1 iguie 10-11. | i ormats or i ort mo | ue negisters 2, 15 | , and o (i wiz, i w | 10, 100) (100000000000000000000000000000000 |

| Address: | FFF22H                                                                | After reset: FFH | R/W                           |      |       |       |       |       |  |  |  |

|----------|-----------------------------------------------------------------------|------------------|-------------------------------|------|-------|-------|-------|-------|--|--|--|

| Symbol   | 7                                                                     | 6                | 5                             | 4    | 3     | 2     | 1     | 0     |  |  |  |

| PM2      | PM27                                                                  | PM26             | PM25                          | PM24 | PM23  | PM22  | PM21  | PM20  |  |  |  |

| _        |                                                                       |                  |                               |      |       |       |       |       |  |  |  |

| Address: | FFF28H                                                                | After reset: FFH | R/W                           |      |       |       |       |       |  |  |  |

| Symbol   | 7                                                                     | 6                | 5                             | 4    | 3     | 2     | 1     | 0     |  |  |  |

| PM8      | 1                                                                     | 1                | 1                             | 1    | PM83  | PM82  | PM81  | PM80  |  |  |  |

| _        |                                                                       |                  |                               |      |       |       |       |       |  |  |  |

| Address: | FFF2FH                                                                | After reset: FFH | R/W                           |      |       |       |       |       |  |  |  |

| Symbol   | 7                                                                     | 6                | 5                             | 4    | 3     | 2     | 1     | 0     |  |  |  |

| PM15     | 1                                                                     | 1                | 1                             | 1    | PM153 | PM152 | PM151 | PM150 |  |  |  |

|          |                                                                       |                  |                               | •    |       |       |       |       |  |  |  |

|          | PMmn Pmn pin I/O mode selection (mn = 20 to 27, 150 to 153, 80 to 83) |                  |                               |      |       |       |       |       |  |  |  |

|          | 0                                                                     | Output mode      | uteut mede (euteut huffer en) |      |       |       |       |       |  |  |  |

| l | PMmn | Pmn pin I/O mode selection (mn = 20 to 27, 150 to 153, 80 to 83) |  |  |  |  |  |  |  |  |

|---|------|------------------------------------------------------------------|--|--|--|--|--|--|--|--|

|   | 0    | Output mode (output buffer on)                                   |  |  |  |  |  |  |  |  |

|   | 1    | Input mode (output buffer off)                                   |  |  |  |  |  |  |  |  |

Remark The figure shown above presents the format of port mode registers 2, 8 and 15 of the 78K0R/KE3-L product. See below for the format of the port mode registers of other products.

78K0R/KC3-L, 78K0R/KD3-L, 78K0R/KE3-L: 5.3 (1) Port mode registers (PMxx).

78K0R/KF3-L, 78K0R/KG3-L: 6.3 (1) Port mode registers (PMxx).

# (1) Register setting

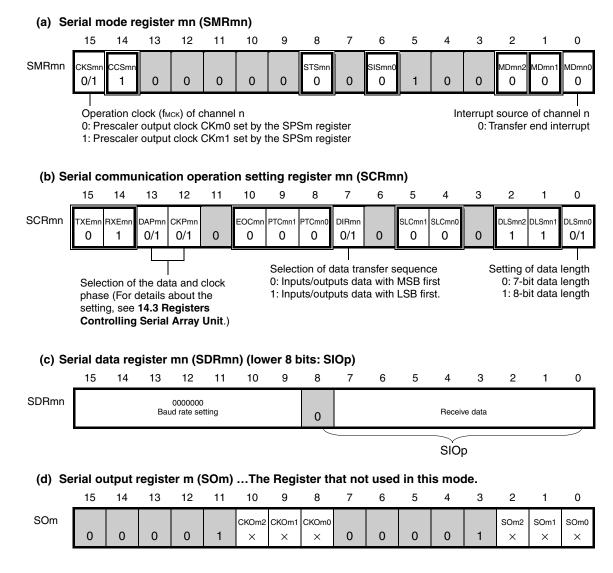

# Figure 14-60. Example of Contents of Registers for Slave Reception of 3-Wire Serial I/O (CSI00, CSI01, CSI10, CSI20, CSI40, CSI41) (1/2)

Notes 1. Those bits are invalid while operating serial allay unit 1.

2. Those bits are invalid while operating serial allay unit 2.

(Remark is listed on the next page.)

<R>

| SMRmn<br>Register |                 |            | 5          | SPSm F     | Registe    | r          |            |                                                             | Operation Cl                     | ock (fMCK) <sup>Note 1</sup> |

|-------------------|-----------------|------------|------------|------------|------------|------------|------------|-------------------------------------------------------------|----------------------------------|------------------------------|

| CKSmn             | PRS<br>m13      | PRS<br>m12 | PRS<br>m11 | PRS<br>m10 | PRS<br>m03 | PRS<br>m02 | PRS<br>m01 | PRS<br>m00                                                  |                                  | fclk = 20 MHz                |

| 0                 | Х               | Х          | Х          | Х          | 0          | 0          | 0          | 0                                                           | fclk                             | 20 MHz                       |

|                   | Х               | Х          | Х          | Х          | 0          | 0          | 0          | 1                                                           | fclк/2                           | 10 MHz                       |

|                   | Х               | Х          | Х          | Х          | 0          | 0          | 1          | 0                                                           | fclk/2 <sup>2</sup>              | 5 MHz                        |

|                   | Х               | Х          | Х          | Х          | 0          | 0          | 1          | 1                                                           | fclk/2 <sup>3</sup>              | 2.5 MHz                      |

|                   | Х               | Х          | Х          | Х          | 0          | 1          | 0          | 0                                                           | fc⊥ĸ/2⁴                          | 1.25 MHz                     |

|                   | Х               | Х          | Х          | Х          | 0          | 1          | 0          | 1                                                           | fclĸ/2⁵                          | 625 kHz                      |

|                   | Х               | Х          | Х          | Х          | 0          | 1          | 1          | 0                                                           | fclk/2 <sup>6</sup>              | 313 kHz                      |

|                   | Х               | Х          | Х          | Х          | 0          | 1          | 1          | 1                                                           | fclk/2 <sup>7</sup>              | 156 kHz                      |

|                   | Х               | Х          | Х          | Х          | 1          | 0          | 0          | 0                                                           | fclk/2 <sup>8</sup>              | 78.1 kHz                     |

|                   | Х               | Х          | Х          | Х          | 1          | 0          | 0          | 1                                                           | fclk/2 <sup>9</sup>              | 39.1 kHz                     |

|                   | Х               | Х          | Х          | Х          | 1          | 0          | 1          | 0                                                           | fclk/2 <sup>10</sup>             | 19.5 kHz                     |

|                   | Х               | Х          | Х          | Х          | 1          | 0          | 1          | 1                                                           | fclk/2 <sup>11</sup>             | 9.77 kHz                     |

|                   | Х               | Х          | Х          | Х          | 1          | 1          | 1          | 1                                                           | INTTM02 if $m = 0^{Note 2}$ , se | tting prohibited if m = 1    |

| 1                 | 0               | 0          | 0          | 0          | Х          | Х          | Х          | Х                                                           | fclk                             | 20 MHz                       |

|                   | 0               | 0          | 0          | 1          | Х          | Х          | Х          | Х                                                           | fclк/2                           | 10 MHz                       |

|                   | 0               | 0          | 1          | 0          | Х          | Х          | Х          | Х                                                           | fclk/2 <sup>2</sup>              | 5 MHz                        |

|                   | 0               | 0          | 1          | 1          | Х          | Х          | Х          | Х                                                           | fclk/2 <sup>3</sup>              | 2.5 MHz                      |

|                   | 0               | 1          | 0          | 0          | Х          | Х          | Х          | Х                                                           | fc⊥ĸ/2⁴                          | 1.25 MHz                     |

|                   | 0               | 1          | 0          | 1          | Х          | Х          | Х          | Х                                                           | fc∟ĸ/2⁵                          | 625 kHz                      |

|                   | 0               | 1          | 1          | 0          | Х          | Х          | Х          | Х                                                           | fclk/2 <sup>6</sup>              | 313 kHz                      |

|                   | 0               | 1          | 1          | 1          | Х          | Х          | Х          | Х                                                           | fclk/2 <sup>7</sup>              | 156 kHz                      |

|                   | 1               | 0          | 0          | 0          | Х          | Х          | Х          | Х                                                           | fclk/2 <sup>8</sup>              | 78.1 kHz                     |

|                   | 1               | 0          | 0          | 1          | Х          | Х          | Х          | Х                                                           | fclk/2 <sup>9</sup>              | 39.1 kHz                     |

|                   | 1               | 0          | 1          | 0          | Х          | Х          | Х          | Х                                                           | fclk/2 <sup>10</sup>             | 19.5 kHz                     |

|                   | 1               | 0          | 1          | 1          | Х          | Х          | Х          | Х                                                           | fськ/2 <sup>11</sup>             | 9.77 kHz                     |

|                   | 1 1 1 1 X X X X |            |            |            |            |            | Х          | INTTM02 if $m = 0^{Note 2}$ , setting prohibited if $m = 1$ |                                  |                              |

| Other than above  |                 |            |            |            |            |            |            | Setting prohibited                                          |                                  |                              |

Table 14-2. Selection of Operation Clock For 3-Wire Serial I/O

Notes 1. When changing the clock selected for fcLk (by changing the system clock control register (CKC) value), do so after having stopped (serial channel stop register m (STm) = 000FH) the operation of the serial array unit (SAU). When selecting INTTM02 for the operation clock, also stop the timer array unit 0 (timer channel stop register 0 (TT0) = 00FFH).

- 2. SAU0 can be operated at a fixed division ratio of the subsystem clock, regardless of the f<sub>CLK</sub> frequency (main system clock, sub system clock), by operating the interval timer for which f<sub>SUB</sub>/4<sup>Note 3</sup> has been selected as the count clock (setting the TIS02 bit of timer input select register 0 (TIS0) to 1) and selecting INTTM02 by using the SPS0 register in channel 2 of TAU0. When changing f<sub>CLK</sub>, however, SAU0 and TAU0 must be stopped as described in Note 1 above.

- 3. The 78K0R/KC3-L (40-pin) doesn't have the subsystem clock.

# Remarks 1. X: Don't care

| <b>2.</b> m | <ol> <li>m: Unit number (m = 0 to 2), n: Channel number (n = 0 to 2)</li> </ol> |                           |  |  |  |  |  |  |  |  |  |

|-------------|---------------------------------------------------------------------------------|---------------------------|--|--|--|--|--|--|--|--|--|

| 78          | 8K0R/KC3-L, 78K0R/KD3-L, 78K0R/KE3-L:                                           | mn = 00 to 02             |  |  |  |  |  |  |  |  |  |

| 78          | 8K0R/KF3-L (μ PD78F1010, 78F1011, 78F1012):                                     | mn = 00 to 02, 10         |  |  |  |  |  |  |  |  |  |

| 78          | 8K0R/KF3-L (μ PD78F1027, 78F1028):                                              | mn = 00 to 02, 10, 20, 21 |  |  |  |  |  |  |  |  |  |

| 78          | 8K0R/KG3-L ( <i>µ</i> PD78F1013, 78F1014):                                      | mn = 00 to 02, 10         |  |  |  |  |  |  |  |  |  |

| 78          | 8K0R/KG3-L ( <i>µ</i> PD78F1029, 78F1030):                                      | mn = 00 to 02, 10, 20, 21 |  |  |  |  |  |  |  |  |  |

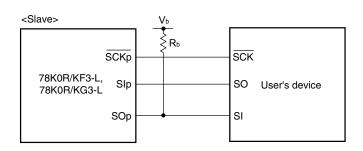

# 14.9.2 78K0R/KF3-L, 78K0R/KG3-L

| SE           | MD  | MD  | SOE | SO            | СКО           | TXE | RXE | PM          | P10         | PM           | P11<br>Note 2 |             | P12         | Operation mode      |               | Pin Function                           |                   |  |

|--------------|-----|-----|-----|---------------|---------------|-----|-----|-------------|-------------|--------------|---------------|-------------|-------------|---------------------|---------------|----------------------------------------|-------------------|--|

| 00<br>Note 1 | 002 | 001 | 00  | 00            | 00            | 00  | 00  | 10          |             | 11<br>Note 2 | Note 2        | 12          |             |                     | SCK00/<br>P10 | SI00/<br>RxD0/P11<br><sub>Note 2</sub> | SO00/<br>TxD0/P12 |  |

| 0            | 0   | 0   | 0   | 1             | 1             | 0   | 0   | ×<br>Note 3 | ×<br>Note 3 | ×<br>Note 3  | ×<br>Note 3   | ×<br>Note 3 | ×<br>Note 3 | Operation stop      | P10           | P11                                    | P12               |  |

|              | 0   | 1   |     |               |               |     |     |             |             |              |               |             |             | mode                |               | P11/RxD0                               |                   |  |

| 1            | 0   | 0   | 0   | 1             | 1             | 0   | 1   | 1           | ×           | 1            | ×             | ×<br>Note 3 | ×<br>Note 3 | Slave CSI00         | SCK00         | SI00                                   | P12               |  |

|              |     |     |     |               |               |     |     |             |             |              |               | NOLE 3      | Note 5      | reception           | (input)       |                                        |                   |  |

|              |     |     | 1   | 0/1<br>Note 4 | 1             | 1   | 0   | 1           | ×           | ×<br>Note 3  | ×<br>Note 3   | 0           | 1           | Slave CSI00         | SCK00         | P11                                    | SO00              |  |

|              |     |     |     | NOLE 4        |               |     |     |             |             | NOLE 3       | NOLE 3        |             |             | transmission        | (input)       |                                        |                   |  |

|              |     |     | 1   | 0/1<br>Note 4 | 1             | 1   | 1   | 1           | ×           | 1            | ×             | 0           | 1           | Slave CSI00         | SCK00         | SI00                                   | SO00              |  |

|              |     |     |     | NOTE 4        |               |     |     |             |             |              |               |             |             | transmission/       | (input)       |                                        |                   |  |

|              |     |     |     |               |               |     |     |             |             |              |               |             |             | reception           |               |                                        |                   |  |

|              |     |     | 0   | 1             | 0/1<br>Note 4 | 0   | 1   | 0           | 1           | 1            | ×             | ×<br>Note 3 | ×<br>Note 3 | Master CSI00        | SCK00         | SI00                                   | P12               |  |

|              |     |     |     |               | NOLE 4        |     |     |             |             |              |               | Note 3      | Note 3      | reception           | (output)      |                                        |                   |  |

|              |     |     | 1   | 0/1           | 0/1<br>Note 4 | 1   | 0   | 0           | 1           | ×            | ×             | 0           | 1           | Master CSI00        | SCK00         | P11                                    | SO00              |  |

|              |     |     |     | Note 4        | Note 4        |     |     |             |             | Note 3       | Note 3        |             |             | transmission        | (output)      |                                        |                   |  |

|              |     |     | 1   | 0/1           | 0/1           | 1   | 1   | 0           | 1           | 1            | ×             | 0           | 1           | Master CSI00        | SCK00         | SI00                                   | SO00              |  |

|              |     |     |     | Note 4        | Note 4        |     |     |             |             |              |               |             |             | transmission/       | (output)      |                                        |                   |  |

|              |     |     |     |               |               |     |     |             |             |              |               |             |             | reception           |               |                                        |                   |  |

|              | 0   | 1   | 1   | 0/1           | 1             | 1   | 0   | ×           | ×           | ×            | ×             | 0           | 1           | UART0               | P10           | P11/RxD0                               | TxD0              |  |

|              |     |     |     | Note 4        |               |     |     | Note 3      | NOTE 3      | Note 3       | NOTE 3        |             |             | transmission Note 5 |               |                                        |                   |  |

# Table 14-9. Relationship between register settings and pins (Channel 0 of unit 0: CSI00, UART0 transmission)

**Notes 1.** Serial channel enable register 0 (SE0) is a read-only status register which is set using serial channel start register 0 (SS0) and serial channel stop register 0 (ST0).

2. When channel 1 of unit 0 is set to UART0 reception, this pin becomes an RxD0 function pin (refer to Table 14-10). In this case, operation stop mode or UART0 transmission must be selected for channel 0 of unit 0.

- **3.** This pin can be set as a port function pin.

- This is 0 or 1, depending on the communication operation. For details, refer to 14.3 (12) Serial output register m (SOm).

- 5. When using UART0 transmission and reception in a pair, set channel 1 of unit 0 to UART0 reception (refer to Table 14-10).

Remark X: Don't care

# 17.5 Example of Setting of DMA Controller

# 17.5.1 CSI consecutive transmission

A flowchart showing an example of setting for CSI consecutive transmission is shown below.

- Consecutive transmission of CSI10 (256 bytes)

- DMA channel 0 is used for DMA transfer.

- DMA start source: INTCSI10 (software trigger (STG0) only for the first start source)

- Interrupt of CSI10 is specified by IFC03 to IFC00 = 1000B.

- Transfers FFB00H to FFBFFH (256 bytes) of RAM to FFF44H of the data register (SIO10) of CSI.

Remark IFC03 to IFC00: Bits 3 to 0 of DMA mode control registers 0 (DMC0)

| Instruction | Mnemonic | Operands              | Bytes | Clo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | cks    | Operation                                                                   |   | Flag |    |

|-------------|----------|-----------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------------------------------------------------------------|---|------|----|

| Group       |          |                       |       | Note 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Note 2 |                                                                             | Z | AC   | CY |

| Condition   | BF       | saddr.bit, \$addr20   | 4     | Note 1Note 2 $3/5^{Note 3}$ - $PC \leftarrow PC + 4 + jdisp8$ if (saddr).bit = 0 $3/5^{Note 3}$ - $PC \leftarrow PC + 4 + jdisp8$ if sfr.bit = 0 $3/5^{Note 3}$ - $PC \leftarrow PC + 3 + jdisp8$ if A.bit = 0 $3/5^{Note 3}$ - $PC \leftarrow PC + 3 + jdisp8$ if PSW.bit = 0 $3/5^{Note 3}$ - $PC \leftarrow PC + 3 + jdisp8$ if (HL).bit = 0 $3/5^{Note 3}$ - $PC \leftarrow PC + 3 + jdisp8$ if (HL).bit = 0 $4/6^{Note 3}$ $7/8$ $PC \leftarrow PC + 4 + jdisp8$ if (ES, HL).bit = 0 $3/5^{Note 3}$ - $PC \leftarrow PC + 4 + jdisp8$ if (saddr).bit = 1<br>then reset (saddr).bit $3/5^{Note 3}$ - $PC \leftarrow PC + 4 + jdisp8$ if sfr.bit = 1<br>then reset sfr.bit $3/5^{Note 3}$ - $PC \leftarrow PC + 3 + jdisp8$ if A.bit = 1<br>then reset A.bit |        |                                                                             | _ |      |    |

| al branch   |          | sfr.bit, \$addr20     | 4     | 3/5 <sup>Note 3</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -      | $PC \leftarrow PC + 4 + jdisp8$ if sfr.bit = 0                              |   |      |    |

|             |          | A.bit, \$addr20       | 3     | 3/5 <sup>Note 3</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -      | $PC \leftarrow PC + 3 + jdisp8$ if A.bit = 0                                |   |      |    |

|             |          | PSW.bit, \$addr20     | 4     | 3/5 <sup>Note 3</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -      | $PC \leftarrow PC + 4 + jdisp8$ if PSW.bit = 0                              |   |      |    |

|             |          | [HL].bit, \$addr20    | 3     | 3/5 <sup>Note 3</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6/7    | $PC \leftarrow PC + 3 + jdisp8$ if (HL).bit = 0                             |   |      |    |

|             |          | ES:[HL].bit, \$addr20 | 4     | 4/6 <sup>Note 3</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7/8    | $PC \leftarrow PC + 4 + jdisp8$ if (ES, HL).bit = 0                         |   |      |    |

|             | BTCLR    | saddr.bit, \$addr20   | 4     | 3/5 <sup>Note 3</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -      |                                                                             |   |      |    |

|             |          | sfr.bit, \$addr20     | 4     | 3/5 <sup>Note 3</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -      |                                                                             |   |      |    |

|             |          | A.bit, \$addr20       | 3     | 3/5 <sup>Note 3</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -      |                                                                             |   |      |    |

|             |          | PSW.bit, \$addr20     | 4     | 3/5 <sup>Note 3</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -      | $PC \leftarrow PC + 4 + jdisp8$ if PSW.bit = 1<br>then reset PSW.bit        | × | ×    | ×  |

|             |          | [HL].bit, \$addr20    | 3     | 3/5 <sup>Note 3</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -      | $PC \leftarrow PC + 3 + jdisp8$ if (HL).bit = 1 then reset (HL).bit         |   |      |    |

|             |          | ES:[HL].bit, \$addr20 | 4     | 4/6 <sup>Note 3</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -      | $PC \leftarrow PC + 4 + jdisp8$ if (ES, HL).bit = 1 then reset (ES, HL).bit |   |      |    |

| Conditional | SKC      | -                     | 2     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | _      | Next instruction skip if CY = 1                                             |   |      |    |

| skip        | SKNC     | -                     | 2     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -      | Next instruction skip if CY = 0                                             |   |      |    |

|             | SKZ      | -                     | 2     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | _      | Next instruction skip if $Z = 1$                                            |   |      |    |

|             | SKNZ     | -                     | 2     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -      | Next instruction skip if $Z = 0$                                            |   |      |    |

|             | SKH      | -                     | 2     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -      | Next instruction skip if $(Z \lor CY) = 0$                                  |   |      |    |

|             | SKNH     | -                     | 2     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -      | Next instruction skip if $(Z \lor CY) = 1$                                  |   |      |    |

| CPU         | SEL      | RBn                   | 2     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -      | RBS[1:0] ← n                                                                |   |      |    |

| control     | NOP      | -                     | 1     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -      | No Operation                                                                |   |      |    |

|             | EI       | -                     | 3     | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -      | IE $\leftarrow$ 1(Enable Interrupt)                                         |   |      |    |

|             | DI       | -                     | 3     | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -      | $IE \leftarrow 0(Disable Interrupt)$                                        |   |      |    |

|             | HALT     | -                     | 2     | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -      | Set HALT Mode                                                               |   |      |    |

|             | STOP     | _                     | 2     | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | _      | Set STOP Mode                                                               |   |      |    |

| Table 29-5. | Operation List (17/17) |

|-------------|------------------------|

|             |                        |

Notes 1. When the internal RAM area, SFR area, or extended SFR area is accessed, or for an instruction with no data access.

- 2. When the program memory area is accessed.

- 3. This indicates the number of clocks "when condition is not met/when condition is met".

- **Remarks 1.** One instruction clock cycle is one cycle of the CPU clock (fcPu) selected by the system clock control register (CKC).

- 2. This number of clocks is for when the program is in the internal ROM (flash memory) area. When fetching an instruction from the internal RAM area, the number of clocks is twice the number of clocks plus 3, maximum.

- **3.** n indicates the number of register banks (n = 0 to 3)

# (5) Communication at different potential (2.5 V, 3 V) (UART mode) (dedicated baud rate generator output) (2/2) ( $T_A = -40$ to +85°C, 2.7 V $\leq$ V<sub>DD</sub> = EV<sub>DD</sub> $\leq$ 5.5 V, V<sub>SS</sub> = EV<sub>SS</sub> = AV<sub>SS</sub> = 0 V)

| Parameter     | Symbol |              | Condit                                 | tions                                                          | MIN. | TYP. | MAX.                  | Unit |

|---------------|--------|--------------|----------------------------------------|----------------------------------------------------------------|------|------|-----------------------|------|

| Transfer rate |        | Transmission | $4.0~V \leq V_{\text{DD}} \leq 5.5~V,$ |                                                                |      |      | Note 1                |      |

|               |        |              | $2.7~V \leq V_b \leq 4.0~V$            | fclk = 16.8 MHz, fmck = fclk,                                  |      |      | 2.8 <sup>Note 2</sup> | Mbps |

|               |        |              |                                        | $C_{\rm b}$ = 50 pF, $R_{\rm b}$ = 1.4 kΩ, $V_{\rm b}$ = 2.7 V |      |      |                       |      |

|               |        |              | $2.7~V \leq V_{\text{DD}} \leq 4.0~V,$ |                                                                |      |      | Note 3                |      |

|               |        |              | $2.3~V \le V_b \le 2.7~V$              | fclк = 19.2 MHz, fмcк = fclк,                                  |      |      | 1.2 <sup>Note 4</sup> | Mbps |

|               |        |              |                                        | $C_{\rm b}$ = 50 pF, $R_{\rm b}$ = 2.7 kΩ, $V_{\rm b}$ = 2.3 V |      |      |                       |      |

**Notes 1.** The smaller maximum transfer rate derived by using fMCK/6 or the following expression is the valid maximum transfer rate.

Expression for calculating the transfer rate when 4.0 V  $\leq$  V\_DD = EV\_DD  $\leq$  5.5 V and 2.7 V  $\leq$  V\_b  $\leq$  4.0 V

Maximum transfer rate =

$$\frac{1}{\{-C_b \times R_b \times \ln (1 - \frac{2.2}{V_b})\} \times 3}$$

[bps]

Baud rate error (theoretical value) =

$$\frac{\frac{1}{\text{Transfer rate} \times 2} - \{ -C_b \times R_b \times \ln(1 - \frac{2.2}{V_b}) \}}{(\frac{1}{\text{Transfer rate}}) \times \text{Number of transferred bits}} \times 100 [\%]$$

\* This value is the theoretical value of the relative difference between the transmission and reception sides.

- 2. This value as an example is calculated when the conditions described in the "Conditions" column are met. Refer to **Note 1** above to calculate the maximum transfer rate under conditions of the customer.

- **3.** The smaller maximum transfer rate derived by using fMCK/6 or the following expression is the valid maximum transfer rate.

Expression for calculating the transfer rate when 2.7 V  $\leq$  V\_DD = EV\_DD  $\leq$  4.0 V and 2.3 V  $\leq$  V\_b  $\leq$  2.7 V

Maximum transfer rate =

$$\frac{1}{\{-C_b \times R_b \times \ln (1 - \frac{2.0}{V_b})\} \times 3}$$

[bps]

Baud rate error (theoretical value) =

$$\frac{1}{\frac{1}{\text{Transfer rate} \times 2}} - \left\{ -C_b \times R_b \times \ln \left(1 - \frac{2.0}{V_b}\right) \right\} \times 100 [\%]$$

$$\left( \frac{1}{\frac{1}{\text{Transfer rate}}} \right) \times \text{Number of transferred bits}$$

\* This value is the theoretical value of the relative difference between the transmission and reception sides.

- 4. This value as an example is calculated when the conditions described in the "Conditions" column are met. Refer to Note 3 above to calculate the maximum transfer rate under conditions of the customer.

- Caution Select the TTL input buffer for the RxDq pin and the N-ch open drain output (VDD tolerance) mode for the TxDq pin by using port input mode register g (PIMg) and port output mode register g (POMg).

(Remarks are given on the next page.)

## 31.3.4 Recommended oscillator circuit constants

# (1) X1 oscillation: Ceramic resonator (AMPH = 0, RMC = 00H, $T_A = -40$ to +85°C)

| Manufacturer  | Part Number     | SMD/<br>Lead | Frequency<br>(MHz) | Recomm        | ended Circuit C | Constants | Oscillation<br>Voltage Range |          |  |

|---------------|-----------------|--------------|--------------------|---------------|-----------------|-----------|------------------------------|----------|--|

|               |                 |              |                    | C1 (pF)       | C2 (pF)         | Rd (kΩ)   | MIN. (V)                     | MAX. (V) |  |

| Murata        | CSTCC2M00G56-R0 | SMD          | 2.0                | Internal (47) | Internal (47)   | 0         | 1.8                          | 5.5      |  |

| Manufacturing | CSTCR4M00G55-R0 | SMD          | 4.0                | Internal (39) | Internal (39)   | 0         |                              |          |  |

| Co., Ltd.     | CSTLS4M00G56-B0 | Lead         |                    | Internal (47) | Internal (47)   | 0         |                              |          |  |

|               | CSTCR4M19G55-R0 | SMD          | 4.194              | Internal (39) | Internal (39)   | 0         |                              |          |  |

|               | CSTLS4M19G56-B0 | Lead         |                    | Internal (47) | Internal (47)   | 0         |                              |          |  |

|               | CSTCR4M91G55-R0 | SMD          | 4.915              | Internal (39) | Internal (39)   | 0         |                              |          |  |

|               | CSTLS4M91G53-B0 | Lead         |                    | Internal (15) | Internal (15)   | 0         |                              |          |  |

|               | CSTCR5M00G55-R0 | SMD          | 5.0                | Internal (39) | Internal (39)   | 0         |                              |          |  |

|               | CSTLS5M00G53-B0 | Lead         |                    | Internal (15) | Internal (15)   | 0         |                              |          |  |

|               | CSTCR6M00G53-R0 | SMD          | 6.0                | Internal (15) | Internal (15)   | 0         |                              |          |  |

|               | CSTLS6M00G53-B0 | Lead         |                    | Internal (15) | Internal (15)   | 0         |                              |          |  |

|               | CSTCE8M00G55-R0 | SMD          | 8.0                | Internal (33) | Internal (33)   | 0         |                              |          |  |

|               | CSTLS8M00G53-B0 | Lead         |                    | Internal (15) | Internal (15)   | 0         |                              |          |  |

|               | CSTCE8M38G55-R0 | SMD          | 8.388              | Internal (33) | Internal (33)   | 0         |                              |          |  |

|               | CSTLS8M38G53-B0 | Lead         |                    | Internal (15) | Internal (15)   | 0         |                              |          |  |

|               | CSTCE10M0G52-R0 | SMD          | 10.0               | Internal (10) | Internal (10)   | 0         | ]                            |          |  |

|               | CSTLS10M0G53-B0 | Lead         |                    | Internal (15) | Internal (15)   | 0         |                              |          |  |

Caution The oscillator constants shown above are reference values based on evaluation in a specific environment by the resonator manufacturer. If it is necessary to optimize the oscillator characteristics in the actual application, apply to the resonator manufacturer for evaluation on the implementation circuit. The oscillation voltage and oscillation frequency only indicate the oscillator characteristic. Use the 78K0R/KF3-L, 78K0R/KG3-L so that the internal operation conditions are within the specifications of the DC and AC characteristics.

| $(T_{A} = -40 \text{ to } +85^{\circ}\text{C}, 1.8 \text{ V} \le \text{V}_{DD} = \text{EV}_{DD0} = \text{EV}_{DD1} \le 5.5 \text{ V}, 1.8 \text{ V} \le \text{AV}_{REF} \le \text{V}_{DD}, \text{V}_{SS} = \text{EV}_{SS0} = \text{EV}_{SS1} = \text{AV}_{SS1} = \text{AV}_{S$ |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|