Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | 78K/0R                                                                               |

| Core Size                  | 16-Bit                                                                               |

| Speed                      | 20MHz                                                                                |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                     |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                              |

| Number of I/O              | 66                                                                                   |

| Program Memory Size        | 64KB (64K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 4K x 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                          |

| Data Converters            | A/D 12x10b                                                                           |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 80-LQFP                                                                              |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f1010gc-gad-ax |

|                            |                                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

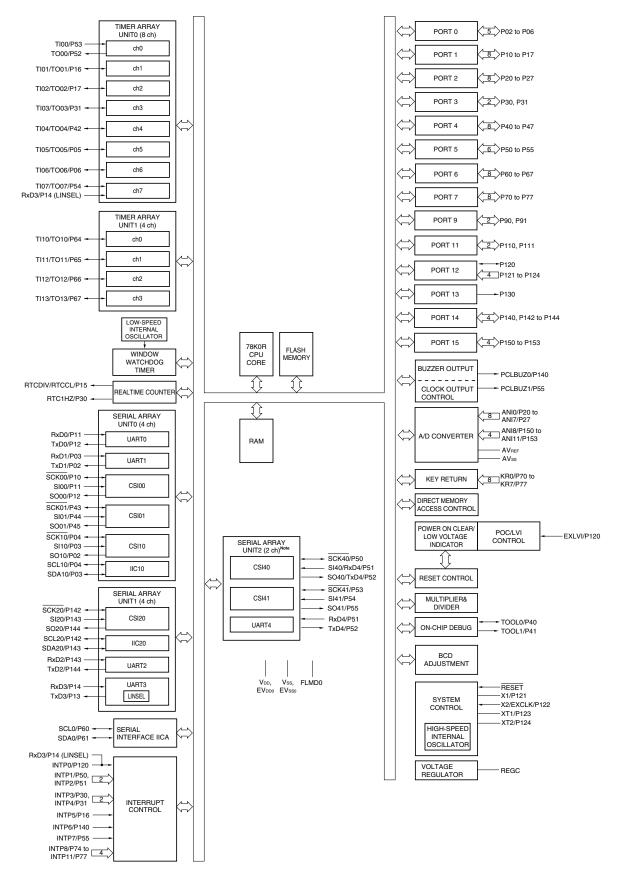

# 1.6.4 78K0R/KF3-L

**Note** Serial array unit 2 is only mounted in the  $\mu$  PD78F1027 and 78F1028.

|                                                         |                                                                                                |                                                                                                                                                                                                                                                                                                                                             |                              |             |             |             | 1           |             |                               | (2/2)                         |  |  |  |  |

|---------------------------------------------------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-------------|-------------|-------------|-------------|-------------|-------------------------------|-------------------------------|--|--|--|--|

| Iter                                                    | n                                                                                              | μ PD78F1010                                                                                                                                                                                                                                                                                                                                 | μ PD78F1011                  | 78K0R/KF3-  | r           | <u> </u>    | r           | /KG3-L      | ~                             |                               |  |  |  |  |

|                                                         |                                                                                                |                                                                                                                                                                                                                                                                                                                                             |                              | μ PD78F1012 | μ PD78F1027 | μ PD78F1028 | μ PD78F1013 | μ PD78F1014 | μ PD78F1029 <sup>Note 1</sup> | μ PD78F1030 <sup>Note 1</sup> |  |  |  |  |

| Clock output/buzze                                      |                                                                                                | 2                                                                                                                                                                                                                                                                                                                                           |                              |             |             |             |             |             |                               |                               |  |  |  |  |

|                                                         | (periphe<br>• 256 Hz                                                                           | <ul> <li>2.44 kHz, 4.88 kHz, 9.76 kHz, 1.25 MHz, 2.5 MHz, 5 MHz, 10 MHz<br/>(peripheral hardware clock: fMAIN = 20 MHz operation)</li> <li>256 Hz, 512 Hz, 1.024 kHz, 2.048 kHz, 4.096 kHz, 8.192 kHz, 16.384 kHz, 32.768 kHz<br/>(Subsystem clock: fsuB = 32.768 kHz operation)</li> </ul>                                                 |                              |             |             |             |             |             |                               |                               |  |  |  |  |

| 10-bit resolution A/<br>(AV <sub>REF</sub> = 1.8 to 5.5 |                                                                                                |                                                                                                                                                                                                                                                                                                                                             |                              | 12 channel  | S           |             |             | 16 ch       | annels                        |                               |  |  |  |  |

| Comparators                                             |                                                                                                |                                                                                                                                                                                                                                                                                                                                             | _                            |             |             |             |             |             |                               |                               |  |  |  |  |

| Programmable gai                                        | n amplifiers                                                                                   |                                                                                                                                                                                                                                                                                                                                             |                              |             |             | _           |             |             |                               |                               |  |  |  |  |

| Serial interface                                        | <ul> <li>CSI: 1 d</li> <li>CSI: 1 d</li> <li>UART s</li> </ul>                                 | <ul> <li>CSI: 2 channels/UART: 1 channel</li> <li>CSI: 1 channel/UART: 1 channel/simplified I<sup>2</sup>C: 1 channel</li> <li>CSI: 1 channel/UART: 1 channel/simplified I<sup>2</sup>C: 1 channel</li> <li>UART supporting LIN-bus: 1 channel</li> <li>CSI: 2 channels/UART: 1 channel (µ PD78F1027, 78F1028, 78F1029, 78F1030)</li> </ul> |                              |             |             |             |             |             |                               |                               |  |  |  |  |

|                                                         | I <sup>2</sup> C bus                                                                           |                                                                                                                                                                                                                                                                                                                                             |                              |             |             | 1 channe    | I           |             | -                             |                               |  |  |  |  |

| Multiplier/divider                                      |                                                                                                | <ul> <li>16 bits × 16 bits = 32 bits (multiplication)</li> <li>32 bits ÷ 32 bits = 32 bits (division)</li> </ul>                                                                                                                                                                                                                            |                              |             |             |             |             |             |                               |                               |  |  |  |  |

| DMA controller                                          |                                                                                                | 2 channel                                                                                                                                                                                                                                                                                                                                   | 2 channels                   |             |             |             |             |             |                               |                               |  |  |  |  |

| Vectored interrupt                                      | Internal                                                                                       |                                                                                                                                                                                                                                                                                                                                             | 33                           |             | 3           | 35          | ;           | 33          | 3                             | 35                            |  |  |  |  |

| sources                                                 | External                                                                                       |                                                                                                                                                                                                                                                                                                                                             |                              |             |             | 13          |             |             |                               |                               |  |  |  |  |

| Key interrupt                                           |                                                                                                | 8 channels (KR0 to KR7)                                                                                                                                                                                                                                                                                                                     |                              |             |             |             |             |             |                               |                               |  |  |  |  |

| Reset                                                   | <ul><li>Internal</li><li>Internal</li><li>Internal</li><li>Internal</li><li>Internal</li></ul> | <ul> <li>Reset by RESET pin</li> <li>Internal reset by watchdog timer</li> <li>Internal reset by power-on-clear</li> <li>Internal reset by low-voltage detector</li> <li>Internal reset by illegal instruction execution <sup>Note 2</sup></li> <li>Internal reset by a reset processing check error</li> </ul>                             |                              |             |             |             |             |             |                               |                               |  |  |  |  |

| Power-on-clear cire                                     |                                                                                                | <ul> <li>Power-on-reset: 1.61 ±0.09 V</li> <li>Power-down-reset: 1.59 ±0.09 V</li> </ul>                                                                                                                                                                                                                                                    |                              |             |             |             |             |             |                               |                               |  |  |  |  |

| Low-voltage detect                                      | tor                                                                                            | 1.91 V to                                                                                                                                                                                                                                                                                                                                   | 1.91 V to 4.22 V (16 stages) |             |             |             |             |             |                               |                               |  |  |  |  |

| On-chip debug fun                                       | ction                                                                                          | Provided                                                                                                                                                                                                                                                                                                                                    |                              |             |             |             |             |             |                               |                               |  |  |  |  |

| Power supply volta                                      | ige                                                                                            | V <sub>DD</sub> = 1.8 to 5.5 V                                                                                                                                                                                                                                                                                                              |                              |             |             |             |             |             |                               |                               |  |  |  |  |

| Operating ambient                                       | temperature                                                                                    | T <sub>A</sub> = -40 to +85 °C                                                                                                                                                                                                                                                                                                              |                              |             |             |             |             |             |                               |                               |  |  |  |  |

**Notes 1.** The  $\mu$ PD78F1029 and  $\mu$ PD78F1030 don't have the FBGA package.

2. The illegal instruction is generated when instruction code FFH is executed.

Reset by the illegal instruction execution not issued by emulation with the in-circuit emulator or on-chip debug emulator.

## 2.2.4 P30 to P33 (port 3)

P30 to P33 function as an I/O port. These pins also function as serial interface data I/O, clock I/O, and external interrupt request input.

Input to the P30 and P31 pins can be specified through a normal input buffer or a TTL input buffer in 1-bit units, using port input mode register 3 (PIM3).

Output from the P30 to P32 pins can be specified as normal CMOS output or N-ch open-drain output (V<sub>DD</sub> tolerance) in 1-bit units, using port output mode register 3 (POM3).

|                               | 78K0R/KC3-L<br>(μPD78F100y: y = 0 to 3) |              |              |              | 78K0R/KC3-L (48-pin)<br>(μPD78F100y: y = 1 to 3) | 78K0R/KD3-L<br>(μPD78F100y: y = 4 to 6) | 78K0R/KE3-L<br>(μPD78F100y: y = 7 to 9) |

|-------------------------------|-----------------------------------------|--------------|--------------|--------------|--------------------------------------------------|-----------------------------------------|-----------------------------------------|

|                               | 40-pin                                  | 44-pin       |              |              |                                                  |                                         |                                         |

| P30/SO10/TxD1                 | r                                       | V            | $\checkmark$ | $\checkmark$ | $\checkmark$                                     |                                         |                                         |

| P31/SI10/RxD1/<br>SDA10/INTP1 | n                                       | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$                                     |                                         |                                         |

| P32/SCK10/<br>SCL10/INTP2     | $\checkmark$                            |              | $\checkmark$ | $\checkmark$ | $\checkmark$                                     |                                         |                                         |

| P33                           | -                                       | -            | _            | _            | $\checkmark$                                     |                                         |                                         |

# **Remark** $\sqrt{}$ : Mounted

The following operation modes can be specified in 1-bit units.

#### (1) Port mode

P30 to P33 function as an I/O port. P30 to P33 can be set to input or output port in 1-bit units using port mode register 3 (PM3). Use of an on-chip pull-up resistor can be specified by pull-up resistor option register 3 (PU3).

#### (2) Control mode

P30 to P33 function as serial interface data I/O, clock I/O, and external interrupt request input.

#### (a) SI10

This is a serial data input pin of serial interface CSI10.

#### (b) SO10

This is a serial data output pin of serial interface CSI10.

#### (c) SCK10

This is a serial clock I/O pin of serial interface CSI10.

#### (d) TxD1

This is a serial data output pin of serial interface UART1.

#### (e) RxD1

This is a serial data input pin of serial interface UART1.

# (2) Non-port functions (1/3): 78K0R/KF3-L

| Function Name        | I/O    | Function                                                                                                                                             | After Reset   | Alternate Function                             |

|----------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------------------------------------------|

| ANI0 to ANI7         | Input  | A/D converter analog input                                                                                                                           | Digital input | P20 to P27                                     |

| ANI8 to ANI11        |        |                                                                                                                                                      | port          | P150 to P153                                   |

| EXLVI                | Input  | Potential input for external low-voltage detection                                                                                                   | Input port    | P120/INTP0                                     |

| INTP0                | Input  | External interrupt request input for which the valid edge (rising                                                                                    | Input port    | P120/EXLVI                                     |

| INTP1                |        | edge, falling edge, or both rising and falling edges) can be                                                                                         |               | P50/SCK40 <sup>Note</sup>                      |

| INTP2                |        | specified                                                                                                                                            |               | P51/SI40 <sup>Note</sup> /RxD4 <sup>Note</sup> |

| INTP3                |        |                                                                                                                                                      |               | P30/RTC1HZ                                     |

| INTP4                |        |                                                                                                                                                      |               | P31/TI03/TO03                                  |

| INTP5                |        |                                                                                                                                                      |               | P16/TI01/TO01                                  |

| INTP6                |        |                                                                                                                                                      |               | P140/PCLBUZ0                                   |

| INTP7                |        |                                                                                                                                                      |               | P55/PCLBUZ1/<br>SO41 <sup>Note</sup>           |

| INTP8 to<br>INTP11   |        |                                                                                                                                                      |               | P74/KR4 to P77/KR7                             |

| KR0 to KR3           | Input  | Key interrupt input                                                                                                                                  | Input port    | P70 to P73                                     |

| KR4 to KR7           |        |                                                                                                                                                      |               | P74/INTP8 to<br>P77/INTP11                     |

| PCLBUZ0              | Output | Clock output/buzzer output                                                                                                                           | Input port    | P140/INTP6                                     |

| PCLBUZ1              |        |                                                                                                                                                      |               | P55/INTP7                                      |

| REGC                 | _      | Connecting regulator output (2.4 V) stabilization capacitance for internal operation.<br>Connect to Vss via a capacitor (0.47 to 1 $\mu$ F: target). | _             | -                                              |

| RTCDIV               | Output | Real-time counter clock (32 kHz divided frequency) output                                                                                            | Input port    | P15/RTCCL                                      |

| RTCCL                | Output | Real-time counter clock (32 kHz original oscillation) output                                                                                         | Input port    | P15/RTCDIV                                     |

| RTC1HZ               | Output | Real-time counter correction clock (1 Hz) output                                                                                                     | Input port    | P30/INTP3                                      |

| RESET                | Input  | System reset input                                                                                                                                   | -             | -                                              |

| RxD0                 | Input  | Serial data input to UART0                                                                                                                           | Input port    | P11/SI00                                       |

| RxD1                 | Input  | Serial data input to UART1                                                                                                                           | Input port    | P03/SI10/SDA10                                 |

| RxD2                 | Input  | Serial data input to UART2                                                                                                                           | Input port    | P143/SI20/SDA20                                |

| RxD3                 | Input  | Serial data input to UART3                                                                                                                           | Input port    | P14                                            |

| RxD4 <sup>Note</sup> | Input  | Serial data input to UART4                                                                                                                           | Input port    | P51/INTP2/SI40 <sup>Note</sup>                 |

| SCK00                | I/O    | Clock input/output for CSI00, CSI01, CSI10, CSI20, CSI40, and                                                                                        | Input port    | P10                                            |

| SCK01                |        | CSI41                                                                                                                                                |               | P43                                            |

| SCK10                |        |                                                                                                                                                      |               | P04/SCL10                                      |

| SCK20                |        |                                                                                                                                                      |               | P142/SCL20                                     |

| SCK40                |        |                                                                                                                                                      |               | P50/INTP1                                      |

| SCK41                |        |                                                                                                                                                      |               | P53/TI00                                       |

| SCL0                 | I/O    | Clock input/output for I <sup>2</sup> C                                                                                                              | Input port    | P60                                            |

| SCL10                | I/O    | Clock input/output for simplified I <sup>2</sup> C                                                                                                   | Input port    | P04/SCK10                                      |

| SCL20                |        |                                                                                                                                                      |               | P142/SCK20                                     |

Note SCK40, SCK41, SI40, SI41, SO40, SO41, TxD4, RxD4 are only mounted in the  $\mu$  PD78F1027 and 78F1028.

# 4.2.4 Special function registers (SFRs)

Unlike a general-purpose register, each SFR has a special function. SFRs are allocated to the FFF00H to FFFFFH area.

SFRs can be manipulated like general-purpose registers, using operation, transfer, and bit manipulation instructions. The manipulable bit units, 1, 8, and 16, depend on the SFR type.

Each manipulation bit unit can be specified as follows.

• 1-bit manipulation

Describe the symbol reserved by the assembler for the 1-bit manipulation instruction operand (sfr.bit). This manipulation can also be specified with an address.

• 8-bit manipulation

Describe the symbol reserved by the assembler for the 8-bit manipulation instruction operand (sfr). This manipulation can also be specified with an address.

• 16-bit manipulation

Describe the symbol reserved by the assembler for the 16-bit manipulation instruction operand (sfrp). When specifying an address, describe an even address.

Table 4-5 gives a list of the SFRs. The meanings of items in the table are as follows.

Symbol

Symbol indicating the address of a special function register. It is a reserved word in the RA78K0R, and is defined as an sfr variable using the #pragma sfr directive in the CC78K0R. When using the RA78K0R, ID78K0R-QB, and SM+ for 78K0R, symbols can be written as an instruction operand.

• R/W

Indicates whether the corresponding SFR can be read or written.

R/W: Read/write enable

R: Read only

W: Write only

Manipulable bit units

" $\sqrt{}$ " indicates the manipulable bit unit (1, 8, or 16). "-" indicates a bit unit for which manipulation is not possible.

After reset

Indicates each register status upon reset signal generation.

## Caution Do not access addresses to which extended SFRs are not assigned.

Remark For extended SFRs (2nd SFRs), see 4.2.5 Extended special function registers (2nd SFRs: 2nd Special Function Registers).

## (6) 20 MHz internal high-speed oscillation control register (DSCCTL)

This register controls the 20 MHz internal high-speed oscillation clock (DSC) function.

This register can be used to control oscillation of the 20 MHz internal high-speed oscillation clock (fiH20) and select the 20 MHz internal high-speed oscillation clock (fiH20) as the CPU/peripheral hardware clock.

The DSCCTL register can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

## Figure 7-9. Format of 20 MHz Internal High-Speed Oscillation Control Register (DSCCTL)

Address: F00F6H After reset: 00H R/WNote

| Symbol | 7 | 6 | 5 | 4 | <3>  | <2>    | 1 | <0>   |

|--------|---|---|---|---|------|--------|---|-------|

| DSCCTL | 0 | 0 | 0 | 0 | DSCS | SELDSC | 0 | DSCON |

| DSCS | 20 MHz internal high-speed oscillation supply status flag                                                         |

|------|-------------------------------------------------------------------------------------------------------------------|

| 0    | Not supplied                                                                                                      |

| 1    | Supplied (The CPU/peripheral hardware clock (fcLK) operates on the 20 MHz internal high-speed oscillation clock.) |

| SELDSC | Selection of 20 MHz internal high-speed oscillation for CPU/peripheral hardware clock (fcuk)                                                 |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | Does not select 20 MHz internal high-speed oscillation (clock selected by the system clock control register (CKC) is supplied to $f_{CLK}$ ) |

| 1      | Selects 20 MHz internal high-speed oscillation (20 MHz internal high-speed oscillation is supplied to $f_{\mbox{\tiny CLK}})$                |

| DSCON | Operating or stopping 20 MHz internal high-speed oscillation clock (fiH20) |

|-------|----------------------------------------------------------------------------|

| 0     | Stopped                                                                    |

| 1     | Operated                                                                   |

**Note** Bit 3 is read-only.

- Cautions 1. 20 MHz internal oscillation can only be used if  $VDD \ge 2.7 V$ .

- 2. Set the SELDSC bit when 100  $\mu$  s have elapsed after the DSCON bit has been set with VDD  $\geq$  2.7 V.

- 3. The internal high-speed oscillator must be operated (HIOSTOP = 0) when DSCON = 1.

- 4. If 1 MHz internal oscillation is selected by using the option byte, 20 MHz internal high-speed oscillation cannot be used. Do not set (1) the DSCON bit.

# 11.4 Operations of Clock Output/Buzzer Output Controller

One pin can be used to output a clock or buzzer sound.

The PCLBUZ0 pin outputs a clock/buzzer selected by the clock output select register 0 (CKS0).

The PCLBUZ1 pin outputs a clock/buzzer selected by the clock output select register 1 (CKS1).

## 11.4.1 Operation as output pin

The PCLBUZn pin is output as the following procedure.

- <1> Select the output frequency with bits 0 to 3 (CCSn0 to CCSn2, CSELn) of the clock output select register (CKSn) of the PCLBUZn pin (output in disabled status).

- <2> Set bit 7 (PCLOEn) of the CKSn register to 1 to enable clock/buzzer output.

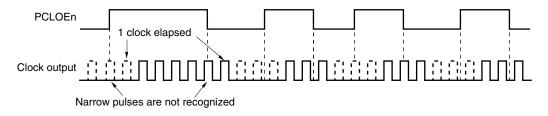

- Remarks 1. The controller used for outputting the clock starts or stops outputting the clock one clock after enabling or disabling clock output (PCLOEn bit) is switched. At this time, pulses with a narrow width are not output. Figure 11-4 shows enabling or stopping output using the PCLOEn bit and the timing of outputting the clock.

- **2.** n = 0: 78K0R/KC3-L (48-pin), 78K0R/KD3-L

- n = 0, 1: 78K0R/KE3-L, 78K0R/KF3-L, 78K0R/KG3-L

## Figure 11-4. Remote Control Output Application Example

## (11) Serial output enable register m (SOEm)

The SOEm register is a register that is used to enable or stop output of the serial communication operation of each channel.

Channel n that enables serial output cannot rewrite by software the value of the SOmn bit of serial output register m (SOm) to be described below, and a value reflected by a communication operation is output from the serial data output pin.

For channel n, whose serial output is stopped, the SOmn bit value of the SOm register can be set by software, and that value can be output from the serial data output pin. In this way, any waveform of the start condition and stop condition can be created by software.

The SOEm register can be set by a 16-bit memory manipulation instruction.

The lower 8 bits of the SOEm register can be set with an 1-bit or 8-bit memory manipulation instruction with SOEmL.

Reset signal generation clears the SOEm register to 0000H.

#### Figure 14-15. Format of Serial Output Enable Register m (SOEm)

| Address: F012AH, F012BH After reset: 0000H R/W                                                                                                      |                                                                                                                                                                                                                                                                                                            |        |         |          |          |          |          |          |          |          |          |   |   |           |           |           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------|----------|----------|----------|----------|----------|----------|----------|----------|---|---|-----------|-----------|-----------|

| Symbol                                                                                                                                              | 15                                                                                                                                                                                                                                                                                                         | 14     | 13      | 12       | 11       | 10       | 9        | 8        | 7        | 6        | 5        | 4 | 3 | 2         | 1         | 0         |

| SOE0                                                                                                                                                | 0                                                                                                                                                                                                                                                                                                          | 0      | 0       | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0 | 0 | SOE<br>02 | SOE<br>01 | SOE<br>00 |

|                                                                                                                                                     |                                                                                                                                                                                                                                                                                                            |        |         |          |          |          |          |          |          |          |          |   |   |           |           |           |

| Address: F01                                                                                                                                        | 6AH, F(                                                                                                                                                                                                                                                                                                    | 016BH  | After   | reset: C | 000H     | R/W      |          |          |          |          |          |   |   |           |           |           |

| Symbol                                                                                                                                              | 15                                                                                                                                                                                                                                                                                                         | 14     | 13      | 12       | 11       | 10       | 9        | 8        | 7        | 6        | 5        | 4 | 3 | 2         | 1         | 0         |

| SOE1                                                                                                                                                | 0                                                                                                                                                                                                                                                                                                          | 0      | 0       | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0 | 0 | SOE<br>12 | 0         | SOE<br>10 |

| Address: F021AH, F021BH After reset: 0000H R/W                                                                                                      |                                                                                                                                                                                                                                                                                                            |        |         |          |          |          |          |          |          |          |          |   |   |           |           |           |

| Symbol                                                                                                                                              | 15                                                                                                                                                                                                                                                                                                         | 14     | 13      | 12       | 11       | 10       | 9        | 8        | 7        | 6        | 5        | 4 | 3 | 2         | 1         | 0         |

| SOE2 Note                                                                                                                                           | 0                                                                                                                                                                                                                                                                                                          | 0      | 0       | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0 | 0 | 0         | SOE<br>21 | SOE<br>20 |

|                                                                                                                                                     |                                                                                                                                                                                                                                                                                                            |        |         |          |          |          |          |          |          |          |          |   |   |           |           |           |

|                                                                                                                                                     | SOE<br>mn                                                                                                                                                                                                                                                                                                  |        |         |          |          | 9        | Serial o | utput er | nable/st | op of ch | nannel r | ı |   |           |           |           |

|                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                          | Stops  | output  | by seria | l comm   | unicatio | on opera | ation.   |          |          |          |   |   |           |           |           |

|                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                                          | Enable | es outp | ut by se | rial con | nmunica  | ation op | eration. |          |          |          |   |   |           |           |           |

| Note                                                                                                                                                | <ol> <li>Enables output by serial communication operation.</li> <li>Note SOE2 register is only mounted in the 78K0R/KF3-L (μ PD78F1027, 78F1028) and 78K0R/KG3-L (μ PD78F1029, 78F1030).</li> </ol>                                                                                                        |        |         |          |          |          |          |          |          |          |          |   |   |           |           |           |

| Caution Be sure to clear bits 15 to 3 of the SOE0 register, bits 1 and 15 to 3 of the SOE1 register, and bits 15 to 2 of the SOE2 registers to "0". |                                                                                                                                                                                                                                                                                                            |        |         |          |          |          |          |          |          |          |          |   |   |           |           |           |

| Rem                                                                                                                                                 | Remark       m: Unit number (m = 0 to 2), n: Channel number (n = 0 to 2)         78K0R/KC3-L, 78K0R/KD3-L, 78K0R/KE3-L:       mn = 00 to 02         78K0R/KF3-L       μ PD78F1010, 78F1011, 78F1012       mn = 00 to 02, 10, 12         78K0R/KF3-L       μ PD78F1007, 78F1012       mn = 00 to 02, 10, 12 |        |         |          |          |          |          |          |          |          |          |   |   |           |           |           |

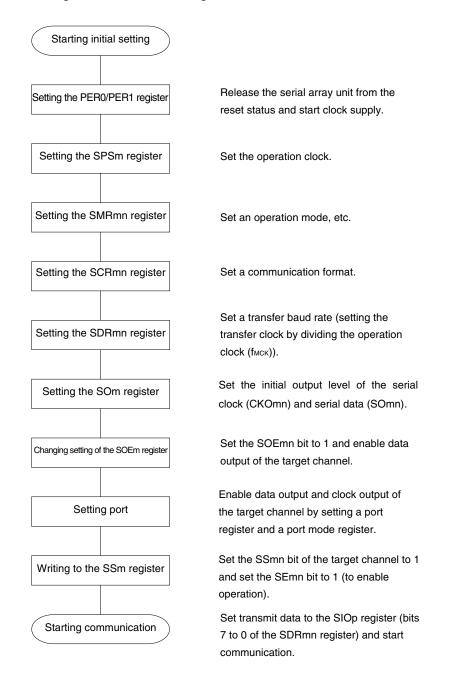

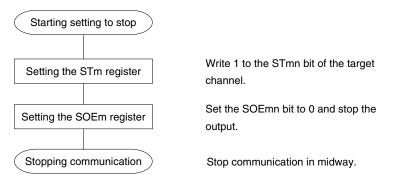

## (2) Operation procedure

Figure 14-29. Initial Setting Procedure for Master Transmission

Caution After setting the SAUmEN bit of peripheral enable register 0/1 (PER0/PER1) to 1, be sure to set serial clock select register m (SPSm) after 4 or more fcLK clocks have elapsed.

**Remark** Even after communication is stopped, the pin level is retained. To resume the operation, re-set serial output register m (SOm) (see Figure 14-78 Procedure for Resuming UART Transmission).

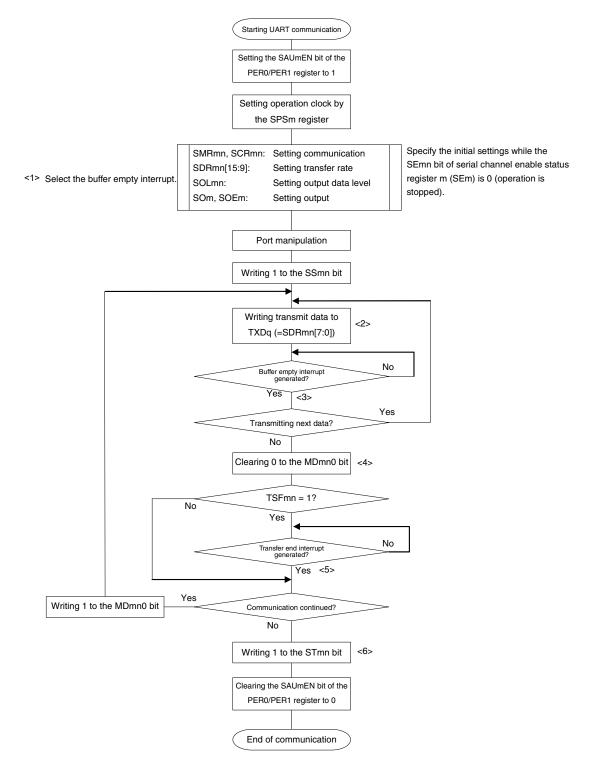

#### Figure 14-82. Flowchart of UART Transmission (in Continuous Transmission Mode)

- Caution After setting the SAUmEN bit of peripheral enable register 0/1 (PER0/PER1) to 1, be sure to set serial clock select register m (SPSm) after 4 or more fclk clocks have elapsed.

- **Remark** <1> to <6> in the figure correspond to <1> to <6> in **Figure 14-81 Timing Chart of UART Transmission (in Continuous Transmission Mode)**.

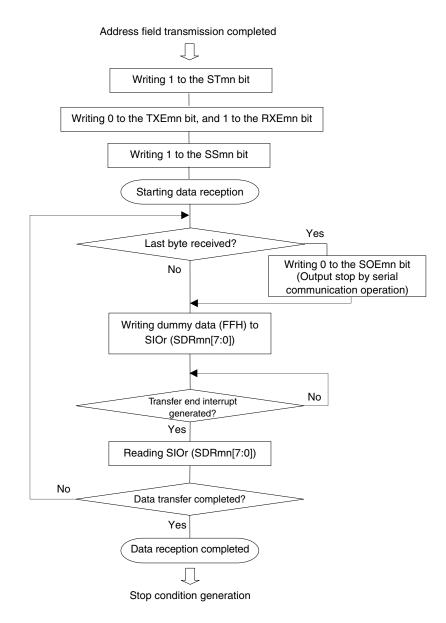

## Figure 14-107. Flowchart of Data Reception

Caution ACK is not output when the last data is received (NACK). Communication is then completed by setting "1" to the STmn bit of serial channel stop register m (STm) to stop operation and generating a stop condition.

# Table 14-17. Relationship between register settings and pins (Channel 0 of unit 2: CSI40, UART4 transmission)

| SE           | MD  | MD  | SOE | SO            | СКО           | TXE | RXE | PM          | P50         | PM           | P51<br>Note 2 | РМ          | P52         | Operation mode                             |                         | Pin Functio                                       | n                          |

|--------------|-----|-----|-----|---------------|---------------|-----|-----|-------------|-------------|--------------|---------------|-------------|-------------|--------------------------------------------|-------------------------|---------------------------------------------------|----------------------------|

| 20<br>Note 1 | 202 | 201 | 20  | 20            | 20            | 20  | 20  | 50          |             | 51<br>Note 2 | Hold I        | 52          |             |                                            | SCK40/<br>INTP1/<br>P50 | SI40/<br>RxD4/<br>INTP2/<br>P51 <sup>Note 2</sup> | SO40/<br>TxD4/<br>TO00/P52 |

| 0            | 0   | 0   | 0   | 1             | 1             | 0   | 0   | ×<br>Note 3 | ×<br>Note 3 | ×<br>Note 3  | ×<br>Note 3   | ×<br>Note 3 | ×<br>Note 3 | Operation stop<br>mode                     | INTP1/<br>P50           | INTP2/<br>P51                                     | TO00/P52                   |

|              | 0   | 1   |     |               |               |     |     |             |             |              |               |             |             |                                            |                         | INTP2/<br>P51/RxD4                                |                            |

| 1            | 0   | 0   | 0   | 1             | 1             | 0   | 1   | 1           | ×           | 1            | ×             | ×<br>Note 3 | ×<br>Note 3 | Slave CSI40 reception                      | SCK40<br>(input)        | SI40                                              | TO00/P52                   |

|              |     |     | 1   | 0/1<br>Note 4 | 1             | 1   | 0   | 1           | ×           | ×<br>Note 3  | ×<br>Note 3   | 0           | 1           | Slave CSI40<br>transmission                | SCK40<br>(input)        | INTP2/P51                                         | SO40                       |

|              |     |     | 1   | 0/1<br>Note 4 | 1             | 1   | 1   | 1           | ×           | 1            | ×             | 0           | 1           | Slave CSI40<br>transmission/<br>reception  | SCK40<br>(input)        | SI40                                              | SO40                       |

|              |     |     | 0   | 1             | 0/1<br>Note 4 | 0   | 1   | 0           | 1           | 1            | ×             | ×<br>Note 3 | ×<br>Note 3 | Master CSI40<br>reception                  | SCK40<br>(output)       | SI40                                              | TO00/P52                   |

|              |     |     | 1   | 0/1<br>Note 4 | 0/1<br>Note 4 | 1   | 0   | 0           | 1           | ×<br>Note 3  | ×<br>Note 3   | 0           | 1           | Master CSI40<br>transmission               | SCK40<br>(output)       | INTP2/P51                                         | SO40                       |

|              |     |     | 1   | 0/1<br>Note 4 | 0/1<br>Note 4 | 1   | 1   | 0           | 1           | 1            | ×             | 0           | 1           | Master CSI40<br>transmission/<br>reception | SCK40<br>(output)       | SI40                                              | SO40                       |

|              | 0   | 1   | 1   | 0/1<br>Note 4 | 1             | 1   | 0   | ×<br>Note 3 | ×<br>Note 3 | ×<br>Note 3  | ×<br>Note 3   | 0           | 1           | UART4<br>transmission <sup>Note 5</sup>    | INTP1/<br>P50           | INTP2/<br>P51/RxD4                                | TxD4                       |

### (µPD78F1027, 78F1028, 78F1029, 78F1030 only)

- **Notes 1.** Serial channel enable register 2 (SE2) is a read-only status register which is set using serial channel start register 2 (SS2) and serial channel stop register 2 (ST2).

- When channel 1 of unit 2 is set to UART4 reception, this pin becomes an RxD4 function pin (refer to Table 14-18). In this case, operation stop mode or UART4 transmission must be selected for channel 0 of unit 2.

- 3. This pin can be set as a port function pin.

- This is 0 or 1, depending on the communication operation. For details, refer to 14.3 (12) Serial output register m (SOm).

- 5. When using UART4 transmission and reception in a pair, set channel 1 of unit 2 to UART4 reception (refer to **Table 14-18**).

Remark X: Don't care

## Figure 15-7. Format of IICA Status Register (IICS) (3/3)

| ACKD                                             | Detection of acknowledge (ACK)                                                                                                                               |                                                                                       |  |  |  |  |  |  |  |

|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 0                                                | Acknowledge was not detected.                                                                                                                                | Acknowledge was not detected.                                                         |  |  |  |  |  |  |  |

| 1                                                | Acknowledge was detected.                                                                                                                                    |                                                                                       |  |  |  |  |  |  |  |

| Condition f                                      | or clearing (ACKD = 0)                                                                                                                                       | Condition for setting (ACKD = 1)                                                      |  |  |  |  |  |  |  |

| <ul><li>At the risi</li><li>Cleared to</li></ul> | stop condition is detected<br>ing edge of the next byte's first clock<br>by LREL = 1 (exit from communications)<br>e IICE bit changes from 1 to 0 (operation | After the SDA0 line is set to low level at the rising edge of SCL0 line's ninth clock |  |  |  |  |  |  |  |

| <ul> <li>Reset</li> </ul>                        |                                                                                                                                                              |                                                                                       |  |  |  |  |  |  |  |

| STD                                                         | Detection of start condition                                                                                                                                                     |                                    |  |  |  |  |  |  |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--|--|--|--|--|--|

| 0                                                           | Start condition was not detected.                                                                                                                                                |                                    |  |  |  |  |  |  |

| 1                                                           | Start condition was detected. This indicates that the address transfer period is in effect.                                                                                      |                                    |  |  |  |  |  |  |

| Condition f                                                 | for clearing (STD = 0)                                                                                                                                                           | Condition for setting (STD = 1)    |  |  |  |  |  |  |

| <ul> <li>At the ris following</li> <li>Cleared I</li> </ul> | stop condition is detected<br>ing edge of the next byte's first clock<br>address transfer<br>by LREL = 1 (exit from communications)<br>e IICE bit changes from 1 to 0 (operation | When a start condition is detected |  |  |  |  |  |  |

| SPD                       | Detection of stop condition                                                                                                                          |                                   |  |  |  |  |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--|--|--|--|

| 0                         | Stop condition was not detected.                                                                                                                     |                                   |  |  |  |  |

| 1                         | Stop condition was detected. The master device's communication is terminated and the bus is released.                                                |                                   |  |  |  |  |

| Condition f               | or clearing (SPD = 0)                                                                                                                                | Condition for setting (SPD = 1)   |  |  |  |  |

| clock follo<br>start cono | ing edge of the address transfer byte's first<br>owing setting of this bit and detection of a<br>dition<br>e IICE bit changes from 1 to 0 (operation | When a stop condition is detected |  |  |  |  |

Remark LREL: Bit 6 of IICA control register 0 (IICCTL0)

IICE: Bit 7 of IICA control register 0 (IICCTL0)

## (4) IICA flag register (IICF)

This register sets the operation mode of  $I^2C$  and indicates the status of the  $I^2C$  bus.

The IICF register can be set by a 1-bit or 8-bit memory manipulation instruction. However, the STT clear flag (STCF) and  $I^2C$  bus status flag (IICBSY) bits are read-only.

The IICRSV bit can be used to enable/disable the communication reservation function.

The STCEN bit can be used to set the initial value of the IICBSY bit.

The IICRSV and STCEN bits can be written only when the operation of  $I^2C$  is disabled (bit 7 (IICE) of IICA control register 0 (IICCTL0) = 0). When operation is enabled, the IICF register can be read.

Reset signal generation clears this register to 00H.

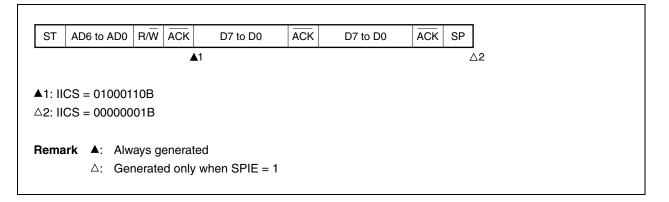

# (ii) When WTIM = 1

|            | ST A    | D6 to AD0 | R/W      | ACK       | D7 to D0      | ACK | D7 to D0 | ACK S | sР |

|------------|---------|-----------|----------|-----------|---------------|-----|----------|-------|----|

|            |         |           |          | ▲1 ▲2     |               |     | }        | ▲4    |    |

|            |         |           |          |           |               |     |          |       |    |

|            | 1: IICS | = 0110×   | 010B     |           |               |     |          |       |    |

| <b>A</b> ; | 2: IICS | = 0010×   | 110B     |           |               |     |          |       |    |

| ▲;         | 3: IICS | = 0010×   | 100B     |           |               |     |          |       |    |

| <b>A</b>   | 4: IICS | = 0010×   | ×00B     |           |               |     |          |       |    |

| $\Delta$   | 5: IICS | = 00000   | 001B     |           |               |     |          |       |    |

|            |         |           |          |           |               |     |          |       |    |

| R          | emark   | ▲: Al     | ways g   | enerate   | d             |     |          |       |    |

|            |         | ∆: G      | enerate  | ed only v | when SPIE = 1 | 1   |          |       |    |

|            |         | ×: Do     | on't car | e         |               |     |          |       |    |

|            |         |           |          |           |               |     |          |       |    |

# (6) Operation when arbitration loss occurs (no communication after arbitration loss)

When the device is used as a master in a multi-master system, read the MSTS bit each time interrupt request signal INTIICA has occurred to check the arbitration result.

## (a) When arbitration loss occurs during transmission of slave address data (when WTIM = 1)

## (3) In self programming mode

It is recommended to leave this pin open when using the self programming function. To pull it down externally, use a resistor of 100 k $\Omega$  to 200 k $\Omega$ .

In the self programming mode, the setting is switched to pull up in the self programming library.

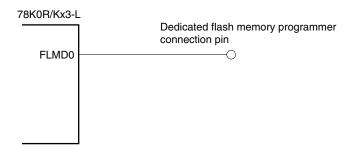

Figure 26-11. FLMD0 Pin Connection Example

#### 26.4.2 TOOL0 pin

In the flash memory programming mode, connect this pin directly to the dedicated flash memory programmer or pull it up by connecting it to EV<sub>DD</sub> via an external resistor.

When on-chip debugging is enabled in the normal operation mode, pull this pin up by connecting it to EV<sub>DD</sub> via an external resistor, and be sure to keep inputting the V<sub>DD</sub> level to the TOOL0 pin before reset is released (pulling down this pin is prohibited).

**Remark** The SAU and IICA pins are not used for communication between the 78K0R/Kx3-L and dedicated flash memory programmer, because single-line UART is used.

## 26.4.3 RESET pin

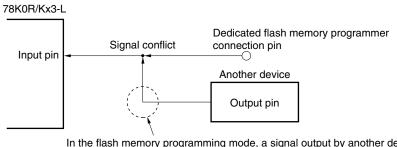

Signal conflict will occur if the reset signal of the dedicated flash memory programmer is connected to the RESET pin that is connected to the reset signal generator on the board. To prevent this conflict, isolate the connection with the reset signal generator.

The flash memory will not be correctly programmed if the reset signal is input from the user system while the flash memory programming mode is set . Do not input any signal other than the reset signal of the dedicated flash memory programmer.

In the flash memory programming mode, a signal output by another device will conflict with the signal output by the dedicated flash memory programmer. Therefore, isolate the signal of another device.

## 26.6.3 Selecting communication mode

Communication mode of the 78K0R/Kx3-L as follows.

| Table 26-5. | Communication Modes |

|-------------|---------------------|

|-------------|---------------------|

| Communication |      | Pins Used                |           |               |       |

|---------------|------|--------------------------|-----------|---------------|-------|

| Mode          | Port | Speed Note 2             | Frequency | Multiply Rate |       |

| 1-line mode   | UART | 115200 bps,              | -         | -             | TOOL0 |

| (dedicated    |      | 250000 bps,              |           |               |       |

| single-line   |      | 500000 bps,              |           |               |       |

| UART)         |      | 1 Mbps <sup>Note 3</sup> |           |               |       |

Notes 1. Selection items for Standard settings on GUI of the flash memory programmer.

- **2.** Because factors other than the baud rate error, such as the signal waveform slew, also affect UART communication, thoroughly evaluate the slew as well as the baud rate error.

- 3. When using a transfer rate of 1 Mbps, do not use the wide voltage mode.

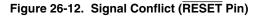

#### 26.6.4 Communication commands

The 78K0R/Kx3-L communicates with the dedicated flash memory programmer by using commands. The signals sent from the flash memory programmer to the 78K0R/Kx3-L are called commands, and the signals sent from the 78K0R/Kx3-L to the dedicated flash memory programmer are called response.

#### Figure 26-16. Communication Commands

The flash memory control commands of the 78K0R/Kx3-L are listed in the table below. All these commands are issued from the programmer and the 78K0R/Kx3-L perform processing corresponding to the respective commands.

| Classification      | Command Name      | Function                                                                                                 |

|---------------------|-------------------|----------------------------------------------------------------------------------------------------------|

| Verify              | Verify            | Compares the contents of a specified area of the flash memory with data transmitted from the programmer. |

| Erase               | Chip Erase        | Erases the entire flash memory.                                                                          |

|                     | Block Erase       | Erases a specified area in the flash memory.                                                             |

| Blank check         | Block Blank Check | Checks if a specified block in the flash memory has been correctly erased.                               |

| Write               | Programming       | Writes data to a specified area in the flash memory.                                                     |

| Getting information | Silicon Signature | Gets the 78K0R/Kx3-L information (such as the part number and flash memory configuration).               |

|                     | Version Get       | Gets the 78K0R/Kx3-L firmware version.                                                                   |

|                     | Checksum          | Gets the checksum data for a specified area.                                                             |

| Security            | Security Set      | Sets security information.                                                                               |

| Others              | Reset             | Used to detect synchronization status of communication.                                                  |

|                     | Baud Rate Set     | Sets baud rate when UART communication mode is selected.                                                 |

Table 26-6. Flash Memory Control Commands

The 78K0R/Kx3-L returns a response for the command issued by the dedicated flash memory programmer. The response names sent from the 78K0R/Kx3-L are listed below.

## Table 26-7. Response Names

| Response Name | Function                           |  |  |  |  |

|---------------|------------------------------------|--|--|--|--|

| ACK           | Acknowledges command/data.         |  |  |  |  |

| NAK           | Acknowledges illegal command/data. |  |  |  |  |

Caution The pins mounted depend on the product. Refer to Caution 2 at the beginning of this chapter.

| $(T_{A} = -40 \text{ to } +85^{\circ}\text{C}, 1.8 \text{ V} \le \text{V}_{DD} = \text{EV}_{DD0} = \text{EV}_{DD1} \le 5.5 \text{ V}, 1.8 \text{ V} \le \text{AV}_{REF} \le \text{V}_{DD}, \text{V}_{SS} = \text{EV}_{SS0} = \text{EV}_{SS1} = \text{AV}_{SS1} = \text{AV}_{SS2} = \text{AV}_{S$ | , |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| = 0 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |

| Items                 | Symbol | Conditions                                                                                                                                                                                             |                                                                               | MIN. | TYP.   | MAX.                 | Unit |

|-----------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------|--------|----------------------|------|

| Input voltage,<br>low | VIL1   | P01, P02, P12, P13, P15, P41, P45, P<br>P80 to P87, P90, P91, P111, P123, P1                                                                                                                           | 0                                                                             |      | 0.3Vdd | V                    |      |

|                       | VIL2   | P00, P03 to P06, P10, P11, P14, P16,<br>P17, P30, P31, P40, P42 to P44, P46,<br>P47, P50, P51, P53 to P55,<br>P64 to P67, P70 to P77, P110, P120<br>to P122, P131, P140 to P143, P145,<br>EXCLK, RESET | Normal input buffer                                                           | 0    |        | 0.2V <sub>DD</sub>   | V    |

|                       | VIL3   | P03, P04, P10, P11, P142, P143                                                                                                                                                                         | TTL input buffer $4.0 \text{ V} \leq \text{V}_{\text{DD}} \leq 5.5 \text{ V}$ | 0    |        | 0.8                  | V    |

|                       |        |                                                                                                                                                                                                        | TTL input buffer $2.7 \text{ V} \leq \text{V}_{\text{DD}} < 4.0 \text{ V}$    | 0    |        | 0.5                  | V    |

|                       |        |                                                                                                                                                                                                        | TTL input buffer $1.8 \text{ V} \leq \text{V}_{\text{DD}} < 2.7 \text{ V}$    | 0    |        | 0.2                  | V    |

|                       | VIL4   | P20 to P27, P150 to P157                                                                                                                                                                               | AVREF = VDD                                                                   | 0    |        | 0.3AV <sub>REF</sub> | V    |

|                       | VIL5   | P60 to P63                                                                                                                                                                                             |                                                                               | 0    |        | 0.3VDD               | V    |

|                       | VIL6   | FLMD0 <sup>Note</sup>                                                                                                                                                                                  |                                                                               | 0    |        | 0.1VDD               | V    |