Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | 78K/0R                                                                               |

| Core Size                  | 16-Bit                                                                               |

| Speed                      | 20MHz                                                                                |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                     |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                              |

| Number of I/O              | 66                                                                                   |

| Program Memory Size        | 128KB (128K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 8K x 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                          |

| Data Converters            | A/D 12x10b                                                                           |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 80-LQFP                                                                              |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f1012gk-gak-ax |

|                            |                                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.1.1 78K0R/KF3-L

### (1) Port functions (1/2): 78K0R/KF3-L

| Function Name         | I/O | Function                                                                                                                                                                   | After Reset           | Alternate Function                       |

|-----------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------------------------|

| P02                   | I/O | Port 0.                                                                                                                                                                    | Input port            | SO10/TxD1                                |

| P03                   |     | 5-bit I/O port.                                                                                                                                                            |                       | SI10/RxD1/SDA10                          |

| P04                   |     | Input of P03 and P04 can be set to TTL input buffer.<br>Output of P02 to P04 can be set to N-ch open-drain output                                                          |                       | SCK10/SCL10                              |

| P05                   |     | (V <sub>DD</sub> tolerance).                                                                                                                                               |                       | TI05/TO05                                |

| P06                   |     | Input/output can be specified in 1-bit units.<br>Use of an on-chip pull-up resistor can be specified by a<br>software setting.                                             |                       | TI06/TO06                                |

| P10                   | I/O | Port 1.                                                                                                                                                                    | Input port            | SCK00                                    |

| P11                   |     | 8-bit I/O port.                                                                                                                                                            |                       | SI00/RxD0                                |

| P12                   |     | Input of P10 and P11 can be set to TTL input buffer.                                                                                                                       |                       | SO00/TxD0                                |

| P13                   |     | Output of P10 and P12 can be set to N-ch open-drain output $(V_{DD} \text{ tolerance}).$                                                                                   |                       | TxD3                                     |

| P14                   |     | Input/output can be specified in 1-bit units.                                                                                                                              |                       | RxD3                                     |

| P15                   |     | Use of an on-chip pull-up resistor can be specified by a                                                                                                                   |                       | RTCDIV/RTCCL                             |

| P16                   |     | software setting.                                                                                                                                                          |                       | TI01/TO01/INTP5                          |

| P17                   |     |                                                                                                                                                                            |                       | TI02/TO02                                |

| P20 to P27            | I/O | Port 2.<br>8-bit I/O port.<br>Input/output can be specified in 1-bit units.                                                                                                | Digital input<br>port | ANI0 to ANI7                             |

| P30                   | I/O | Port 3.                                                                                                                                                                    | Input port            | RTC1HZ/INTP3                             |

| P31                   |     | <ul><li>2-bit I/O port.</li><li>Input/output can be specified in 1-bit units.</li><li>Use of an on-chip pull-up resistor can be specified by a software setting.</li></ul> |                       | TI03/TO03/INTP4                          |

| P40 <sup>Note 1</sup> | I/O | Port 4.                                                                                                                                                                    | Input port            | TOOL0                                    |

| P41                   |     | 8-bit I/O port.                                                                                                                                                            |                       | TOOL1                                    |

| P42                   |     | Input/output can be specified in 1-bit units.<br>Use of an on-chip pull-up resistor can be specified by a                                                                  |                       | TI04/TO04                                |

| P43                   |     | software setting.                                                                                                                                                          |                       | SCK01                                    |

| P44                   |     |                                                                                                                                                                            |                       | SI01                                     |

| P45                   |     |                                                                                                                                                                            |                       | SO01                                     |

| P46, P47              |     |                                                                                                                                                                            |                       | _                                        |

| P50                   | I/O | Port 5.                                                                                                                                                                    | Input port            | INTP1/SCK40 <sup>Note 2</sup>            |

| P51                   |     | 6-bit I/O port.                                                                                                                                                            |                       | INTP2/SI40/RxD4 <sup>Note 2</sup>        |

| P52                   |     | Input/output can be specified in 1-bit units.<br>Use of an on-chip pull-up resistor can be specified by a                                                                  |                       | TO00/SO40/TxD4 <sup>Note 2</sup>         |

| P53                   |     | software setting.                                                                                                                                                          |                       | TI00/SCK41 Note 2                        |

| P54                   |     |                                                                                                                                                                            |                       | TI07/TO07/SI41 <sup>Note 2</sup>         |

| P55                   |     |                                                                                                                                                                            |                       | PCLBUZ1/INTP7/<br>SO41 <sup>Note 2</sup> |

Notes 1. If on-chip debugging is enabled by using an option byte, be sure to pull up the P40/TOOL0 pin externally (see Caution in 3.2.5 P40 to P47 (port 4)).

2. SCK40, SCK41, SI40, SI41, SO40, SO41, TxD4, RxD4 are only mounted in the  $\mu$  PD78F1027 and 78F1028.

| Address | Special Function Register (SFR) Name                   | Symbol  | R/W | Manipulable Bit Range |              |        | After Reset             | Ā              | Ā              | Z              | Z            | 조            | 주            | Ā            |

|---------|--------------------------------------------------------|---------|-----|-----------------------|--------------|--------|-------------------------|----------------|----------------|----------------|--------------|--------------|--------------|--------------|

|         |                                                        |         |     | 1-bit                 | 8-bit        | 16-bit |                         | KC3-L (40-pin) | KC3-L (44-pin) | KC3-L (48-pin) | KD3-L        | KE3-L        | KF3-L        | KG3-L        |

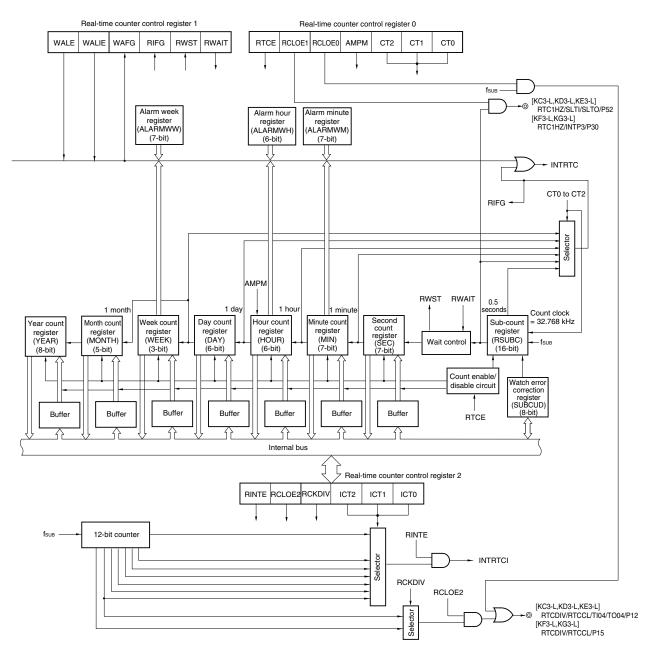

| FFF98H  | Year count register                                    | YEAR    | R/W | -                     | $\checkmark$ | _      | 00H                     | -              | $\checkmark$   | $\checkmark$   | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| FFF99H  | Watch error correction register                        | SUBCUD  | R/W | -                     | $\checkmark$ | -      | 00H                     | -              | $\checkmark$   | $\checkmark$   | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| FFF9AH  | Alarm minute register                                  | ALARMWM | R/W | -                     | $\checkmark$ | -      | 00H                     | -              |                | $\checkmark$   | $\checkmark$ | $\checkmark$ |              | $\checkmark$ |

| FFF9BH  | Alarm hour register                                    | ALARMWH | R/W | -                     | $\checkmark$ | -      | 12H                     | -              |                | $\checkmark$   | $\checkmark$ | $\checkmark$ |              | $\checkmark$ |

| FFF9CH  | Alarm week register                                    | ALARMWW | R/W | -                     | $\checkmark$ | -      | 00H                     | -              |                | $\checkmark$   | $\checkmark$ | $\checkmark$ |              | $\checkmark$ |

| FFF9DH  | Real-time counter control<br>register 0                | RTCC0   | R/W | $\checkmark$          | $\checkmark$ | -      | 00H                     | -              | $\checkmark$   | $\checkmark$   | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| FFF9EH  | Real-time counter control<br>register 1                | RTCC1   | R/W | $\checkmark$          | $\checkmark$ | -      | 00H                     | -              | $\checkmark$   | $\checkmark$   | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| FFF9FH  | Real-time counter control register 2                   | RTCC2   | R/W | $\checkmark$          | $\checkmark$ | _      | 00H                     | -              | V              | $\checkmark$   | $\checkmark$ | $\checkmark$ | V            | $\checkmark$ |

| FFFA0H  | Clock operation mode control register                  | CMC     | R/W | -                     | $\checkmark$ | -      | 00H                     | V              | $\checkmark$   | $\checkmark$   | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| FFFA1H  | Clock operation status control register                | CSC     | R/W | $\checkmark$          | $\checkmark$ | -      | СОН                     | $\checkmark$   | V              | $\checkmark$   | $\checkmark$ | $\checkmark$ | V            | $\checkmark$ |

| FFFA2H  | Oscillation stabilization time counter status register | OSTC    | R   | $\checkmark$          | $\checkmark$ | -      | 00H                     | V              | V              | $\checkmark$   | $\checkmark$ | $\checkmark$ | V            | $\checkmark$ |

| FFFA3H  | Oscillation stabilization time select register         | OSTS    | R/W | -                     | V            | -      | 07H                     | V              | $\checkmark$   | $\checkmark$   | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| FFFA4H  | System clock control register                          | CKC     | R/W | $\checkmark$          | $\checkmark$ | -      | 09H                     |                | $\checkmark$   | $\checkmark$   | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| FFFA5H  | Clock output select register 0                         | CKS0    | R/W | $\checkmark$          | $\checkmark$ | -      | 00H                     | _              | _              | $\checkmark$   | $\checkmark$ | $\checkmark$ |              | $\checkmark$ |

| FFFA6H  | Clock output select register 1                         | CKS1    | R/W | $\checkmark$          | $\checkmark$ | _      | 00H                     | -              | -              | -              | -            | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| FFFA8H  | Reset control flag register                            | RESF    | R   | -                     | $\checkmark$ | _      | Undefined Note 1        |                | $\checkmark$   | $\checkmark$   | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| FFFA9H  | Low-voltage detection register                         | LVIM    | R/W | $\checkmark$          | $\checkmark$ | -      | 00H <sup>Note 2</sup>   |                |                | $\checkmark$   | $\checkmark$ | $\checkmark$ |              | $\checkmark$ |

| FFFAAH  | Low-voltage detection level select register            | LVIS    | R/W | $\checkmark$          | $\checkmark$ | _      | 0EH <sup>Note 3</sup>   | $\checkmark$   | $\checkmark$   | $\checkmark$   | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| FFFABH  | Watchdog timer enable register                         | WDTE    | R/W | _                     | $\checkmark$ | _      | 1A/9A <sup>Note 4</sup> |                | $\checkmark$   | $\checkmark$   | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

# Table 4-5. SFR List (4/6)

**Notes 1.** The reset value of the RESF register varies depending on the reset source.

2. The reset value of the LVIM register varies depending on the reset source and the setting of the option byte.

3. The reset value of the LVIS register varies depending on the reset source.

4. The reset value of the WDTE register is determined by the setting of the option byte.

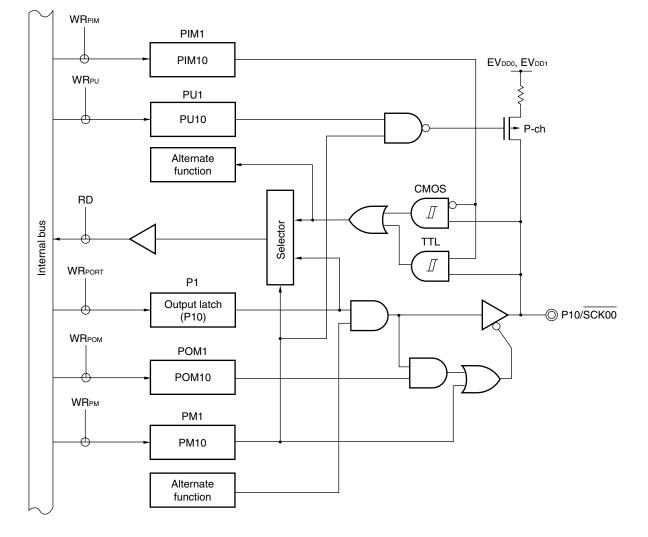

Figure 6-6. Block Diagram of P10

- P1: Port register 1

- PU1: Pull-up resistor option register 1

- PM1: Port mode register 1

- PIM1: Port input mode register 1

- POM1: Port output mode register 1

- RD: Read signal

- WR×x: Write signal

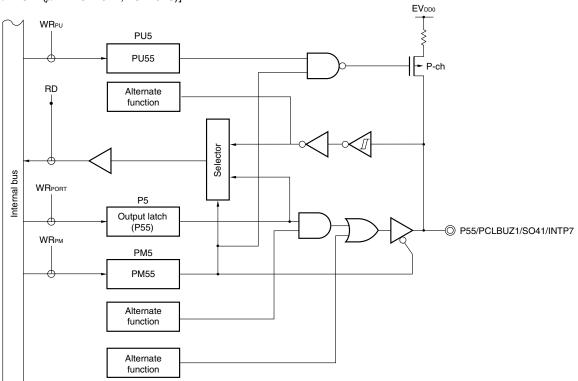

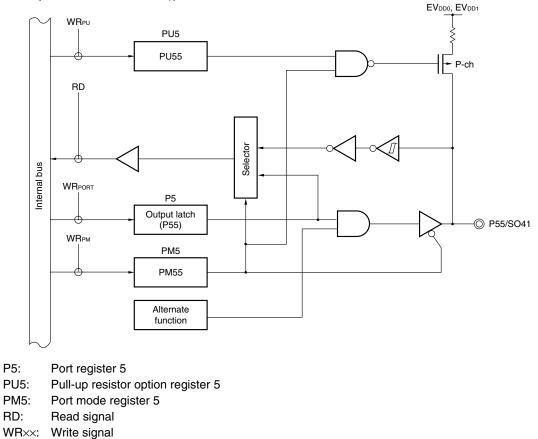

## Figure 6-31. Block Diagram of P55

[78K0R/KF3-L (µ PD78F1027, 78F1028)]

[78K0R/KG3-L (µ PD78F1029, 78F1030)]

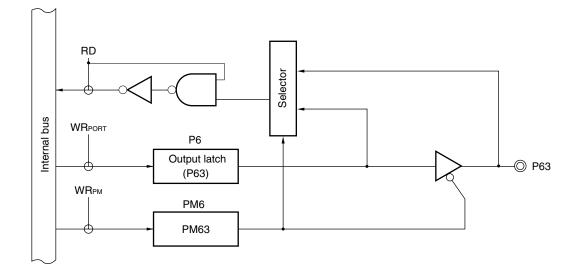

Figure 6-35. Block Diagram of P63

- P6: Port register 6

- PM6: Port mode register 6

RD: Read signal

WR××: Write signal

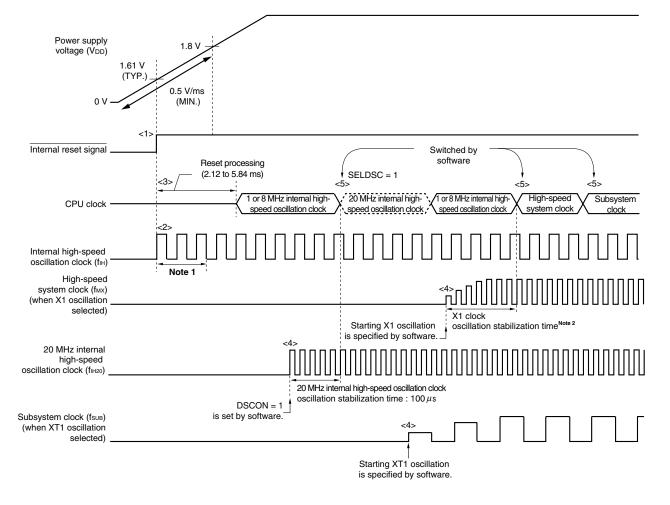

# Figure 7-16. Clock Generator Operation When Power Supply Voltage Is Turned On (When LVI Default Start Function Stopped Is Set (Option Byte: LVIOFF = 1))

- <1> When the power is turned on, an internal reset signal is generated by the power-on-clear (POC) circuit.

- <2> When the power supply voltage exceeds 1.61 V (TYP.), the reset is released and the internal high-speed oscillator <sup>Note 3</sup> automatically starts oscillation.

- <3> The CPU starts operation on the internal high-speed oscillation clock <sup>Note 3</sup> after a reset processing such as waiting for the voltage of the power supply or regulator to stabilize has been performed after reset release.

- <4> Set the start of oscillation of the X1 or XT1 clock <sup>Note 4</sup> via software (see **7.6.4 Example of setting X1 oscillation clock** and **7.6.5 Example of setting XT1 oscillation clock**). Switch to oscillation using the 20 MHz internal high-speed oscillation clock after confirming that the power supply voltage is at least 2.7 V and setting the DSCON bit to 1 by using software.

- <5> When switching the CPU clock to the X1 or XT1 clock, wait for the clock oscillation to stabilize, and then set switching via software (see 7.6.4 Example of setting X1 oscillation clock and 7.6.5 Example of setting XT1 oscillation clock).

Switch to the 20 MHz internal high-speed oscillation clock by setting the DSCON bit (bit 0 of the 20 MHz internal high-speed oscillation control register (DSCCTL)), waiting for 100  $\mu$ s, and then setting the SELDSC bit to 1 by using software <sup>Note 5</sup>.

(Notes and Cautions are listed on the next page.)

### (13) Watch error correction register (SUBCUD)

This register is used to correct the watch with high accuracy when it is slow or fast by changing the value that overflows from the sub-count register (RSUBC) to the second count register (SEC) (reference value: 7FFFH). The SUBCUD register can be set by an 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

### Figure 9-14. Format of Watch Error Correction Register (SUBCUD)

| Address: FFF | 99H After re | eset: 00H F | R/W |    |    |    |    |    |

|--------------|--------------|-------------|-----|----|----|----|----|----|

| Symbol       | 7            | 6           | 5   | 4  | 3  | 2  | 1  | 0  |

| SUBCUD       | DEV          | F6          | F5  | F4 | F3 | F2 | F1 | F0 |

| DEV            | Setting of watch error correction timing                                             |  |  |  |  |  |  |

|----------------|--------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 0              | Corrects watch error when the second digits are at 00, 20, or 40 (every 20 seconds). |  |  |  |  |  |  |

| 1              | 1 Corrects watch error only when the second digits are at 00 (every 60 seconds).     |  |  |  |  |  |  |

| Writing to the | SUBCUD register at the following timing is prohibited.                               |  |  |  |  |  |  |

| • When DEV     | = 0 is set: For a period of SEC = 00H, 20H, 40H                                      |  |  |  |  |  |  |

| • When DEV     | = 1 is set: For a period of SEC = 00H                                                |  |  |  |  |  |  |

| F6            | Setting of watch error correction value                                                                                                                                                 |  |  |  |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 0             | ncreases by {(F5, F4, F3, F2, F1, F0) - 1} × 2.                                                                                                                                         |  |  |  |  |  |  |

| 1             | Decreases by {(/F5, /F4, /F3, /F2, /F1, /F0) + 1} × 2.                                                                                                                                  |  |  |  |  |  |  |

|               | 5, F4, F3, F2, F1, F0) = ( $^{*}$ , 0, 0, 0, 0, 0, $^{*}$ ), the watch error is not corrected. $^{*}$ is 0 or 1.<br>the inverted values of the corresponding bits (000011 when 111100). |  |  |  |  |  |  |

| Range of corr | rection value: (when F6 = 0) 2, 4, 6, 8,, 120, 122, 124                                                                                                                                 |  |  |  |  |  |  |

|               | (when F6 = 1) -2, -4, -6, -8,, -120, -122, -124                                                                                                                                         |  |  |  |  |  |  |

The range of value that can be corrected by using the watch error correction register (SUBCUD) is shown below.

|                    | DEV = 0 (correction every 20 seconds) | DEV = 1 (correction every 60 seconds) |

|--------------------|---------------------------------------|---------------------------------------|

| Correctable range  | -189.2 ppm to 189.2 ppm               | -63.1 ppm to 63.1 ppm                 |

| Maximum excludes   | ± 1.53 ppm                            | ± 0.51 ppm                            |

| quantization error |                                       |                                       |

| Minimum resolution | ± 3.05 ppm                            | ± 1.02 ppm                            |

**Remark** If a correctable range is -63.1 ppm or lower and 63.1 ppm or higher, set 0 to DEV.

## CHAPTER 14 SERIAL ARRAY UNIT

Each serial array unit has four serial channels, each of which can be used for 3-wire serial (CSI), UART, and simplified I2C communication.

Function assignment of each channel supported by the 78K0R/Kx3-L is as shown below.

• 78K0R/KC3-L, 78K0R/KD3-L, 78K0R/KE3-L

|   | Unit | Channel | Used as CSI | Used as UART               | Used as Simplified I <sup>2</sup> C |

|---|------|---------|-------------|----------------------------|-------------------------------------|

| ( | )    | 0       | CSI00       | UART0 (supporting LIN-bus) | -                                   |

|   |      | 1       | CSI01       |                            | -                                   |

|   |      | 2       | CSI10       | UART1                      | IIC10                               |

|   |      | 3       | _           |                            | _                                   |

• 78K0R/KF3-L, 78K0R/KG3-L

| Unit   | Channel | Used as CSI | Used as UART               | Used as Simplified I <sup>2</sup> C |

|--------|---------|-------------|----------------------------|-------------------------------------|

| 0      | 0       | CSI00       | UART0                      | -                                   |

|        | 1       | CSI01       |                            | _                                   |

|        | 2       | CSI10       | UART1                      | IIC10                               |

|        | 3       | -           |                            | -                                   |

| 1      | 0       | CSI20       | UART2                      | IIC20                               |

|        | 1       | -           |                            | -                                   |

|        | 2       | -           | UART3 (supporting LIN-bus) | -                                   |

|        | 3       | -           |                            | -                                   |

| 2 Note | 0       | CSI40       | UART4                      | _                                   |

|        | 1       | CSI41       |                            | _                                   |

**Note** Serial array unit 2 is only mounted in the  $\mu$  PD78F1027, 78F1028, 78F1029, and 78F1030.

When "UART0" is used for channels 0 and 1 of the unit 0, CSI00 and CSI01 cannot be used, but CSI10, UART1, or IIC10 can be used.

| mbo  |                                               | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 14        | 13       | 12       | 11      | 203H (S<br>10     | 9      | 8               | 7       | 6        | 5                      | 4         | 3     | 2 | 1 | 0 |

|------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------|----------|---------|-------------------|--------|-----------------|---------|----------|------------------------|-----------|-------|---|---|---|

| SRmr |                                               | 0 0 0 0 0 0 0 0 0 TSF BFF 0 0 FEF PEF                                                                                                                                                                                                                                                                                                                                                                                                                               |           |          |          |         |                   |        |                 |         |          | PEF<br>mn              | OVF<br>mn |       |   |   |   |

|      | FEF Framing error detection flag of channel n |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |          |          |         |                   |        |                 |         |          |                        |           |       |   |   |   |

|      | 0                                             | No e                                                                                                                                                                                                                                                                                                                                                                                                                                                                | rror oc   | curs.    |          |         |                   |        |                 |         |          |                        |           |       |   |   |   |

|      | 1                                             | An e                                                                                                                                                                                                                                                                                                                                                                                                                                                                | rror oc   | curs (du | uring U/ | ART rec | eption)           |        |                 |         |          |                        |           |       |   |   |   |

|      | PEF                                           | stop I                                                                                                                                                                                                                                                                                                                                                                                                                                                              | bit is no | ot detec | ted whe  | en UAR  | T recep<br>Parity |        | ds.<br>etectior | flag of | channe   | el n                   |           |       |   |   |   |

| mn   |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |          |          |         |                   |        |                 |         |          |                        |           |       |   |   |   |

| ŀ    | 0 No error occurs.                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |          |          |         |                   | or ACK | is not o        | detecte | d (durin | g l <sup>2</sup> C tra | nsmiss    | ion). |   |   |   |

|      | 1                                             | 1 An error occurs (during UART reception) or ACK is not detected (during I <sup>2</sup> C transmission). <clear condition="">   • 1 is written to the PECTmn bit of the SIRmn register.   <set condition="">   • The parity of the transmit data and the parity bit do not match when UART reception ends (parity error).   • No ACK signal is returned from the slave channel at the ACK reception timing during I<sup>2</sup>C transmission (ACK is</set></clear> |           |          |          |         |                   |        |                 |         |          |                        |           |       |   |   |   |

Figure 14-11. Format of Serial Status Register mn (SSRmn) (2/2)

| OVF | Overrun error detection flag of channel n                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| mn  |                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

| 0   | No error occurs.                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| 1   | An error occurs                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

| <0  | <clear condition=""></clear>                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| • 1 | • 1 is written to the OVCTmn bit of the SIRmn register.                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| <8  | Set condition>                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| 1   | • Even though receive data is stored in the SDRmn register, that data is not read and transmit data or the next receive data is written while the RXEmn bit of the SCRmn register is set to 1 (reception or transmission and reception mode in each communication mode). |  |  |  |  |  |  |  |

| • 1 | Fransmit data is not ready for slave transmission or transmission and reception in CSI mode.                                                                                                                                                                             |  |  |  |  |  |  |  |

**Remark** m: Unit number (m = 0 to 2), n: Channel number (n = 0 to 3)

| 78K0R/KC3-L, 78K0R/KD3-L, 78K0R/KE3-L:          | mn = 00 to 03                   |

|-------------------------------------------------|---------------------------------|

| 78K0R/KF3-L $\mu$ PD78F1010, 78F1011, 78F1012 : | mn = 00 to 03, 10 to 13         |

| 78K0R/KF3-L $\mu$ PD78F1027, 78F1028 :          | mn = 00 to 03, 10 to 13, 20, 21 |

| 78K0R/KG3-L μPD78F1013, 78F1014 :               | mn = 00 to 03, 10 to 13         |

| 78K0R/KG3-L $\mu$ PD78F1029, 78F1030 :          | mn = 00 to 03, 10 to 13, 20, 21 |

### 14.5.1 Master transmission

Master transmission is that the 78K0R/Kx3-L outputs a transfer clock and transmits data to another device.

| 3-Wire Serial I/O                                                                                                   | CSI00                                                                                                                                                                                                                                                                                                                                                                                                                              | CSI01                | CSI10                | CSI20 <sup>Note 1</sup> | CSI40 <sup>Note 2</sup> | CSI41 Note 2         |

|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|-------------------------|-------------------------|----------------------|

| Target channel                                                                                                      | Channel 0 of<br>SAU0                                                                                                                                                                                                                                                                                                                                                                                                               | Channel 1 of<br>SAU0 | Channel 2 of<br>SAU0 | Channel 0 of<br>SAU1    | Channel 0 of<br>SAU2    | Channel 1 of<br>SAU2 |

| Pins used                                                                                                           | SCK00, SO00                                                                                                                                                                                                                                                                                                                                                                                                                        | SCK01, SO01          | SCK10, SO10          | SCK20, SO20             | SCK40, SO40             | SCK41, SO41          |

| Interrupt                                                                                                           | INTCSI00                                                                                                                                                                                                                                                                                                                                                                                                                           | INTCSI01             | INTCSI10             | INTCSI20                | INTCSI40                | INTCSI41             |

| Transfer end interrupt (in single-transfer mode) or buffer empty interrupt (in continuous transfer can be selected. |                                                                                                                                                                                                                                                                                                                                                                                                                                    |                      |                      | ransfer mode)           |                         |                      |

| Error detection flag                                                                                                | r detection flag None                                                                                                                                                                                                                                                                                                                                                                                                              |                      |                      |                         |                         |                      |

| Transfer data length                                                                                                | 7 or 8 bits                                                                                                                                                                                                                                                                                                                                                                                                                        |                      |                      |                         |                         |                      |

| Transfer rate                                                                                                       | Max. fcLk/4 [Hz], Min. fcLk/(2 × 2 <sup>11</sup> × 128) [Hz] Note 3 fcLk: System clock frequency   Selectable by the DAPmn bit of the SCRmn register DAPmn = 0: Data output starts from the start of the operation of the serial clock.   DAPmn = 1: Data output starts half a clock before the start of the serial clock operation.   Selectable by the CKPmn bit of the SCRmn register   CKPmn = 0: Forward   CKPmn = 1: Reverse |                      |                      |                         |                         |                      |

| Data phase                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                    |                      |                      |                         |                         | on.                  |

| Clock phase                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                    |                      |                      |                         |                         |                      |

| Data direction MSB or LSB first                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                    |                      |                      |                         |                         |                      |

#### Notes 1. 78K0R/KF3-L, 78K0R/KG3-L only.

- **2.** CSI40 and CSI41 are only mounted in the 78K0R/KF3-L (μ PD78F1027, 78F1028) and 78K0R/KG3-L (μ PD78F1029, 78F1030).

- 3. Use this operation within a range that satisfies the conditions above and the AC characteristics in the electrical specifications (see CHAPTER 30 ELECTRICAL SPECIFICATIONS (78K0R/KC3-L, 78K0R/KD3-L, 78K0R/KE3-L), CHAPTER 31 ELECTRICAL SPECIFICATIONS (78K0R/KF3-L, 78K0R/KG3-L)).

| Remark | m: Unit number (m = 0 to 2), n: Channel number (n = 0 | to 2)                     |

|--------|-------------------------------------------------------|---------------------------|

|        | 78K0R/KC3-L, 78K0R/KD3-L, 78K0R/KE3-L:                | mn = 00 to 02             |

|        | 78K0R/KF3-L (μ PD78F1010, 78F1011, 78F1012):          | mn = 00 to 02, 10         |

|        | 78K0R/KF3-L (µ PD78F1027, 78F1028):                   | mn = 00 to 02, 10, 20, 21 |

|        | 78K0R/KG3-L (μ PD78F1013, 78F1014):                   | mn = 00 to 02, 10         |

|        | 78K0R/KG3-L (μ PD78F1029, 78F1030):                   | mn = 00 to 02, 10, 20, 21 |

# 17.5.3 UART consecutive reception + ACK transmission

A flowchart illustrating an example of setting for UART consecutive reception + ACK transmission is shown below.

- Consecutively receives data from UART0 and outputs ACK to P10 on completion of reception.

- DMA channel 0 is used for DMA transfer.

- DMA start source: Software trigger (DMA transfer on occurrence of an interrupt is disabled.)

- Transfers FFF12H of UART receive data register 0 (RXD0) to 64 bytes of FFE00H to FFE3FH of RAM.

# 29.1 Conventions Used in Operation List

#### 29.1.1 Operand identifiers and specification methods

Operands are described in the "Operand" column of each instruction in accordance with the description method of the instruction operand identifier (refer to the assembler specifications for details). When there are two or more description methods, select one of them. Alphabetic letters in capitals and the symbols, #, !, !!, \$, \$!, [], and ES: are keywords and are described as they are. Each symbol has the following meaning.

- #: Immediate data specification

- !: 16-bit absolute address specification

- !!: 20-bit absolute address specification

- \$: 8-bit relative address specification

- \$!: 16-bit relative address specification

- []: Indirect address specification

- ES:: Extension address specification

In the case of immediate data, describe an appropriate numeric value or a label. When using a label, be sure to describe the #, !, !!, \$, \$!, [], and ES: symbols.

For operand register identifiers, r and rp, either function names (X, A, C, etc.) or absolute names (names in parentheses in the table below, R0, R1, R2, etc.) can be used for description.

| Identifier | Description Method                                                                                                   |

|------------|----------------------------------------------------------------------------------------------------------------------|

| r          | X (R0), A (R1), C (R2), B (R3), E (R4), D (R5), L (R6), H (R7)                                                       |

| rp         | AX (RP0), BC (RP1), DE (RP2), HL (RP3)                                                                               |

| sfr        | Special-function register symbol (SFR symbol) FFF00H to FFFFFH                                                       |

| sfrp       | Special-function register symbols (16-bit manipulatable SFR symbol. Even addresses only <sup>Note</sup> ) FFF00H to  |

|            | FFFFH                                                                                                                |

| saddr      | FFE20H to FFF1FH Immediate data or labels                                                                            |

| saddrp     | FFE20H to FF1FH Immediate data or labels (even addresses only <sup>Note</sup> )                                      |

| addr20     | 00000H to FFFFFH Immediate data or labels                                                                            |

| addr16     | 0000H to FFFFH Immediate data or labels (only even addresses for 16-bit data transfer instructions <sup>Note</sup> ) |

| addr5      | 0080H to 00BFH Immediate data or labels (even addresses only)                                                        |

| word       | 16-bit immediate data or label                                                                                       |

| byte       | 8-bit immediate data or label                                                                                        |

| bit        | 3-bit immediate data or label                                                                                        |

| RBn        | RB0 to RB3                                                                                                           |

### Table 29-1. Operand Identifiers and Specification Methods

**Note** Bit 0 = 0 when an odd address is specified.

**Remark** The special function registers can be described to operand sfr as symbols. See **Table 4-5 SFR List** for the symbols of the special function registers. The extended special function registers can be described to operand !addr16 as symbols. See **Table 4-6 Extended SFR (2nd SFR) List** for the symbols of the extended special function registers.

| Instruction | Mnemonic | Operands             | Bytes                                | Clo    | cks    | Operation                              |   | Flag  |

|-------------|----------|----------------------|--------------------------------------|--------|--------|----------------------------------------|---|-------|

| Group       |          |                      |                                      | Note 1 | Note 2 |                                        | z | AC CY |

| 8-bit data  | MOV      | A, ES:[HL]           | 2                                    | 2      | 5      | $A \leftarrow (ES, HL)$                |   |       |

| transfer    |          | ES:[HL], A           | 2                                    | 2      | -      | $(ES, HL) \leftarrow A$                |   |       |

|             |          | ES:[HL + byte],#byte | 4                                    | 2      | -      | $((ES, HL) + byte) \leftarrow byte$    |   |       |

|             |          | A, ES:[HL + byte]    | 3                                    | 2      | 5      | $A \leftarrow ((ES, HL) + byte)$       |   |       |

|             |          | ES:[HL + byte], A    | 3                                    | 2      | _      | $((ES,HL) + byte) \leftarrow A$        |   |       |

|             |          | A, ES:[HL + B]       | 3                                    | 2      | 5      | $A \gets ((ES, HL) + B)$               |   |       |

|             |          | ES:[HL + B], A       | 3                                    | 2      | _      | $((ES,HL)+B)\leftarrowA$               |   |       |

|             |          | A, ES:[HL + C]       | 3                                    | 2      | 5      | $A \gets ((ES, HL) + C)$               |   |       |

|             |          | ES:[HL + C], A       | 3                                    | 2      | -      | $((ES, HL) + C) \leftarrow A$          |   |       |

|             |          | ES:word[B], #byte    | 5                                    | 2      | -      | $((ES, B) + word) \leftarrow byte$     |   |       |

|             |          | A, ES:word[B]        | 4                                    | 2      | 5      | $A \gets ((ES, B) + word)$             |   |       |

|             |          | ES:word[B], A        | 4                                    | 2      | -      | $((ES, B) + word) \leftarrow A$        |   |       |

|             |          | ES:word[C], #byte    | 5                                    | 2      | -      | $((ES, C) + word) \leftarrow byte$     |   |       |

|             |          | A, ES:word[C]        | 4                                    | 2      | 5      | $A \gets ((ES, C) + word)$             |   |       |

|             |          | ES:word[C], A        | 4                                    | 2      | -      | $((ES, C) + word) \leftarrow A$        |   |       |

|             |          | ES:word[BC], #byte   | 5                                    | 2      | -      | $((ES, BC) + word) \leftarrow byte$    |   |       |

|             |          | A, ES:word[BC]       | 4                                    | 2      | 5      | $A \gets ((ES, BC) + word)$            |   |       |

|             |          | ES:word[BC], A       | 4                                    | 2      | -      | $((ES,BC)+word)\leftarrowA$            |   |       |

|             |          | B, ES:!addr16        | 4                                    | 2      | 5      | $B \leftarrow (ES, addr16)$            |   |       |

|             |          | C, ES:!addr16        | 4                                    | 2      | 5      | $C \leftarrow (ES, addr16)$            |   |       |

|             |          | X, ES:!addr16        | 4                                    | 2      | 5      | $X \leftarrow (ES, addr16)$            |   |       |

|             | ХСН      | A, r Note 3          | 1 (r = X)<br>2 (other<br>than r = X) | 1      | _      | $A \leftarrow \rightarrow r$           |   |       |

|             |          | A, saddr             | 3                                    | 2      | -      | $A \longleftrightarrow (saddr)$        |   |       |

|             |          | A, sfr               | 3                                    | 2      | -      | $A \longleftrightarrow sfr$            |   |       |

|             |          | A, !addr16           | 4                                    | 2      | -      | $A \leftarrow \rightarrow$ (addr16)    |   |       |

|             |          | A, [DE]              | 2                                    | 2      | -      | $A \longleftrightarrow (DE)$           |   |       |

|             |          | A, [DE + byte]       | 3                                    | 2      | -      | $A \leftarrow \rightarrow (DE + byte)$ |   |       |

|             |          | A, [HL]              | 2                                    | 2      | -      | $A \longleftrightarrow (HL)$           |   |       |

|             |          | A, [HL + byte]       | 3                                    | 2      | -      | $A \leftarrow \rightarrow (HL + byte)$ |   |       |

|             |          | A, [HL + B]          | 2                                    | 2      | _      | $A \longleftrightarrow (HL + B)$       |   |       |

|             |          | A, [HL + C]          | 2                                    | 2      | -      | $A \longleftrightarrow (HL + C)$       |   |       |

| Table 29-5. Operation List (3/17) | Table 29-5. | <b>Operation L</b> | .ist (3/17) |

|-----------------------------------|-------------|--------------------|-------------|

|-----------------------------------|-------------|--------------------|-------------|

**Notes 1.** When the internal RAM area, SFR area, or extended SFR area is accessed, or for an instruction with no data access.

2. When the program memory area is accessed.

3. Except r = A

**Remarks 1.** One instruction clock cycle is one cycle of the CPU clock (fcPu) selected by the system clock control register (CKC).

2. This number of clocks is for when the program is in the internal ROM (flash memory) area. When fetching an instruction from the internal RAM area, the number of clocks is twice the number of clocks plus 3, maximum.

| Parameter               | Symbol                                                                                               | Conditions                                                                                      |                                                                                                                                               | MIN.                       | TYP. | MAX. | Unit |

|-------------------------|------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------|------|------|

| Output voltage,<br>high | Voh1                                                                                                 | P00, P01, P10 to P17, P30 to P33,<br>P40 to P43, P50 to P53, P70 to P77,                        | $\begin{array}{l} 4.0 \mbox{ V} \leq \mbox{V}_{\mbox{DD}} \leq 5.5 \mbox{ V}, \\ \mbox{I}_{\mbox{DH1}} = -3.0 \mbox{ mA} \end{array}$         | $V_{\text{DD}} - 0.7$      |      |      | V    |

|                         |                                                                                                      | P120, P140, P141                                                                                | $\label{eq:VDD} \begin{array}{l} 1.8 \mbox{ V} \leq \mbox{V}_{\mbox{DD}} \leq 5.5 \mbox{ V}, \\ I_{\mbox{OH1}} = -1.0 \mbox{ mA} \end{array}$ | $V_{\text{DD}} - 0.5$      |      |      | V    |

|                         | Vон2                                                                                                 | P20 to P27, P80 to P83, P150 to<br>P153                                                         | $AV_{REF} = V_{DD},$<br>Ioh2 = -0.1 mA                                                                                                        | AV <sub>REF</sub> –<br>0.5 |      |      | V    |

| Output voltage,<br>low  | Vol1                                                                                                 | P00, P01, P10 to P17, P30, P33, P40 to P43, P50 to P53, P70 to P77,                             | $\begin{array}{l} 4.0 \ V \leq V_{\text{DD}} \leq 5.5 \ V, \\ I_{\text{OL1}} = 8.5 \ mA \end{array} \end{array} \label{eq:VDD}$               |                            |      | 0.7  | ۷    |

|                         | P120, P140, P141     P31, P32     Vol2   P20 to P27, P80 to P83,<br>P150 to P153     Vol3   P60, P61 |                                                                                                 | $\begin{array}{l} 2.7 \ V \leq V_{\text{DD}} \leq 5.5 \ V, \\ I_{\text{OL1}} = 1.0 \ mA \end{array} \end{array} \label{eq:VDD}$               |                            |      | 0.5  | V    |

|                         |                                                                                                      |                                                                                                 | $1.8 \text{ V} \leq \text{V}_{\text{DD}} \leq 5.5 \text{ V},$ $I_{\text{OL1}} = 0.5 \text{ mA}$                                               |                            |      | 0.4  | ۷    |

|                         |                                                                                                      | P31, P32                                                                                        | $\begin{array}{l} 4.0 \ V \leq V_{\text{DD}} \leq 5.5 \ V, \\ I_{\text{OL1}} = 8.5 \ mA \end{array} \end{array} \label{eq:DD}$                |                            |      | 0.7  | V    |

|                         |                                                                                                      |                                                                                                 | $\begin{array}{l} 2.7 \ V \leq V_{\text{DD}} \leq 5.5 \ V, \\ I_{\text{OL1}} = 1.5 \ mA \end{array} \end{array} \label{eq:DD}$                |                            |      | 0.5  | V    |

|                         |                                                                                                      | $1.8 \text{ V} \leq \text{V}_{\text{DD}} \leq 5.5 \text{ V},$ $I_{\text{OL1}} = 0.6 \text{ mA}$ |                                                                                                                                               |                            | 0.4  | V    |      |

|                         |                                                                                                      | AVREF = VDD,<br>IOL2 = 0.4 mA                                                                   |                                                                                                                                               |                            | 0.4  | V    |      |

|                         |                                                                                                      | P60, P61                                                                                        | $\begin{array}{l} 4.0 \ V \leq V_{\text{DD}} \leq 5.5 \ V, \\ I_{\text{OL1}} = 15.0 \ mA \end{array} \end{array} \label{eq:VDD}$              |                            |      | 2.0  | V    |

|                         |                                                                                                      |                                                                                                 | $\begin{array}{l} 4.0 \ V \leq V_{\text{DD}} \leq 5.5 \ V, \\ I_{\text{OL1}} = 5.0 \ mA \end{array} \end{array} \label{eq:VDD}$               |                            |      | 0.4  | V    |

|                         |                                                                                                      |                                                                                                 | $\label{eq:VDD} \begin{array}{l} 2.7 \mbox{ V} \leq V_{\mbox{DD}} \leq 5.5 \mbox{ V}, \\ I_{\mbox{DL1}} = 3.0 \mbox{ mA} \end{array}$         |                            |      | 0.4  | ۷    |

|                         |                                                                                                      |                                                                                                 | $1.8 \text{ V} \le \text{V}_{\text{DD}} \le 5.5 \text{ V},$<br>$I_{\text{OL1}} = 2.0 \text{ mA}$                                              |                            |      | 0.4  | V    |

| (T 40.1- 0500       |                              |                                   |                                |

|---------------------|------------------------------|-----------------------------------|--------------------------------|

| (1A = -40 to +85°C, | $1.8 V \leq VDD = EVDD \leq$ | $5.5 V, 1.8 V \leq AVREF \leq VD$ | D, $Vss = EVss = AVss = 0 V$ ) |

## Caution P30 to P32, P70, P72, P73, and P75 do not output high level in N-ch open-drain mode.

**Remark** Unless specified otherwise, the characteristics of alternate-function pins are the same as those of the port pins.

| Parameter                     | Symbol  | Conditions                                                  | MIN.         | MAX.                | Unit |

|-------------------------------|---------|-------------------------------------------------------------|--------------|---------------------|------|

| SCL10 clock frequency         | fsc∟    | $4.0 V \le V_{DD} \le 5.5 V$ ,                              |              | 400 Note            | kHz  |

|                               |         | $2.7 V \le V_b \le 4.0 V_s$                                 |              |                     |      |

|                               |         | $C_b = 100 \text{ pF}, R_b = 1.4 \text{ k}\Omega$           |              |                     |      |

|                               |         | $2.7 \text{ V} \le \text{V}_{\text{DD}} \le 4.0 \text{ V},$ |              | 400 <sup>Note</sup> | kHz  |

|                               |         | $2.3 V \le V_b \le 2.7 V$ ,                                 |              |                     |      |

|                               |         | $C_b = 100 \text{ pF}, \text{ R}_b = 2.7 \text{ k}\Omega$   |              |                     |      |

| Hold time when SCL10 = "L"    | t∟ow    | $4.0 V \le V_{DD} \le 5.5 V$ ,                              | 1275         |                     | ns   |

|                               |         | $2.7 V \le V_b \le 4.0 V$ ,                                 |              |                     |      |

|                               |         | $C_b = 100 \text{ pF}, \text{R}_b = 1.4 \text{ k}\Omega$    |              |                     |      |

|                               |         | $2.7 \text{ V} \le \text{V}_{\text{DD}} \le 4.0 \text{ V},$ | 1275         |                     | ns   |

|                               |         | $2.3 V \le V_b \le 2.7 V$ ,                                 |              |                     |      |

|                               |         | $C_b = 100 \text{ pF}, \text{R}_b = 2.7 \text{ k}\Omega$    |              |                     |      |

| Hold time when SCL10 = "H"    | tніgн   | $4.0 V \le V_{DD} \le 5.5 V$ ,                              | 655          |                     | ns   |

|                               |         | $2.7 V \le V_b \le 4.0 V$ ,                                 |              |                     |      |

|                               |         | $C_b = 100 \text{ pF}, \text{R}_b = 1.4 \text{ k}\Omega$    |              |                     |      |

|                               |         | $2.7~V \leq V_{\text{DD}} \leq 4.0~V,$                      | 655          |                     | ns   |

|                               |         | $2.3 V \le V_b \le 2.7 V$ ,                                 |              |                     |      |

|                               |         | $C_b = 100 \text{ pF}, \text{R}_b = 2.7 \text{ k}\Omega$    |              |                     |      |

| Data setup time (reception)   | tsu:dat | $4.0~V \leq V_{\text{DD}} \leq 5.5~V,$                      | 1/fмск + 190 |                     | ns   |

|                               |         | $2.7 V \le V_b \le 4.0 V$ ,                                 |              |                     |      |

|                               |         | $C_b$ = 100 pF, $R_b$ = 1.4 k $\Omega$                      |              |                     |      |

|                               |         | $2.7~V \leq V_{\text{DD}} \leq 4.0~V,$                      | 1/fмск + 190 |                     | ns   |

|                               |         | $2.3 V \le V_b \le 2.7 V$ ,                                 |              |                     |      |

|                               |         | $C_b$ = 100 pF, $R_b$ = 2.7 k $\Omega$                      |              |                     |      |

| Data hold time (transmission) | thd:dat | $4.0~V \leq V_{\text{DD}} \leq 5.5~V,$                      | 0            | 640                 | ns   |

|                               |         | $2.7 \ V \le V_b \le 4.0 \ V,$                              |              |                     |      |

|                               |         | $C_b$ = 100 pF, $R_b$ = 1.4 k $\Omega$                      |              |                     |      |

|                               |         | $2.7~V \leq V_{\text{DD}} \leq 4.0~V,$                      | 0            | 660                 | ns   |

|                               |         | $2.3~V \le V_{b} \le 2.7~V,$                                |              |                     |      |

|                               |         | $C_b = 100 \text{ pF}, \text{R}_b = 2.7 \text{ k}\Omega$    |              |                     |      |

# (8) Communication at different potential (2.5 V, 3 V) (simplified $I^2C$ mode) (T<sub>A</sub> = -40 to +85°C, 2.7 V $\leq$ V<sub>DD</sub> = EV<sub>DD</sub> $\leq$ 5.5 V, V<sub>SS</sub> = EV<sub>SS</sub> = AV<sub>SS</sub> = 0 V)

**Note** The value must also be fMCK/4 or more.

Caution Select the TTL input buffer and the N-ch open drain output (VDD tolerance) mode for the SDA10 pin and the N-ch open drain output (VDD tolerance) mode for the SCL10 pin by using port input mode register 3 (PIM3) and port output mode register 3 (POM3).

**Remarks 1.**  $R_b[\Omega]$ :Communication line (SDA10, SCL10) pull-up resistance,

- Cb[F]: Communication line (SDA10, SCL10) load capacitance, Vb[V]: Communication line voltage 2. fмск: Serial array unit operation clock frequency

- (Operation clock to be set by the CKS02 bit of serial mode register 02 (SMR02).)

- 3. V<sub>IH</sub> and V<sub>IL</sub> below are observation points for the AC characteristics of the serial array unit when communicating at different potentials in simplified I<sup>2</sup>C mode.

- $\begin{array}{l} 4.0 \; V \leq V_{\text{DD}} \leq 5.5 \; \text{V}, \; 2.7 \; \text{V} \leq V_{\text{b}} \leq 4.0 \; \text{V}; \; \text{ViH} = 2.2 \; \text{V}, \; \text{Vil} = 0.8 \; \text{V} \\ 2.7 \; \text{V} \leq V_{\text{DD}} \leq 4.0 \; \text{V}, \; 2.3 \; \text{V} \leq V_{\text{b}} \leq 2.7 \; \text{V}; \; \text{ViH} = 2.0 \; \text{V}, \; \text{Vil} = 0.5 \; \text{V} \end{array}$

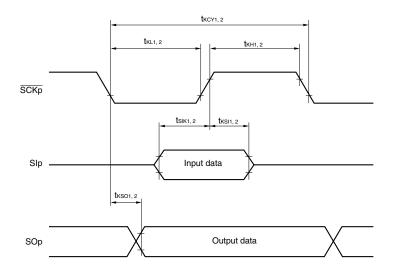

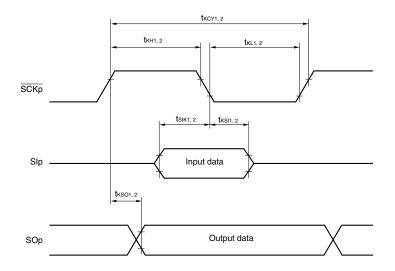

| Parameter                                               | Symbol        | Cor                                                | Conditions                                                |           | TYP. | MAX.       | Unit |

|---------------------------------------------------------|---------------|----------------------------------------------------|-----------------------------------------------------------|-----------|------|------------|------|

| SCKp cycle time                                         | tксү2         | $4.0 \text{ V} \leq \text{V}_{\text{DD}} \leq 5.5$ | 5 V                                                       | 6/fмск    |      |            | ns   |

|                                                         |               | $1.8 \text{ V} \leq \text{V}_{\text{DD}} < 4.0$    | 0 16 MHz < fмск                                           | 8/fмск    |      |            | ns   |

|                                                         |               | V                                                  | fмск ≤ 16 MHz                                             | 6/fмск    |      |            | ns   |

| SCKp high-/low-level width                              | tкн₂,<br>tк∟₂ |                                                    |                                                           | tксч₂/2   |      |            | ns   |

| SIp setup time<br>(to SCKp↑) <sup>Note 1</sup>          | tsik2         |                                                    |                                                           | 80        |      |            | ns   |

| SIp hold time<br>(from SCKp↑) <sup>Note 2</sup>         | tksi2         |                                                    |                                                           | 1/fмск+50 |      |            | ns   |

| Delay time from $\overline{\mathrm{SCKp}}\downarrow$ to | tkso2         | $C = 30 \text{ pF}^{Note 4}$                       | $4.0~V \le V_{\text{DD}} \le 5.5~V$                       |           |      | 2/fмск+45  | ns   |

| SOp output Note 3                                       |               |                                                    | $2.7 \text{ V} \leq \text{V}_{\text{DD}} < 4.0 \text{ V}$ |           |      | 2/fмск+57  | ns   |

|                                                         |               |                                                    | $1.8~V \leq V_{\text{DD}} < 2.7~V$                        |           |      | 2/fмск+125 | ns   |

# (3) During communication at same potential (CSI mode) (slave mode, $\overline{SCKp}$ ... external clock input) (T<sub>A</sub> = -40 to +85°C, 1.8 V ≤ V<sub>DD</sub> = EV<sub>DD0</sub> = EV<sub>DD1</sub> ≤ 5.5 V, V<sub>SS</sub> = EV<sub>SS0</sub> = EV<sub>SS1</sub> = AV<sub>SS</sub> = 0 V)

- **Notes 1.** When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The SIp setup time becomes "to  $\overline{SCKp}\downarrow$ " when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

- **2.** When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The SIp hold time becomes "from  $\overline{SCKp}\downarrow$ " when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

- **3.** When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The delay time to SOp output becomes "from SCKp↑" when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

- 4. C is the load capacitance of the SOp output lines.

- Caution Select the normal input buffer for the SIp pin and SCKp pin and the normal output mode for the SOp pin by using port input mode register g (PIMg) and port output mode register g (POMg).

**Remarks 1.** p: CSI number (p = 00, 01, 10, 20, 40, 41), g: PIM and POM number (g = 0, 1, 14)

fmck: Serial array unit operation clock frequency (Operation clock to be set by the CKSmn bit of the SMRmn register. m: Unit number (m = 0 to 2), n: Channel number (n = 0 to 2))

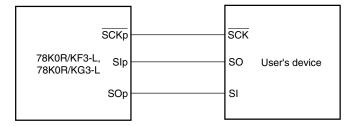

CSI mode connection diagram (during communication at same potential)

CSI mode serial transfer timing (during communication at same potential) (When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1.)

CSI mode serial transfer timing (during communication at same potential) (When DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.)

# CHAPTER 33 RECOMMENDED SOLDERING CONDITIONS

- Cautions 1. Recommended soldering conditions about WQFN package of the 78K0R/KC3-L and 78K0R/KE3-L are under development.

- 2. For soldering methods and conditions other than those recommended below, contact an Renesas Electronics sales representative.

These products should be soldered and mounted under the following recommended conditions.

For soldering methods and conditions other than those recommended below, contact an Renesas Electronics sales representative.

For technical information, see the following website.

Semiconductor Device Mount Manual (http://www.renesas.com/prod/package/index.html) (under production)

#### Table 33-1. Surface Mounting Type Soldering Conditions (1/2)

• 44-pin plastic LQFP (10 × 10)

$\mu$  PD78F1000GB-GAF-AX,  $\mu$  PD78F1001GB-GAF-AX,  $\mu$  PD78F1002GB-GAF-AX,  $\mu$  PD78F1003GB-GAF-AX

• 52-pin plastic LQFP (10  $\times$  10)

$\mu$  PD78F1004GB-GAG-AX,  $\mu$  PD78F1005GB-GAG-AX,  $\mu$  PD78F1006GB-GAG-AX

• 64-pin plastic LQFP (12 × 12)

$\mu$  PD78F1007GK-GAJ-AX,  $\mu$  PD78F1008GK-GAJ-AX,  $\mu$  PD78F1009GK-GAJ-AXX

•80-pin plastic LQFP (14 × 14)

μ PD78F1010GC-GAD-AX, μ PD78F1011GC-GAD-AX, μ PD78F1012GC-GAD-AX,

$\mu$  PD78F1027GC-GAD-AX,  $\mu$  PD78F1028GC-GAD-AX

#### •100-pin plastic LQFP (14 × 20)

$\mu$  PD78F1013GF-GAS-AX,  $\mu$  PD78F1014GF-GAS-AX,  $\mu$  PD78F1029GF-GAS-AX,  $\mu$  PD78F1030GF-GAS-AX

| Soldering Method | Soldering Method Soldering Conditions                                                                                                                                                                                                     |            |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Infrared reflow  | Package peak temperature: 260°C, Time: 60 seconds max. (at 220°C or higher),<br>Count: 3 times or less, Exposure limit: 7 days <sup>Note</sup> (after that, prebake at 125°C for<br>10 to 72 hours)                                       | IR60-107-3 |

| Wave soldering   | Solder bath temperature: 260°C max., Time: 10 seconds max., Count: Once,<br>Preheating temperature: 120°C max. (package surface temperature), Exposure<br>limit: 7 days <sup>Note</sup> (after that, prebake at 125°C for 10 to 72 hours) | WS60-107-1 |