Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product StatusActiveCore ProcessorARM® Cortex®-M4Core Size32-Bit Single-CoreSpeed100MHzConnectivityI²C, IrDA, LINbus, SPI, UART/USARTPeripheralsBrown-out Detect/Reset, DMA, I²S, POR, PWM, WDTNumber of I/O36Program Memory Size128KB (128K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size32K x 8Voltage - Supply (Vcc/Vdd)1.7V ~ 3.6VData ConvertersA/D 10x12b; D/A 1x12bOscillator TypeInternal |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Core Size32-Bit Single-CoreSpeed100MHzConnectivityI²C, IrDA, LINbus, SPI, UART/USARTPeripheralsBrown-out Detect/Reset, DMA, I²S, POR, PWM, WDTNumber of I/O36Program Memory Size128KB (128K × 8)Program Memory TypeFLASHEEPROM Size-RAM Size32K × 8Voltage - Supply (Vcc/Vdd)1.7V ~ 3.6VData ConvertersA/D 10x12b; D/A 1x12b                                                                         |

| Speed100MHzConnectivityI*C, IrDA, LINbus, SPI, UART/USARTPeripheralsBrown-out Detect/Reset, DMA, I*S, POR, PWM, WDTNumber of I/O36Program Memory Size128KB (128K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size32K x 8Voltage - Supply (Vcc/Vdd)1.7V ~ 3.6VData ConvertersA/D 10x12b; D/A 1x12b                                                                                                    |

| ConnectivityI²C, IrDA, LINbus, SPI, UART/USARTPeripheralsBrown-out Detect/Reset, DMA, I²S, POR, PWM, WDTNumber of I/O36Program Memory Size128KB (128K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size32K x 8Voltage - Supply (Vcc/Vdd)1.7V ~ 3.6VData ConvertersA/D 10x12b; D/A 1x12b                                                                                                               |

| PeripheralsBrown-out Detect/Reset, DMA, I²S, POR, PWM, WDTNumber of I/O36Program Memory Size128KB (128K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size32K x 8Voltage - Supply (Vcc/Vdd)1.7V ~ 3.6VData ConvertersA/D 10x12b; D/A 1x12b                                                                                                                                                             |

| Number of I/O36Program Memory Size128KB (128K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size32K x 8Voltage - Supply (Vcc/Vdd)1.7V ~ 3.6VData ConvertersA/D 10x12b; D/A 1x12b                                                                                                                                                                                                                       |

| Program Memory Size128KB (128K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size32K x 8Voltage - Supply (Vcc/Vdd)1.7V ~ 3.6VData ConvertersA/D 10x12b; D/A 1x12b                                                                                                                                                                                                                                      |

| Program Memory TypeFLASHEEPROM Size-RAM Size32K x 8Voltage - Supply (Vcc/Vdd)1.7V ~ 3.6VData ConvertersA/D 10x12b; D/A 1x12b                                                                                                                                                                                                                                                                         |

| EEPROM Size-RAM Size32K x 8Voltage - Supply (Vcc/Vdd)1.7V ~ 3.6VData ConvertersA/D 10x12b; D/A 1x12b                                                                                                                                                                                                                                                                                                 |

| RAM Size32K x 8Voltage - Supply (Vcc/Vdd)1.7V ~ 3.6VData ConvertersA/D 10x12b; D/A 1x12b                                                                                                                                                                                                                                                                                                             |

| Voltage - Supply (Vcc/Vdd)1.7V ~ 3.6VData ConvertersA/D 10x12b; D/A 1x12b                                                                                                                                                                                                                                                                                                                            |

| Data Converters     A/D 10x12b; D/A 1x12b                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                      |

| Oscillator Type Internal                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                      |

| Operating Temperature -40°C ~ 85°C (TA)                                                                                                                                                                                                                                                                                                                                                              |

| Mounting Type Surface Mount                                                                                                                                                                                                                                                                                                                                                                          |

| Package / Case     48-UFQFN Exposed Pad                                                                                                                                                                                                                                                                                                                                                              |

| Supplier Device Package48-UFQFPN (7x7)                                                                                                                                                                                                                                                                                                                                                               |

| Purchase URL https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f410cbu6                                                                                                                                                                                                                                                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| 1 | Introd | duction                                                                                         | 11   |

|---|--------|-------------------------------------------------------------------------------------------------|------|

| 2 | Desc   | ription                                                                                         | 12   |

|   | 2.1    | Compatibility with STM32F4 series                                                               | 14   |

| 3 | Funct  | tional overview                                                                                 | 16   |

|   | 3.1    | $ARM^{	extsf{R}}$ Cortex $^{	extsf{R}}$ -M4 with FPU core with embedded Flash and SRAM $\ldots$ | 16   |

|   | 3.2    | Adaptive real-time memory accelerator (ART Accelerator™)                                        | 16   |

|   | 3.3    | Batch Acquisition mode (BAM)                                                                    | 16   |

|   | 3.4    | Memory protection unit                                                                          | 17   |

|   | 3.5    | Embedded Flash memory                                                                           | 17   |

|   | 3.6    | CRC (cyclic redundancy check) calculation unit                                                  | 17   |

|   | 3.7    | Embedded SRAM                                                                                   | 17   |

|   | 3.8    | Multi-AHB bus matrix                                                                            | 18   |

|   | 3.9    | DMA controller (DMA)                                                                            | 18   |

|   | 3.10   | Nested vectored interrupt controller (NVIC)                                                     | 19   |

|   | 3.11   | External interrupt/event controller (EXTI)                                                      | 19   |

|   | 3.12   | Clocks and startup                                                                              | 19   |

|   | 3.13   | Boot modes                                                                                      | 20   |

|   | 3.14   | Power supply schemes                                                                            | 20   |

|   | 3.15   | Power supply supervisor                                                                         | 21   |

|   |        | 3.15.1 Internal reset ON                                                                        | . 21 |

|   |        | 3.15.2 Internal reset OFF                                                                       | . 21 |

|   | 3.16   | Voltage regulator                                                                               | 22   |

|   |        | 3.16.1 Internal power supply supervisor availability                                            | . 22 |

|   | 3.17   | Real-time clock (RTC) and backup registers                                                      | 23   |

|   | 3.18   | Low-power modes                                                                                 | 23   |

|   | 3.19   | V <sub>BAT</sub> operation                                                                      | 24   |

|   | 3.20   | Timers and watchdogs                                                                            | 24   |

|   |        | 3.20.1 Advanced-control timers (TIM1)                                                           | . 26 |

|   |        | 3.20.2 General-purpose timers (TIM5, TIM9 and TIM11)                                            |      |

|   |        | 3.20.3 Basic timer (TIM6)                                                                       | . 26 |

DocID028094 Rev 5

# 1 Introduction

This datasheet provides the description of the STM32F410x8/B microcontrollers.

For information on the Cortex<sup>®</sup>-M4 core, please refer to the  $Cortex^{®}$ -M4 programming manual (PM0214) available from *www.st.com*.

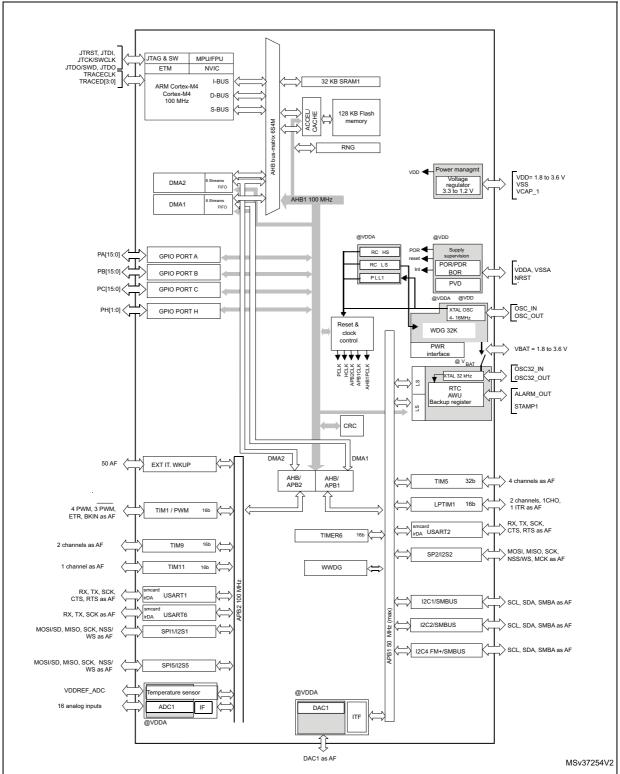

Figure 2. STM32F410x8/B block diagram

1. The timers connected to APB2 are clocked from TIMxCLK up to 100 MHz, while the timers connected to APB1 are clocked from TIMxCLK up to 100 MHz.

DocID028094 Rev 5

### 3.10 Nested vectored interrupt controller (NVIC)

The devices embed a nested vectored interrupt controller able to manage 16 priority levels, and handle up to 62 maskable interrupt channels plus the 16 interrupt lines of the  $Cortex^{\$}$ -M4 with FPU.

- Closely coupled NVIC gives low-latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Allows early processing of interrupts

- Processing of late arriving, higher-priority interrupts

- Support tail chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

This hardware block provides flexible interrupt management features with minimum interrupt latency.

### 3.11 External interrupt/event controller (EXTI)

The external interrupt/event controller consists of 21 edge-detector lines used to generate interrupt/event requests. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the Internal APB2 clock period. Up to 50 GPIOs can be connected to the 16 external interrupt lines.

### 3.12 Clocks and startup

On reset the 16 MHz internal RC oscillator is selected as the default CPU clock. The 16 MHz internal RC oscillator is factory-trimmed to offer 1% accuracy at 25 °C. The application can then select as system clock either the RC oscillator or an external 4-26 MHz clock source. This clock can be monitored for failure. If a failure is detected, the system automatically switches back to the internal RC oscillator and a software interrupt is generated (if enabled). This clock source is input to a PLL thus allowing to increase the frequency up to 100 MHz. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example if an indirectly used external oscillator fails).

Several prescalers allow the configuration of the AHB bus, the high-speed APB (APB2) and the low-speed APB (APB1) domains. The maximum frequency of the AHB bus and high-speed APB domains is 100 MHz. The maximum allowed frequency of the low-speed APB domain is 50 MHz.

#### 3.20.4 Low-power timer (LPTIM1)

The devices embed one low-power timer. This timer features an independent clock and runs in Stop mode if it is clocked by LSE, LSI or by an external clock. It is able to wake up the system from Stop mode.

The low-power timer main features are the following:

- 16-bit up counter with 16-bit autoreload register

- 16-bit compare register

- Configurable output: pulse, PWM

- Continuous/ one shot mode

- Selectable software/hardware input trigger

- Selectable clock source

- Internal clock sources: LSE, LSI, HSI or APB1 clock

- External clock source over LPTIM input (working even when no internal clock source is running and used by pulse-counter applications).

- Programmable digital glitch filter

- Encoder mode

- Active in Stop mode.

#### 3.20.5 Independent watchdog

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 32 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free-running timer for application timeout management. It is hardware- or software-configurable through the option bytes.

#### 3.20.6 Window watchdog

The window watchdog is based on a 7-bit downcounter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

#### 3.20.7 SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard downcounter. It features:

- A 24-bit downcounter

- Autoreload capability

- Maskable system interrupt generation when the counter reaches 0

- Programmable clock source.

### 3.21 Inter-integrated circuit interface (I<sup>2</sup>C)

The devices feature up to three  $I^2C$  bus interfaces which can operate in multimaster and slave modes:

- One I<sup>2</sup>C interface supports the Standard mode (up to 100 kHz), Fast-mode (up to 400 kHz) modes and Fast-mode plus (up to 1 MHz).

- Two I<sup>2</sup>C interfaces support the Standard mode (up to 100 KHz) and the Fast mode (up to 400 KHz). Their frequency can be increased up to 1 MHz. For more details on the complete solution, refer to the nearest STMicroelectronics sales office.

All I<sup>2</sup>C interfaces features 7/10-bit addressing mode and 7-bit addressing mode (as slave) and embed a hardware CRC generation/verification.

They can be served by DMA and they support SMBus 2.0/PMBus.

The devices also include programmable analog and digital noise filters (see *Table 6*).

|                                     | Analog filter | Digital filter                                         |

|-------------------------------------|---------------|--------------------------------------------------------|

| Pulse width of<br>suppressed spikes | ≥ 50 ns       | Programmable length from 1 to 15 I2C peripheral clocks |

Table 6. Comparison of I2C analog and digital filters

# 3.22 Universal synchronous/asynchronous receiver transmitters (USART)

The devices embed three universal synchronous/asynchronous receiver transmitters (USART1, USART2 and USART6).

These three interfaces provide asynchronous communication, IrDA SIR ENDEC support, multiprocessor communication mode, single-wire half-duplex communication mode and have LIN Master/Slave capability. The USART1 and USART6 interfaces are able to communicate at speeds of up to 12.5 Mbit/s. The USART2 interface communicates at up to 6.25 bit/s.

USART1 and USART2 also provide hardware management of the CTS and RTS signals, Smart Card mode (ISO 7816 compliant) and SPI-like communication capability. All interfaces can be served by the DMA controller.

| USART<br>name | Standard<br>features | Modem<br>(RTS/CTS) | LIN | SPI<br>master       | irDA | Smartcard<br>(ISO 7816) | Max. baud<br>rate in Mbit/s<br>(oversampling<br>by 16) | Max. baud<br>rate in Mbit/s<br>(oversampling<br>by 8) | APB<br>mapping            |

|---------------|----------------------|--------------------|-----|---------------------|------|-------------------------|--------------------------------------------------------|-------------------------------------------------------|---------------------------|

| USART1        | х                    | X <sup>(1)</sup>   | х   | х                   | х    | х                       | 6.25                                                   | 12.5                                                  | APB2<br>(max.<br>100 MHz) |

| USART2        | х                    | X <sup>(1)</sup>   | х   | X <sup>(1)</sup>    | х    | X <sup>(1)</sup>        | 3.12                                                   | 6.25                                                  | APB1<br>(max.<br>50 MHz)  |

| USART6        | х                    | N.A                | х   | X <sup>(1)(2)</sup> | х    | X <sup>(1)(2)</sup>     | 6.25                                                   | 12.5                                                  | APB2<br>(max.<br>50 MHz)  |

Table 7. USART feature comparison

1. Not available on WLCSP36 package.

2. Not available on UFQFPN48 package.

### 3.23 Serial peripheral interface (SPI)

The devices feature three SPIs in slave and master modes in full-duplex and simplex communication modes. SPI1 and SPI5 can communicate at up to 50 Mbit/s, SPI2 can communicate at up to 25 Mbit/s. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable to 8 bits or 16 bits. The hardware CRC generation/verification supports basic SD Card/MMC modes. All SPIs can be served by the DMA controller.

The SPI interface can be configured to operate in TI mode for communications in master mode and slave mode.

### 3.24 Inter-integrated sound (I<sup>2</sup>S)

Three standard  $I^2S$  interfaces (multiplexed with SPI1 to SPI5) are available. They can be operated in master or slave mode, in simplex communication modes and can be configured to operate with a 16-/32-bit resolution as an input or output channel. All the I2Sx audio sampling frequencies from 8 kHz up to 192 kHz are supported. When either or both of the I<sup>2</sup>S interfaces is/are configured in master mode, the master clock can be output to the external DAC/CODEC at 256 times the sampling frequency.

All I<sup>2</sup>Sx can be served by the DMA controller.

### 3.25 Random number generator (RNG)

All devices embed an RNG that delivers 32-bit random numbers generated by an integrated analog circuit.

|         | Р      | in Num   | ber    |         |                                                      | _        | e             |       |                                                                  |                      |

|---------|--------|----------|--------|---------|------------------------------------------------------|----------|---------------|-------|------------------------------------------------------------------|----------------------|

| WLCSP36 | LQFP48 | UFQFPN48 | LQFP64 | UFBGA64 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Notes | Alternate functions                                              | Additional functions |

| D1      | 29     | 29       | 41     | C8      | PA8                                                  | I/O      | FT            | -     | MCO_1, TIM1_CH1,<br>I2C4_SCL,<br>USART1_CK,<br>EVENTOUT          | -                    |

| -       | 30     | 30       | 42     | B8      | PA9                                                  | I/O      | FT            | -     | TIM1_CH2,<br>USART1_TX,<br>EVENTOUT                              | -                    |

| -       | 31     | 31       | 43     | E6      | PA10                                                 | I/O      | FT            | -     | TIM1_CH3,<br>SPI5_MOSI/I2S5_SD,<br>USART1_RX,<br>EVENTOUT        | -                    |

| -       | 32     | 32       | 44     | D7      | PA11                                                 | I/O      | FT            | -     | TIM1_CH4,<br>USART1_CTS,<br>USART6_TX,<br>EVENTOUT               | -                    |

| D2      | 33     | 33       | 45     | A8      | PA12                                                 | I/O      | FT            | -     | TIM1_ETR,<br>SPI5_MISO,<br>USART1_RTS,<br>USART6_RX,<br>EVENTOUT | -                    |

| C1      | 34     | 34       | 46     | C7      | PA13                                                 | I/O      | FT            | -     | JTMS-SWDIO,<br>EVENTOUT                                          | -                    |

| B1      | 35     | 35       | 47     | D5      | VSS                                                  | S        | -             | -     | -                                                                | -                    |

| -       | 36     | 36       | 48     | -       | VDD                                                  | S        | -             | -     | -                                                                | -                    |

| A1      | -      | -        | -      | -       | VDD                                                  | S        | -             | -     | -                                                                | -                    |

| B2      | 37     | 37       | 49     | B7      | PA14                                                 | I/O      | FT            | -     | JTCK-SWCLK,<br>EVENTOUT                                          | -                    |

| A2      | 38     | 38       | 50     | A7      | PA15                                                 | I/O      | FT            | -     | JTDI,<br>SPI1_NSS/I2S1_WS,<br>USART1_TX,<br>EVENTOUT             | -                    |

| -       | -      | -        | 51     | C6      | PC10                                                 | I/O      | FT            | -     | TRACED0,<br>TIM5_CH2,<br>EVENTOUT                                | -                    |

| -       | -      | -        | 52     | B6      | PC11                                                 | I/O      | FT            | -     | TRACED1,<br>TIM5_CH3,<br>EVENTOUT                                | -                    |

| -       | -      | -        | 53     | A6      | PC12                                                 | I/O      | FT            | -     | TRACED2,<br>TIM11_CH1,<br>EVENTOUT                               | -                    |

Table 9. STM32F410x8/B pin definitions (continued)

| Bus  | Boundary address          | Peripheral |

|------|---------------------------|------------|

|      | 0x4001 5400- 0x4001 FFFF  | Reserved   |

|      | 0x4001 5000 - 0x4001 53FF | SPI5/I2S5  |

|      | 0x4001 4C00- 0x4001 4FFF  | Reserved   |

|      | 0x4001 4800 - 0x4001 4BFF | TIM11      |

|      | 0x4001 4400 - 0x4001 47FF | Reserved   |

|      | 0x4001 4000 - 0x4001 43FF | ТІМ9       |

|      | 0x4001 3C00 - 0x4001 3FFF | EXTI       |

|      | 0x4001 3800 - 0x4001 3BFF | SYSCFG     |

| APB2 | 0x4001 3400 - 0x4001 37FF | Reserved   |

|      | 0x4001 3000 - 0x4001 33FF | SPI1/I2S1  |

|      | 0x4001 2400 - 0x4001 2FF  | Reserved   |

|      | 0x4001 2000 - 0x4001 23FF | ADC1       |

|      | 0x4001 1800 - 0x4001 1FFF | Reserved   |

|      | 0x4001 1400 - 0x4001 17FF | USART6     |

|      | 0x4001 1000 - 0x4001 13FF | USART1     |

|      | 0x4001 0400 - 0x4001 0FFF | Reserved   |

|      | 0x4001 0000 - 0x4001 03FF | TIM1       |

#### Table 11. STM32F410x8/B register boundary addresses<sup>(1)</sup>

### 6.1.5 Pin input voltage

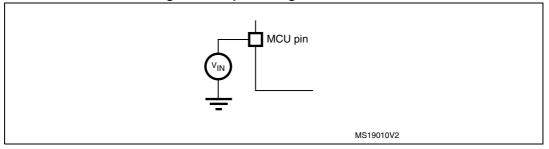

The input voltage measurement on a pin of the device is described in *Figure 12*.

#### Figure 12. Input voltage measurement

## 6.3 Operating conditions

### 6.3.1 General operating conditions

| Table 15. G | Seneral | operating | conditions |

|-------------|---------|-----------|------------|

|-------------|---------|-----------|------------|

| Symbol                             | Parameter                                                     | Conditions                                                             | Min                | Тур  | Max                 | Unit |  |

|------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------------|--------------------|------|---------------------|------|--|

|                                    |                                                               | Power Scale3: Regulator ON,<br>VOS[1:0] bits in PWR_CR register = 0x01 | 0                  | -    | 64                  |      |  |

| f <sub>HCLK</sub>                  | Internal AHB clock frequency                                  | Power Scale2: Regulator ON,<br>VOS[1:0] bits in PWR_CR register = 0x10 | 0                  | -    | 84                  | MHz  |  |

|                                    |                                                               | Power Scale1: Regulator ON,<br>VOS[1:0] bits in PWR_CR register = 0x11 | 0                  | -    | 100                 |      |  |

| f <sub>PCLK1</sub>                 | Internal APB1 clock frequency                                 | -                                                                      | 0                  | -    | 50                  | MHz  |  |

| f <sub>PCLK2</sub>                 | Internal APB2 clock frequency                                 | -                                                                      | 0                  | -    | 100                 | MHz  |  |

| V <sub>DD</sub>                    | Standard operating voltage                                    | -                                                                      | 1.7 <sup>(1)</sup> | -    | 3.6                 | V    |  |

| V <sub>DDA</sub> <sup>(2)(3)</sup> | Analog operating voltage<br>(ADC limited to 1.2 M<br>samples) | Must be the same potential as $V_{DD}^{(4)}$                           |                    | -    | 2.4                 | v    |  |

| V DDA                              | Analog operating voltage<br>(ADC limited to 2.4 M<br>samples) |                                                                        |                    | -    | 3.6                 | v    |  |

| V <sub>BAT</sub>                   | Backup operating voltage                                      | -                                                                      | 1.65               | -    | 3.6                 | V    |  |

|                                    |                                                               | VOS[1:0] bits in PWR_CR register = 0x01<br>Max frequency 64 MHz        | 1.08<br>(5)        | 1.14 | 1.20 <sup>(5)</sup> |      |  |

| V <sub>12</sub>                    | Regulator ON: 1.2 V internal voltage on VCAP_1 pins           | VOS[1:0] bits in PWR_CR register = 0x10<br>Max frequency 84 MHz        | 1.20<br>(5)        | 1.26 | 1.32 <sup>(5)</sup> | V    |  |

|                                    |                                                               | VOS[1:0] bits in PWR_CR register = 0x11<br>Max frequency 100 MHz       | 1.26               | 1.32 | 1.38                |      |  |

|                                    | Regulator OFF: 1.2 V external                                 | Max frequency 64 MHz                                                   | 1.10               | 1.14 | 1.20                |      |  |

| V <sub>12</sub>                    | voltage must be supplied on                                   | Max frequency 84 MHz                                                   | 1.20               | 1.26 | 1.32                | V    |  |

|                                    | VCAP_1 pins                                                   | Max frequency 100 MHz                                                  | 1.26               | 1.32 | 1.38                | †    |  |

|                                    | Input voltage on RST, FT and                                  | $2 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V}$                      | -0.3               | -    | 5.5                 |      |  |

| V <sub>IN</sub>                    | TC pins <sup>(6)</sup>                                        | $V_{DD} \leq 2 V$                                                      | -0.3               | -    | 5.2                 | V    |  |

|                                    | Input voltage on BOOT0 pin                                    | -                                                                      | 0                  | -    | 9                   | ]    |  |

| Symbol                           | Parameter                                                                            | Conditions                                                                                | Min | Тур | Max | Unit |

|----------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----|-----|-----|------|

| I <sub>RUSH</sub> <sup>(2)</sup> | In-Rush current on<br>voltage regulator power-<br>on (POR or wakeup from<br>Standby) | -                                                                                         | -   | 160 | 200 | mA   |

| E <sub>RUSH</sub> <sup>(2)</sup> | In-Rush energy on<br>voltage regulator power-<br>on (POR or wakeup from<br>Standby)  | V <sub>DD</sub> = 1.7 V, T <sub>A</sub> = 125 °C,<br>I <sub>RUSH</sub> = 171 mA for 31 µs | -   | -   | 5.4 | μC   |

Table 20. Embedded reset and power control block characteristics (continued)

1. The product behavior is guaranteed by design down to the minimum V<sub>POR/PDR</sub> value.

2. Guaranteed by design.

3. The reset timing is measured from the power-on (POR reset or wakeup from  $V_{BAT}$ ) to the instant when first instruction is fetched by the user application code.

#### 6.3.6 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 14: Current consumption measurement scheme*.

All the run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to CoreMark code.

#### Typical and maximum current consumption

The MCU is placed under the following conditions:

- All I/O pins are in input mode with a static value at VDD or VSS (no load).

- All peripherals are disabled except if it is explicitly mentioned.

- The Flash memory access time is adjusted to both f<sub>HCLK</sub> frequency and VDD ranges (refer to *Table 16: Features depending on the operating power supply range*).

- The voltage scaling is adjusted to f<sub>HCLK</sub> frequency as follows:

- Scale 3 for  $f_{HCLK} \le 64$  MHz

- Scale 2 for 64 MHz <  $f_{HCLK} \le 84$  MHz

- Scale 1 for 84 MHz < f<sub>HCLK</sub> ≤ 100 MHz

- The system clock is HCLK,  $f_{PCLK1} = f_{HCLK}/2$ , and  $f_{PCLK2} = f_{HCLK}$ .

- External clock is 4 MHz and PLL is ON except if it is explicitly mentioned.

- The maximum values are obtained for V<sub>DD</sub> = 3.6 V and a maximum ambient temperature (T<sub>A</sub>), and the typical values for T<sub>A</sub>= 25 °C and V<sub>DD</sub> = 3.3 V unless otherwise specified.

The LSE high-power mode allows to cover a wider range of possible crystals but with a cost of higher power consumption.

| Symbol                              | Parameter                               | Conditions                    | Min | Тур  | Max  | Unit |

|-------------------------------------|-----------------------------------------|-------------------------------|-----|------|------|------|

| R <sub>F</sub>                      | Feedback resistor                       | -                             | -   | 18.4 | -    | MΩ   |

| I <sub>DD</sub>                     | LSE current consumption                 | Low-power mode<br>(default)   | -   | -    | 1    | μA   |

|                                     |                                         | High-drive mode               | -   | -    | 3    |      |

| C crit may                          | Maximum critical crystal g <sub>m</sub> | Startup, low-power<br>mode    | -   | -    | 0.56 |      |

| G <sub>m</sub> _crit_max            |                                         | Startup, high-drive<br>mode   | -   | -    | 1.50 | μA/V |

| t <sub>SU(LSE)</sub> <sup>(2)</sup> | startup time                            | V <sub>DD</sub> is stabilized | -   | 2    | -    | s    |

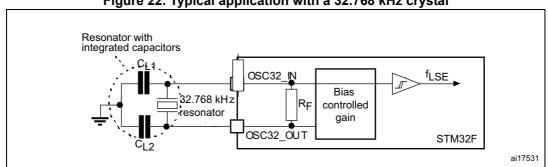

Table 41. LSE oscillator characteristics (f<sub>LSE</sub> = 32.768 kHz) <sup>(1)</sup>

1. Guaranteed by design.

t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is guaranteed by characterization. It is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

*Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

For information about the LSE high-power mode, refer to the reference manual RM0401.

#### Figure 22. Typical application with a 32.768 kHz crystal

- 1. Guaranteed by design.

- 2. The maximum programming time is measured after 100K erase operations.

- 3.  $V_{PP}$  should only be connected during programming/erasing.

| Cumhal           | Devenator      | Conditions                                                                                                                                                                                                          | Value              | 11     |  |

|------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------|--|

| Symbol           | Parameter      | Conditions                                                                                                                                                                                                          | Min <sup>(1)</sup> | Unit   |  |

| N <sub>END</sub> | Endurance      | $T_A = -40 \text{ to } +85 \text{ °C } (6 \text{ suffix versions})$<br>$T_A = -40 \text{ to } +105 \text{ °C } (7 \text{ suffix versions})$<br>$T_A = -40 \text{ to } +125 \text{ °C } (3 \text{ suffix versions})$ | 10                 | Kcycle |  |

|                  |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C                                                                                                                                                                   | 30                 |        |  |

| tRET             | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C                                                                                                                                                                  | 10                 | Years  |  |

|                  |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 125 °C                                                                                                                                                                  | 3                  | rears  |  |

|                  |                | 10 kcycle <sup>(2)</sup> at T <sub>A</sub> = 55 °C                                                                                                                                                                  | 20                 |        |  |

| Table 49. Flash memor | y endurance and data retention |

|-----------------------|--------------------------------|

|-----------------------|--------------------------------|

1. Guaranteed by characterization.

2. Cycling performed over the whole temperature range.

#### 6.3.13 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 51*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                                           | Level/<br>Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD}$ = 3.3 V, LQFP64, T <sub>A</sub> = +25 °C,<br>f <sub>HCLK</sub> = 100 MHz, conforms to<br>IEC 61000-4-2                      | 2B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD} = 3.3 \text{ V}, \text{LQFP64}, \text{T}_{A} = +25 \text{ °C},$<br>f <sub>HCLK</sub> = 100 MHz, conforms to<br>IEC 61000-4-4 | 4A              |

#### Table 50. EMS characteristics

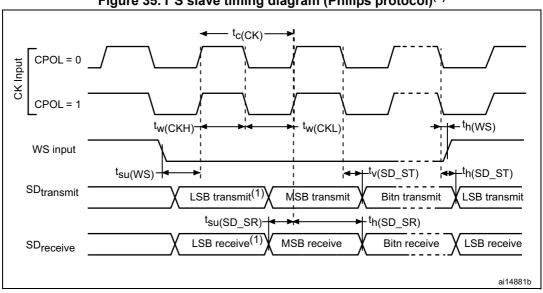

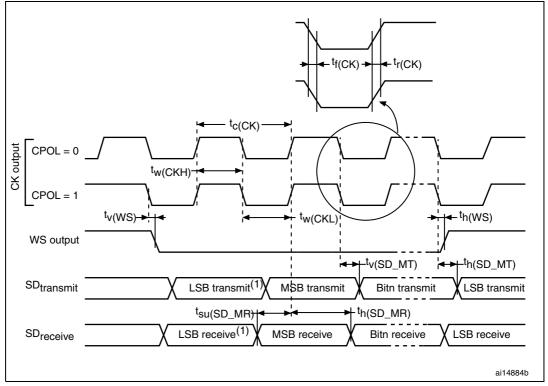

Figure 35. I<sup>2</sup>S slave timing diagram (Philips protocol)<sup>(1)</sup>

LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

#### Figure 36. I<sup>2</sup>S master timing diagram (Philips protocol)<sup>(1)</sup>

1. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

#### 6.3.20 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 66* are derived from tests performed under the ambient temperature,  $f_{PCLK2}$  frequency and  $V_{DDA}$  supply voltage conditions summarized in *Table 15*.

| Symbol                           | Parameter                                          | Conditions                                                                            | Min                                                         | Тур | Мах               | Unit               |

|----------------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------|-----|-------------------|--------------------|

| V <sub>DDA</sub>                 | Power supply                                       | N N 10 10 10 10                                                                       | 1.7 <sup>(1)</sup>                                          | -   | 3.6               |                    |

| V <sub>REF+</sub>                | Positive reference voltage                         | V <sub>DDA</sub> –V <sub>REF+</sub> < 1.2 V                                           | 1.7 <sup>(1)</sup>                                          | -   | V <sub>DDA</sub>  | V                  |

| V <sub>REF-</sub>                | Negative reference voltage -                       |                                                                                       | -                                                           | 0   | -                 |                    |

| £                                |                                                    | $V_{DDA} = 1.7^{(1)}$ to 2.4 V                                                        | 0.6                                                         | 15  | 18                | MHz                |

| f <sub>ADC</sub>                 | ADC clock frequency                                | V <sub>DDA</sub> = 2.4 to 3.6 V                                                       | 0.6                                                         | 30  | 36                | MHz                |

| f <sub>TRIG</sub> <sup>(2)</sup> | External trigger frequency                         | f <sub>ADC</sub> = 30 MHz,<br>12-bit resolution                                       | -                                                           | -   | 1764              | kHz                |

|                                  |                                                    | -                                                                                     | -                                                           | -   | 17                | 1/f <sub>ADC</sub> |

| V <sub>AIN</sub>                 | Conversion voltage range <sup>(3)</sup>            | -                                                                                     | 0 (V <sub>SSA</sub> or V <sub>REF-</sub><br>tied to ground) | -   | V <sub>REF+</sub> | V                  |

| R <sub>AIN</sub> <sup>(2)</sup>  | External input impedance                           | See <i>Equation 1</i> for details                                                     | -                                                           | -   | 50                | κΩ                 |

| $R_{ADC}^{(2)(4)}$               | Sampling switch resistance                         | -                                                                                     | -                                                           | -   | 6                 | кΩ                 |

| C <sub>ADC</sub> <sup>(2)</sup>  | Internal sample and hold capacitor                 | -                                                                                     | -                                                           | 4   | 7                 | pF                 |

| t <sub>lat</sub> (2)             | Injection trigger conversion                       | f <sub>ADC</sub> = 30 MHz                                                             | -                                                           | -   | 0.100             | μs                 |

| 'lat` '                          | latency                                            | -                                                                                     | -                                                           | -   | 3 <sup>(5)</sup>  | 1/f <sub>ADC</sub> |

| t <sub>latr</sub> (2)            | Regular trigger conversion                         | f <sub>ADC</sub> = 30 MHz                                                             | -                                                           | 1   | 0.067             | μs                 |

| Yatr                             | latency                                            | -                                                                                     | -                                                           | -   | 2 <sup>(5)</sup>  | 1/f <sub>ADC</sub> |

| ts <sup>(2)</sup>                | Sampling time                                      | f <sub>ADC</sub> = 30 MHz                                                             | 0.100                                                       | 1   | 16                | μs                 |

| Ũ                                |                                                    | -                                                                                     | 3                                                           | -   | 480               | 1/f <sub>ADC</sub> |

| t <sub>STAB</sub> <sup>(2)</sup> | Power-up time                                      | -                                                                                     | -                                                           | 2   | 3                 | μs                 |

|                                  |                                                    | f <sub>ADC</sub> = 30 MHz<br>12-bit resolution                                        | 0.50                                                        | -   | 16.40             | μs                 |

|                                  | Total conversion time<br>(including sampling time) | f <sub>ADC</sub> = 30 MHz<br>10-bit resolution                                        | 0.43                                                        | -   | 16.34             | μs                 |

| t <sub>CONV</sub> <sup>(2)</sup> |                                                    | f <sub>ADC</sub> = 30 MHz<br>8-bit resolution                                         | 0.37                                                        | -   | 16.27             | μs                 |

|                                  |                                                    | f <sub>ADC</sub> = 30 MHz<br>6-bit resolution                                         | 0.30                                                        | -   | 16.20             | μs                 |

|                                  |                                                    | 9 to 492 (t <sub>S</sub> for sampling +n-bit resolution for successive approximation) |                                                             |     |                   |                    |

| Symbol | Parameter                    | Test conditions                                                                | Тур  | Max <sup>(2)</sup> | Unit |

|--------|------------------------------|--------------------------------------------------------------------------------|------|--------------------|------|

| ET     | Total unadjusted error       |                                                                                | ±2   | ±5                 |      |

| EO     | Offset error                 | f <sub>ADC</sub> = 30 MHz,<br>R <sub>AIN</sub> < 10 kΩ                         | ±1.5 | ±2.5               |      |

| EG     | Gain error                   | V <sub>DDA</sub> = 2.4 to 3.6 V,                                               | ±1.5 | ±4                 | LSB  |

| ED     | Differential linearity error | V <sub>REF</sub> = 1.7 to 3.6 V,<br>V <sub>DDA</sub> –V <sub>REF</sub> < 1.2 V | ±1   | ±2                 |      |

| EL     | Integral linearity error     |                                                                                | ±1.5 | ±3                 |      |

#### Table 68. ADC accuracy at $f_{ADC} = 30 \text{ MHz}^{(1)}$

1. Better performance could be achieved in restricted  $\mathrm{V}_{\mathrm{DD}},$  frequency and temperature ranges.

2. Guaranteed by characterization.

| Symbol | Parameter                    | Test conditions                                                     | Тур | Max <sup>(2)</sup> | Unit |  |  |  |  |

|--------|------------------------------|---------------------------------------------------------------------|-----|--------------------|------|--|--|--|--|

| ET     | Total unadjusted error       |                                                                     | ±4  | ±7                 |      |  |  |  |  |

| EO     | Offset error                 | f <sub>ADC</sub> =36 MHz,<br>V <sub>DDA</sub> = 2.4 to 3.6 V,       | ±2  | ±3                 |      |  |  |  |  |

| EG     | Gain error                   | V <sub>DDA</sub> = 2.4 to 3.6 V,<br>V <sub>REF</sub> = 1.7 to 3.6 V | ±3  | ±6                 | LSB  |  |  |  |  |

| ED     | Differential linearity error | $V_{DDA} - V_{REF} < 1.2 V$                                         | ±2  | ±3                 |      |  |  |  |  |

| EL     | Integral linearity error     |                                                                     | ±3  | ±6                 |      |  |  |  |  |

### Table 69. ADC accuracy at $f_{ADC} = 36 \text{ MHz}^{(1)}$

1. Better performance could be achieved in restricted  $V_{\text{DD}}$ , frequency and temperature ranges.

2. Guaranteed by characterization.

| Symbol | Parameter                            | Test conditions                           | Min | Тур  | Max | Unit |

|--------|--------------------------------------|-------------------------------------------|-----|------|-----|------|

| ENOB   | Effective number of bits             | e number of bits f <sub>ADC</sub> =18 MHz |     | 10.4 | -   | bits |

| SINAD  | Signal-to-noise and distortion ratio | $V_{DDA} = V_{REF+} = 1.7 V$              | 64  | 64.2 | -   |      |

| SNR    | Signal-to-noise ratio                | Input Frequency = 20 KHz                  | 64  | 65   | -   | dB   |

| THD    | Total harmonic distortion            | Temperature = 25 °C                       | -   | -72  | -67 |      |

1. Guaranteed by characterization.

| Symbol | Parameter                            | Test conditions              | Min  | Тур  | Max | Unit |

|--------|--------------------------------------|------------------------------|------|------|-----|------|

| ENOB   | Effective number of bits             | f <sub>ADC</sub> = 36 MHz    | 10.6 | 10.8 | -   | bits |

| SINAD  | Signal-to noise and distortion ratio | $V_{DDA} = V_{REF+} = 3.3 V$ | 66   | 67   | -   |      |

| SNR    | Signal-to noise ratio                | Input Frequency = 20 KHz     | 64   | 68   | -   | dB   |

| THD    | Total harmonic distortion            | Temperature = 25 °C          | -    | -72  | -70 |      |

1. Guaranteed by characterization.

### 6.3.24 DAC electrical characteristics

| Table 77. DAC characteristics     |                                                    |                         |                                                       |                    |     |                                |      |                                                                                                                         |  |  |

|-----------------------------------|----------------------------------------------------|-------------------------|-------------------------------------------------------|--------------------|-----|--------------------------------|------|-------------------------------------------------------------------------------------------------------------------------|--|--|

| Symbol                            | Parameter                                          | Cond                    | itions                                                | Min                | Тур | Мах                            | Unit | Comments                                                                                                                |  |  |

| V <sub>DDA</sub>                  | Analog supply voltage                              | -                       |                                                       | 1.7 <sup>(1)</sup> | -   | 3.6                            | V    | -                                                                                                                       |  |  |

| V <sub>REF+</sub>                 | Reference supply voltage                           | -                       |                                                       | 1.7 <sup>(1)</sup> | -   | 3.6                            | V    | V <sub>REF+</sub> ⊴V <sub>DDA</sub>                                                                                     |  |  |

| $V_{SSA}$                         | Ground                                             |                         | -                                                     | 0                  | -   | 0                              | V    | -                                                                                                                       |  |  |

| R <sub>LOAD</sub> <sup>(2)</sup>  | Resistive load                                     | DAC to V <sub>SSA</sub> | kΩ                                                    | -                  |     |                                |      |                                                                                                                         |  |  |

| , LOAD                            |                                                    | buffer ON               | R <sub>LOAD</sub><br>connected<br>to V <sub>DDA</sub> | 25                 | -   | -                              | kΩ   | -                                                                                                                       |  |  |

| R <sub>O</sub> <sup>(2)</sup>     | Impedance output<br>with buffer OFF                | -                       |                                                       | -                  | -   | 15                             | kΩ   | When the buffer is OFF, the Minimum resistive load between DAC_OUT and $V_{SS}$ to have a 1% accuracy is 1.5 M $\Omega$ |  |  |

| C <sub>LOAD</sub> <sup>(2)</sup>  | Capacitive load                                    | -                       |                                                       | -                  | -   | 50                             | pF   | Maximum capacitive load at DAC_OUT pin (when the buffer is ON).                                                         |  |  |

| DAC_OUT<br>min <sup>(2)</sup>     | Lower DAC_OUT<br>voltage with buffer<br>ON         |                         | -                                                     | 0.2                | -   | -                              | v    | It gives the maximum output<br>excursion of the DAC.<br>It corresponds to 12-bit input                                  |  |  |

| DAC_OUT<br>max <sup>(2)</sup>     | Higher DAC_OUT<br>voltage with buffer<br>ON        |                         | -                                                     | -                  | -   | V <sub>DDA</sub><br>- 0.2      | V    | code (0x0E0) to (0xF1C) at<br>V <sub>REF+</sub> = 3.6 V and (0x1C7)<br>to (0xE38) at V <sub>REF+</sub> = 1.7 V          |  |  |

| DAC_OUT<br>min <sup>(2)</sup>     | Lower DAC_OUT<br>voltage with buffer<br>OFF        |                         | -                                                     | -                  | 0.5 | -                              | mV   | It gives the maximum output                                                                                             |  |  |

| DAC_OUT<br>max <sup>(2)</sup>     | Higher DAC_OUT<br>voltage with buffer<br>OFF       |                         | -                                                     | -                  | -   | V <sub>REF+</sub><br>_<br>1LSB | V    | excursion of the DAC.                                                                                                   |  |  |

| L                                 | DAC DC V <sub>REF</sub><br>current                 |                         | -                                                     | -                  | 170 | 240                            |      | With no load, worst code<br>( $0x800$ ) at V <sub>REF+</sub> = 3.6 V in<br>terms of DC consumption on<br>the inputs     |  |  |

| I <sub>VREF+</sub> <sup>(4)</sup> | consumption in<br>quiescent mode<br>(Standby mode) |                         | -                                                     | -                  | 50  | 75                             | μA   | With no load, worst code<br>(0xF1C) at $V_{REF+}$ = 3.6 V in<br>terms of DC consumption on<br>the inputs                |  |  |

#### Table 77. DAC characteristics

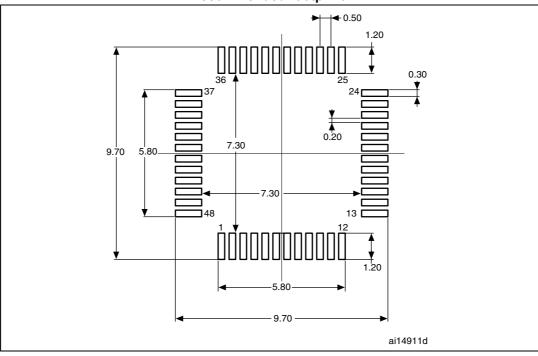

1. Dimensions are expressed in millimeters.

# **Revision history**

| Dete        | Devision | Table 89. Document revision history                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 28-Sep-2015 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 07-Dec-2015 | 2        | Junction temperature range changed to –40 to + 110 °C for WLCSP49 package.<br>Updated <i>Figure 7: UFQFPN48 pinout</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 10-Aug-2016 | 3        | Updated:         - Table 2: STM32F410x8/B features and peripheral counts         - Table 9: STM32F410x8/B pin definitions         - Table 14: Thermal characteristics         - Table 15: General operating conditions         - Table 20: Embedded reset and power control block characteristics         - Tables from Table 21: Typical and maximum current consumption, code with data processing (ART accelerator disabled) running from SRAM - VDD = 1.7 V to Table 34: Typical and maximum current consumptions in VBAT mode (LSE and RTC ON, LSE low- drive mode)         - Table 42: HSI oscillator characteristics         - Table 43: LSI oscillator characteristics         - Table 52: ESD absolute maximum ratings         - Table 66: ADC characteristics         - Table 75: Embedded internal reference voltage         - Table 87: Ordering information scheme         - Figure 16: Typical VBAT current consumption (LSE and RTC ON/LSE oscillator in "low power" mode selection         - Section 7: Package information         Added:         - Figure 8: UFBGA64 pinout         - Figure 49: LQFP48 marking example (package top view)         - Figure 55: UFBGA64 marking example (package top view) |

| Table 8 | 89. D | ocument | revision | history |

|---------|-------|---------|----------|---------|

|---------|-------|---------|----------|---------|