Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 100MHz                                                                |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT          |

| Number of I/O              | 50                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 32K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                           |

| Data Converters            | A/D 16x12b; D/A 1x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-UFBGA                                                              |

| Supplier Device Package    | 64-UFBGA (5x5)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f410rbi6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.4 Memory protection unit

The memory protection unit (MPU) is used to manage the CPU accesses to memory to prevent one task to accidentally corrupt the memory or resources used by any other active task. This memory area is organized into up to 8 protected areas that can in turn be divided up into 8 subareas. The protection area sizes are between 32 bytes and the whole 4 gigabytes of addressable memory.

The MPU is especially helpful for applications where some critical or certified code has to be protected against the misbehavior of other tasks. It is usually managed by an RTOS (real-time operating system). If a program accesses a memory location that is prohibited by the MPU, the RTOS can detect it and take action. In an RTOS environment, the kernel can dynamically update the MPU area setting, based on the process to be executed.

The MPU is optional and can be bypassed for applications that do not need it.

# 3.5 Embedded Flash memory

The devices embed up to 128 Kbytes of Flash memory available for storing programs and data, plus 512 bytes of OTP memory organized in 16 blocks which can be independently locked.

To optimize the power consumption the Flash memory can also be switched off in Run or in Sleep mode (see *Section 3.18: Low-power modes*).

Two modes are available: Flash in Stop mode or in DeepSleep mode (trade off between power saving and startup time.

Before disabling the Flash, the code must be executed from the internal RAM.

# 3.6 CRC (cyclic redundancy check) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit data word and a fixed generator polynomial.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a software signature during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

# 3.7 Embedded SRAM

All devices embed 32 Kbytes of system SRAM which can be accessed (read/write) at CPU clock speed with 0 wait states

| Timer<br>type        | Timer  | Counter<br>resolution | Counter<br>type         | Prescaler<br>factor                         | DMA<br>request<br>generation | Capture/<br>compare<br>channels | Complemen-<br>tary output | Max.<br>interface<br>clock<br>(MHz) | Max.<br>timer<br>clock<br>(MHz) |

|----------------------|--------|-----------------------|-------------------------|---------------------------------------------|------------------------------|---------------------------------|---------------------------|-------------------------------------|---------------------------------|

| Advanced<br>-control | TIM1   | 16-bit                | Up,<br>Down,<br>Up/down | Any<br>integer<br>between<br>1 and<br>65536 | Yes                          | 4                               | Yes                       | 100                                 | 100                             |

|                      | TIM5   | 32-bit                | Up,<br>Down,<br>Up/down | Any<br>integer<br>between<br>1 and<br>65536 | Yes                          | 4                               | No                        | 50                                  | 100                             |

| General<br>purpose   | TIM9   | 16-bit                | Up                      | Any<br>integer<br>between<br>1 and<br>65536 | No                           | 2                               | No                        | 100                                 | 100                             |

|                      | TIM11  | 16-bit                | Up                      | Any<br>integer<br>between<br>1 and<br>65536 | No                           | 1                               | No                        | 100                                 | 100                             |

| Basic                | TIM6   | 16-bit                | Up                      | Any<br>integer<br>between<br>1 and<br>65536 | Yes                          | 0                               | No                        | 50                                  | 100                             |

| Low-<br>power        | LPTIM1 | 16-bit                | Up                      | Between<br>1 and 128                        | No                           | 2                               | No                        | 50                                  | 100                             |

Table 5. Timer feature comparison

|         | Р      | in Num          | nber   |         |                                                      | e e e    |               |       |                                                                        |                         |

|---------|--------|-----------------|--------|---------|------------------------------------------------------|----------|---------------|-------|------------------------------------------------------------------------|-------------------------|

| WLCSP36 | LQFP48 | <b>UFQFPN48</b> | LQFP64 | UFBGA64 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Notes | Alternate functions                                                    | Additional<br>functions |

| E3      | 21     | 21              | 29     | G7      | PB10                                                 | I/O      | FT            | -     | I2C2_SCL,<br>SPI2_SCK/I2S2_CK,<br>I2S1_MCK,<br>I2C4_SCL,<br>EVENTOUT   | -                       |

| E2      | 22     | 22              | 30     | H7      | VCAP_1                                               | S        | -             | -     | -                                                                      | -                       |

| F2      | 23     | 23              | 31     | D6      | VSS                                                  | S        | I             | -     | -                                                                      | -                       |

| F1      | 24     | 24              | 32     | E5      | VDD                                                  | S        | -             | -     | -                                                                      | -                       |

| E1      | 25     | 25              | 33     | H8      | PB12                                                 | I/O      | FT            | -     | TIM1_BKIN,<br>TIM5_CH1,<br>I2C2_SMBA,<br>SPI2_NSS/I2S2_WS,<br>EVENTOUT | -                       |

| -       | 26     | 26              | 34     | G8      | PB13                                                 | I/O      | FT            | -     | TIM1_CH1N,<br>I2C4_SMBA,<br>SPI2_SCK/I2S2_CK,<br>EVENTOUT              | -                       |

| -       | 27     | 27              | 35     | F8      | PB14                                                 | I/O      | FT            | -     | TIM1_CH2N,<br>I2C4_SDA,<br>SPI2_MISO,<br>EVENTOUT                      | -                       |

| -       | 28     | 28              | 36     | F7      | PB15                                                 | I/O      | FT            | -     | RTC_50Hz,<br>TIM1_CH3N,<br>I2C4_SCL,<br>SPI2_MOSI/I2S2_SD,<br>EVENTOUT | -                       |

| -       | -      | -               | 37     | F6      | PC6                                                  | I/O      | FT            | -     | TRACECLK,<br>I2C4_SCL,<br>I2S2_MCK,<br>USART6_TX,<br>EVENTOUT          | -                       |

| -       | -      | -               | 38     | E7      | PC7                                                  | I/O      | FT            | -     | I2C4_SDA,<br>SPI2_SCK/I2S2_CK,<br>I2S1_MCK,<br>USART6_RX,<br>EVENTOUT  | -                       |

| -       | -      | -               | 39     | E8      | PC8                                                  | I/O      | FT            | -     | USART6_CK,<br>EVENTOUT                                                 | -                       |

| -       | -      | -               | 40     | D8      | PC9                                                  | I/O      | FT            | -     | MCO_2, I2C4_SDA,<br>I2S2_CKIN,<br>EVENTOUT                             | -                       |

Table 9. STM32F410x8/B pin definitions (continued)

42/142

DocID028094 Rev 5

5

|        |      |              |             |              | Tab            | le 10. Al          | ternate fu              | inction m                             | apping (          | continu | ed)           |      |      |      |      |      |          |

|--------|------|--------------|-------------|--------------|----------------|--------------------|-------------------------|---------------------------------------|-------------------|---------|---------------|------|------|------|------|------|----------|

|        |      | AF0          | AF1         | AF2          | AF3            | AF4                | AF5                     | AF6                                   | AF7               | AF8     | AF9           | AF10 | AF11 | AF12 | AF13 | AF14 | AF15     |

| Po     | ort  | SYS_AF       | TIM1/LPTIM1 | TIM5         | TIM9/<br>TIM11 | I2C1/I2C2<br>/I2C4 | SPI1/I2S1/S<br>PI2/I2S2 | SPI1/I2S1/<br>SPI2/I2S2/<br>SPI5/I2S5 | USART1/<br>USART2 | USART6  | 12C2/<br>12C4 | -    | -    | -    | -    | -    | SYS_AF   |

|        | PB0  | -            | TIM1_CH2N   | -            | -              | -                  | -                       | SPI5_SCK/<br>I2S5_CK                  | -                 | -       | -             | -    | -    | -    | -    | -    | EVENTOUT |

|        | PB1  | -            | TIM1_CH3N   | -            | -              | -                  | -                       | SPI5_NSS/<br>I2S5_WS                  | -                 | -       | -             | -    | -    | -    | -    | -    | EVENTOUT |

|        | PB2  | -            | LPTIM1_OUT  | -            | -              | -                  | -                       | -                                     | -                 | -       | -             | -    | -    | -    | -    | -    | EVENTOUT |

|        | PB3  | JTDO-<br>SWO | -           | -            | -              | I2C4_<br>SDA       | SPI1_SCK/I<br>2S1_CK    | -                                     | USART1_<br>RX     | -       | I2C2_<br>SDA  | -    | -    | -    | -    | -    | EVENTOUT |

|        | PB4  | JTRST        | -           | -            | -              | -                  | SPI1_MISO               | -                                     | -                 | -       | -             | -    | -    | -    | -    | -    | EVENTOUT |

|        | PB5  | -            | LPTIM1_IN1  | -            | -              | I2C1_<br>SMBA      | SPI1_MOSI<br>/I2S1_SD   | -                                     | -                 | -       | -             | -    | -    | -    | -    | -    | EVENTOUT |

|        | PB6  | -            | LPTIM1_ETR  | -            | -              | I2C1_<br>SCL       | -                       | -                                     | USART1_<br>TX     | -       | -             | -    | -    | -    | -    | -    | EVENTOUT |

|        | PB7  | -            | LPTIM1_IN2  | -            | -              | I2C1_<br>SDA       | -                       | -                                     | USART1_<br>RX     | -       | -             | -    | -    | -    | -    | -    | EVENTOUT |

| Port B | PB8  | -            | LPTIM1_OUT  | -            | -              | I2C1_<br>SCL       | -                       | SPI5_MOSI<br>/I2S5_SD                 | -                 | -       | -             | -    | -    | -    | -    | -    | EVENTOUT |

|        | PB9  | -            | -           | -            | TIM11_<br>CH1  | I2C1_<br>SDA       | SPI2_NSS/<br>I2S2_WS    | -                                     | -                 | -       | I2C2_<br>SDA  | -    | -    | -    | -    | -    | EVENTOUT |

|        | PB10 | -            | -           | -            | -              | I2C2_<br>SCL       | SPI2_SCK/<br>I2S2_CK    | I2S1_MCK                              | -                 | -       | I2C4_<br>SCL  | -    | -    | -    | -    | -    | EVENTOUT |

|        | PB11 | TRACED3      | -           | TIM5_<br>CH4 | -              | I2C2_<br>SDA       | I2S2_CKIN               | -                                     | -                 | -       | -             | -    | -    | -    | -    | -    | EVENTOUT |

|        | PB12 | -            | TIM1_BKIN   | TIM5_<br>CH1 | -              | I2C2_<br>SMBA      | SPI2_NSS/<br>I2S2_WS    | -                                     | -                 | -       | -             | -    | -    | -    | -    | -    | EVENTOUT |

|        | PB13 | -            | TIM1_CH1N   | -            | -              | I2C4_<br>SMBA      | SPI2_SCK<br>/I2S2_CK    | -                                     | -                 | -       | -             | -    | -    | -    | -    | -    | EVENTOUT |

|        | PB14 | -            | TIM1_CH2N   | -            | -              | I2C4_<br>SDA       | SPI2_MISO               | -                                     | -                 | -       | -             | -    | -    | -    | -    | -    | EVENTOUT |

|        | PB15 | RTC_<br>50Hz | TIM1_CH3N   | -            | -              | I2C4_<br>SCL       | SPI2_MOSI<br>/I2S2_SD   | -                                     | -                 | -       | -             | -    | -    | -    | -    | -    | EVENTOUT |

Pinouts and pin description

| Symbol                               | Ratings                                                                         | Max. | Unit |

|--------------------------------------|---------------------------------------------------------------------------------|------|------|

| $\Sigma I_{VDD}$                     | Total current into sum of all $V_{DD_x}$ power lines (source) <sup>(1)</sup>    | 160  |      |

| $\Sigma I_{VSS}$                     | Total current out of sum of all $V_{SS_x}$ ground lines $(sink)^{(1)}$          | -160 |      |

| I <sub>VDD</sub>                     | Maximum current into each V <sub>DD_x</sub> power line (source) <sup>(1)</sup>  | 100  |      |

| I <sub>VSS</sub>                     | Maximum current out of each $V_{SS_x}$ ground line (sink) <sup>(1)</sup>        | -100 |      |

| I                                    | Output current sunk by any I/O and control pin                                  | 25   |      |

| Ι <sub>ΙΟ</sub>                      | Output current sourced by any I/O and control pin                               | -25  | mA   |

| ΣI                                   | Total output current sunk by sum of all I/O and control pins <sup>(2)</sup>     | 120  |      |

| $\Sigma I_{IO}$                      | Total output current sourced by sum of all I/Os and control pins <sup>(2)</sup> | -120 |      |

| (3)                                  | Injected current on FT and TC pins <sup>(4)</sup>                               | 5/10 |      |

| I <sub>INJ(PIN)</sub> <sup>(3)</sup> | Injected current on NRST and B pins <sup>(4)</sup>                              |      |      |

| $\Sigma I_{INJ(PIN)}$                | Total injected current (sum of all I/O and control pins) <sup>(5)</sup>         | ±25  |      |

#### Table 13. Current characteristics

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

2. This current consumption must be correctly distributed over all I/Os and control pins.

3. Negative injection disturbs the analog performance of the device. See note in Section 6.3.20: 12-bit ADC characteristics.

4. Positive injection is not possible on these I/Os and does not occur for input voltages lower than the specified maximum value.

5. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values).

| Symbol            | Ratings                                                                                      | Value                   | Unit |

|-------------------|----------------------------------------------------------------------------------------------|-------------------------|------|

| T <sub>STG</sub>  | Storage temperature range                                                                    | –65 to +150             |      |

| TJ                | Maximum junction temperature                                                                 | 130                     |      |

| T <sub>LEAD</sub> | Maximum lead temperature during soldering<br>(WLCSP36, LQFP48, LQFP64, UFQFPN48,<br>UFBGA64) | see note <sup>(1)</sup> | °C   |

#### Table 14. Thermal characteristics

Compliant with JEDEC Std J-STD-020D (for small body, Sn-Pb or Pb assembly), the ST ECOPACK<sup>®</sup> 7191395 specification, and the European directive on Restrictions on Hazardous Substances (ROHS directive 2011/65/EU, July 2011).

| Operating<br>power<br>supply<br>range           | ADC<br>operation                     | Maximum<br>Flash<br>memory<br>access<br>frequency<br>with no wait<br>states<br>(f <sub>Flashmax</sub> ) | Maximum Flash<br>memory access<br>frequency with<br>wait states <sup>(1)(2)</sup> | I/O operation                                                | Clock output<br>frequency on<br>I/O pins <sup>(3)</sup>                                                       | Possible<br>Flash<br>memory<br>operations        |

|-------------------------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| V <sub>DD</sub> =1.7 to<br>2.1 V <sup>(4)</sup> | Conversion<br>time up to<br>1.2 Msps | 16 MHz <sup>(5)</sup>                                                                                   | 100 MHz with 6<br>wait states                                                     | <ul> <li>No I/O compensation</li> </ul>                      | up to 30 MHz                                                                                                  | 8-bit erase<br>and program<br>operations<br>only |

| V <sub>DD</sub> = 2.1 to<br>2.4 V               | Conversion<br>time up to<br>1.2 Msps | 18 MHz                                                                                                  | 100 MHz with 5<br>wait states                                                     | <ul> <li>No I/O compensation</li> </ul>                      | up to 30 MHz                                                                                                  | 16-bit erase<br>and program<br>operations        |

| V <sub>DD</sub> = 2.4 to<br>2.7 V               | Conversion<br>time up to<br>2.4 Msps | 24 MHz                                                                                                  | 100 MHz with 4<br>wait states                                                     | <ul> <li>I/O</li> <li>compensation</li> <li>works</li> </ul> | up to 50 MHz                                                                                                  | 16-bit erase<br>and program<br>operations        |

| V <sub>DD</sub> = 2.7 to<br>3.6 V               | Conversion<br>time up to<br>2.4 Msps | 30 MHz                                                                                                  | 100 MHz with 3<br>wait states                                                     | <ul> <li>I/O<br/>compensation<br/>works</li> </ul>           | - up to<br>100 MHz<br>when $V_{DD}$ =<br>3.0 to 3.6 V<br>- up to<br>50 MHz<br>when $V_{DD}$ =<br>2.7 to 3.0 V | 32-bit erase<br>and program<br>operations        |

Table 16. Features depending on the operating power supply range

1. Applicable only when the code is executed from Flash memory. When the code is executed from RAM, no wait state is required.

2. Thanks to the ART accelerator and the 128-bit Flash memory, the number of wait states given here does not impact the execution speed from Flash memory since the ART accelerator allows to achieve a performance equivalent to 0 wait state program execution.

3. Refer to Table 57: I/O AC characteristics for frequencies vs. external load.

4. V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V, with the use of an external power supply supervisor (refer to Section 3.15.2: Internal reset OFF).

5. Prefetch is not available. Refer to AN3430 application note for details on how to adjust performance and power.

|                 |                               |                                                                  |                                          |     | PLL                 | Тур                       |                           | Ma                        | x <sup>(2)</sup>           |                            |      |  |

|-----------------|-------------------------------|------------------------------------------------------------------|------------------------------------------|-----|---------------------|---------------------------|---------------------------|---------------------------|----------------------------|----------------------------|------|--|

| Symbol          | Parameter                     | Conditions                                                       | f <sub>HCLK</sub> Voltage<br>(MHz) scale |     | VCO<br>(MHz)<br>(1) | Т <sub>А</sub> =<br>25 °С | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | T <sub>A</sub> =<br>125 °C | Unit |  |

|                 |                               |                                                                  | 100                                      | S1  | 200                 | 16.3                      | 17.3 <sup>(5)</sup>       | 17.1                      | 17.5 <sup>(6)</sup>        | 18.4 <sup>(5)</sup>        |      |  |

|                 |                               |                                                                  | 84                                       | S2  | 168                 | 13.2                      | 14.1                      | 14.0                      | 14.3                       | 15.2                       |      |  |

|                 |                               | External clock,                                                  | 64                                       | S3  | 128                 | 9.3                       | 10.0                      | 9.9                       | 10.2                       | 11.1                       |      |  |

|                 |                               | all peripherals<br>enabled <sup>(3)(4)</sup>                     | 50                                       | S3  | 100                 | 7.4                       | 8.0                       | 8.0                       | 8.3                        | 9.2                        |      |  |

|                 |                               | enabled <sup>(3)(4)</sup>                                        | 25                                       | S3  | 100                 | 4.2                       | 4.7                       | 4.8                       | 5.0                        | 5.9                        |      |  |

|                 |                               | 20                                                               | S3                                       | 160 | 3.7                 | 4.2                       | 4.3                       | 4.6                       | 5.5                        |                            |      |  |

|                 |                               | HSI, PLL<br>OFF,<br>all peripherals<br>enabled <sup>(3)(4)</sup> | 16                                       | S3  | off                 | 2.4                       | 2.8                       | 3.0                       | 3.4                        | 4.3                        |      |  |

|                 | Supply                        |                                                                  | 1                                        | S3  | off                 | 0.6                       | 1.0                       | 1.2                       | 1.5                        | 2.4                        |      |  |

| I <sub>DD</sub> | current in<br><b>Run mode</b> |                                                                  | 100                                      | S1  | 200                 | 10.6                      | 11.4 <sup>(5)</sup>       | 11.4                      | 11.7 <sup>(6)</sup>        | 12.6 <sup>(5)</sup>        | mA   |  |

|                 |                               | External                                                         | 84                                       | S2  | 168                 | 8.7                       | 9.4                       | 9.3                       | 9.7                        | 10.6                       |      |  |

|                 |                               | External clock,                                                  | 64                                       | S3  | 128                 | 6.2                       | 6.8                       | 6.8                       | 7.1                        | 7.9                        |      |  |

|                 |                               | allperipherals                                                   | all peripherals disabled <sup>(3)</sup>  | 50  | S3                  | 100                       | 5.0                       | 5.5                       | 5.5                        | 5.8                        | 6.8  |  |

|                 |                               | uisabieu                                                         | 25                                       | S3  | 100                 | 2.9                       | 3.4                       | 3.5                       | 3.8                        | 4.7                        |      |  |

|                 |                               |                                                                  | 20                                       | S3  | 160                 | 2.7                       | 3.1                       | 3.2                       | 3.5                        | 4.4                        |      |  |

|                 |                               | HSI, PLL                                                         | 16                                       | S3  | off                 | 1.7                       | 2.1                       | 2.3                       | 2.6                        | 3.5                        |      |  |

|                 |                               | OFF,<br>all peripherals<br>disabled <sup>(3)</sup>               | 1                                        | S3  | off                 | 0.6                       | 0.9                       | 1.1                       | 1.5                        | 2.4                        |      |  |

# Table 24. Typical and maximum current consumption in run mode, code with data processing (ART accelerator enabled except prefetch) running from Flash memory - V<sub>DD</sub> = 3.6 V

1. Refer to *Table 44* and RM0401 for the possible PLL VCO setting

2. Guaranteed by characterization, unless otherwise specified.

3. When the ADC is ON (ADON bit set in ADC\_CR2), an additional power consumption of 1.6 mA must be added.

4. Add an additional power consumption of 1.6 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is ON (ADON bit is set in the ADC\_CR2 register)

5. Guaranteed by tests in production.

6. Guaranteed by test in production on temperature range 7 salestypes only.

|                 | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                                                                                             |                            |                  | PLL                 | Тур                       |                           |                           | x <sup>(2)</sup>           |                            |      |     |     |     |     |  |

|-----------------|-----------------------------------------|---------------------------------------------------------------------------------------------|----------------------------|------------------|---------------------|---------------------------|---------------------------|---------------------------|----------------------------|----------------------------|------|-----|-----|-----|-----|--|

| Symbol          | Parameter                               | Conditions                                                                                  | f <sub>HCLK</sub><br>(MHz) | Voltage<br>scale | VCO<br>(MHz)<br>(1) | Т <sub>А</sub> =<br>25 °С | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | T <sub>A</sub> =<br>125 °C | Unit |     |     |     |     |  |

|                 |                                         |                                                                                             | 100                        | S1               | 200                 | 2.2                       | 2.3 <sup>(5)</sup>        | 2.6                       | 3.0 <sup>(6)</sup>         | 3.8 <sup>(5)</sup>         |      |     |     |     |     |  |

|                 |                                         | All peripherals<br>disabled,                                                                | 84                         | S2               | 168                 | 1.8                       | 1.9                       | 2.2                       | 2.6                        | 3.4                        |      |     |     |     |     |  |

|                 |                                         | External clock,<br>PLL ON, Flash                                                            | 64                         | S3               | 128                 | 1.4                       | 1.5                       | 1.8                       | 2.1                        | 2.9                        |      |     |     |     |     |  |

|                 |                                         | memory in Deep                                                                              | 50                         | S3               | 100                 | 1.2                       | 1.3                       | 1.6                       | 1.9                        | 2.7                        |      |     |     |     |     |  |

|                 |                                         | power down<br>mode                                                                          | 25                         | S3               | 100                 | 0.9                       | 1.0                       | 1.3                       | 1.7                        | 2.5                        |      |     |     |     |     |  |

|                 |                                         | mode                                                                                        | 20                         | S3               | 160                 | 1.0                       | 1.2                       | 1.4                       | 1.7                        | 2.5                        |      |     |     |     |     |  |

|                 |                                         | nt in mode<br>p                                                                             | 16                         | S3               | off                 | 0.3                       | 0.4                       | 0.7                       | 1.1                        | 1.9                        |      |     |     |     |     |  |

| I <sub>DD</sub> | Supply current in                       |                                                                                             | 1                          | S3               | off                 | 0.3                       | 0.3                       | 0.7                       | 1.0                        | 1.8                        |      |     |     |     |     |  |

| (continued)     | Sleep<br>mode                           |                                                                                             | 100                        | S1               | 200                 | 2.6                       | 2.7                       | 3.0                       | 3.4                        | 4.2                        | mA   |     |     |     |     |  |

|                 | (continued)                             | All peripherals                                                                             | 84                         | S2               | 168                 | 2.2                       | 2.3                       | 2.6                       | 3.0                        | 3.8                        |      |     |     |     |     |  |

|                 |                                         | disabled,<br>External clock,                                                                | 64                         | S3               | 128                 | 1.8                       | 1.9                       | 2.1                       | 2.5                        | 3.3                        |      |     |     |     |     |  |

|                 |                                         | PLL ON, Flash                                                                               | 50                         | S3               | 100                 | 1.5                       | 1.6                       | 1.9                       | 2.2                        | 3.1                        |      |     |     |     |     |  |

|                 |                                         | memory ON                                                                                   | 25                         | S3               | 100                 | 1.2                       | 1.4                       | 1.6                       | 2.0                        | 2.8                        |      |     |     |     |     |  |

|                 |                                         | All peripherals<br>disabled, HSI,<br>PLL OFF, Flash<br>memory in Deep<br>power down<br>mode |                            |                  |                     |                           |                           | 20                        | S3                         | 160                        | 1.3  | 1.4 | 1.7 | 2.0 | 2.8 |  |

|                 |                                         |                                                                                             | 16                         | S3               | off                 | 0.6                       | 0.6                       | 1.0                       | 1.3                        | 2.0                        |      |     |     |     |     |  |

|                 |                                         |                                                                                             | 1                          | S3               | off                 | 0.5                       | 0.6                       | 0.9                       | 1.3                        | 2.0                        |      |     |     |     |     |  |

#### Table 28. Typical and maximum current consumption in Sleep mode - $V_{DD}$ = 3.6 V (continued)

1. Refer to Table 44 and RM0401 for the possible PLL VCO setting

2. Guaranteed by characterization, unless otherwise specified.

3. When the ADC is ON (ADON bit set in ADC\_CR2), an additional power consumption of 1.6 mA must be added.

4. Add an additional power consumption of 1.6 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is ON (ADON bit is set in the ADC\_CR2 register)

5. Guaranteed by tests in production.

6. Guaranteed by test in production on temperature range 7 salestypes only.

|                 | 29. Typical a                                                                                           | and maximum (                                          | Lunem                      | consul  |                             | Sleep                     | moue -                    |                          |                            | onunue                     | eu)  |  |

|-----------------|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------|----------------------------|---------|-----------------------------|---------------------------|---------------------------|--------------------------|----------------------------|----------------------------|------|--|

|                 |                                                                                                         |                                                        | £                          | Voltage | PLL                         | Тур                       |                           | Ма                       | ax <sup>(2)</sup>          |                            |      |  |

| Symbol          | Parameter                                                                                               | Conditions                                             | f <sub>HCLK</sub><br>(MHz) | scale   | VCO<br>(MHz) <sup>(1)</sup> | Т <sub>А</sub> =<br>25 °С | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 ℃ | T <sub>A</sub> =<br>105 °C | T <sub>A</sub> =<br>125 °C | Unit |  |

|                 |                                                                                                         | All peripherals disabled,                              | All peripherals            | 100     | S1                          | 200                       | 1.9                       | 2,0                      | 2,4                        | 2,7                        | 3.5  |  |

|                 |                                                                                                         |                                                        | 84                         | S2      | 168                         | 1.6                       | 1,7                       | 2,0                      | 2,4                        | 3.2                        |      |  |

|                 |                                                                                                         | External clock,<br>PLL ON, Flash                       | 64                         | S3      | 128                         | 1.1                       | 1,2                       | 1,5                      | 1,9                        | 2.7                        |      |  |

|                 | memo                                                                                                    | memory in                                              | 50                         | S3      | 100                         | 0.9                       | 1,0                       | 1,3                      | 1,7                        | 2.5                        |      |  |

|                 |                                                                                                         | Deep power<br>down mode                                | 25                         | S3      | 100                         | 0.7                       | 0,8                       | 1,1                      | 1,4                        | 2.2                        |      |  |

|                 | All periphera<br>disabled, HS<br>PLL OFF, Flax<br>memory in<br>Supply Deep powe<br>current in down mode | down mode                                              | 20                         | S3      | 160                         | 0.8                       | 0,8                       | 1,2                      | 1,5                        | 2.3                        |      |  |

|                 |                                                                                                         | All peripherals                                        | 16                         | S3      | off                         | 0.3                       | 0,4                       | 0,7                      | 1,0                        | 1.8                        |      |  |

| I <sub>DD</sub> |                                                                                                         | PLL OFF, Flash<br>memory in<br>Deep power<br>down mode | 1                          | S3      | off                         | 0.2                       | 0,3                       | 0,6                      | 1,0                        | 1.8                        |      |  |

| (continued)     | Sleep<br>mode                                                                                           |                                                        | 100                        | S1      | 200                         | 2.3                       | 2,4                       | 2,9                      | 3,3                        | 4.0                        | mA   |  |

|                 | (continued)                                                                                             | All peripherals                                        | 84                         | S2      | 168                         | 2.0                       | 2,1                       | 2,4                      | 2,8                        | 3.6                        |      |  |

|                 |                                                                                                         | disabled,<br>External clock,                           | 64                         | S3      | 128                         | 1.5                       | 1,6                       | 1,9                      | 2,3                        | 3.1                        |      |  |

|                 |                                                                                                         | PLL ON, Flash                                          | 50                         | S3      | 100                         | 1.3                       | 1,4                       | 1,7                      | 2,0                        | 2.8                        |      |  |

|                 |                                                                                                         | memory ON                                              | 25                         | S3      | 100                         | 1.0                       | 1,1                       | 1,4                      | 1,7                        | 2.5                        |      |  |

|                 | All peripherals                                                                                         |                                                        | 20                         | S3      | 160                         | 1.0                       | 1,2                       | 1,5                      | 1,8                        | 2.6                        |      |  |

|                 |                                                                                                         | 16                                                     | S3                         | off     | 0.6                         | 0,6                       | 1,0                       | 1,4                      | 2.1                        |                            |      |  |

|                 | disabled, HSI,<br>PLL OFF, Flash<br>memory in<br>Deep power<br>down mode                                |                                                        | 1                          | S3      | off                         | 0.5                       | 0,6                       | 0,9                      | 1,3                        | 2.0                        |      |  |

#### Table 29. Typical and maximum current consumption in Sleep mode - $V_{DD}$ = 1.7 V (continued)

1. Refer to Table 44 and RM0401 for the possible PLL VCO setting

2. Guaranteed by characterization, unless otherwise specified.

3. When the ADC is ON (ADON bit set in ADC\_CR2), an additional power consumption of 1.6 mA must be added.

4. Add an additional power consumption of 1.6 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is ON (ADON bit is set in the ADC\_CR2 register)

|                      |                                                    |                                          | Тур                       |                                          |                           | Мах                                       |                                           |      |

|----------------------|----------------------------------------------------|------------------------------------------|---------------------------|------------------------------------------|---------------------------|-------------------------------------------|-------------------------------------------|------|

| Symbol               | Conditions                                         |                                          | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>25 °C <sup>(1)</sup> | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C <sup>(1)</sup> | T <sub>A</sub> =<br>125 °C <sup>(1)</sup> | Unit |

|                      | Flash in Stop mode,                                | Main regulator usage                     | 105.6                     | 117.1                                    | 385.1                     | 665.7                                     | 1270.0                                    |      |

|                      | all oscillators OFF,<br>no independent<br>watchdog | Low power regulator usage                | 39.5                      | 48.7                                     | 287.5                     | 548.4                                     | 1070.0                                    |      |

| I <sub>DD_STOP</sub> | Flash in Deep power                                | Main regulator usage                     | 77.8                      | 87.5                                     | 351.3                     | 630.1                                     | 1222.0                                    | μA   |

|                      | down mode, all<br>oscillators OFF, no              | Low power regulator usage                | 11.0                      | 20.0                                     | 254.2                     | 512.0                                     | 1006.0                                    |      |

|                      | independent<br>watchdog                            | Low power low voltage<br>regulator usage | 6.1                       | 13.6                                     | 217.0                     | 442.5                                     | 941.0                                     |      |

1. Guaranteed by characterization.

|                      | Conditions                                                                |                                          | Тур                       | Тур Мах                                  |                           |                                           |                                           |      |

|----------------------|---------------------------------------------------------------------------|------------------------------------------|---------------------------|------------------------------------------|---------------------------|-------------------------------------------|-------------------------------------------|------|

| Symbol               |                                                                           |                                          | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>25 °C <sup>(1)</sup> | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C <sup>(1)</sup> | T <sub>A</sub> =<br>125 °C <sup>(1)</sup> | Unit |

|                      | Flash in Stop mode,<br>all oscillators OFF,<br>no independent<br>watchdog | Main regulator usage                     | 108.6                     | 126 <sup>(2)</sup>                       | 392.8                     | 675.4 <sup>(3)</sup>                      | 1280.0 <sup>(2)</sup>                     |      |

|                      |                                                                           | Low power regulator usage                | 41.03                     | 50.31 <sup>(2)</sup>                     | 290.9                     | 554.2 <sup>(3)</sup>                      | 1077.0 <sup>(2)</sup>                     |      |

| I <sub>DD_STOP</sub> | Flash in Deep power                                                       | Main regulator usage                     | 80.32                     | 94.0 <sup>(2)</sup>                      | 357.0                     | 639.5 <sup>(3)</sup>                      | 1232.0 <sup>(2)</sup>                     | μA   |

| oscillato<br>indep   | down mode, all<br>oscillators OFF, no                                     | Low power regulator usage                | 12.41                     | 21.5 <sup>(2)</sup>                      | 258.1                     | 518.1 <sup>(3)</sup>                      | 1010.0 <sup>(2)</sup>                     |      |

|                      | independent Low po                                                        | Low power low voltage<br>regulator usage | 7.53                      | 15.2 <sup>(2)</sup>                      | 221.6                     | 449.2 <sup>(3)</sup>                      | 947.0 <sup>(2)</sup>                      |      |

| Table 31. Typical | and maximum curren | t consumption ir | n Stop mode - V <sub>DD</sub> =3.6 V |

|-------------------|--------------------|------------------|--------------------------------------|

|-------------------|--------------------|------------------|--------------------------------------|

1. Guaranteed by characterization.

2. Guaranteed by tests in production.

3. Guaranteed by test in production on temperature range 7 salestypes only.

| Table 32, Typica | I and maximum curren | t consumption in Sta | ndby mode - V <sub>DD</sub> = 1.7 V |

|------------------|----------------------|----------------------|-------------------------------------|

| Tuble of Typica  |                      | t oonsumption in otu |                                     |

|                                                   |           |                                          | Тур                       |                                          |                           | Max                                       |                                           |      |

|---------------------------------------------------|-----------|------------------------------------------|---------------------------|------------------------------------------|---------------------------|-------------------------------------------|-------------------------------------------|------|

| Symbol                                            | Parameter | Conditions                               | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>25 °C <sup>(1)</sup> | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C <sup>(1)</sup> | T <sub>A</sub> =<br>125 °C <sup>(1)</sup> | Unit |

| Supply current<br>I <sub>DD STBY</sub> in Standby |           | Low-speed oscillator (LSE)<br>and RTC ON | 2.1                       | 2.9                                      | 6.5                       | 18.2                                      | 60.0                                      | μA   |

|                                                   | mode      | RTC and LSE OFF                          | 1.2                       | 1.9                                      | 5.5                       | 17.1                                      | 59.0                                      |      |

1. Guaranteed by characterization, unless otherwise specified.

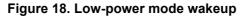

#### 6.3.7 Wakeup time from low-power modes

The wakeup times given in *Table 37* are measured starting from the wakeup event trigger up to the first instruction executed by the CPU:

- For Stop or Sleep modes: the wakeup event is WFE.

- WKUP (PA0) pin is used to wakeup from Standby, Stop and Sleep modes.

All timings are derived from tests performed under ambient temperature and  $V_{DD}$ =3.3 V.

The LSE high-power mode allows to cover a wider range of possible crystals but with a cost of higher power consumption.

| Symbol                              | Parameter                               | Conditions                    | Min | Тур  | Max  | Unit              |  |  |

|-------------------------------------|-----------------------------------------|-------------------------------|-----|------|------|-------------------|--|--|

| R <sub>F</sub>                      | Feedback resistor                       | -                             | -   | 18.4 | -    | MΩ                |  |  |

| I <sub>DD</sub>                     | LSE current consumption                 | Low-power mode<br>(default)   | -   | -    | 1    | μA                |  |  |

|                                     |                                         | High-drive mode               | -   | -    | 3    |                   |  |  |

| G <sub>m</sub> _crit_max            |                                         | Startup, low-power<br>mode    | -   | -    | 0.56 | μA/V              |  |  |

|                                     | Maximum critical crystal g <sub>m</sub> | Startup, high-drive<br>mode   | -   | -    | 1.50 | μ <sub>Α</sub> νν |  |  |

| t <sub>SU(LSE)</sub> <sup>(2)</sup> | startup time                            | V <sub>DD</sub> is stabilized | -   | 2    | -    | s                 |  |  |

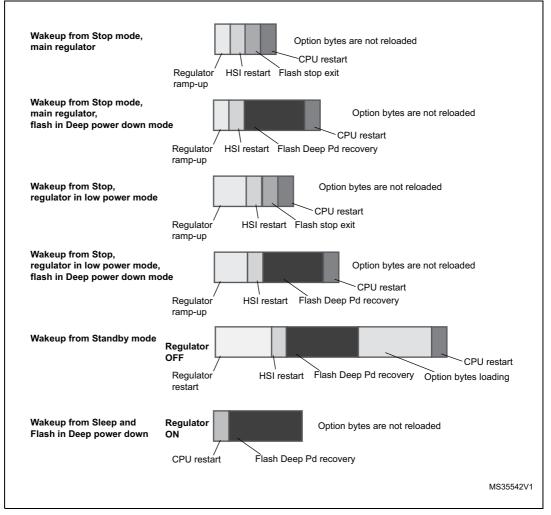

Table 41. LSE oscillator characteristics (f<sub>LSE</sub> = 32.768 kHz) <sup>(1)</sup>

1. Guaranteed by design.

t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is guaranteed by characterization. It is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

*Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

For information about the LSE high-power mode, refer to the reference manual RM0401.

#### Figure 22. Typical application with a 32.768 kHz crystal

#### 6.3.9 Internal clock source characteristics

The parameters given in *Table 42* and *Table 43* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 15*.

#### High-speed internal (HSI) RC oscillator

| Symbol                              | Parameter                           | Conditions                              |                                      | Min | Тур | Max | Unit |

|-------------------------------------|-------------------------------------|-----------------------------------------|--------------------------------------|-----|-----|-----|------|

| f <sub>HSI</sub>                    | Frequency                           | -                                       |                                      | -   | 16  | -   | MHz  |

|                                     |                                     | User-trimmed<br>register <sup>(2)</sup> | d with the RCC_CR                    | -   | -   | 1   | %    |

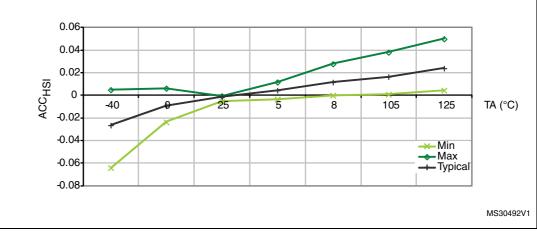

| ACC <sub>HSI</sub>                  | Accuracy of the HSI oscillator      |                                         | $T_A = -40$ to 125 °C <sup>(3)</sup> | -8  | -   | 5.5 | %    |

| _                                   |                                     | Factory-<br>calibrated                  | $T_A = -10$ to 85 °C <sup>(3)</sup>  | -4  | -   | 4   | %    |

|                                     |                                     |                                         | $T_A = 25 \ ^{\circ}C^{(4)}$         | -1  | -   | 1   | %    |

| t <sub>su(HSI)</sub> <sup>(2)</sup> | HSI oscillator<br>startup time      | -                                       |                                      | -   | 2.2 | 4   | μs   |

| I <sub>DD(HSI)</sub> <sup>(2)</sup> | HSI oscillator<br>power consumption |                                         | -                                    |     | 60  | 80  | μA   |

| Table 42 | HSI | oscillator | characteristics | (1) |

|----------|-----|------------|-----------------|-----|

|          |     | USCIIIALUI | Characteristics |     |

1. V<sub>DD</sub> = 3.3 V, T<sub>A</sub> = –40 to 125 °C unless otherwise specified.

2. Guaranteed by design.

3. Guaranteed by characterization.

4. Factory calibrated non-soldered parts.

<sup>1.</sup> Guaranteed by characterization.

| Symbol                               | Parameter                     | Condition                                | S                  | Min          | Тур  | Max          | Unit |

|--------------------------------------|-------------------------------|------------------------------------------|--------------------|--------------|------|--------------|------|

| +                                    | PLL lock time                 | VCO freq = 100 N                         | /Hz                | 75           | -    | 200          |      |

| t <sub>LOCK</sub>                    |                               | VCO freq = 432 N                         | /Hz                | 100          | -    | 300          | μs   |

|                                      |                               |                                          | RMS                | -            | 25   | -            |      |

| Jitter <sup>(3)</sup>                | Cycle-to-cycle jitter         | System clock                             | peak<br>to<br>peak | -            | ±150 | -            |      |

| JILLEI                               | Period Jitter                 | 100 MHz                                  | RMS                | -            | 15   | -            | ps   |

|                                      |                               |                                          | peak<br>to<br>peak | -            | ±200 | -            |      |

| I <sub>DD(PLL)</sub> <sup>(4)</sup>  | PLL power consumption on VDD  | VCO freq = 100 MHz<br>VCO freq = 432 MHz |                    | 0.15<br>0.45 | -    | 0.40<br>0.75 |      |

| I <sub>DDA(PLL)</sub> <sup>(4)</sup> | PLL power consumption on VDDA | VCO freq = 100 M<br>VCO freq = 432 M     |                    | 0.30<br>0.55 | -    | 0.40<br>0.85 | mA   |

#### Table 44. Main PLL characteristics (continued)

1. Take care of using the appropriate division factor M to obtain the specified PLL input clock values. The M factor is shared between PLL and PLLI2S.

2. Guaranteed by design.

3. The use of two PLLs in parallel could degraded the Jitter up to +30%.

4. Guaranteed by characterization.

#### 6.3.14 Absolute maximum ratings (electrical sensitivity)

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

#### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the JESD22-A114/C101 standard.

| Symbol                | Ratings                                                  | Conditions                                                 |          | Class | Maximum<br>value <sup>(2)</sup> | Unit |

|-----------------------|----------------------------------------------------------|------------------------------------------------------------|----------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge<br>voltage (human body<br>model) | T <sub>A</sub> = +25 °C conforming to<br>ANSI/JEDEC JS-001 |          | 2     | 2000                            |      |

|                       | Electrostatic discharge                                  |                                                            | UFQFPN48 | 4     | 500                             |      |

|                       |                                                          | $T_A = +25$ °C conforming to<br>ANSI/ESD STM5.3.1          | WLCSP36  | 3     | 250                             | V    |

| V <sub>ESD(CDM)</sub> | voltage (charge device                                   |                                                            | LQFP48   | 4     | 500                             |      |

|                       | model)                                                   |                                                            | LQPF64   | 4     | 500                             | 1    |

|                       |                                                          |                                                            | UFBGA64  | TBD   | TBD                             | 1    |

#### Table 52. ESD absolute maximum ratings<sup>(1)</sup>

1. TBD stands for "to be defined".

2. Guaranteed by characterization.

#### Static latchup

Two complementary static tests are required on six parts to assess the latchup performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latchup standard.

#### Table 53. Electrical sensitivities

| Symbol | Parameter             | Conditions                                    | Class      |

|--------|-----------------------|-----------------------------------------------|------------|

| LU     | Static latch-up class | $T_A = +125 \text{ °C conforming to JESD78A}$ | II level A |

#### 6.3.15 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard, 3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

DocID028094 Rev 5

| f (kHz)                | I2C_CCR value           |

|------------------------|-------------------------|

| f <sub>SCL</sub> (kHz) | R <sub>P</sub> = 4.7 kΩ |

| 400                    | 0x8019                  |

| 300                    | 0x8021                  |

| 200                    | 0x8032                  |

| 100                    | 0x0096                  |

| 50                     | 0x012C                  |

| 20                     | 0x02EE                  |

| Table 62 | SCL freque |               | 42 MHz Vaa = V        | $_{DD I2C} = 3.3 \text{ V}^{(1)(2)}$ |

|----------|------------|---------------|-----------------------|--------------------------------------|

|          | SCL HEQUE  | ICY (IPCI K1- | - 42 IVINZ., V DD - V | 12C - 3.3 V)                         |

1.  $R_P$  = External pull-up resistance,  $f_{SCL} = I^2C$  speed,

For speeds around 200 kHz, the tolerance on the achieved speed is of ±5%. For other speed ranges, the tolerance on the achieved speed ±2%. These variations depend on the accuracy of the external components used to design the application.

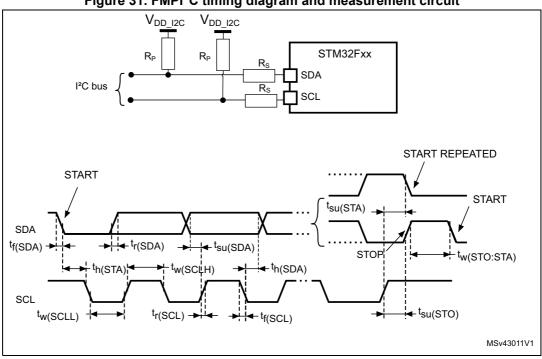

Figure 31. FMPI<sup>2</sup>C timing diagram and measurement circuit

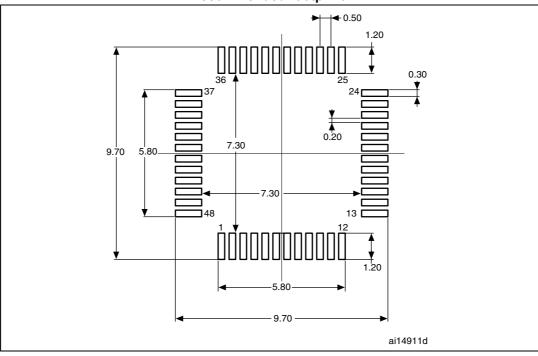

1. Dimensions are expressed in millimeters.

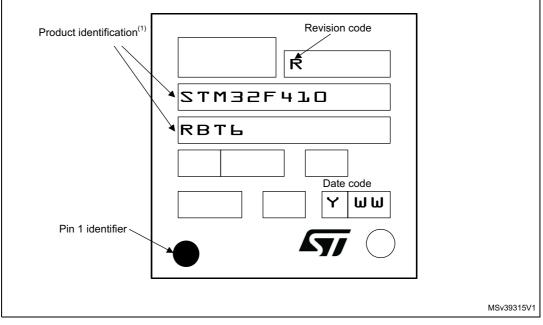

#### LQFP64 device marking

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

# Appendix A Recommendations when using the internal reset OFF

When the internal reset is OFF, the following integrated features are no longer supported:

- The integrated power-on-reset (POR)/power-down reset (PDR) circuitry is disabled.

- The brownout reset (BRO) circuitry must be disabled. By default BOR is OFF.

- The embedded programmable voltage detector (PVD) is disabled.

- VBAT functionality is no more available and VBAT pin should be connected to VDD.

# A.1 Operating conditions

#### Table 88. Limitations depending on the operating power supply range

|   | Operating<br>power supply<br>range               | ADC<br>operation                     | Maximum<br>Flash memory<br>access<br>frequency<br>with no wait<br>state<br>(f <sub>Flashmax</sub> ) | Maximum<br>Flash memory<br>access<br>frequency<br>with no wait<br>states <sup>(1) (2)</sup> | I/O operation          | Possible<br>Flash memory<br>operations        |

|---|--------------------------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------|-----------------------------------------------|

| ſ | V <sub>DD</sub> = 1.7 to<br>2.1 V <sup>(3)</sup> | Conversion<br>time up to<br>1.2 Msps | 20 MHz <sup>(4)</sup>                                                                               | 100 MHz with<br>6 wait states                                                               | No I/O<br>compensation | 8-bit erase and<br>program<br>operations only |

1. Applicable only when the code is executed from Flash memory. When the code is executed from RAM, no wait state is required.

2. Thanks to the ART Accelerator and the 128-bit Flash memory, the number of wait states given here does not impact the execution speed from Flash memory since the ART Accelerator allows to achieve a performance equivalent to 0 wait state program execution.

V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V, with the use of an external power supply supervisor (refer to Section 3.15.1: Internal reset ON).

4. Prefetch is not available. Refer to AN3430 application note for details on how to adjust performance and power.