Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 100MHz                                                                |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT          |

| Number of I/O              | 50                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 32K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                           |

| Data Converters            | A/D 16x12b; D/A 1x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | 64-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f410rbt6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of tables

| Table 1.  | Device summary                                                                               | . 1 |

|-----------|----------------------------------------------------------------------------------------------|-----|

| Table 2.  | STM32F410x8/B features and peripheral counts                                                 | 13  |

| Table 3.  | Embedded bootloader interfaces                                                               | 20  |

| Table 4.  | Regulator ON/OFF and internal power supply supervisor availability                           | 22  |

| Table 5.  | Timer feature comparison.                                                                    | 25  |

| Table 6.  | Comparison of I2C analog and digital filters                                                 | 28  |

| Table 7.  | USART feature comparison                                                                     |     |

| Table 8.  | Legend/abbreviations used in the pinout table                                                |     |

| Table 9.  | STM32F410x8/B pin definitions                                                                | 35  |

| Table 10. | Alternate function mapping                                                                   |     |

| Table 11. | STM32F410x8/B register boundary addresses                                                    | 45  |

| Table 12. | Voltage characteristics                                                                      | 51  |

| Table 13. | Current characteristics                                                                      | 52  |

| Table 14. | Thermal characteristics.                                                                     | 52  |

| Table 15. | General operating conditions                                                                 | 53  |

| Table 16. | Features depending on the operating power supply range                                       | 55  |

| Table 17. | VCAP_1 operating conditions                                                                  |     |

| Table 18. | Operating conditions at power-up / power-down (regulator ON)                                 | 56  |

| Table 19. | Operating conditions at power-up / power-down (regulator OFF)                                |     |

| Table 20. | Embedded reset and power control block characteristics.                                      | 57  |

| Table 21. | Typical and maximum current consumption, code with data processing (ART                      |     |

|           | accelerator disabled) running from SRAM - V <sub>DD</sub> = 1.7 V                            | 59  |

| Table 22. | Typical and maximum current consumption, code with data processing (ART                      |     |

|           | accelerator disabled) running from SRAM - V <sub>DD</sub> = 3.6 V                            | 60  |

| Table 23. | Typical and maximum current consumption in run mode, code with data processing               |     |

|           | (ART accelerator enabled except prefetch) running from Flash memory- V <sub>DD</sub> = 1.7 V | 61  |

| Table 24. | Typical and maximum current consumption in run mode, code with data processing               |     |

|           | (ART accelerator enabled except prefetch) running from Flash memory - $V_{DD}$ = 3.6 V       | 62  |

| Table 25. | Typical and maximum current consumption in run mode, code with data processing               |     |

|           | (ART accelerator disabled) running from Flash memory - V <sub>DD</sub> = 3.6 V               | 63  |

| Table 26. | Typical and maximum current consumption in run mode, code with data processing               |     |

|           | (ART accelerator disabled) running from Flash memory - V <sub>DD</sub> = 1.7 V               | 64  |

| Table 27. | Typical and maximum current consumption in run mode, code with data processing               |     |

|           | (ART accelerator enabled with prefetch) running from Flash memory - $V_{DD}$ = 3.6 V         |     |

| Table 28. | Typical and maximum current consumption in Sleep mode - V <sub>DD</sub> = 3.6 V              |     |

| Table 29. | Typical and maximum current consumption in Sleep mode - $V_{DD}$ = 1.7 V                     |     |

| Table 30. | Typical and maximum current consumptions in Stop mode - V <sub>DD</sub> = 1.7 V              |     |

| Table 31. | Typical and maximum current consumption in Stop mode - V <sub>DD</sub> =3.6 V                |     |

| Table 32. | Typical and maximum current consumption in Standby mode - V <sub>DD</sub> = 1.7 V            |     |

| Table 33. | Typical and maximum current consumption in Standby mode - V <sub>DD</sub> = 3.6 V            | 71  |

| Table 34. | Typical and maximum current consumptions in V <sub>BAT</sub> mode                            |     |

|           | (LSE and RTC ON, LSE low- drive mode)                                                        | 71  |

| Table 35. | Switching output I/O current consumption                                                     | 74  |

| Table 36. | Peripheral current consumption                                                               | 75  |

| Table 37. | Low-power mode wakeup timings                                                                |     |

| Table 38. | High-speed external user clock characteristics.                                              |     |

| Table 39. | Low-speed external user clock characteristics                                                |     |

| Table 40. | HSE 4-26 MHz oscillator characteristics                                                      | 81  |

# 3 Functional overview

# 3.1 ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU core with embedded Flash and SRAM

The ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU processor is the latest generation of ARM processors for embedded systems. It was developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced response to interrupts.

The ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU 32-bit RISC processor features exceptional codeefficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices. The processor supports a set of DSP instructions which allow efficient signal processing and complex algorithm execution. Its single precision FPU (floating point unit) speeds up software development by using metalanguage development tools, while avoiding saturation.

The STM32F410x8/B devices are compatible with all ARM tools and software.

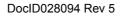

Figure 2 shows the general block diagram of the STM32F410x8/B.

Note: Cortex<sup>®</sup>-M4 with FPU is binary compatible with Cortex<sup>®</sup>-M3.

# 3.2 Adaptive real-time memory accelerator (ART Accelerator<sup>™</sup>)

The ART Accelerator<sup>™</sup> is a memory accelerator which is optimized for STM32 industrystandard ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU processors. It balances the inherent performance advantage of the ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU over Flash memory technologies, which normally requires the processor to wait for the Flash memory at higher frequencies.

To release the processor full 125 DMIPS performance at this frequency, the accelerator implements an instruction prefetch queue and branch cache, which increases program execution speed from the 128-bit Flash memory. Based on CoreMark benchmark, the performance achieved thanks to the ART Accelerator is equivalent to 0 wait state program execution from Flash memory at a CPU frequency up to 100 MHz.

# 3.3 Batch Acquisition mode (BAM)

The Batch acquisition mode allows enhanced power efficiency during data batching. It enables data acquisition through any communication peripherals directly to memory using the DMA in reduced power consumption as well as data processing while the rest of the system is in low-power mode (including the flash and ART). For example in an audio system, a smart combination of PDM audio sample acquisition and processing from the I2S directly to RAM (flash and ART<sup>TM</sup> stopped) with the DMA using BAM followed by some very short processing from flash allows to drastically reduce the power consumption of the application. A dedicated application note (AN4515) describes how to implement the STM32F410x8/B BAM to allow the best power efficiency.

## 3.20.4 Low-power timer (LPTIM1)

The devices embed one low-power timer. This timer features an independent clock and runs in Stop mode if it is clocked by LSE, LSI or by an external clock. It is able to wake up the system from Stop mode.

The low-power timer main features are the following:

- 16-bit up counter with 16-bit autoreload register

- 16-bit compare register

- Configurable output: pulse, PWM

- Continuous/ one shot mode

- Selectable software/hardware input trigger

- Selectable clock source

- Internal clock sources: LSE, LSI, HSI or APB1 clock

- External clock source over LPTIM input (working even when no internal clock source is running and used by pulse-counter applications).

- Programmable digital glitch filter

- Encoder mode

- Active in Stop mode.

#### 3.20.5 Independent watchdog

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 32 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free-running timer for application timeout management. It is hardware- or software-configurable through the option bytes.

#### 3.20.6 Window watchdog

The window watchdog is based on a 7-bit downcounter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

#### 3.20.7 SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard downcounter. It features:

- A 24-bit downcounter

- Autoreload capability

- Maskable system interrupt generation when the counter reaches 0

- Programmable clock source.

# 6.1.6 Power supply scheme

Figure 13. Power supply scheme

**Caution:** Each power supply pair (for example V<sub>DD</sub>/V<sub>SS</sub>, V<sub>DDA</sub>/V<sub>SSA</sub>) must be decoupled with filtering ceramic capacitors as shown above. These capacitors must be placed as close as possible to, or below, the appropriate pins on the underside of the PCB to ensure good operation of the device. It is not recommended to remove filtering capacitors to reduce PCB size or cost. This might cause incorrect operation of the device.

<sup>1.</sup> To connect PDR\_ON pin, refer to Section 3.15: Power supply supervisor.

| (.              |                   | rator enabled e                                               | scept p                    |         |              | <u> </u>                  | 1 10511 1                 |                           |                            | - 1.7 V                    |      |

|-----------------|-------------------|---------------------------------------------------------------|----------------------------|---------|--------------|---------------------------|---------------------------|---------------------------|----------------------------|----------------------------|------|

|                 |                   |                                                               | £                          | Voltage | PLL<br>VCO   | Тур                       | Max <sup>(2)</sup>        |                           |                            |                            |      |

| Symbol F        | Parameter         | Conditions                                                    | f <sub>HCLK</sub><br>(MHz) | scale   | (MHz)<br>(1) | Т <sub>А</sub> =<br>25 °С | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | T <sub>A</sub> =<br>125 °C | Unit |

|                 |                   |                                                               | 100                        | S1      | 200          | 15.7                      | 16.5                      | 16.5                      | 16.9                       | 17.8                       |      |

|                 |                   |                                                               | 84                         | S2      | 168          | 12.7                      | 13.3                      | 13.4                      | 13.8                       | 14.6                       |      |

|                 |                   | External clock,                                               | 64                         | S3      | 128          | 8.8                       | 9.3                       | 9.4                       | 9.7                        | 10.6                       |      |

|                 |                   | all peripherals<br>enabled <sup>(3)(4)</sup>                  | 50                         | S3      | 100          | 7.0                       | 7.4                       | 7.5                       | 7.8                        | 8.6                        |      |

|                 |                   |                                                               | 25                         | S3      | 100          | 3.9                       | 4.1                       | 4.3                       | 4.7                        | 5.6                        |      |

|                 |                   |                                                               | 20                         | S3      | 160          | 3.4                       | 3.6                       | 3.8                       | 4.2                        | 5.1                        |      |

|                 |                   | HSI, PLL OFF,<br>all peripherals<br>enabled <sup>(3)(4)</sup> | 16                         | S3      | off          | 2.4                       | 2.5                       | 2.8                       | 3.2                        | 4.1                        |      |

| I               | Supply current in |                                                               | 1                          | S3      | off          | 0.6                       | 0.7                       | 1.0                       | 1.4                        | 2.3                        | mA   |

| I <sub>DD</sub> | Run mode          |                                                               | 100                        | S1      | 200          | 10.1                      | 10.7                      | 10.8                      | 11.2                       | 12.0                       |      |

|                 |                   | External clock,                                               | 84                         | S2      | 168          | 8.2                       | 8.6                       | 8.7                       | 9.1                        | 10.0                       |      |

|                 |                   |                                                               | 64                         | S3      | 128          | 5.7                       | 6.1                       | 6.2                       | 6.6                        | 7.4                        |      |

|                 |                   | all peripherals<br>disabled <sup>(3)</sup>                    | 50                         | S3      | 100          | 4.6                       | 4.9                       | 5.0                       | 5.4                        | 6.3                        |      |

|                 |                   |                                                               | 25                         | S3      | 100          | 2.6                       | 2.8                       | 3.0                       | 3.4                        | 4.3                        |      |

|                 |                   |                                                               | 20                         | S3      | 160          | 2.4                       | 2.5                       | 2.8                       | 3.1                        | 4.0                        |      |

|                 |                   | HSI, PLL OFF,                                                 | 16                         | S3      | off          | 1.7                       | 1.8                       | 2.1                       | 2.4                        | 3.3                        |      |

|                 |                   | all peripherals<br>disabled <sup>(3)</sup>                    | 1                          | S3      | off          | 0.6                       | 0.6                       | 1.0                       | 1.4                        | 2.2                        |      |

# Table 23. Typical and maximum current consumption in run mode, code with data processing (ART accelerator enabled except prefetch) running from Flash memory- V<sub>DD</sub> = 1.7 V

1. Refer to Table 44 and RM0401 for the possible PLL VCO setting

2. Guaranteed by characterization, unless otherwise specified.

3. When the ADC is ON (ADON bit set in ADC\_CR2), an additional power consumption of 1.6 mA must be added.

4. Add an additional power consumption of 1.6 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is ON (ADON bit is set in the ADC\_CR2 register)

| Symbol                                  | Parameter                 | Conditions                                                                                     | Min | Тур   | Мах   | Unit                   |

|-----------------------------------------|---------------------------|------------------------------------------------------------------------------------------------|-----|-------|-------|------------------------|

| t <sub>WUSLEEP</sub> <sup>(2)</sup>     | Wakeup from Sleep mode    | -                                                                                              | -   | 4     | 6     | CPU<br>clock<br>cycles |

| t <sub>WUSLEEPFDSM</sub> <sup>(2)</sup> |                           | Flash memory in Deep power<br>down mode                                                        | -   | -     | 40,0  |                        |

|                                         |                           | Main regulator                                                                                 | -   | 12.9  | 15.0  |                        |

|                                         | Wakeup from Stop mode,    | Main regulator, Flash memory<br>in Deep power down mode                                        | -   | 104.9 | 115.0 |                        |

|                                         | code execution from Flash | Regulator in low-power mode <sup>(3)</sup>                                                     | -   | 20.8  | 25.0  |                        |

| t <sub>WUSTOP</sub> <sup>(2)</sup>      | memory                    | Regulator in low-power mode,<br>Flash memory in Deep power<br>down mode                        | -   | 112.9 | 120.0 |                        |

|                                         | Wakeup from Stop mode,    | Main regulator, Flash memory<br>in Stop or Deep power down<br>mode                             | -   | 4.9   | 7.0   | μs                     |

|                                         | code execution from RAM   | Regulator in low-power mode,<br>Flash memory in Stop or Deep<br>power down mode <sup>(3)</sup> | -   | 12.8  | 20.0  |                        |

| twustdby <sup>(2)(4)</sup>              | Wakeup from Standby mode  | -                                                                                              | -   | 316.8 | 350.0 |                        |

|                                         | Wakeup of Flash memory    | From Flash_Stop mode                                                                           | -   | -     | 10.0  |                        |

| <sup>t</sup> wuflash                    | Wakeup of Flash memory    | From Flash Deep power down mode                                                                | -   | -     | 40.0  |                        |

| Table 37. Low | -power mode | wakeup | timings <sup>(1)</sup> |

|---------------|-------------|--------|------------------------|

|---------------|-------------|--------|------------------------|

1. Guaranteed by characterization.

2. The wakeup times are measured from the wakeup event to the point in which the application code reads the first instruction.

3. The specification is valid for wakeup from regulator in low power mode or in low power low voltage mode, since the timing difference is negligible.

4. t<sub>WUSTDBY</sub> maximum value is given at - 40 °C.

# 6.3.8 External clock source characteristics

#### High-speed external user clock generated from an external source

In bypass mode the HSE oscillator is switched off and the input pin is a standard I/O. The external clock signal has to respect the *Table 55*. However, the recommended clock input waveform is shown in *Figure 19*.

The characteristics given in *Table 38* result from tests performed using an high-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 15*.

| Symbol                              | Parameter                               | Conditions                                                            | Min | Тур | Max | Unit |  |

|-------------------------------------|-----------------------------------------|-----------------------------------------------------------------------|-----|-----|-----|------|--|

| f <sub>OSC_IN</sub>                 | Oscillator frequency                    | -                                                                     | 4   | -   | 26  | MHz  |  |

| R <sub>F</sub>                      | Feedback resistor                       | -                                                                     | -   | 200 | -   | kΩ   |  |

|                                     | HSE current consumption                 | V <sub>DD</sub> =3.3 V,<br>ESR= 30 Ω<br>C <sub>L</sub> =5 pF @25 MHz  | -   | 450 | -   |      |  |

| I <sub>DD</sub>                     |                                         | V <sub>DD</sub> =3.3 V,<br>ESR= 30 Ω<br>C <sub>L</sub> =10 pF @25 MHz | -   | 530 | -   | μΑ   |  |

| G <sub>m_crit_max</sub>             | Maximum critical crystal g <sub>m</sub> | Startup                                                               |     | -   | 1   | mA/V |  |

| t <sub>SU(HSE)</sub> <sup>(2)</sup> | Startup time                            | $V_{\text{DD}}$ is stabilized                                         | -   | 2   | -   | ms   |  |

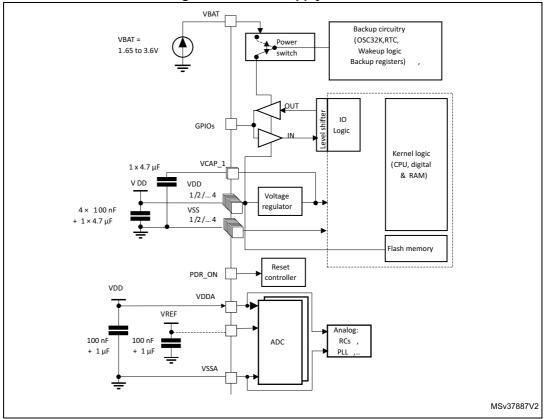

Table 40. HSE 4-26 MHz oscillator characteristics<sup>(1)</sup>

1. Guaranteed by design.

t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer

For C<sub>L1</sub> and C<sub>L2</sub>, it is recommended to use high-quality external ceramic capacitors in the 5 pF to 25 pF range (Typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 21*). C<sub>L1</sub> and C<sub>L2</sub> are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of C<sub>L1</sub> and C<sub>L2</sub>. PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing C<sub>L1</sub> and C<sub>L2</sub>.

Note:

For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

#### Figure 21. Typical application with an 8 MHz crystal

1. R<sub>EXT</sub> value depends on the crystal characteristics.

## Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 41*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

DocID028094 Rev 5

| Symbol                               | Parameter                     | Conditions                               |                    | Min          | Тур  | Max          | Unit |

|--------------------------------------|-------------------------------|------------------------------------------|--------------------|--------------|------|--------------|------|

| +                                    | PLL lock time                 | VCO freq = 100 N                         | ЛНz                | 75           | -    | 200          |      |

| t <sub>LOCK</sub>                    |                               | VCO freq = 432 N                         | ЛНz                | 100          | -    | 300          | μs   |

|                                      |                               |                                          | RMS                | -            | 25   | -            |      |

| Jitter <sup>(3)</sup>                | Cycle-to-cycle jitter         | System clock                             | peak<br>to<br>peak | -            | ±150 | -            |      |

| JILLEI                               |                               | 100 MHz                                  | RMS                | -            | 15   | -            | ps   |

|                                      | Period Jitter                 |                                          | peak<br>to<br>peak | -            | ±200 | -            |      |

| I <sub>DD(PLL)</sub> <sup>(4)</sup>  | PLL power consumption on VDD  | VCO freq = 100 MHz<br>VCO freq = 432 MHz |                    | 0.15<br>0.45 | -    | 0.40<br>0.75 |      |

| I <sub>DDA(PLL)</sub> <sup>(4)</sup> | PLL power consumption on VDDA | VCO freq = 100 M<br>VCO freq = 432 M     |                    | 0.30<br>0.55 | -    | 0.40<br>0.85 | mA   |

#### Table 44. Main PLL characteristics (continued)

1. Take care of using the appropriate division factor M to obtain the specified PLL input clock values. The M factor is shared between PLL and PLLI2S.

2. Guaranteed by design.

3. The use of two PLLs in parallel could degraded the Jitter up to +30%.

4. Guaranteed by characterization.

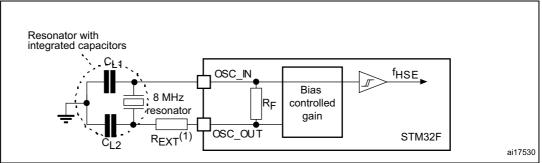

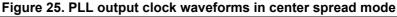

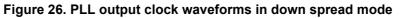

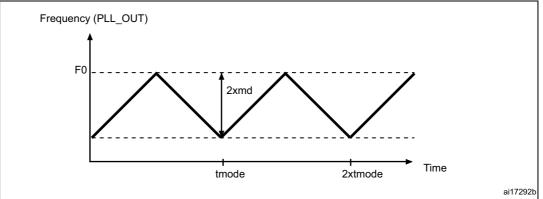

*Figure 25* and *Figure 26* show the main PLL output clock waveforms in center spread and down spread modes, where:

F0 is  $f_{PLL_OUT}$  nominal.

T<sub>mode</sub> is the modulation period.

md is the modulation depth.

#### 6.3.12 Memory characteristics

#### **Flash memory**

The characteristics are given at  $T_A = -40$  to 125 °C unless otherwise specified.

The devices are shipped to customers with the Flash memory erased.

Table 46. Flash memory characteristics

| Symbol          | Parameter      | Conditions                                  | Min | Тур | Мах | Unit |

|-----------------|----------------|---------------------------------------------|-----|-----|-----|------|

|                 |                | Write / Erase 8-bit mode, $V_{DD}$ = 1.7 V  | -   | 5   | -   |      |

| I <sub>DD</sub> | Supply current | Write / Erase 16-bit mode, $V_{DD}$ = 2.1 V | -   | 8   | -   | mA   |

|                 |                | Write / Erase 32-bit mode, $V_{DD}$ = 3.3 V | -   | 12  | -   |      |

In noisy environments, it is recommended to avoid pin exposition to disturbances. The pins showing a middle range robustness are PA14 and PA15.

As a consequence, it is recommended to add a serial resistor (1 k $\Omega$  maximum) located as close as possible to the MCU pins exposed to noise (connected to tracks longer than 50 mm on PCB).

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and pregualification tests in relation with the EMC level requested for his application.

Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

#### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

#### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application, executing EEMBC code, is running. This emission test is compliant with SAE IEC61967-2 standard which specifies the test board and the pin loading.

| Symbol           | Parameter  | Conditions                                              | Monitored<br>frequency band | Max vs.<br>[f <sub>HSE</sub> /f <sub>CPU</sub> ]<br>8/100 MHz | Unit |

|------------------|------------|---------------------------------------------------------|-----------------------------|---------------------------------------------------------------|------|

|                  |            |                                                         | 0.1 to 30 MHz               | 10                                                            |      |

| \$               | Peak level | $V_{DD}$ = 3.6 V, T <sub>A</sub> = 25 °C, conforming to | 30 to 130 MHz               | 11                                                            | dBµV |

| S <sub>EMI</sub> | Feak level | IEC61967-2                                              | 130 MHz to 1 GHz            | 5                                                             |      |

|                  |            |                                                         | SAE EMI Level               | 2.5                                                           | -    |

#### Table 51. EMI characteristics for LQFP64

## 6.3.14 Absolute maximum ratings (electrical sensitivity)

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

#### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the JESD22-A114/C101 standard.

| Symbol                | Ratings                                                  | Conditions                                                 |          | Class | Maximum<br>value <sup>(2)</sup> | Unit |

|-----------------------|----------------------------------------------------------|------------------------------------------------------------|----------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge<br>voltage (human body<br>model) | T <sub>A</sub> = +25 °C conforming to<br>ANSI/JEDEC JS-001 |          | 2     | 2000                            |      |

|                       |                                                          |                                                            | UFQFPN48 | 4     | 500                             |      |

|                       | Electrostatic discharge                                  |                                                            | WLCSP36  | 3     | 250                             | V    |

| V <sub>ESD(CDM)</sub> | voltage (charge device                                   | $T_A = +25$ °C conforming to<br>ANSI/ESD STM5.3.1          | LQFP48   | 4     | 500                             |      |

|                       | model)                                                   |                                                            | LQPF64   | 4     | 500                             |      |

|                       |                                                          |                                                            | UFBGA64  | TBD   | TBD                             | 1    |

#### Table 52. ESD absolute maximum ratings<sup>(1)</sup>

1. TBD stands for "to be defined".

2. Guaranteed by characterization.

## Static latchup

Two complementary static tests are required on six parts to assess the latchup performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latchup standard.

#### Table 53. Electrical sensitivities

| Symbol | Parameter             | Conditions                                    | Class      |

|--------|-----------------------|-----------------------------------------------|------------|

| LU     | Static latch-up class | $T_A = +125 \text{ °C conforming to JESD78A}$ | II level A |

## 6.3.15 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard, 3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

DocID028094 Rev 5

| Symbol                         | Param                                                 | eter                                                          | Conditions                                                        | Min                                         | Тур                                | Мах  | Unit |

|--------------------------------|-------------------------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------|---------------------------------------------|------------------------------------|------|------|

|                                | FT, TC and NRST level voltage <sup>(5)</sup>          | I/O input high                                                | 1.7 V≤V <sub>DD</sub> ≤3.6 V                                      | 0.7V <sub>DD</sub> <sup>(1)</sup>           | -                                  | -    |      |

| V <sub>IH</sub>                | BOOT0 I/O input I                                     | nigh level                                                    | 1.75 V≤V <sub>DD</sub> ≤3.6 V,<br>-40 °C≤T <sub>A</sub> ≤ 125 °C  | 0.17V <sub>DD</sub> +<br>0.7 <sup>(2)</sup> |                                    | _    | V    |

|                                | voltage                                               |                                                               | 1.7 V≤V <sub>DD</sub> ≤3.6 V,<br>0 °C≤T <sub>A</sub> ≤ 125 °C     | 0.7 <sup>(2)</sup>                          | -                                  | -    |      |

|                                | FT, TC and NRST hysteresis                            | I/O input                                                     | 1.7 V≤V <sub>DD</sub> ≤3.6 V                                      | -                                           | 10% V <sub>DD</sub> <sup>(3)</sup> | -    | V    |

| V <sub>HYS</sub>               | BOOT0 I/O input I                                     | nysteresis                                                    | 1.75 V≤V <sub>DD</sub> ≤3.6 V,<br>- 40 °C≤T <sub>A</sub> ≤ 125 °C |                                             | 100                                | _    | mV   |

|                                | lysteresis                                            | 1.7 V⊴V <sub>DD</sub> ≤3.6 V,<br>0 °C⊴T <sub>A</sub> ≤ 125 °C |                                                                   | 100                                         |                                    | IIIV |      |

|                                | I/O input leakage current <sup>(4)</sup>              |                                                               | $V_{SS} \leq V_{IN} \leq V_{DD}$                                  | -                                           | -                                  | Ŧ    |      |

| l <sub>lkg</sub>               | I/O FT/TC input le                                    | akage current                                                 | V <sub>IN</sub> = 5 V                                             | -                                           | -                                  | 3    | μA   |

| R <sub>PU</sub>                | Weak pull-up<br>equivalent<br>resistor <sup>(6)</sup> | All pins<br>except for<br>PA10<br>(OTG_FS_ID)                 | V <sub>IN</sub> = V <sub>SS</sub>                                 | 30                                          | 40                                 | 50   |      |

|                                |                                                       | PA10<br>(OTG_FS_ID)                                           | -                                                                 | 7                                           | 10                                 | 14   | kΩ   |

| R <sub>PD</sub>                | Weak pull-down<br>R <sub>PD</sub> equivalent          | All pins<br>except for<br>PA10<br>(OTG_FS_ID)                 | $V_{IN} = V_{DD}$                                                 | 30                                          | 40                                 | 50   | N22  |

|                                | resistor <sup>(7)</sup> PA10 (OTG_FS_ID)              |                                                               | -                                                                 | 7                                           | 10                                 | 14   |      |

| C <sub>IO</sub> <sup>(8)</sup> | I/O pin capacitanc                                    | e                                                             | -                                                                 | -                                           | 5                                  | -    | pF   |

Table 55. I/O static characteristics (continued)

1. Guaranteed by tests in production.

2. Guaranteed by design.

3. With a minimum of 200 mV.

4. Leakage could be higher than the maximum value, if negative current is injected on adjacent pins, Refer to Table 54: I/O current injection susceptibility

To sustain a voltage higher than VDD +0.3 V, the internal pull-up/pull-down resistors must be disabled. Leakage could be higher than the maximum value, if negative current is injected on adjacent pins. Refer to Table 54: I/O current injection susceptibility

6. Pull-up resistors are designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is minimum (~10% order).

7. Pull-down resistors are designed with a true resistance in series with a switchable NMOS. This NMOS contribution to the series resistance is minimum (~10% order).

8. Hysteresis voltage between Schmitt trigger switching levels. Guaranteed by characterization.

All I/Os are CMOS and TTL compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters. The coverage of these requirements for FT and TC I/Os is shown in *Figure* 27.

DocID028094 Rev 5

# I<sup>2</sup>S interface characteristics

Unless otherwise specified, the parameters given in *Table 65* for the I<sup>2</sup>S interface are derived from tests performed under the ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 15*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>

Refer to Section 6.3.16: I/O port characteristics for more details on the input/output alternate function characteristics (CK, SD, WS).

| Symbol                 | Parameter                      | Conditions                             | Min    | Max                   | Unit |

|------------------------|--------------------------------|----------------------------------------|--------|-----------------------|------|

| f <sub>MCK</sub>       | I2S Main clock output          | -                                      | 256x8K | 256xFs <sup>(2)</sup> | MHz  |

| f                      | 128 clock froguency            | Master data: 32 bits                   | -      | 64xFs                 | MHz  |

| f <sub>СК</sub>        | I2S clock frequency            | Slave data: 32 bits                    | -      | 64xFs                 |      |

| D <sub>CK</sub>        | I2S clock frequency duty cycle | Slave receiver                         | 30     | 70                    | %    |

| t <sub>v(WS)</sub>     | WS valid time                  | Master mode                            | 0      | 7                     |      |

| t <sub>h(WS)</sub>     | WS hold time                   | Master mode                            | 1.5    | -                     |      |

| t <sub>su(WS)</sub>    | WS setup time                  | Slave mode                             | 1.5    | -                     |      |

| t <sub>h(WS)</sub>     | WS hold time                   | Slave mode                             | 3      | -                     |      |

| t <sub>su(SD_MR)</sub> | Data input setup time          | Master receiver                        | 1      | -                     |      |

| $t_{su(SD\_SR)}$       |                                | Slave receiver                         | 2.5    | -                     | ns   |

| t <sub>h(SD_MR)</sub>  | Data input hold time           | Master receiver                        | 7      | -                     | 115  |

| t <sub>h(SD_SR)</sub>  | Data input noid time           | Slave receiver                         | 2.5    | -                     |      |

| t <sub>v(SD_ST)</sub>  | Data output valid time         | Slave transmitter (after enable edge)  | -      | 20                    |      |

| t <sub>v(SD_MT)</sub>  |                                | Master transmitter (after enable edge) | -      | 6                     |      |

| t <sub>h(SD_ST)</sub>  | Data output hold time          | Slave transmitter (after enable edge)  | 8      | -                     |      |

| t <sub>h(SD_MT)</sub>  |                                | Master transmitter (after enable edge) | 2      | -                     |      |

| Table 65. I <sup>2</sup> S dv | namic characteristics <sup>(1)</sup> |

|-------------------------------|--------------------------------------|

|-------------------------------|--------------------------------------|

1. Guaranteed by characterization.

2. The maximum value of 256xFs is 50 MHz (APB1 maximum frequency).

Note: Refer to the I2S section of RM0401 reference manual for more details on the sampling frequency ( $F_{S}$ ).

$f_{MCK}$ ,  $f_{CK}$ , and  $D_{CK}$  values reflect only the digital peripheral behavior. The values of these parameters might be slightly impacted by the source clock precision.  $D_{CK}$  depends mainly on the value of ODD bit. The digital contribution leads to a minimum value of (I2SDIV/(2\*I2SDIV+ODD) and a maximum value of (I2SDIV+ODD)/(2\*I2SDIV+ODD).  $F_S$  maximum value is supported for each mode/condition.

| Symbol                            | Parameter                                                                          | Conditions                                         | Min | Тур | Max  | Unit |

|-----------------------------------|------------------------------------------------------------------------------------|----------------------------------------------------|-----|-----|------|------|

|                                   |                                                                                    | 12-bit resolution<br>Single ADC                    | -   | -   | 2    | Msps |

| f <sub>S</sub> <sup>(2)</sup>     | Sampling rate<br>(f <sub>ADC</sub> = 30 MHz, and<br>t <sub>S</sub> = 3 ADC cycles) | 12-bit resolution<br>Interleave Dual ADC<br>mode   | -   | -   | 3.75 | Msps |

|                                   |                                                                                    | 12-bit resolution<br>Interleave Triple ADC<br>mode | -   | -   | 6    | Msps |

| I <sub>VREF+</sub> <sup>(2)</sup> | ADC V <sub>REF</sub> DC current<br>consumption in conversion<br>mode               | -                                                  | -   | 300 | 500  | μA   |

| I <sub>VDDA</sub> <sup>(2)</sup>  | ADC V <sub>DDA</sub> DC current<br>consumption in conversion<br>mode               | -                                                  | -   | 1.6 | 1.8  | mA   |

1. V<sub>DDA</sub> minimum value of 1.7 V is possible with the use of an external power supply supervisor (refer to Section 3.15.2: Internal reset OFF).

2. Guaranteed by characterization.

3.  $V_{REF+}$  is internally connected to  $V_{DDA}$  and  $V_{REF-}$  is internally connected to  $V_{SSA}$ .

4.  $R_{ADC}$  maximum value is given for V<sub>DD</sub>=1.7 V, and minimum value for V<sub>DD</sub>=3.3 V.

5. For external triggers, a delay of  $1/f_{PCLK2}$  must be added to the latency specified in Table 66.

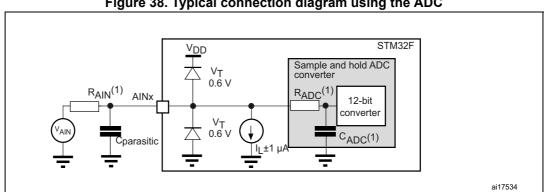

#### Equation 1: R<sub>AIN</sub> max formula

$$\mathsf{R}_{\mathsf{AIN}} = \frac{(k-0.5)}{\mathsf{f}_{\mathsf{ADC}} \times \mathsf{C}_{\mathsf{ADC}} \times \mathsf{In}(2^{\mathsf{N}+2})} - \mathsf{R}_{\mathsf{ADC}}$$

The formula above (*Equation 1*) is used to determine the maximum external impedance allowed for an error below 1/4 of LSB. N = 12 (from 12-bit resolution) and k is the number of sampling periods defined in the ADC\_SMPR1 register.

| Symbol | Parameter                    | Test conditions                                             | Тур | Max <sup>(2)</sup> | Unit |

|--------|------------------------------|-------------------------------------------------------------|-----|--------------------|------|

| ET     | Total unadjusted error       | f <sub>ADC</sub> =18 MHz<br>V <sub>DDA</sub> = 1.7 to 3.6 V | ±3  | ±4                 |      |

| EO     | Offset error                 |                                                             | ±2  | ±3                 |      |

| EG     | Gain error                   | V <sub>REF</sub> = 1.7 to 3.6 V                             | ±1  | ±3                 | LSB  |

| ED     | Differential linearity error | V <sub>DDA</sub> –V <sub>REF</sub> < 1.2 V                  | ±1  | ±2                 |      |

| EL     | Integral linearity error     |                                                             | ±2  | ±3                 |      |

| Table 67. | ADC | accuracy | at f <sub>ADC</sub> = | 18 | MHz <sup>(1)</sup> |

|-----------|-----|----------|-----------------------|----|--------------------|

|-----------|-----|----------|-----------------------|----|--------------------|

1. Better performance could be achieved in restricted  $V_{\text{DD}}$ , frequency and temperature ranges.

2. Guaranteed by characterization.

| Symbol | Parameter                    | Test conditions                                                                | Тур  | Max <sup>(2)</sup> | Unit |

|--------|------------------------------|--------------------------------------------------------------------------------|------|--------------------|------|

| ET     | Total unadjusted error       | f <sub>ADC</sub> = 30 MHz,<br>R <sub>AIN</sub> < 10 kΩ                         | ±2   | ±5                 |      |

| EO     | Offset error                 |                                                                                | ±1.5 | ±2.5               |      |

| EG     | Gain error                   | V <sub>DDA</sub> = 2.4 to 3.6 V,                                               | ±1.5 | ±4                 | LSB  |

| ED     | Differential linearity error | V <sub>REF</sub> = 1.7 to 3.6 V,<br>V <sub>DDA</sub> –V <sub>REF</sub> < 1.2 V | ±1   | ±2                 |      |

| EL     | Integral linearity error     |                                                                                | ±1.5 | ±3                 |      |

# Table 68. ADC accuracy at $f_{ADC} = 30 \text{ MHz}^{(1)}$

1. Better performance could be achieved in restricted  $\mathrm{V}_{\mathrm{DD}},$  frequency and temperature ranges.

2. Guaranteed by characterization.

| Symbol | Parameter                    | Test conditions                                                     | Тур | Max <sup>(2)</sup> | Unit |  |

|--------|------------------------------|---------------------------------------------------------------------|-----|--------------------|------|--|

| ET     | Total unadjusted error       | f <sub>ADC</sub> =36 MHz,<br>V <sub>DDA</sub> = 2.4 to 3.6 V,       | ±4  | ±7                 |      |  |

| EO     | Offset error                 |                                                                     | ±2  | ±3                 |      |  |

| EG     | Gain error                   | V <sub>DDA</sub> = 2.4 to 3.6 V,<br>V <sub>REF</sub> = 1.7 to 3.6 V | ±3  | ±6                 | LSB  |  |

| ED     | Differential linearity error | $V_{DDA} - V_{REF} < 1.2 V$                                         | ±2  | ±3                 |      |  |

| EL     | Integral linearity error     |                                                                     | ±3  | ±6                 |      |  |

# Table 69. ADC accuracy at $f_{ADC} = 36 \text{ MHz}^{(1)}$

1. Better performance could be achieved in restricted  $V_{\text{DD}}$ , frequency and temperature ranges.

2. Guaranteed by characterization.

| Symbol | Parameter                            | Test conditions                                                               | Min  | Тур  | Max | Unit |

|--------|--------------------------------------|-------------------------------------------------------------------------------|------|------|-----|------|

| ENOB   | Effective number of bits             | $f_{ADC}$ =18 MHz<br>$V_{DDA} = V_{REF+}$ = 1.7 V<br>Input Frequency = 20 KHz | 10.3 | 10.4 | -   | bits |

| SINAD  | Signal-to-noise and distortion ratio |                                                                               | 64   | 64.2 | -   |      |

| SNR    | Signal-to-noise ratio                |                                                                               | 64   | 65   | -   | dB   |

| THD    | Total harmonic distortion            | Temperature = 25 °C                                                           | -    | -72  | -67 |      |

1. Guaranteed by characterization.

| Symbol | Parameter                            | Test conditions                                                           | Min  | Тур  | Max | Unit |

|--------|--------------------------------------|---------------------------------------------------------------------------|------|------|-----|------|

| ENOB   | Effective number of bits             | f <sub>ADC</sub> = 36 MHz<br>V <sub>DDA</sub> = V <sub>REF+</sub> = 3.3 V | 10.6 | 10.8 | -   | bits |

| SINAD  | Signal-to noise and distortion ratio |                                                                           | 66   | 67   | -   |      |

| SNR    | Signal-to noise ratio                | Input Frequency = 20 KHz                                                  | 64   | 68   | -   | dB   |

| THD    | Total harmonic distortion            | Temperature = 25 °C                                                       | -    | -72  | -70 |      |

1. Guaranteed by characterization.

Figure 38. Typical connection diagram using the ADC

1. Refer to Table 66 for the values of  $R_{AIN}$ ,  $R_{ADC}$  and  $C_{ADC}$ .

$C_{parasitic}$  represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 5 pF). A high  $C_{parasitic}$  value downgrades conversion accuracy. To remedy this,  $f_{ADC}$  should be reduced. 2.

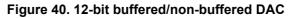

# 6.3.24 DAC electrical characteristics

| Table 77. DAC characteristics     |                                                                                          |                            |                                                                    |                    |     |                                |      |                                                                                                                                                                                                                      |  |  |

|-----------------------------------|------------------------------------------------------------------------------------------|----------------------------|--------------------------------------------------------------------|--------------------|-----|--------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Symbol                            | Parameter                                                                                | Cond                       | itions                                                             | Min                | Тур | Мах                            | Unit | Comments                                                                                                                                                                                                             |  |  |

| V <sub>DDA</sub>                  | Analog supply voltage                                                                    | -                          |                                                                    | 1.7 <sup>(1)</sup> | -   | 3.6                            | V    | -                                                                                                                                                                                                                    |  |  |

| V <sub>REF+</sub>                 | Reference supply voltage                                                                 | -                          |                                                                    | 1.7 <sup>(1)</sup> | -   | 3.6                            | V    | V <sub>REF+</sub> ⊴V <sub>DDA</sub>                                                                                                                                                                                  |  |  |

| $V_{SSA}$                         | Ground                                                                                   | -                          |                                                                    | 0                  | -   | 0                              | V    | -                                                                                                                                                                                                                    |  |  |

| R <sub>LOAD</sub> <sup>(2)</sup>  | Resistive load                                                                           | DAC<br>output<br>buffer ON | $\begin{array}{c} R_{LOAD}\\ connected\\ to \ V_{SSA} \end{array}$ | 5                  | -   | -                              | kΩ   | -                                                                                                                                                                                                                    |  |  |

|                                   |                                                                                          |                            | R <sub>LOAD</sub><br>connected<br>to V <sub>DDA</sub>              | 25                 | -   | -                              | kΩ   | -                                                                                                                                                                                                                    |  |  |

| R <sub>O</sub> <sup>(2)</sup>     | Impedance output<br>with buffer OFF                                                      | -                          |                                                                    | -                  | -   | 15                             | kΩ   | When the buffer is OFF, the Minimum resistive load between DAC_OUT and $V_{SS}$ to have a 1% accuracy is 1.5 M $\Omega$                                                                                              |  |  |

| C <sub>LOAD</sub> <sup>(2)</sup>  | Capacitive load                                                                          | -                          |                                                                    | -                  | -   | 50                             | pF   | Maximum capacitive load at DAC_OUT pin (when the buffer is ON).                                                                                                                                                      |  |  |

| DAC_OUT<br>min <sup>(2)</sup>     | Lower DAC_OUT<br>voltage with buffer<br>ON                                               | -                          |                                                                    | 0.2                | -   | -                              | v    | It gives the maximum output<br>excursion of the DAC.<br>It corresponds to 12-bit input                                                                                                                               |  |  |

| DAC_OUT<br>max <sup>(2)</sup>     | Higher DAC_OUT<br>voltage with buffer<br>ON                                              |                            | -                                                                  | -                  | -   | V <sub>DDA</sub><br>- 0.2      | V    | code (0x0E0) to (0xF1C) at<br>V <sub>REF+</sub> = 3.6 V and (0x1C7)<br>to (0xE38) at V <sub>REF+</sub> = 1.7 V                                                                                                       |  |  |

| DAC_OUT<br>min <sup>(2)</sup>     | Lower DAC_OUT<br>voltage with buffer<br>OFF                                              |                            | -                                                                  | -                  | 0.5 | -                              | mV   | It gives the maximum output excursion of the DAC.                                                                                                                                                                    |  |  |

| DAC_OUT<br>max <sup>(2)</sup>     | Higher DAC_OUT<br>voltage with buffer<br>OFF                                             |                            | -                                                                  | -                  | -   | V <sub>REF+</sub><br>_<br>1LSB | V    |                                                                                                                                                                                                                      |  |  |

| I <sub>VREF+</sub> <sup>(4)</sup> | DAC DC V <sub>REF</sub><br>current<br>consumption in<br>quiescent mode<br>(Standby mode) | -                          |                                                                    | -                  | 170 | 240                            | μA   | With no load, worst code<br>(0x800) at $V_{REF+} = 3.6$ V in<br>terms of DC consumption on<br>the inputs<br>With no load, worst code<br>(0xF1C) at $V_{REF+} = 3.6$ V in<br>terms of DC consumption on<br>the inputs |  |  |

|                                   |                                                                                          |                            |                                                                    | -                  | 50  | 75                             |      |                                                                                                                                                                                                                      |  |  |

## Table 77. DAC characteristics

#### **Electrical characteristics**

| Table 77. DAC characteristics (continued) |                                                                                          |            |     |     |      |      |                                                       |  |

|-------------------------------------------|------------------------------------------------------------------------------------------|------------|-----|-----|------|------|-------------------------------------------------------|--|

| Symbol                                    | Parameter                                                                                | Conditions | Min | Тур | Мах  | Unit | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |  |

| t <sub>WAKEUP</sub> <sup>(4)</sup>        | Wakeup time from<br>off state (Setting<br>the ENx bit in the<br>DAC Control<br>register) | -          | -   | 6.5 | 10   | μs   |                                                       |  |

| PSRR+ <sup>(2)</sup>                      | Power supply<br>rejection ratio (to<br>V <sub>DDA</sub> ) (static DC<br>measurement)     | -          | -   | 67  | - 40 | dB   | No R <sub>LOAD</sub> , C <sub>LOAD</sub> = 50 pF      |  |

#### Table 77. DAC characteristics (continued)

1. V<sub>DDA</sub> minimum value of 1.7 V is obtained with the use of an external power supply supervisor (refer to *Section 3.15.2: Internal reset OFF*).

2. Guaranteed by design.

3. The quiescent mode corresponds to a state where the DAC maintains a stable output level to ensure that no dynamic consumption occurs.

4. Guaranteed based on test during characterization.

1. The DAC integrates an output buffer that can be used to reduce the output impedance and to drive external loads directly without the use of an external operational amplifier. The buffer can be bypassed by configuring the BOFFx bit in the DAC\_CR register.

# 6.3.25 RTC characteristics

| Table | 78. | RTC | characteristics |

|-------|-----|-----|-----------------|

|       |     |     |                 |

| Symbol | Parameter                                  | Conditions                                          | Min | Max |

|--------|--------------------------------------------|-----------------------------------------------------|-----|-----|

| -      | f <sub>PCLK1</sub> /RTCCLK frequency ratio | Any read/write operation<br>from/to an RTC register | 4   | -   |

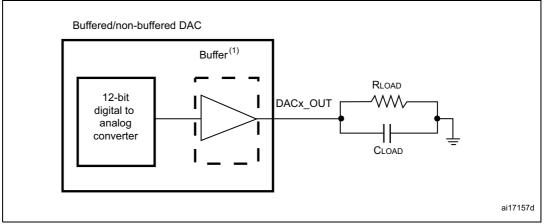

# 7.3 LQFP48 package information

Figure 47. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline

1. Drawing is not to scale.

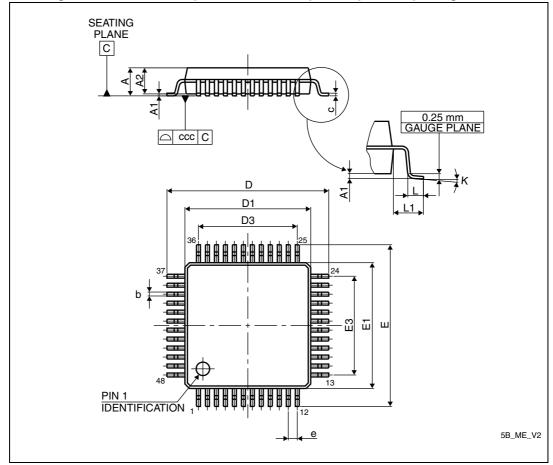

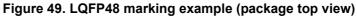

#### LQFP48 device marking

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.