Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 100MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT            |

| Number of I/O              | 23                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 32K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                             |

| Data Converters            | A/D 4x12b; D/A 1x12b                                                    |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 36-UFBGA, WLCSP                                                         |

| Supplier Device Package    | 36-WLCSP                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f410tby6tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

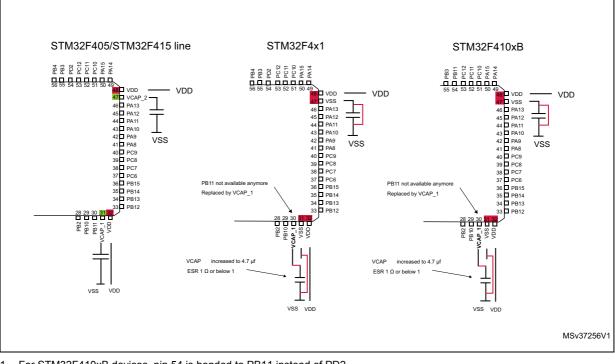

## 2.1 Compatibility with STM32F4 series

The STM32F410x8/B are fully software and feature compatible with the STM32F4 series (STM32F42x, STM32F401, STM32F43x, STM32F41x, STM32F405 and STM32F407)

The STM32F410x8/B can be used as drop-in replacement of the other STM32F4 products but some slight changes have to be done on the PCB board.

1. For STM32F410xB devices, pin 54 is bonded to PB11 instead of PD2.

and the HSE crystal oscillators are disabled. The voltage regulator can also be put either in normal or in low-power mode.

The RTC and the low-power timer (LPTIM1) can remain active in Stop mode. They can consequently be used to wake up the device from this mode.

The device can be woken up from the Stop mode by any of the EXTI line (the EXTI line source can be one of the 16 external lines, the PVD output, LPTIM1, the RTC alarm/ wakeup/ tamper/ time stamp events).

#### • Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.2 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, the SRAM and register contents are lost except for registers in the backup domain when selected.

The device exits the Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on the WKUP pin, or an RTC alarm/ wakeup/ tamper/time stamp event occurs.

Standby mode is not supported when the embedded voltage regulator is bypassed and the 1.2 V domain is controlled by an external power.

## 3.19 V<sub>BAT</sub> operation

The VBAT pin allows to power the device  $V_{BAT}$  domain from an external battery, an external super-capacitor, or from  $V_{DD}$  when no external battery and an external super-capacitor are present.

$V_{BAT}$  operation is activated when  $V_{DD}$  is not present.

The VBAT pin supplies the RTC and the backup registers.

Note: When the microcontroller is supplied from VBAT, external interrupts and RTC alarm/events do not exit it from  $V_{BAT}$  operation. When PDR\_ON pin is not connected to  $V_{DD}$  (internal Reset OFF), the  $V_{BAT}$  functionality is no more available and VBAT pin should be connected to  $V_{DD}$ .

## 3.20 Timers and watchdogs

The devices embed one advanced-control timer, four general purpose timers, one low power timer, two watchdog timers and one SysTick timer.

All timer counters can be frozen in debug mode.

*Table 5* compares the features of the advanced-control and general-purpose timers.

## 3.20.1 Advanced-control timers (TIM1)

The advanced-control timer (TIM1) can be seen as three-phase PWM generator multiplexed on 4 independent channels. It has complementary PWM outputs with programmable inserted dead times. It can also be considered as a complete general-purpose timer. Its 4 independent channels can be used for:

- Input capture

- Output compare

- PWM generation (edge- or center-aligned modes)

- One-pulse mode output

If configured as standard 16-bit timers, it has the same features as the general-purpose TIMx timers. If configured as a 16-bit PWM generator, it has full modulation capability (0-100%).

The advanced-control timer can work together with the TIMx timers via the Timer Link feature for synchronization or event chaining.

TIM1 supports independent DMA request generation.

#### **3.20.2** General-purpose timers (TIM5, TIM9 and TIM11)

There are three synchronizable general-purpose timers embedded in the STM32F410x8/B (see *Table 5* for differences).

#### • TIM5

The STM32F410x8/B devices includes a full-featured general-purpose timer, TIM5. TIM5 timer is based on a 32-bit auto-reload up/downcounter and a 16-bit prescaler. It features four independent channels for input capture/output compare, PWM or one-pulse mode output.

TIM5 can operate in conjunction with the other general-purpose timers and TIM1 advanced-control timer via the Timer Link feature for synchronization or event chaining.

TIM5 general-purpose timer can be used to generate PWM output.

All TIM5 channels have independent DMA request generation. They are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 4 hall-effect sensors.

#### • TIM9 and TIM11

These timers are based on a 16-bit auto-reload upcounter and a 16-bit prescaler. TIM11 features one independent channel, whereas TIM9 has two independent channels for input capture/output compare, PWM or one-pulse mode output. They can be synchronized with TIM5 full-featured general-purpose timer or used as simple time bases.

### 3.20.3 Basic timer (TIM6)

This timer is mainly used for DAC triggering and waveform generation. It can also operate as generic 16-bit timers.

TIM6 supports independent DMA request generation.

## 3.21 Inter-integrated circuit interface (I<sup>2</sup>C)

The devices feature up to three  $I^2C$  bus interfaces which can operate in multimaster and slave modes:

- One I<sup>2</sup>C interface supports the Standard mode (up to 100 kHz), Fast-mode (up to 400 kHz) modes and Fast-mode plus (up to 1 MHz).

- Two I<sup>2</sup>C interfaces support the Standard mode (up to 100 KHz) and the Fast mode (up to 400 KHz). Their frequency can be increased up to 1 MHz. For more details on the complete solution, refer to the nearest STMicroelectronics sales office.

All I<sup>2</sup>C interfaces features 7/10-bit addressing mode and 7-bit addressing mode (as slave) and embed a hardware CRC generation/verification.

They can be served by DMA and they support SMBus 2.0/PMBus.

The devices also include programmable analog and digital noise filters (see *Table 6*).

|                                     | Analog filter | Digital filter                                         |

|-------------------------------------|---------------|--------------------------------------------------------|

| Pulse width of<br>suppressed spikes | ≥ 50 ns       | Programmable length from 1 to 15 I2C peripheral clocks |

Table 6. Comparison of I2C analog and digital filters

# 3.22 Universal synchronous/asynchronous receiver transmitters (USART)

The devices embed three universal synchronous/asynchronous receiver transmitters (USART1, USART2 and USART6).

These three interfaces provide asynchronous communication, IrDA SIR ENDEC support, multiprocessor communication mode, single-wire half-duplex communication mode and have LIN Master/Slave capability. The USART1 and USART6 interfaces are able to communicate at speeds of up to 12.5 Mbit/s. The USART2 interface communicates at up to 6.25 bit/s.

USART1 and USART2 also provide hardware management of the CTS and RTS signals, Smart Card mode (ISO 7816 compliant) and SPI-like communication capability. All interfaces can be served by the DMA controller.

## 3.26 General-purpose input/outputs (GPIOs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain, with or without pull-up or pull-down), as input (floating, with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions. All GPIOs are high-current-capable and have speed selection to better manage internal noise, power consumption and electromagnetic emission.

The I/O configuration can be locked if needed by following a specific sequence in order to avoid spurious writing to the I/Os registers.

Fast I/O handling allowing maximum I/O toggling up to 100 MHz.

## 3.27 Analog-to-digital converter (ADC)

One 12-bit analog-to-digital converter is embedded and shares up to 16 external channels, performing conversions in the single-shot or scan mode. In scan mode, automatic conversion is performed on a selected group of analog inputs.

The ADC can be served by the DMA controller. An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

To synchronize A/D conversion and timers, the ADCs could be triggered by any of TIM1 or TIM5 timer.

## 3.28 Temperature sensor

The temperature sensor has to generate a voltage that varies linearly with temperature. The conversion range is between 1.7 V and 3.6 V. The temperature sensor is internally connected to the ADC\_IN18 input channel which is used to convert the sensor output voltage into a digital value. Refer to the reference manual for additional information.

As the offset of the temperature sensor varies from chip to chip due to process variation, the internal temperature sensor is mainly suitable for applications that detect temperature changes instead of absolute temperatures. If an accurate temperature reading is needed, then an external temperature sensor part should be used.

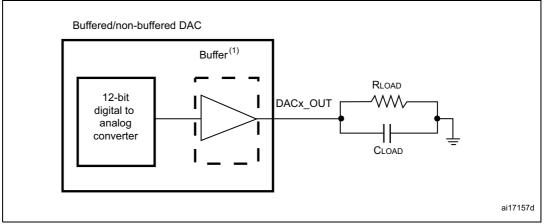

## 3.29 Digital-to-analog converter (DAC)

One 12-bit buffered DAC channel can be used to convert a digital signal into an analog voltage signal output. The chosen design structure is composed of integrated resistor strings and an amplifier in inverting configuration.

This digital interface supports the following features:

- 8-bit or 12-bit monotonic output

- Buffer offset calibration (factory and user trimming)

- Left or right data alignment in 12-bit mode

- Synchronized update capability

- Noise-wave generation

|                 |                   | accelerator di                                                | sableu)                    | running |              |                           | <u>• DD -</u>             | J.U V                     |                            |                            |      |

|-----------------|-------------------|---------------------------------------------------------------|----------------------------|---------|--------------|---------------------------|---------------------------|---------------------------|----------------------------|----------------------------|------|

|                 |                   |                                                               | £                          | Voltage | PLL<br>VCO   | Тур                       |                           | Ма                        | ax <sup>(2)</sup>          |                            |      |

| Symbol          | Parameter         | Conditions                                                    | f <sub>HCLK</sub><br>(MHz) | scale   | (MHz)<br>(1) | Т <sub>А</sub> =<br>25 °С | Т <sub>А</sub> =<br>25 °С | Т <sub>А</sub> =<br>85 °С | T <sub>A</sub> =<br>105 °C | T <sub>A</sub> =<br>125 °C | Unit |

|                 |                   |                                                               | 100                        | S1      | 200          | 17.7                      | 19.1 <sup>(5)</sup>       | 19.3                      | 19.7 <sup>(6)</sup>        | 20.5 <sup>(5)</sup>        |      |

|                 |                   |                                                               | 84                         | S2      | 168          | 14.4                      | 15.3 <sup>(5)</sup>       | 15.7                      | 16.0 <sup>(6)</sup>        | 16.8 <sup>(5)</sup>        |      |

|                 |                   | External clock, all peripherals                               | 64                         | S3      | 128          | 10.1                      | 10.6 <sup>(5)</sup>       | 11.0                      | 11.3 <sup>(6)</sup>        | 12.0 <sup>(5)</sup>        |      |

|                 |                   | enabled <sup>(3)(4)</sup>                                     | 50                         | S3      | 100          | 8.0                       | 8.4                       | 8.8                       | 9.1                        | 9.8                        |      |

|                 | Supply current in |                                                               | 25                         | S3      | 100          | 4.4                       | 4.7                       | 4.9                       | 5.2                        | 5.9                        |      |

|                 |                   |                                                               | 20                         | S3      | 160          | 3.8                       | 4.1                       | 4.3                       | 4.6                        | 5.3                        |      |

|                 |                   | HSI, PLL off,<br>all peripherals<br>enabled <sup>(3)(4)</sup> | 16                         | S3      | off          | 2.5                       | 2.6                       | 2.9                       | 3.2                        | 4.0                        |      |

| 1               |                   |                                                               | 1                          | S3      | off          | 0.4                       | 0.5                       | 0.8                       | 1.2                        | 2.0                        | mA   |

| I <sub>DD</sub> | Run mode          |                                                               | 100                        | S1      | 200          | 12.1                      | 13.1 <sup>(5)</sup>       | 13.1                      | 13.5 <sup>(6)</sup>        | 14.3 <sup>(5)</sup>        |      |

|                 |                   |                                                               | 84                         | S2      | 168          | 9.8                       | 10.6 <sup>(5)</sup>       | 10.7                      | 11.0 <sup>(6)</sup>        | 11.8 <sup>(5)</sup>        |      |

|                 |                   | External clock,<br>all peripherals                            | 64                         | S3      | 128          | 7.0                       | 7.4 <sup>(5)</sup>        | 7.6                       | 7.9 <sup>(6)</sup>         | 8.6 <sup>(5)</sup>         |      |

|                 |                   | disabled <sup>(3)</sup>                                       | 50                         | S3      | 100          | 5.6                       | 5.9                       | 6.1                       | 6.4                        | 7.2                        |      |

|                 |                   |                                                               | 25                         | S3      | 100          | 3.1                       | 3.3                       | 3.5                       | 3.9                        | 4.8                        |      |

|                 |                   |                                                               | 20                         | S3      | 160          | 2.8                       | 3.0                       | 3.2                       | 3.5                        | 4.4                        |      |

|                 |                   | HSI, PLL off, all                                             | 16                         | S3      | off          | 1.7                       | 1.8                       | 2.1                       | 2.4                        | 3.3                        |      |

|                 |                   | peripherals<br>disabled <sup>(3)</sup>                        | 1                          | S3      | off          | 0.4                       | 0.4                       | 0.7                       | 1.1                        | 1.8                        |      |

## Table 22. Typical and maximum current consumption, code with data processing (ART accelerator disabled) running from SRAM - V<sub>DD</sub> = 3.6 V

1. Refer to Table 44 and RM0401 for the possible PLL VCO setting

2. Guaranteed by characterization.

3. When the ADC is ON (ADON bit set in ADC\_CR2), an additional power consumption of 1.6 mA must be added.

4. Add an additional power consumption of 1.6 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is ON (ADON bit is set in the ADC\_CR2 register)

5. Guaranteed by tests in production.

6. Guaranteed by test in production for temperature range 7 salestypes only.

|                 |                      |                                                                                                               |                                            |     | PLL                       | Тур                       |                          |                            | ax <sup>(2)</sup>          |      |    |

|-----------------|----------------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------|-----|---------------------------|---------------------------|--------------------------|----------------------------|----------------------------|------|----|

| Symbol          | Parameter            | Conditions                                                                                                    | f <sub>HCLK</sub> Voltage<br>(MHz) scale ( | VCO | Т <sub>А</sub> =<br>25 °С | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 ℃ | T <sub>A</sub> =<br>105 °C | T <sub>A</sub> =<br>125 °C | Unit |    |

|                 |                      | All peripherals                                                                                               | 100                                        | S1  | 200                       | 7.7                       | 7,9                      | 8,8                        | 9,2                        | 10.0 |    |

|                 |                      | enabled <sup><math>(3)</math></sup> (4),                                                                      | 84                                         | S2  | 168                       | 6.2                       | 6,4                      | 7,1                        | 7,5                        | 8.3  |    |

|                 |                      | External clock,<br>PLL ON, Flash                                                                              | 64                                         | S3  | 128                       | 4.3                       | 4,5                      | 5,0                        | 5,3                        | 6.1  |    |

|                 |                      | memory in                                                                                                     | 50                                         | S3  | 100                       | 3.4                       | 3,6                      | 4,0                        | 4,4                        | 5.2  |    |

|                 |                      | Deep power<br>down mode                                                                                       | 25                                         | S3  | 100                       | 2.0                       | 2,1                      | 2,4                        | 2,7                        | 3.5  |    |

|                 | downmode             | 20                                                                                                            | S3                                         | 160 | 1.8                       | 1,9                       | 2,3                      | 2,6                        | 3.4                        |      |    |

|                 |                      | All peripherals<br>enabled <sup>(3)(4)</sup> ,<br>HSI, PLL OFF,<br>Flash memory<br>in Deep power<br>down mode | 16                                         | S3  | off                       | 1.1                       | 1,2                      | 1,5                        | 1,9                        | 2.7  |    |

| I <sub>DD</sub> | Supply<br>current in |                                                                                                               | 1                                          | S3  | off                       | 0.3                       | 0,4                      | 0,7                        | 1,0                        | 1.8  | mA |

|                 | Sleep<br>mode        |                                                                                                               | 100                                        | S1  | 200                       | 8.1                       | 8,4                      | 9,3                        | 9,7                        | 10.5 |    |

|                 |                      | All peripherals                                                                                               | 84                                         | S2  | 168                       | 6.6                       | 6,8                      | 7,5                        | 7,9                        | 8.7  |    |

|                 |                      | enabled <sup>(3)(4)</sup> ,<br>External clock,                                                                | 64                                         | S3  | 128                       | 4.7                       | 4,8                      | 5,4                        | 5,7                        | 6.5  |    |

|                 |                      | PLL ON, Flash                                                                                                 | 50                                         | S3  | 100                       | 3.8                       | 3,9                      | 4,4                        | 4,7                        | 5.5  |    |

|                 |                      | memory ON                                                                                                     | 25                                         | S3  | 100                       | 2.3                       | 2,4                      | 2,7                        | 3,1                        | 3.9  |    |

|                 |                      |                                                                                                               | 20                                         | S3  | 160                       | 2.1                       | 2,2                      | 2,6                        | 2,9                        | 3.7  | 1  |

|                 | All peripherals      | 16                                                                                                            | S3                                         | off | 1.4                       | 1,5                       | 1,8                      | 2,2                        | 3.0                        |      |    |

|                 |                      | enabled <sup>(3)(4)</sup> ,<br>HSI, PLL OFF,<br>Flash memory<br>ON                                            | 1                                          | S3  | off                       | 0.5                       | 0,6                      | 1,0                        | 1,3                        | 2.0  |    |

Table 29. Typical and maximum current consumption in Sleep mode -  $V_{DD}$  = 1.7 V

|                             |                                                    | Ту                        |       |                                          | Тур Мах                   |                                           |                                           |      |  |  |

|-----------------------------|----------------------------------------------------|---------------------------|-------|------------------------------------------|---------------------------|-------------------------------------------|-------------------------------------------|------|--|--|

| Symbol                      | Conditions                                         |                           |       | T <sub>A</sub> =<br>25 °C <sup>(1)</sup> | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C <sup>(1)</sup> | T <sub>A</sub> =<br>125 °C <sup>(1)</sup> | Unit |  |  |

|                             | Flash in Stop mode,                                | Main regulator usage      | 105.6 | 117.1                                    | 385.1                     | 665.7                                     | 1270.0                                    |      |  |  |

|                             | all oscillators OFF,<br>no independent<br>watchdog | Low power regulator usage | 39.5  | 48.7                                     | 287.5                     | 548.4                                     | 1070.0                                    |      |  |  |

| I <sub>DD_STOP</sub>        | Flash in Deep power                                | Main regulator usage      | 77.8  | 87.5                                     | 351.3                     | 630.1                                     | 1222.0                                    | μA   |  |  |

| oscillators OF<br>independe | down mode, all<br>oscillators OFF, no              | Low power regulator usage | 11.0  | 20.0                                     | 254.2                     | 512.0                                     | 1006.0                                    |      |  |  |

|                             | independent<br>watchdog regulator usage            |                           | 6.1   | 13.6                                     | 217.0                     | 442.5                                     | 941.0                                     |      |  |  |

1. Guaranteed by characterization.

|                      |                                                            |                           |                           | Мах                                      |                           |                                           |                                           |      |

|----------------------|------------------------------------------------------------|---------------------------|---------------------------|------------------------------------------|---------------------------|-------------------------------------------|-------------------------------------------|------|

| Symbol               | Co                                                         | onditions                 | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>25 °C <sup>(1)</sup> | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C <sup>(1)</sup> | T <sub>A</sub> =<br>125 °C <sup>(1)</sup> | Unit |

|                      | Flash in Stop mode,                                        | Main regulator usage      | 108.6                     | 126 <sup>(2)</sup>                       | 392.8                     | 675.4 <sup>(3)</sup>                      | 1280.0 <sup>(2)</sup>                     |      |

|                      | all oscillators OFF,<br>no independent<br>watchdog         | Low power regulator usage | 41.03                     | 50.31 <sup>(2)</sup>                     | 290.9                     | 554.2 <sup>(3)</sup>                      | 1077.0 <sup>(2)</sup>                     |      |

| I <sub>DD_STOP</sub> | Flash in Deep power                                        | Main regulator usage      | 80.32                     | 94.0 <sup>(2)</sup>                      | 357.0                     | 639.5 <sup>(3)</sup>                      | 1232.0 <sup>(2)</sup>                     | μA   |

|                      | down mode, all<br>oscillators OFF, no                      | Low power regulator usage | 12.41                     | 21.5 <sup>(2)</sup>                      | 258.1                     | 518.1 <sup>(3)</sup>                      | 1010.0 <sup>(2)</sup>                     | 1    |

|                      | independent Low power low voltage watchdog regulator usage |                           | 7.53                      | 15.2 <sup>(2)</sup>                      | 221.6                     | 449.2 <sup>(3)</sup>                      | 947.0 <sup>(2)</sup>                      |      |

| Table 31. Typical | and maximum curren | t consumption ir | n Stop mode - V <sub>DD</sub> =3.6 V |

|-------------------|--------------------|------------------|--------------------------------------|

|-------------------|--------------------|------------------|--------------------------------------|

1. Guaranteed by characterization.

2. Guaranteed by tests in production.

3. Guaranteed by test in production on temperature range 7 salestypes only.

| Table 32, Typica | I and maximum curren | t consumption in Sta | ndby mode - V <sub>DD</sub> = 1.7 V |

|------------------|----------------------|----------------------|-------------------------------------|

| Tuble of Typica  |                      | t oonsumption in otu |                                     |

| Symbol               |                              |                                          | Тур                       |                                          |                           | Max                                       |                                           |      |

|----------------------|------------------------------|------------------------------------------|---------------------------|------------------------------------------|---------------------------|-------------------------------------------|-------------------------------------------|------|

|                      | Parameter                    | Conditions                               | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>25 °C <sup>(1)</sup> | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C <sup>(1)</sup> | T <sub>A</sub> =<br>125 °C <sup>(1)</sup> | Unit |

| I <sub>DD STBY</sub> | Supply current<br>in Standby | Low-speed oscillator (LSE)<br>and RTC ON | 2.1                       | 2.9                                      | 6.5                       | 18.2                                      | 60.0                                      | μA   |

|                      | mode                         | RTC and LSE OFF                          | 1.2                       | 1.9                                      | 5.5                       | 17.1                                      | 59.0                                      |      |

1. Guaranteed by characterization, unless otherwise specified.

| Symbol | Parameter     | Conditions <sup>(1)</sup>                                                            | I/O toggling<br>frequency (f <sub>SW</sub> ) | Тур   | Unit |

|--------|---------------|--------------------------------------------------------------------------------------|----------------------------------------------|-------|------|

|        |               |                                                                                      | 2 MHz                                        | 0.05  |      |

|        |               |                                                                                      | 8 MHz                                        | 0.15  |      |

|        |               |                                                                                      | 25 MHz                                       | 0.45  |      |

|        |               | V <sub>DD</sub> = 3.3 V<br>C = C <sub>INT</sub>                                      | 50 MHz                                       | 0.85  |      |

|        |               | U = U <sub>INI</sub>                                                                 | 60 MHz                                       | 1.00  |      |

|        |               |                                                                                      | 84 MHz                                       | 1.40  |      |

|        |               |                                                                                      | 90 MHz                                       | 1.67  |      |

|        |               |                                                                                      | 2 MHz                                        | 0.10  |      |

|        |               |                                                                                      | 8 MHz                                        | 0.35  |      |

|        |               | V <sub>DD</sub> = 3.3 V                                                              | 25 MHz                                       | 1.05  |      |

|        |               | $C_{EXT} = 0 \text{ pF}$<br>C = C <sub>INT</sub> + C <sub>EXT</sub> + C <sub>S</sub> | 50 MHz                                       | 2.20  |      |

|        |               |                                                                                      | 60 MHz                                       | 2.40  |      |

|        |               |                                                                                      | 84 MHz                                       | 3.55  |      |

|        |               |                                                                                      | 90 MHz                                       | 4.23  |      |

| IDDIO  | I/O switching |                                                                                      | 2 MHz                                        | 0.20  | mA   |

|        | current       |                                                                                      | 8 MHz                                        | 0.65  |      |

|        |               | V <sub>DD</sub> = 3.3 V                                                              | 25 MHz                                       | 1.85  |      |

|        |               | C <sub>EXT</sub> =10 pF                                                              | 50 MHz                                       | 2.45  |      |

|        |               | $C = C_{INT} + C_{EXT} + C_S$                                                        | 60 MHz                                       | 4.70  |      |

|        |               |                                                                                      | 84 MHz                                       | 8.80  |      |

|        |               |                                                                                      | 90 MHz                                       | 10.47 |      |

|        |               |                                                                                      | 2 MHz                                        | 0.25  |      |

|        |               | V <sub>DD</sub> = 3.3 V                                                              | 8 MHz                                        | 1.00  |      |

|        |               | C <sub>EXT</sub> = 22 pF                                                             | 25 MHz                                       | 3.45  |      |

|        |               | $C = C_{INT} + C_{EXT} + C_{S}$                                                      | 50 MHz                                       | 7.15  |      |

|        |               |                                                                                      | 60 MHz                                       | 11.55 |      |

|        |               |                                                                                      | 2 MHz                                        | 0.32  |      |

|        |               | V <sub>DD</sub> = 3.3 V<br>C <sub>EXT</sub> = 33 pF                                  | 8 MHz                                        | 1.27  |      |

|        |               | $C = C_{INT} + C_{EXT} + C_S$                                                        | 25 MHz                                       | 3.88  |      |

|        |               |                                                                                      | 50 MHz                                       | 12.34 |      |

Table 35. Switching output I/O current consumption

1. CS is the PCB board capacitance including the pad pin. CS = 7 pF (estimated value).

| Symbol                                  | Parameter                                                     | Conditions                                                                                     | Min | Тур   | Мах   | Unit                   |  |

|-----------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----|-------|-------|------------------------|--|

| t <sub>WUSLEEP</sub> <sup>(2)</sup>     | Wakeup from Sleep mode                                        | -                                                                                              | -   | 4     | 6     | CPU<br>clock<br>cycles |  |

| t <sub>WUSLEEPFDSM</sub> <sup>(2)</sup> |                                                               | Flash memory in Deep power<br>down mode                                                        | -   | -     | 40,0  |                        |  |

|                                         |                                                               | Main regulator                                                                                 | -   | 12.9  | 15.0  |                        |  |

|                                         | Wakeup from Stop mode,                                        | Main regulator, Flash memory<br>in Deep power down mode                                        | -   | 104.9 | 115.0 |                        |  |

|                                         | code execution from Flash<br>memory<br>Wakeup from Stop mode, | Regulator in low-power mode <sup>(3)</sup>                                                     | -   | 20.8  | 25.0  |                        |  |

| t <sub>WUSTOP</sub> <sup>(2)</sup>      |                                                               | Regulator in low-power mode,<br>Flash memory in Deep power<br>down mode                        | -   | 112.9 | 120.0 |                        |  |

|                                         |                                                               | Main regulator, Flash memory<br>in Stop or Deep power down<br>mode                             | -   | 4.9   | 7.0   | μs                     |  |

|                                         | code execution from RAM                                       | Regulator in low-power mode,<br>Flash memory in Stop or Deep<br>power down mode <sup>(3)</sup> | -   | 12.8  | 20.0  |                        |  |

| twustdby <sup>(2)(4)</sup>              | Wakeup from Standby mode                                      | -                                                                                              | -   | 316.8 | 350.0 |                        |  |

|                                         | Wakeup of Flash memory                                        | From Flash_Stop mode                                                                           | -   | -     | 10.0  |                        |  |

| <sup>t</sup> wuflash                    | Wakeup of Flash memory                                        | From Flash Deep power down mode                                                                | -   | -     | 40.0  |                        |  |

| Table 37. Low | -power mode | wakeup | timings <sup>(1)</sup> |

|---------------|-------------|--------|------------------------|

|---------------|-------------|--------|------------------------|

1. Guaranteed by characterization.

2. The wakeup times are measured from the wakeup event to the point in which the application code reads the first instruction.

3. The specification is valid for wakeup from regulator in low power mode or in low power low voltage mode, since the timing difference is negligible.

4. t<sub>WUSTDBY</sub> maximum value is given at - 40 °C.

## 6.3.8 External clock source characteristics

#### High-speed external user clock generated from an external source

In bypass mode the HSE oscillator is switched off and the input pin is a standard I/O. The external clock signal has to respect the *Table 55*. However, the recommended clock input waveform is shown in *Figure 19*.

The characteristics given in *Table 38* result from tests performed using an high-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 15*.

- 1. Guaranteed by design.

- 2. The maximum programming time is measured after 100K erase operations.

- 3.  $V_{PP}$  should only be connected during programming/erasing.

| Cumhal           | Devenueter     | Conditions                                                                                                                                                                                                          | Value              | l lucit |

|------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------|

| Symbol           | Parameter      | Conditions                                                                                                                                                                                                          | Min <sup>(1)</sup> | Unit    |

| N <sub>END</sub> | Endurance      | $T_A = -40 \text{ to } +85 \text{ °C } (6 \text{ suffix versions})$<br>$T_A = -40 \text{ to } +105 \text{ °C } (7 \text{ suffix versions})$<br>$T_A = -40 \text{ to } +125 \text{ °C } (3 \text{ suffix versions})$ | 10                 | Kcycle  |

|                  |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C                                                                                                                                                                   | 30                 |         |

| tRET             | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C                                                                                                                                                                  | 10                 | Years   |

| IKET             | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 125 °C                                                                                                                                                                  | 3                  | Teals   |

|                  |                | 10 kcycle <sup>(2)</sup> at T <sub>A</sub> = 55 °C                                                                                                                                                                  | 20                 |         |

| Table 49. Flash memo | bry endurance and data retention |

|----------------------|----------------------------------|

|----------------------|----------------------------------|

1. Guaranteed by characterization.

2. Cycling performed over the whole temperature range.

## 6.3.13 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 51*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                                           | Level/<br>Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD}$ = 3.3 V, LQFP64, T <sub>A</sub> = +25 °C,<br>f <sub>HCLK</sub> = 100 MHz, conforms to<br>IEC 61000-4-2                      | 2B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD} = 3.3 \text{ V}, \text{LQFP64}, \text{T}_{A} = +25 \text{ °C},$<br>f <sub>HCLK</sub> = 100 MHz, conforms to<br>IEC 61000-4-4 | 4A              |

#### Table 50. EMS characteristics

| Symbol                         | Parameter                                | Conditions                                               | Min                                 | Max                | Unit |

|--------------------------------|------------------------------------------|----------------------------------------------------------|-------------------------------------|--------------------|------|

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin  | CMOS port <sup>(2)</sup>                                 | -                                   | 0.4                |      |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin | I <sub>IO</sub> = +8 mA<br>2.7 V ≤V <sub>DD</sub> ≤3.6 V | V <sub>DD</sub> -0.4                | -                  | V    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin  | TTL port <sup>(2)</sup>                                  | -                                   | 0.4                |      |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin | l <sub>IO</sub> =+8 mA<br>2.7 V ≤V <sub>DD</sub> ≤3.6 V  | 2.4                                 | -                  | V    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = +20 mA                                 | -                                   | 1.3 <sup>(4)</sup> | v    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin | 2.7 V ≤V <sub>DD</sub> ≤3.6 V                            | V <sub>DD</sub> -1.3 <sup>(4)</sup> | -                  | v    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = +6 mA                                  | -                                   | 0.4 <sup>(4)</sup> | v    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin | 1.8 V ≤V <sub>DD</sub> ≤3.6 V                            | V <sub>DD</sub> -0.4 <sup>(4)</sup> | -                  | v    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = +4 mA                                  | -                                   | 0.4 <sup>(5)</sup> | v    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin | 1.7 V ≤V <sub>DD</sub> ≤3.6 V                            | V <sub>DD</sub> -0.4 <sup>(5)</sup> | -                  | v    |

| Table 56 | Output volta | ge characteristics |

|----------|--------------|--------------------|

|----------|--------------|--------------------|

1. The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in *Table 13*. and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

2. TTL and CMOS outputs are compatible with JEDEC standards JESD36 and JESD52.

3. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in Table 13 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

- 4. Guaranteed by characterization results.

- 5. Guaranteed by design.

#### Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 28* and *Table 57*, respectively.

Unless otherwise specified, the parameters given in *Table 57* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 15*.

| OSPEEDRy<br>[1:0] bit<br>value <sup>(1)</sup> | Symbol                                           | Parameter                                                                       | Conditions                                               | Min | Тур | Max | Unit |

|-----------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------|----------------------------------------------------------|-----|-----|-----|------|

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD</sub> ≥ 2.70 V         | -   | -   | 4   |      |

|                                               | f <sub>max(IO)out</sub>                          | Maximum frequency <sup>(3)</sup>                                                | C <sub>L</sub> = 50 pF, V <sub>DD</sub> ≥ 1.7 V          | -   | -   | 2   | MHz  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.70 V         | -   | -   | 8   |      |

| 00                                            |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V          | -   | -   | 4   |      |

|                                               | t <sub>f(IO)out</sub> /<br>t <sub>r(IO)out</sub> | Output high to low level fall<br>time and output low to high<br>level rise time | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.7 V to 3.6 V | -   | -   | 100 | ns   |

Table 57. I/O AC characteristics<sup>(1)(2)</sup>

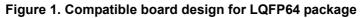

Figure 29. Recommended NRST pin protection

1. The reset network protects the device against parasitic resets.

The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in Table 58. Otherwise the reset is not taken into account by the device.

### 6.3.18 TIM timer characteristics

The parameters given in Table 59 are guaranteed by design.

Refer to Section 6.3.16: I/O port characteristics for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Symbol                 | Parameter                                                         | Conditions <sup>(3)</sup>                                | Min    | Мах                     | Unit                 |

|------------------------|-------------------------------------------------------------------|----------------------------------------------------------|--------|-------------------------|----------------------|

| t <sub>res(TIM)</sub>  |                                                                   | AHB/APBx                                                 | 1      | -                       | t <sub>TIMxCLK</sub> |

|                        | Timer resolution time                                             | prescaler=1 or 2 or 4,<br>f <sub>TIMxCLK</sub> = 100 MHz | 11.9   | -                       | ns                   |

|                        |                                                                   | AHB/APBx                                                 | 1      | -                       | t <sub>TIMxCLK</sub> |

|                        |                                                                   | prescaler>4, f <sub>TIMxCLK</sub> =<br>100 MHz           | 11.9   | -                       | ns                   |

|                        | Timer external clock                                              | f <sub>TIMxCLK</sub> = 100 MHz                           | 0      | f <sub>TIMxCLK</sub> /2 | MHz                  |

| f <sub>EXT</sub>       | frequency on CH1 to<br>CH4                                        |                                                          | 0      | 50                      | MHz                  |

| Res <sub>TIM</sub>     | Timer resolution                                                  |                                                          | -      | 16/32                   | bit                  |

| t <sub>COUNTER</sub>   | 16-bit counter clock<br>period when internal<br>clock is selected | f <sub>TIMxCLK</sub> = 100 MHz                           | 0.0119 | 780                     | μs                   |

| t <sub>MAX_COUNT</sub> | Maximum possible count<br>with 32-bit counter                     | -                                                        | -      | 65536 ×<br>65536        | t <sub>TIMxCLK</sub> |

| -                      |                                                                   | f <sub>TIMxCLK</sub> = 100 MHz                           | -      | 51.1                    | S                    |

Table 59. TIMx characteristics<sup>(1)(2)</sup>

1. TIMx is used as a general term to refer to the TIM1 to TIM11 timers.

2. Guaranteed by design.

The maximum timer frequency on APB1 is 50 MHz and on APB2 is up to 100 MHz, by setting the TIMPRE bit in the RCC\_DCKCFGR register, if APBx prescaler is 1 or 2 or 4, then TIMxCLK = HCKL, otherwise TIMxCLK >= 4x PCLKx.

## FMPI<sup>2</sup>C characteristics

The FMPI2C characteristics are described in *Table* 63.

Refer also to Section 6.3.16: I/O port characteristics for more details on the input/output alternate function characteristics (SDA and SCL).

|                                            | <b>D</b>                                                                                               | Standa | rd mode | Fast | mode | Fast+                   | mode               |      |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------|--------|---------|------|------|-------------------------|--------------------|------|

| -                                          | Parameter                                                                                              | Min    | Max     | Min  | Max  | Min                     | Max                | Unit |

| f <sub>FMPI2CC</sub>                       | F <sub>MPI2CCLK</sub> frequency                                                                        | 2      | -       | 8    | -    | 17<br>16 <sup>(2)</sup> | -                  |      |

| t <sub>w(SCLL)</sub>                       | SCL clock low time                                                                                     | 4.7    | -       | 1.3  | -    | 0.5                     | -                  |      |

| t <sub>w(SCLH)</sub>                       | SCL clock high time                                                                                    | 4.0    | -       | 0.6  | -    | 0.26                    | -                  |      |

| t <sub>su(SDA)</sub>                       | SDA setup time                                                                                         | 0.25   | -       | 0.10 | -    | 0.05                    | -                  |      |

| t <sub>H(SDA)</sub>                        | SDA data hold time                                                                                     | 0      | -       | 0    | -    | 0                       | -                  |      |

| t <sub>v(SDA,ACK)</sub>                    | Data, ACK valid time                                                                                   | -      | 3.45    | -    | 0.9  | -                       | 0.45               |      |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time                                                                                  | -      | 0.100   | -    | 0.30 | -                       | 0.12               |      |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time                                                                                  | -      | 0.30    | -    | 0.30 | -                       | 0.12               | us   |

| t <sub>h(STA)</sub>                        | Start condition hold time                                                                              | 4      | -       | 0.6  | -    | 0.26                    | -                  |      |

| t <sub>su(STA)</sub>                       | Repeated Start condition setup time                                                                    | 4.7    | -       | 0.6  | -    | 0.26                    | -                  |      |

| t <sub>su(STO)</sub>                       | Stop condition setup time                                                                              | 4      | -       | 0.6  | -    | 0.26                    | -                  |      |

| t <sub>w(STO:STA)</sub>                    | Stop to Start condition time (bus free)                                                                | 4.7    | -       | 1.3  | -    | 0.5                     | -                  |      |

| t <sub>SP</sub>                            | Pulse width of the spikes that<br>are suppressed by the<br>analog filter for standard and<br>fast mode | -      | -       | 0.05 | 0.09 | 0.05                    | 0.09               |      |

| Cb                                         | Capacitive load for each bus Line                                                                      | -      | 400     | -    | 400  | -                       | 550 <sup>(3)</sup> | pF   |

| Table 6 | 3. FMPI <sup>2</sup> C | characteristics <sup>(1)</sup> |

|---------|------------------------|--------------------------------|

|---------|------------------------|--------------------------------|

1. Guaranteed based on test during characterization.

2. When tr(SDA,SCL)<=110 ns.

3. Can be limited. Maximum supported value can be retrieved by referring to the following formulas:  $t_{r(SDA/SCL)} = 0.8473 \times R_p \times C_{load}$   $R_{p(min)} = (V_{DD} - V_{OL(max)}) / I_{OL(max)}$

ſ

٦

#### **SPI interface characteristics**

Unless otherwise specified, the parameters given in *Table 64* for the SPI interface are derived from tests performed under the ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 15*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>

Refer to Section 6.3.16: I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO for SPI).

Т

| Symbol                                       | Parameter                            | Parameter Conditions                                                             |                            | Тур               | Max                       | Unit |

|----------------------------------------------|--------------------------------------|----------------------------------------------------------------------------------|----------------------------|-------------------|---------------------------|------|

|                                              |                                      | Master full duplex/receiver mode,<br>2.7 V < V <sub>DD</sub> < 3.6 V<br>SPI1/4/5 | -                          | -                 | 42                        |      |

|                                              |                                      | Master full duplex/receiver mode,<br>3.0 V < V <sub>DD</sub> < 3.6 V<br>SPI1/4/5 | -                          | -                 | 50                        |      |

|                                              |                                      | Master transmitter mode<br>1.7 V < V <sub>DD</sub> < 3.6 V<br>SPI1/4/5           | -                          | -                 | 50                        |      |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub>    | SPI clock frequency                  | Master mode<br>1.7 V < V <sub>DD</sub> < 3.6 V<br>SPI1/2/3/4/5                   | -                          | -                 | 25                        | MHz  |

|                                              |                                      | Slave transmitter/full duplex mode $2.7 V < V_{DD} < 3.6 V$ SPI1/4/5             |                            | -                 | 38 <sup>(2)</sup>         |      |

|                                              |                                      | Slave receiver mode,<br>1.8 V < V <sub>DD</sub> < 3.6 V<br>SPI1/4/5              | -                          | -                 | 50                        |      |

|                                              |                                      | Slave mode,<br>1.8 V < V <sub>DD</sub> < 3.6 V<br>SPI1/2/3/4/5                   | -                          | -                 | 25                        |      |

| Duty(SCK)                                    | Duty cycle of SPI clock<br>frequency | Slave mode                                                                       | 30                         | 50                | 70                        | %    |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time                | Master mode, SPI presc = 2                                                       | Т <sub>РСLК</sub><br>- 1.5 | T <sub>PCLK</sub> | Т <sub>РСLК</sub><br>+1.5 | ns   |

| t <sub>su(NSS)</sub>                         | NSS setup time                       | Slave mode, SPI presc = 2                                                        | 3T <sub>PCLK</sub>         | -                 | -                         | ns   |

| t <sub>h(NSS)</sub>                          | NSS hold time                        | Slave mode, SPI presc = 2                                                        | 2T <sub>PCLK</sub>         | -                 | -                         | ns   |

| t <sub>su(MI)</sub>                          | Data input setup time                | Master mode                                                                      | 4                          | -                 | -                         | ns   |

| t <sub>su(SI)</sub>                          |                                      | Slave mode                                                                       | 2.5                        | -                 | -                         | ns   |

| t <sub>h(MI)</sub>                           | Data input hold time                 | Master mode                                                                      | 7.5                        | -                 | -                         | ns   |

| t <sub>h(SI)</sub>                           |                                      | Slave mode                                                                       | 3.5                        | -                 | -                         | ns   |

## I<sup>2</sup>S interface characteristics

Unless otherwise specified, the parameters given in *Table 65* for the I<sup>2</sup>S interface are derived from tests performed under the ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 15*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>

Refer to Section 6.3.16: I/O port characteristics for more details on the input/output alternate function characteristics (CK, SD, WS).

| Symbol                 | Parameter                      | Conditions                             | Min     | Max                   | Unit |  |

|------------------------|--------------------------------|----------------------------------------|---------|-----------------------|------|--|

| f <sub>MCK</sub>       | I2S Main clock output          | -                                      | 256x8K  | 256xFs <sup>(2)</sup> | MHz  |  |

| f                      | 128 clock froguency            | Master data: 32 bits                   | - 64xFs |                       |      |  |

| f <sub>СК</sub>        | I2S clock frequency            | Slave data: 32 bits                    | -       | 64xFs                 | MHz  |  |

| D <sub>CK</sub>        | I2S clock frequency duty cycle | Slave receiver                         | 30      | 70                    | %    |  |

| t <sub>v(WS)</sub>     | WS valid time                  | Master mode                            | 0       | 7                     |      |  |

| t <sub>h(WS)</sub>     | WS hold time                   | Master mode                            | 1.5     | -                     |      |  |

| t <sub>su(WS)</sub>    | WS setup time                  | Slave mode                             | 1.5 -   |                       | 1    |  |

| t <sub>h(WS)</sub>     | WS hold time                   | Slave mode                             | 3       | -                     |      |  |

| t <sub>su(SD_MR)</sub> | Data input setup time          | Master receiver                        | 1       | -                     |      |  |

| $t_{su(SD\_SR)}$       |                                | Slave receiver                         | 2.5     | -                     | ns   |  |

| t <sub>h(SD_MR)</sub>  | Data input hold time           | Master receiver                        | 7       | -                     | 115  |  |

| t <sub>h(SD_SR)</sub>  | Data input noid time           | Slave receiver                         | 2.5     | -                     |      |  |

| t <sub>v(SD_ST)</sub>  | Data output valid time         | Slave transmitter (after enable edge)  | -       | 20                    |      |  |

| t <sub>v(SD_MT)</sub>  |                                | Master transmitter (after enable edge) | -       | 6                     |      |  |

| t <sub>h(SD_ST)</sub>  | Data output hold time          | Slave transmitter (after enable edge)  | 8       | -                     |      |  |

| t <sub>h(SD_MT)</sub>  |                                | Master transmitter (after enable edge) | 2       | -                     |      |  |

| Table 65. I <sup>2</sup> S dv | namic characteristics <sup>(1)</sup> |

|-------------------------------|--------------------------------------|

|-------------------------------|--------------------------------------|

1. Guaranteed by characterization.

2. The maximum value of 256xFs is 50 MHz (APB1 maximum frequency).

Note: Refer to the I2S section of RM0401 reference manual for more details on the sampling frequency ( $F_{S}$ ).

$f_{MCK}$ ,  $f_{CK}$ , and  $D_{CK}$  values reflect only the digital peripheral behavior. The values of these parameters might be slightly impacted by the source clock precision.  $D_{CK}$  depends mainly on the value of ODD bit. The digital contribution leads to a minimum value of (I2SDIV/(2\*I2SDIV+ODD) and a maximum value of (I2SDIV+ODD)/(2\*I2SDIV+ODD).  $F_S$  maximum value is supported for each mode/condition.

#### **Electrical characteristics**

| Table 11. DAC characteristics (continued) |                                                                                          |            |     |     |      |      |                                                                                                                   |

|-------------------------------------------|------------------------------------------------------------------------------------------|------------|-----|-----|------|------|-------------------------------------------------------------------------------------------------------------------|

| Symbol                                    | Parameter                                                                                | Conditions | Min | Тур | Мах  | Unit | Comments                                                                                                          |

| t <sub>WAKEUP</sub> <sup>(4)</sup>        | Wakeup time from<br>off state (Setting<br>the ENx bit in the<br>DAC Control<br>register) | -          | -   | 6.5 | 10   | μs   | $C_{LOAD} \le 50$ pF, $R_{LOAD} \ge 5 \text{ k}\Omega$<br>input code between lowest<br>and highest possible ones. |

| PSRR+ <sup>(2)</sup>                      | Power supply<br>rejection ratio (to<br>V <sub>DDA</sub> ) (static DC<br>measurement)     | -          | -   | 67  | - 40 | dB   | No R <sub>LOAD</sub> , C <sub>LOAD</sub> = 50 pF                                                                  |

#### Table 77. DAC characteristics (continued)

1. V<sub>DDA</sub> minimum value of 1.7 V is obtained with the use of an external power supply supervisor (refer to *Section 3.15.2: Internal reset OFF*).

2. Guaranteed by design.

3. The quiescent mode corresponds to a state where the DAC maintains a stable output level to ensure that no dynamic consumption occurs.

4. Guaranteed based on test during characterization.

1. The DAC integrates an output buffer that can be used to reduce the output impedance and to drive external loads directly without the use of an external operational amplifier. The buffer can be bypassed by configuring the BOFFx bit in the DAC\_CR register.

## 6.3.25 RTC characteristics

| Table | 78. | RTC | characteristics |

|-------|-----|-----|-----------------|

|       |     |     |                 |

| Symbol | Parameter                                  | Conditions                                          | Min | Max |

|--------|--------------------------------------------|-----------------------------------------------------|-----|-----|

| -      | f <sub>PCLK1</sub> /RTCCLK frequency ratio | Any read/write operation<br>from/to an RTC register | 4   | -   |

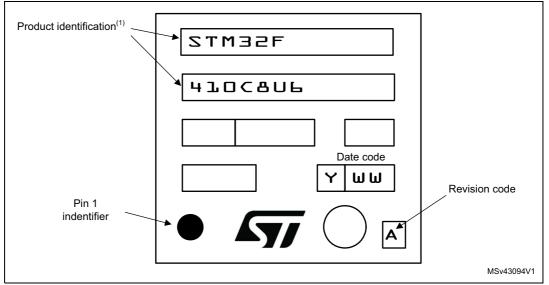

#### LQFP48 device marking

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

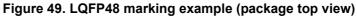

## 7.5 **UFBGA64** package information

Figure 53. UFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch ultra profile fine pitch ball grid array

1. Drawing is not to scale.

| Table 84. UFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch ultra profile fine pitch ball grid |  |  |  |  |  |

|----------------------------------------------------------------------------------------|--|--|--|--|--|

| array                                                                                  |  |  |  |  |  |

| nackage mechanical data                                                                |  |  |  |  |  |

| package mechanical data |             |       |       |                       |        |        |  |

|-------------------------|-------------|-------|-------|-----------------------|--------|--------|--|

| Symbol                  | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |

| Symbol                  | Min         | Тур   | Max   | Min                   | Тур    | Мах    |  |

| А                       | 0.460       | 0.530 | 0.600 | 0.0181                | 0.0209 | 0.0236 |  |

| A1                      | 0.050       | 0.080 | 0.110 | 0.0020                | 0.0031 | 0.0043 |  |

| A2                      | 0.400       | 0.450 | 0.500 | 0.0157                | 0.0177 | 0.0197 |  |

| A3                      | 0.080       | 0.130 | 0.180 | 0.0031                | 0.0051 | 0.0071 |  |

| A4                      | 0.270       | 0.320 | 0.370 | 0.0106                | 0.0126 | 0.0146 |  |

| b                       | 0.170       | 0.280 | 0.330 | 0.0067                | 0.0110 | 0.0130 |  |

| D                       | 4.850       | 5.000 | 5.150 | 0.1909                | 0.1969 | 0.2028 |  |

| D1                      | 3.450       | 3.500 | 3.550 | 0.1358                | 0.1378 | 0.1398 |  |

| E                       | 4.850       | 5.000 | 5.150 | 0.1909                | 0.1969 | 0.2028 |  |

| E1                      | 3.450       | 3.500 | 3.550 | 0.1358                | 0.1378 | 0.1398 |  |

| е                       | -           | 0.500 | -     | -                     | 0.0197 | -      |  |

## 7.6 Thermal characteristics

The maximum chip junction temperature (T<sub>J</sub>max) must never exceed the values given in *Table 15: General operating conditions on page 53*.

The maximum chip-junction temperature,  $T_J$  max., in degrees Celsius, may be calculated using the following equation:

$T_J max = T_A max + (PD max x \Theta_{JA})$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance, in ° C/W,

- PD max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (PD max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

$P_{I/O}$  max represents the maximum power dissipation on output pins where: