Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 100MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT            |

| Number of I/O              | 23                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 32K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                             |

| Data Converters            | A/D 4x12b; D/A 1x12b                                                    |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 36-UFBGA, WLCSP                                                         |

| Supplier Device Package    | 36-WLCSP (2.55x2.58)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f410tby7tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Revision history |                                      | 140 |

|------------------|--------------------------------------|-----|

| B.2 E            | Batch Acquisition Mode (BAM) example | 139 |

and the HSE crystal oscillators are disabled. The voltage regulator can also be put either in normal or in low-power mode.

The RTC and the low-power timer (LPTIM1) can remain active in Stop mode. They can consequently be used to wake up the device from this mode.

The device can be woken up from the Stop mode by any of the EXTI line (the EXTI line source can be one of the 16 external lines, the PVD output, LPTIM1, the RTC alarm/ wakeup/ tamper/ time stamp events).

#### • Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.2 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, the SRAM and register contents are lost except for registers in the backup domain when selected.

The device exits the Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on the WKUP pin, or an RTC alarm/ wakeup/ tamper/time stamp event occurs.

Standby mode is not supported when the embedded voltage regulator is bypassed and the 1.2 V domain is controlled by an external power.

# 3.19 V<sub>BAT</sub> operation

The VBAT pin allows to power the device  $V_{BAT}$  domain from an external battery, an external super-capacitor, or from  $V_{DD}$  when no external battery and an external super-capacitor are present.

$V_{BAT}$  operation is activated when  $V_{DD}$  is not present.

The VBAT pin supplies the RTC and the backup registers.

Note: When the microcontroller is supplied from VBAT, external interrupts and RTC alarm/events do not exit it from  $V_{BAT}$  operation. When PDR\_ON pin is not connected to  $V_{DD}$  (internal Reset OFF), the  $V_{BAT}$  functionality is no more available and VBAT pin should be connected to  $V_{DD}$ .

## 3.20 Timers and watchdogs

The devices embed one advanced-control timer, four general purpose timers, one low power timer, two watchdog timers and one SysTick timer.

All timer counters can be frozen in debug mode.

*Table 5* compares the features of the advanced-control and general-purpose timers.

| Timer<br>type        | Timer  | Counter<br>resolution | Counter<br>type         | Prescaler<br>factor                         | DMA<br>request<br>generation | Capture/<br>compare<br>channels | Complemen-<br>tary output | Max.<br>interface<br>clock<br>(MHz) | Max.<br>timer<br>clock<br>(MHz) |

|----------------------|--------|-----------------------|-------------------------|---------------------------------------------|------------------------------|---------------------------------|---------------------------|-------------------------------------|---------------------------------|

| Advanced<br>-control | TIM1   | 16-bit                | Up,<br>Down,<br>Up/down | Any<br>integer<br>between<br>1 and<br>65536 | Yes                          | 4                               | Yes                       | 100                                 | 100                             |

|                      | TIM5   | 32-bit                | Up,<br>Down,<br>Up/down | Any<br>integer<br>between<br>1 and<br>65536 | Yes                          | 4                               | No                        | 50                                  | 100                             |

| General<br>purpose   | TIM9   | 16-bit                | Up                      | Any<br>integer<br>between<br>1 and<br>65536 | No                           | 2                               | No                        | 100                                 | 100                             |

|                      | TIM11  | 16-bit                | Up                      | Any<br>integer<br>between<br>1 and<br>65536 | No                           | 1                               | No                        | 100                                 | 100                             |

| Basic                | TIM6   | 16-bit                | Up                      | Any<br>integer<br>between<br>1 and<br>65536 | Yes                          | 0                               | No                        | 50                                  | 100                             |

| Low-<br>power        | LPTIM1 | 16-bit                | Up                      | Between<br>1 and 128                        | No                           | 2                               | No                        | 50                                  | 100                             |

Table 5. Timer feature comparison

# 3.26 General-purpose input/outputs (GPIOs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain, with or without pull-up or pull-down), as input (floating, with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions. All GPIOs are high-current-capable and have speed selection to better manage internal noise, power consumption and electromagnetic emission.

The I/O configuration can be locked if needed by following a specific sequence in order to avoid spurious writing to the I/Os registers.

Fast I/O handling allowing maximum I/O toggling up to 100 MHz.

# 3.27 Analog-to-digital converter (ADC)

One 12-bit analog-to-digital converter is embedded and shares up to 16 external channels, performing conversions in the single-shot or scan mode. In scan mode, automatic conversion is performed on a selected group of analog inputs.

The ADC can be served by the DMA controller. An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

To synchronize A/D conversion and timers, the ADCs could be triggered by any of TIM1 or TIM5 timer.

## 3.28 Temperature sensor

The temperature sensor has to generate a voltage that varies linearly with temperature. The conversion range is between 1.7 V and 3.6 V. The temperature sensor is internally connected to the ADC\_IN18 input channel which is used to convert the sensor output voltage into a digital value. Refer to the reference manual for additional information.

As the offset of the temperature sensor varies from chip to chip due to process variation, the internal temperature sensor is mainly suitable for applications that detect temperature changes instead of absolute temperatures. If an accurate temperature reading is needed, then an external temperature sensor part should be used.

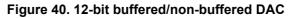

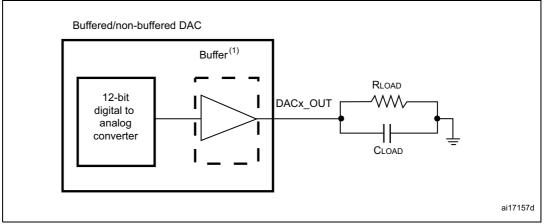

# 3.29 Digital-to-analog converter (DAC)

One 12-bit buffered DAC channel can be used to convert a digital signal into an analog voltage signal output. The chosen design structure is composed of integrated resistor strings and an amplifier in inverting configuration.

This digital interface supports the following features:

- 8-bit or 12-bit monotonic output

- Buffer offset calibration (factory and user trimming)

- Left or right data alignment in 12-bit mode

- Synchronized update capability

- Noise-wave generation

|         | Р      | in Num   | nber   |         |                                                      | e                                  |    |        |                                                                |                      |  |

|---------|--------|----------|--------|---------|------------------------------------------------------|------------------------------------|----|--------|----------------------------------------------------------------|----------------------|--|

| WLCSP36 | LQFP48 | UFQFPN48 | LQFP64 | UFBGA64 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type<br>I/O structure<br>Notes |    | Notes  | Alternate functions                                            | Additional functions |  |

| E4      | 12     | 12       | 16     | F3      | PA2                                                  | I/O                                | FT | -      | TIM5_CH3,<br>TIM9_CH1,<br>I2S2_CKIN,<br>USART2_TX,<br>EVENTOUT | ADC1_2               |  |

| F5      | 13     | 13       | 17     | G3      | PA3                                                  | TIM5_CH4,<br>TIM9_CH2,             |    | ADC1_3 |                                                                |                      |  |

| -       | 1      | -        | 18     | D5      | VSS                                                  | S                                  | I  | -      | -                                                              | -                    |  |

| -       | -      | -        | 19     | E4      | VDD                                                  | S                                  | ŀ  | -      | -                                                              | -                    |  |

| -       | 14     | 14       | 20     | H3      | PA4                                                  | I/O                                | FT | -      | SPI1_NSS/I2S1_WS,<br>USART2_CK,<br>EVENTOUT                    | ADC1_4               |  |

| F4      | 15     | 15       | 21     | F4      | PA5                                                  | I/O                                | тс | -      | SPI1_SCK/I2S1_CK,<br>EVENTOUT                                  | ADC1_5,<br>DAC_OUT1  |  |

| -       | 16     | 16       | 22     | G4      | PA6                                                  | I/O                                | FT | -      | TIM1_BKIN,<br>SPI1_MISO,<br>I2S2_MCK,<br>EVENTOUT              | ADC1_6               |  |

| -       | 17     | 17       | 23     | H4      | PA7                                                  | I/O                                | FT | -      | TIM1_CH1N,<br>SPI1_MOSI/I2S1_SD,<br>EVENTOUT                   | ADC1_7               |  |

| -       | -      | -        | 24     | G5      | PC4                                                  | I/O                                | FT | -      | TIM9_CH1,<br>EVENTOUT                                          | ADC1_14              |  |

| -       | -      | -        | 25     | H5      | PC5                                                  | I/O                                | FT | -      | TIM9_CH2,<br>I2C4_SMBA,<br>EVENTOUT                            | ADC1_15              |  |

| -       | 18     | 18       | 26     | F5      | PB0                                                  | I/O                                | FT | -      | TIM1_CH2N,<br>SPI5_SCK/I2S5_CK,<br>EVENTOUT                    | ADC1_8               |  |

| -       | 19     | 19       | 27     | G6      | PB1                                                  | I/O                                | тс | -      | TIM1_CH3N,<br>SPI5_NSS/I2S5_WS,<br>EVENTOUT                    | ADC1_9               |  |

| F3      | 20     | 20       | 28     | H6      | PB2                                                  | I/O                                | FT | -      | LPTIM1_OUT,<br>EVENTOUT                                        | BOOT1                |  |

|                 | accelerator disabled) running from SRAM - V <sub>DD</sub> = 1.7 V |                                                         |                                          |         |              |                           |                           |                           |                            |                            |      |

|-----------------|-------------------------------------------------------------------|---------------------------------------------------------|------------------------------------------|---------|--------------|---------------------------|---------------------------|---------------------------|----------------------------|----------------------------|------|

|                 |                                                                   |                                                         | £                                        | Valtaga | PLL<br>VCO   | Тур                       |                           | Ма                        | ax <sup>(2)</sup>          |                            |      |

| Symbol          | Parameter                                                         | Conditions                                              | f <sub>HCLK</sub> Voltage<br>(MHz) scale |         | (MHz)<br>(1) | Т <sub>А</sub> =<br>25 °С | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | T <sub>A</sub> =<br>125 °C | Unit |

|                 |                                                                   |                                                         | 100                                      | S1      | 200          | 17.4                      | 18.3 <sup>(5)</sup>       | 19.1                      | 19.4 <sup>(6)</sup>        | 20.2 <sup>(5)</sup>        |      |

|                 |                                                                   | Enternal                                                | 84                                       | S2      | 168          | 14.1                      | 14.8 <sup>(5)</sup>       | 15.4                      | 15.8 <sup>(6)</sup>        | 16.6 <sup>(5)</sup>        |      |

|                 |                                                                   | External clock,                                         | 64                                       | S3      | 128          | 9.8                       | 10.3 <sup>(5)</sup>       | 10.7                      | 11.0 <sup>(6)</sup>        | 11.7 <sup>(5)</sup>        |      |

|                 |                                                                   | all peripherals enabled $^{(3)(4)}$                     | 50                                       | S3      | 100          | 7.7                       | 8.1                       | 8.5                       | 8.8                        | 9.5                        |      |

|                 |                                                                   | enabled                                                 | 25                                       | S3      | 100          | 4.1                       | 4.4                       | 4.7                       | 5.0                        | 5.7                        | mA   |

|                 | Supply current in                                                 |                                                         | 20                                       | S3      | 160          | 3.5                       | 3.8                       | 4.1                       | 4.4                        | 5.1                        |      |

|                 |                                                                   | HSI, PLL off,<br>all peripherals<br>enabled $^{(3)(4)}$ | 16                                       | S3      | off          | 2.5                       | 2.6                       | 2.9                       | 3.2                        | 4.0                        |      |

| I               |                                                                   |                                                         | 1                                        | S3      | off          | 0.4                       | 0.5                       | 0.8                       | 1.2                        | 2.0                        |      |

| I <sub>DD</sub> | Run mode                                                          |                                                         | 100                                      | S1      | 200          | 11.8                      | 12.5                      | 12.9                      | 13.3                       | 14.1                       |      |

|                 |                                                                   | External                                                | 84                                       | S2      | 168          | 9.6                       | 10.1                      | 10.4                      | 10.8                       | 11.6                       |      |

|                 |                                                                   | clock,                                                  | 64                                       | S3      | 128          | 6.7                       | 7.2                       | 7.4                       | 7.7                        | 8.4                        |      |

|                 |                                                                   | all peripherals disabled <sup>(3)</sup>                 | 50                                       | S3      | 100          | 5.3                       | 5.6                       | 5.9                       | 6.2                        | 6.9                        |      |

|                 |                                                                   | uisabieu                                                | 25                                       | S3      | 100          | 2.9                       | 3.1                       | 3.3                       | 3.7                        | 4.4                        |      |

|                 |                                                                   |                                                         | 20                                       | S3      | 160          | 2.5                       | 2.7                       | 2.9                       | 3.2                        | 3.9                        |      |

|                 |                                                                   | HSI, PLL off,                                           | 16                                       | S3      | off          | 1.7                       | 1.9                       | 2.1                       | 2.4                        | 3.2                        |      |

|                 |                                                                   | all peripherals<br>disabled <sup>(3)</sup>              | 1                                        | S3      | off          | 0.3                       | 0.4                       | 0.7                       | 1.1                        | 1.9                        |      |

# Table 21. Typical and maximum current consumption, code with data processing (ART accelerator disabled) running from SRAM - V<sub>DD</sub> = 1.7 V

1. Refer to Table 44 and RM0401 for the possible PLL VCO setting

2. Guaranteed by characterization, unless otherwise specified

3. When the ADC is ON (ADON bit set in ADC\_CR2), an additional power consumption of 1.6 mA must be added.

4. Add an additional power consumption of 1.6 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is ON (ADON bit is set in the ADC\_CR2 register)

5. Guaranteed by tests in production.

6. Guaranteed by test in production for temperature range 7 salestypes only.

|                 |                      | accelerator di                                                | Sabieuj                                  | running |              | iasii ii                  | lemory                    |                           |                            |                            |      |

|-----------------|----------------------|---------------------------------------------------------------|------------------------------------------|---------|--------------|---------------------------|---------------------------|---------------------------|----------------------------|----------------------------|------|

|                 |                      |                                                               | £                                        | Valtaga | PLL<br>VCO   | Тур                       |                           | Ма                        | x <sup>(2)</sup>           |                            |      |

| Symbol          | Parameter            | Conditions                                                    | f <sub>HCLK</sub> Voltage<br>(MHz) scale |         | (MHz)<br>(1) | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | T <sub>A</sub> =<br>125 °C | Unit |

|                 |                      |                                                               | 100                                      | S1      | 200          | 24.7                      | 26.3                      | 26.5                      | 27.0                       | 28.0                       |      |

|                 |                      |                                                               | 84                                       | S2      | 168          | 21.6                      | 23.0                      | 23.2                      | 23.7                       | 24.7                       |      |

|                 |                      | External clock,                                               | 64                                       | S3      | 128          | 15.9                      | 17.0                      | 17.1                      | 17.6                       | 18.6                       |      |

|                 |                      | all peripherals<br>enabled <sup>(3)(4)</sup>                  | 50                                       | S3      | 100          | 13.1                      | 14.2                      | 14.3                      | 14.7                       | 15.7                       |      |

|                 | Supply<br>current in |                                                               | 25                                       | S3      | 100          | 7.5                       | 8.2                       | 8.3                       | 8.7                        | 9.7                        | mA   |

|                 |                      |                                                               | 20                                       | S3      | 160          | 6.5                       | 7.1                       | 7.2                       | 7.5                        | 8.5                        |      |

|                 |                      | HSI, PLL OFF,<br>all peripherals<br>enabled <sup>(3)(4)</sup> | 16                                       | S3      | off          | 4.7                       | 5.3                       | 5.5                       | 5.9                        | 6.9                        |      |

| l               |                      |                                                               | 1                                        | S3      | off          | 0.8                       | 1.2                       | 1.6                       | 1.9                        | 2.9                        |      |

| I <sub>DD</sub> | Run mode             |                                                               | 100                                      | S1      | 200          | 19.1                      | 20.5                      | 20.7                      | 21.3                       | 22.3                       |      |

|                 |                      |                                                               | 84                                       | S2      | 168          | 17.1                      | 18.3                      | 18.6                      | 19.1                       | 20.1                       |      |

|                 |                      | External clock,                                               | 64                                       | S3      | 128          | 12.8                      | 13.8                      | 14.0                      | 14.5                       | 15.5                       |      |

|                 |                      | all peripherals disabled <sup>(3)</sup>                       | 50                                       | S3      | 100          | 10.7                      | 11.7                      | 11.8                      | 12.2                       | 13.2                       | -    |

|                 |                      |                                                               | 25                                       | S3      | 100          | 6.3                       | 7.0                       | 7.1                       | 7.4                        | 8.3                        |      |

|                 |                      |                                                               | 20                                       | S3      | 160          | 5.4                       | 6.0                       | 6.2                       | 6.5                        | 7.4                        |      |

|                 |                      | HSI, PLL OFF,                                                 | 16                                       | S3      | off          | 4.0                       | 4.5                       | 5.0                       | 5.1                        | 6.0                        |      |

|                 |                      | all peripherals disabled <sup>(3)</sup>                       | 1                                        | S3      | off          | 0.8                       | 1.1                       | 1.5                       | 1.8                        | 2.7                        |      |

| Table 25. | Typical and maximum current consumption in run mode, code with data processing |

|-----------|--------------------------------------------------------------------------------|

|           | (ART accelerator disabled) running from Flash memory - V <sub>DD</sub> = 3.6 V |

1. Refer to Table 44 and RM0401 for the possible PLL VCO setting

2. Guaranteed by characterization, unless otherwise specified.

3. When the ADC is ON (ADON bit set in ADC\_CR2), an additional power consumption of 1.6 mA must be added.

4. Add an additional power consumption of 1.6 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is ON (ADON bit is set in the ADC\_CR2 register)

|                 |                                      |                                                                                                               |                            |                  | PLL<br>VCO  | Тур                       |                           |                           | x <sup>(2)</sup>           |                            |      |

|-----------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------|------------------|-------------|---------------------------|---------------------------|---------------------------|----------------------------|----------------------------|------|

| Symbol          | Parameter                            | Conditions                                                                                                    | f <sub>HCLK</sub><br>(MHz) | Voltage<br>scale | scale (MHz) | Т <sub>А</sub> =<br>25 °С | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | T <sub>A</sub> =<br>125 °C | Unit |

|                 |                                      | All peripherals                                                                                               | 100                        | S1               | 200         | 8.0                       | 8.2 <sup>(5)</sup>        | 9.0                       | 9.4 <sup>(6)</sup>         | 10.2 <sup>(5)</sup>        |      |

|                 |                                      | enabled <sup>(3)(4)</sup> ,                                                                                   | 84                         | S2               | 168         | 6.5                       | 6.7                       | 7.4                       | 7.7                        | 8.5                        |      |

|                 |                                      | External clock,<br>PLL ON, Flash                                                                              | 64                         | S3               | 128         | 4.6                       | 4.7                       | 5.2                       | 5.5                        | 6.3                        |      |

|                 | memory in Deep                       | 50                                                                                                            | S3                         | 100              | 3.7         | 3.9                       | 4.3                       | 4.6                       | 5.4                        |                            |      |

|                 | power down<br>mode                   | 25                                                                                                            | S3                         | 100              | 2.2         | 2.3                       | 2.6                       | 2.9                       | 3.8                        |                            |      |

|                 |                                      | mode                                                                                                          | 20                         | S3               | 160         | 2.1                       | 2.2                       | 2.5                       | 2.8                        | 3.6                        |      |

|                 |                                      | All peripherals<br>enabled <sup>(3)(4)</sup> ,<br>HSI, PLL OFF,<br>Flash memory in<br>Deep power<br>down mode | 16                         | S3               | off         | 1.1                       | 1.2                       | 1.5                       | 1.9                        | 2.7                        |      |

| I <sub>DD</sub> | Supply<br>current in<br><b>Sleep</b> |                                                                                                               | 1                          | S3               | off         | 0.3                       | 0.4                       | 0.7                       | 1.1                        | 1.9                        | mA   |

|                 | mode                                 |                                                                                                               | 100                        | S1               | 200         | 8.4                       | 8.7                       | 9.5                       | 9.9                        | 10.7                       |      |

|                 |                                      | All peripherals                                                                                               | 84                         | S2               | 168         | 6.9                       | 7.1                       | 7.7                       | 8.1                        | 8.9                        |      |

|                 |                                      | enabled <sup>(3)(4)</sup> ,<br>External clock,                                                                | 64                         | S3               | 128         | 4.9                       | 5.1                       | 5.5                       | 5.9                        | 6.7                        |      |

|                 |                                      | PLL ON, Flash                                                                                                 | 50                         | S3               | 100         | 4.0                       | 4.2                       | 4.6                       | 4.9                        | 5.7                        |      |

|                 |                                      | memory ON                                                                                                     | 25                         | S3               | 100         | 2.5                       | 2.6                       | 2.9                       | 3.2                        | 4.0                        |      |

|                 |                                      |                                                                                                               | 20                         | S3               | 160         | 2.4                       | 2.5                       | 2.7                       | 3.1                        | 3.9                        |      |

|                 |                                      | All peripherals                                                                                               | 16                         | S3               | off         | 1.4                       | 1.4                       | 1.8                       | 2.2                        | 3.0                        |      |

|                 |                                      | enabled <sup>(3)</sup> , HSI,<br>PLL OFF, Flash<br>memory ON                                                  | 1                          | S3               | off         | 0.6                       | 0.6                       | 1.0                       | 1.3                        | 2.0                        |      |

Table 28. Typical and maximum current consumption in Sleep mode -  $V_{DD}$  = 3.6 V

trigger circuits used to discriminate the input value. Unless this specific configuration is required by the application, this supply current consumption can be avoided by configuring these I/Os in analog mode. This is notably the case of ADC input pins which should be configured as analog inputs.

**Caution:** Any floating input pin can also settle to an intermediate voltage level or switch inadvertently, as a result of external electromagnetic noise. To avoid current consumption related to floating pins, they must either be configured in analog mode, or forced internally to a definite digital value. This can be done either by using pull-up/down resistors or by configuring the pins in output mode.

I/O dynamic current consumption

In addition to the internal peripheral current consumption (see *Table 36: Peripheral current consumption*), the I/Os used by an application also contribute to the current consumption. When an I/O pin switches, it uses the current from the MCU supply voltage to supply the I/O pin circuitry and to charge/discharge the capacitive load (internal or external) connected to the pin:

$$I_{SW} = V_{DD} \times f_{SW} \times C$$

where

$I_{SW}$  is the current sunk by a switching I/O to charge/discharge the capacitive load  $V_{DD}$  is the MCU supply voltage

f<sub>SW</sub> is the I/O switching frequency

C is the total capacitance seen by the I/O pin: C =  $C_{INT}$ +  $C_{EXT}$

The test pin is configured in push-pull output mode and is toggled by software at a fixed frequency.

| Symbol | Parameter               | Conditions <sup>(1)</sup>                                  | I/O toggling<br>frequency (f <sub>SW</sub> ) | Тур   | Unit |

|--------|-------------------------|------------------------------------------------------------|----------------------------------------------|-------|------|

|        |                         |                                                            | 2 MHz                                        | 0.05  |      |

|        |                         |                                                            | 8 MHz                                        | 0.15  |      |

|        |                         |                                                            | 25 MHz                                       | 0.45  |      |

|        |                         | V <sub>DD</sub> = 3.3 V<br>C = C <sub>INT</sub>            | 50 MHz                                       | 0.85  |      |

|        |                         |                                                            | 60 MHz                                       | 1.00  |      |

|        |                         |                                                            | 84 MHz                                       | 1.40  |      |

|        |                         | 90 MHz                                                     | 1.67                                         |       |      |

|        |                         |                                                            | 2 MHz                                        | 0.10  |      |

|        |                         | 8 MHz                                                      | 0.35                                         |       |      |

|        | V <sub>DD</sub> = 3.3 V | 25 MHz                                                     | 1.05                                         |       |      |

|        |                         | $C_{EXT} = 0 \text{ pF}$ $C = C_{INT} + C_{EXT} + C_S$     | 50 MHz                                       | 2.20  | mA   |

|        |                         |                                                            | 60 MHz                                       | 2.40  |      |

|        |                         |                                                            | 84 MHz                                       | 3.55  |      |

|        |                         |                                                            | 90 MHz                                       | 4.23  |      |

| IDDIO  | I/O switching           |                                                            | 2 MHz                                        | 0.20  |      |

|        | current                 |                                                            | 8 MHz                                        | 0.65  |      |

|        |                         | V <sub>DD</sub> = 3.3 V                                    | 25 MHz                                       | 1.85  |      |

|        |                         | C <sub>EXT</sub> =10 pF                                    | 50 MHz                                       | 2.45  |      |

|        |                         | $C = C_{INT} + C_{EXT} + C_S$                              | 60 MHz                                       | 4.70  |      |

|        |                         |                                                            | 84 MHz                                       | 8.80  |      |

|        |                         |                                                            | 90 MHz                                       | 10.47 |      |

|        |                         |                                                            | 2 MHz                                        | 0.25  |      |

|        |                         | V <sub>DD</sub> = 3.3 V                                    | 8 MHz                                        | 1.00  |      |

|        |                         | C <sub>EXT</sub> = 22 pF                                   | 25 MHz                                       | 3.45  |      |

|        |                         | $C = C_{INT} + C_{EXT} + C_{S}$                            | 50 MHz                                       | 7.15  |      |

|        |                         |                                                            | 60 MHz                                       | 11.55 |      |

|        |                         |                                                            | 2 MHz                                        | 0.32  |      |

|        |                         | $V_{DD} = 3.3 V$                                           | 8 MHz                                        | 1.27  | -    |

|        |                         | $C_{EXT} = 33 \text{ pF}$<br>$C = C_{INT} + C_{EXT} + C_S$ | 25 MHz                                       | 3.88  |      |

|        |                         |                                                            | 50 MHz                                       | 12.34 |      |

Table 35. Switching output I/O current consumption

1. CS is the PCB board capacitance including the pad pin. CS = 7 pF (estimated value).

### On-chip peripheral current consumption

The MCU is placed under the following conditions:

- At startup, all I/O pins are in analog input configuration.

- All peripherals are disabled unless otherwise mentioned.

- The ART accelerator is ON.

- Voltage Scale 2 mode selected, internal digital voltage V12 = 1.26 V.

- HCLK is the system clock at 100 MHz.  $f_{PCLK1} = f_{HCLK}/2$ , and  $f_{PCLK2} = f_{HCLK}$ . The given value is calculated by measuring the difference of current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

- Ambient operating temperature is 25 °C and V<sub>DD</sub>=3.3 V.

|                 |                     |                   | I <sub>DD</sub> (Typ) |                   |          |  |

|-----------------|---------------------|-------------------|-----------------------|-------------------|----------|--|

| Perip           | bheral              | Voltage<br>scale1 | Voltage<br>scale2     | Voltage<br>scale3 | Unit     |  |

|                 | GPIOA               | 1.68              | 1.62                  | 1.42              |          |  |

|                 | GPIOB               | 1.67              | 1.60                  | 1.41              |          |  |

|                 | GPIOC               | 1.63              | 1.56                  | 1.39              |          |  |

|                 | GPIOH               | 0.61              | 0.61                  | 0.52              |          |  |

| AHB1            | CRC                 | 0.31              | 0.32                  | 0.25              | µA/MHz   |  |

| (up to 100 MHz) | DMA1 <sup>(1)</sup> | 1.67N +<br>3.12   | 1.60N +<br>2.96       | 1.43N +<br>2.64   |          |  |

|                 | DMA2 <sup>(1)</sup> | 1.59N +<br>2.83   | 1.52N +<br>2.65       | 1.36N +<br>2.41   |          |  |

|                 | RNG                 | 0.90              | 0.88                  | 0.75              |          |  |

|                 | APB1 to AHB         | 0,78              | 0,74                  | 0,63              |          |  |

|                 | TIM5                | 13,38             | 12,76                 | 11,41             |          |  |

|                 | TIM6                | 2,14              | 1,98                  | 1,75              |          |  |

|                 | LPTIM               | 8,22              | 7,88                  | 7,06              |          |  |

|                 | WWDG                | 0,64              | 0,64                  | 0,56              |          |  |

| APB1            | SPI2/I2S2           | 2,42              | 2,33                  | 2,06              |          |  |

| (up to 50 MHz)  | USART2              | 3,38              | 3,29                  | 2,91              | - μA/MHz |  |

|                 | I2C1                | 3,46              | 3,33                  | 2,97              |          |  |

|                 | I2C2                | 3,50              | 3,31                  | 2,97              |          |  |

|                 | I2C4                | 4,82              | 4,64                  | 4,09              |          |  |

|                 | PWR                 | 0,66              | 0,64                  | 0,62              |          |  |

|                 | DAC                 | 0,84              | 0,81                  | 0,78              |          |  |

### Table 36. Peripheral current consumption

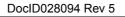

Figure 19. High-speed external clock source AC timing diagram

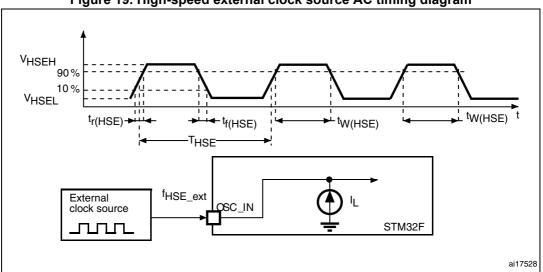

Figure 20. Low-speed external clock source AC timing diagram

#### High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 4 to 26 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 40*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Param                                                 | eter                                                              | Conditions                                                       | Min                                         | Тур                                | Мах | Unit |

|-------------------------------------|-------------------------------------------------------|-------------------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------|------------------------------------|-----|------|

|                                     | FT, TC and NRST level voltage <sup>(5)</sup>          | I/O input high                                                    | 1.7 V≤V <sub>DD</sub> ≤3.6 V                                     | 0.7V <sub>DD</sub> <sup>(1)</sup>           | -                                  | -   |      |

| V <sub>IH</sub>                     | BOOT0 I/O input I                                     | nigh level                                                        | 1.75 V≤V <sub>DD</sub> ≤3.6 V,<br>-40 °C≤T <sub>A</sub> ≤ 125 °C | 0.17V <sub>DD</sub> +<br>0.7 <sup>(2)</sup> |                                    |     | V    |

|                                     | voltage                                               |                                                                   | 1.7 V≤V <sub>DD</sub> ≤3.6 V,<br>0 °C≤T <sub>A</sub> ≤ 125 °C    | 0.7 <sup>(2)</sup>                          | -                                  | -   |      |

|                                     | FT, TC and NRST hysteresis                            | I/O input                                                         | 1.7 V≤V <sub>DD</sub> ≤3.6 V                                     | -                                           | 10% V <sub>DD</sub> <sup>(3)</sup> | -   | V    |

| V <sub>HYS</sub><br>BOOT0 I/O input | nysteresis                                            | 1.75 V≤V <sub>DD</sub> ≤3.6 V,<br>- 40 °C≤T <sub>A</sub> ≤ 125 °C |                                                                  | 100                                         | _                                  | mV  |      |

|                                     |                                                       |                                                                   | 1.7 V⊴V <sub>DD</sub> ≤3.6 V,<br>0 °C⊴T <sub>A</sub> ≤ 125 °C    |                                             | 100                                |     |      |

|                                     | I/O input leakage current <sup>(4)</sup>              |                                                                   | $V_{SS} \leq V_{IN} \leq V_{DD}$                                 | -                                           | -                                  | Ŧ   |      |

| l <sub>lkg</sub>                    | I/O FT/TC input le                                    | akage current                                                     | V <sub>IN</sub> = 5 V                                            | -                                           | -                                  | 3   | μA   |

| R <sub>PU</sub>                     | Weak pull-up<br>equivalent<br>resistor <sup>(6)</sup> | All pins<br>except for<br>PA10<br>(OTG_FS_ID)                     | V <sub>IN</sub> = V <sub>SS</sub>                                | 30                                          | 40                                 | 50  |      |

|                                     |                                                       | PA10<br>(OTG_FS_ID)                                               | -                                                                | 7                                           | 10                                 | 14  | kΩ   |

| R <sub>PD</sub>                     | Weak pull-down<br>R <sub>PD</sub> equivalent          | All pins<br>except for<br>PA10<br>(OTG_FS_ID)                     | $V_{IN} = V_{DD}$                                                | 30                                          | 40                                 | 50  | N22  |

|                                     | resistor <sup>(7)</sup>                               | PA10<br>(OTG_FS_ID)                                               | -                                                                | 7                                           | 10                                 | 14  |      |

| C <sub>IO</sub> <sup>(8)</sup>      | I/O pin capacitanc                                    | e                                                                 | -                                                                | -                                           | 5                                  | -   | pF   |

Table 55. I/O static characteristics (continued)

1. Guaranteed by tests in production.

2. Guaranteed by design.

3. With a minimum of 200 mV.

4. Leakage could be higher than the maximum value, if negative current is injected on adjacent pins, Refer to Table 54: I/O current injection susceptibility

To sustain a voltage higher than VDD +0.3 V, the internal pull-up/pull-down resistors must be disabled. Leakage could be higher than the maximum value, if negative current is injected on adjacent pins. Refer to Table 54: I/O current injection susceptibility

6. Pull-up resistors are designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is minimum (~10% order).

7. Pull-down resistors are designed with a true resistance in series with a switchable NMOS. This NMOS contribution to the series resistance is minimum (~10% order).

8. Hysteresis voltage between Schmitt trigger switching levels. Guaranteed by characterization.

All I/Os are CMOS and TTL compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters. The coverage of these requirements for FT and TC I/Os is shown in *Figure* 27.

DocID028094 Rev 5

#### **Electrical characteristics**

| OSPEEDRy<br>[1:0] bit<br>value <sup>(1)</sup> | Symbol                                           | Parameter                                                                       | Conditions                                       | Min | Тур | Max                    | Unit       |

|-----------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------|-----|-----|------------------------|------------|

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD</sub> ≥ 2.70 V | -   | -   | 25                     |            |

|                                               | £                                                | Maximum fraguanau <sup>(3)</sup>                                                | C <sub>L</sub> = 50 pF, V <sub>DD</sub> ≥ 1.7 V  | -   | -   | 12.5                   | MHz        |

|                                               | f <sub>max(IO)out</sub>                          | Maximum frequency <sup>(3)</sup>                                                | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.70 V | -   | -   | 50                     |            |

| 01                                            |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V  | -   | -   | 20                     |            |

| 01                                            |                                                  |                                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD</sub> ≥2.7 V   | -   | -   | 10                     |            |

|                                               | t <sub>f(IO)out</sub> /                          | Output high to low level fall time and output low to high                       | C <sub>L</sub> = 50 pF, V <sub>DD</sub> ≥ 1.7 V  |     |     | 20                     | ns         |

|                                               | t <sub>r(IO)out</sub>                            | level rise time                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.70 V | -   |     |                        |            |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V  | -   | -   | 10                     |            |

|                                               | f <sub>max</sub> (IO)out                         | Maximum frequency <sup>(3)</sup>                                                | C <sub>L</sub> = 40 pF, V <sub>DD</sub> ≥ 2.70 V | -   | -   | 50 <sup>(4)</sup>      |            |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 40 pF, V <sub>DD</sub> ≥ 1.7 V  | -   | -   | 25                     |            |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.70 V | -   | -   | 100 <sup>(</sup><br>4) | MHz        |

| 10                                            |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V  | -   | -   | 50 <sup>(4)</sup>      |            |

|                                               | t <sub>f(IO)out</sub> /<br>t <sub>r(IO)out</sub> | Output high to low level fall<br>time and output low to high<br>level rise time | C <sub>L</sub> = 40 pF, V <sub>DD</sub> ≥ 2.70 V | -   | -   | 6                      |            |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 40 pF, V <sub>DD</sub> ≥ 1.7 V  | -   | -   | 10                     |            |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.70 V | -   | -   | 4                      | ns         |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V  | -   | -   | 6                      |            |

|                                               | F <sub>max(IO)out</sub>                          | ut Maximum frequency <sup>(3)</sup>                                             | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥ 2.70 V | -   | -   | 100 <sup>(</sup><br>4) | MHz        |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥ 1.7 V  | -   | -   | 50 <sup>(4)</sup>      |            |

| 11                                            |                                                  |                                                                                 | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥ 2.70 V | -   | -   | 4                      |            |

|                                               | t <sub>f(IO)out</sub> /                          | Output high to low level fall                                                   | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥ 1.7 V  | -   | -   | 6                      | <b>n</b> 0 |

|                                               | t <sub>r(IO)out</sub>                            | time and output low to high level rise time                                     | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.70 V | -   | -   | 2.5                    | ns         |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V  | -   | -   | 4                      |            |

| -                                             | t <sub>EXTIpw</sub>                              | Pulse width of external signals detected by the EXTI controller                 | -                                                | 10  | -   | -                      | ns         |

Table 57. I/O AC characteristics<sup>(1)(2)</sup> (continued)

1. Guaranteed by characterization.

2. The I/O speed is configured using the OSPEEDRy[1:0] bits. Refer to the STM32F4xx reference manual for a description of the GPIOx\_SPEEDR GPIO port output speed register.

3. The maximum frequency is defined in *Figure 28*.

4. For maximum frequencies above 50 MHz and  $V_{DD}$  > 2.4 V, the compensation cell should be used.

## 6.3.19 Communications interfaces

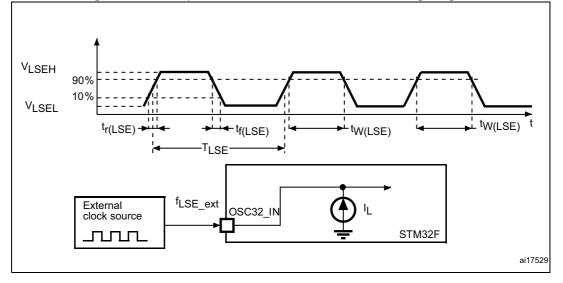

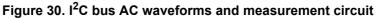

## I<sup>2</sup>C interface characteristics

The I<sup>2</sup>C interface meets the requirements of the standard I<sup>2</sup>C communication protocol with the following restrictions: the I/O pins SDA and SCL are mapped to are not "true" opendrain. When configured as open-drain, the PMOS connected between the I/O pin and V<sub>DD</sub> is disabled, but is still present.

The I<sup>2</sup>C characteristics are described in *Table 60*. Refer also to *Section 6.3.16*: I/O port *characteristics* for more details on the input/output alternate function characteristics (SDA and SCL).

The  $I^2C$  bus interface supports standard mode (up to 100 kHz) and fast mode (up to 400 kHz). The  $I^2C$  bus frequency can be increased up to 1 MHz. For more details about the complete solution, please contact your local ST sales representative.

| Symbol                                     | Parameter                                                                                          |     | rd mode<br>(1)(2)   | Fast mod          | Unit               |     |  |

|--------------------------------------------|----------------------------------------------------------------------------------------------------|-----|---------------------|-------------------|--------------------|-----|--|

|                                            |                                                                                                    | Min | Max                 | Min               | Max                |     |  |

| t <sub>w(SCLL)</sub>                       | SCL clock low time                                                                                 | 4.7 | -                   | 1.3               | -                  | 110 |  |

| t <sub>w(SCLH)</sub>                       | SCL clock high time                                                                                | 4.0 | -                   | 0.6               | -                  | μs  |  |

| t <sub>su(SDA)</sub>                       | SDA setup time                                                                                     | 250 | -                   | 100               | -                  |     |  |

| t <sub>h(SDA)</sub>                        | SDA data hold time                                                                                 | 0   | 3450 <sup>(3)</sup> | 0                 | 900 <sup>(4)</sup> |     |  |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time                                                                              | -   | 1000                | -                 | 300                | ns  |  |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time                                                                              | -   | 300                 | -                 | 300                |     |  |

| t <sub>h(STA)</sub>                        | Start condition hold time                                                                          | 4.0 | -                   | 0.6               | -                  |     |  |

| t <sub>su(STA)</sub>                       | Repeated Start condition setup time                                                                | 4.7 | -                   | 0.6               | -                  | μs  |  |

| t <sub>su(STO)</sub>                       | Stop condition setup time                                                                          | 4.0 | -                   | 0.6               | -                  | μs  |  |

| t <sub>w(STO:STA)</sub>                    | Stop to Start condition time (bus free)                                                            | 4.7 | -                   | 1.3               | -                  | μs  |  |

| t <sub>SP</sub>                            | Pulse width of the spikes<br>that are suppressed by the<br>analog filter for standard fast<br>mode |     |                     | 50 <sup>(5)</sup> | ns                 |     |  |

| Cb                                         | Capacitive load for each bus line                                                                  | -   | 400                 | -                 | 400                | pF  |  |

## Table 60. I<sup>2</sup>C characteristics

1. Guaranteed by design.

f<sub>PCLK1</sub> must be at least 2 MHz to achieve standard mode I<sup>2</sup>C frequencies. It must be at least 4 MHz to achieve fast mode I<sup>2</sup>C frequencies, and a multiple of 10 MHz to reach the 400 kHz maximum I<sup>2</sup>C fast mode clock.

3. The device must internally provide a hold time of at least 300 ns for the SDA signal in order to bridge the undefined region of the falling edge of SCL.

- 4. The maximum data hold time has only to be met if the interface does not stretch the low period of SCL signal.

- 5. The minimum width of the spikes filtered by the analog filter is above  $t_{SP}$  (max)

- 1. R<sub>S</sub> = series protection resistor.

- 2.  $R_P$  = external pull-up resistor.

- 3.  $V_{DD\_I2C}$  is the I2C bus power supply.

| Table 61. SCL frequency | (f <sub>PCLK1</sub> = 50 MHz, V <sub>DD</sub> = V <sub>DD_12C</sub> = 3.3 V) <sup>(1)(2)</sup> |

|-------------------------|------------------------------------------------------------------------------------------------|

|-------------------------|------------------------------------------------------------------------------------------------|

| f (kU-)                | I2C_CCR value           |

|------------------------|-------------------------|

| f <sub>SCL</sub> (kHz) | R <sub>P</sub> = 4.7 kΩ |

| 400                    | 0x8019                  |

| 300                    | 0x8021                  |

| 200                    | 0x8032                  |

| 100                    | 0x0096                  |

| 50                     | 0x012C                  |

| 20                     | 0x02EE                  |

1.  $R_P$  = External pull-up resistance,  $f_{SCL}$  =  $I^2C$  speed

For speeds around 200 kHz, the tolerance on the achieved speed is of ±5%. For other speed ranges, the tolerance on the achieved speed is ±2%. These variations depend on the accuracy of the external components used to design the application.

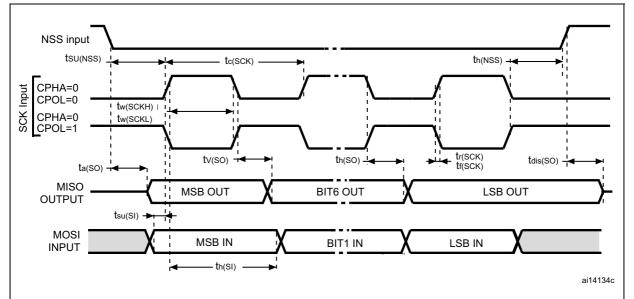

| Symbol               | Parameter                | Conditions                                                  | Min | Тур | Мах  | Unit |  |  |  |

|----------------------|--------------------------|-------------------------------------------------------------|-----|-----|------|------|--|--|--|

| t <sub>a(SO</sub> )  | Data output access time  | Slave mode                                                  | 7   | -   | 21   | ns   |  |  |  |

| t <sub>dis(SO)</sub> | Data output disable time | Slave mode                                                  | 5   | -   | 12   | ns   |  |  |  |

| t <sub>v(SO)</sub>   | Data output valid time   | Slave mode (after enable edge),<br>2.7 V < $V_{DD}$ < 3.6 V | -   | 11  | 13   | ns   |  |  |  |

|                      |                          | Slave mode (after enable edge),<br>1.7 V < $V_{DD}$ < 3.6 V | -   | 11  | 18.5 | ns   |  |  |  |

| t <sub>h(SO)</sub>   | Data output hold time    | Slave mode (after enable edge),<br>1.7 V < $V_{DD}$ < 3.6 V | 8   | -   | -    | ns   |  |  |  |

| t <sub>v(MO)</sub>   | Data output valid time   | Master mode (after enable edge)                             | -   | 4   | 6    | ns   |  |  |  |

| t <sub>h(MO)</sub>   | Data output hold time    | Master mode (after enable edge)                             | 0   | -   | _    | ns   |  |  |  |

| Table 64. SPI dynamic characteristics <sup>(1</sup> | ) (continued) |

|-----------------------------------------------------|---------------|

|-----------------------------------------------------|---------------|

1. Guaranteed by characterization.

2. Maximum frequency in Slave transmitter mode is determined by the sum of  $t_{v(SO)}$  and  $t_{su(MI)}$  which has to fit into SCK low or high phase preceding the SCK sampling edge. This value can be achieved when the SPI communicates with a master having  $t_{su(MI)} = 0$  while Duty(SCK) = 50%

### **Electrical characteristics**

| Symbol                             | Parameter                                                                                | Conditions | Min | Тур | Мах  | Unit | Comments                                                                                                    |  |

|------------------------------------|------------------------------------------------------------------------------------------|------------|-----|-----|------|------|-------------------------------------------------------------------------------------------------------------|--|

| t <sub>WAKEUP</sub> <sup>(4)</sup> | Wakeup time from<br>off state (Setting<br>the ENx bit in the<br>DAC Control<br>register) | -          | -   | 6.5 | 10   | μs   | $C_{LOAD} \le 50$ pF, $R_{LOAD} \ge 5 \text{ k}\Omega$ input code between lowest and highest possible ones. |  |

| PSRR+ <sup>(2)</sup>               | Power supply<br>rejection ratio (to<br>V <sub>DDA</sub> ) (static DC<br>measurement)     | -          | -   | 67  | - 40 | dB   | No R <sub>LOAD</sub> , C <sub>LOAD</sub> = 50 pF                                                            |  |

#### Table 77. DAC characteristics (continued)

1. V<sub>DDA</sub> minimum value of 1.7 V is obtained with the use of an external power supply supervisor (refer to *Section 3.15.2: Internal reset OFF*).

2. Guaranteed by design.

3. The quiescent mode corresponds to a state where the DAC maintains a stable output level to ensure that no dynamic consumption occurs.

4. Guaranteed based on test during characterization.

1. The DAC integrates an output buffer that can be used to reduce the output impedance and to drive external loads directly without the use of an external operational amplifier. The buffer can be bypassed by configuring the BOFFx bit in the DAC\_CR register.

## 6.3.25 RTC characteristics

| Table | 78. | RTC | characteristics |

|-------|-----|-----|-----------------|

|       |     |     |                 |

| Symbol | Parameter                                  | Conditions                                          | Min | Max |

|--------|--------------------------------------------|-----------------------------------------------------|-----|-----|

| -      | f <sub>PCLK1</sub> /RTCCLK frequency ratio | Any read/write operation<br>from/to an RTC register | 4   | -   |

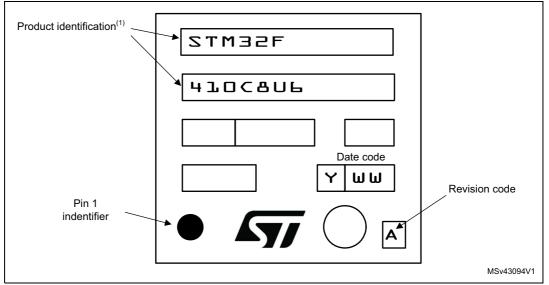

## LQFP48 device marking

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

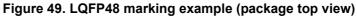

## **UFBGA64** device marking

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

#### Figure 55. UFBGA64 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.