Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Dectano                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                       |

| Peripherals                | Brown-out Detect/Reset, HLVD, LCD, POR, PWM, WDT                           |

| Number of I/O              | 52                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                  |

| Data Converters            | A/D 16x10b/12b                                                             |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 64-QFN (9x9)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f65j94-i-mr |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| _          |                 | _                                   |                  |                       |                 |                 |                |

|------------|-----------------|-------------------------------------|------------------|-----------------------|-----------------|-----------------|----------------|

| R/W-0      | U-0             | R/W-0                               | R/W-0            | R/W-0                 | U-0             | HC/R/W-0        | HS/HC/R-0      |

| ON         |                 | SIDL                                | OE               | RSLP <sup>(1)</sup>   |                 | DIVSW_EN        | ACTIVE         |

| bit 7      |                 |                                     |                  |                       |                 |                 | bit 0          |

|            |                 |                                     |                  |                       |                 |                 |                |

| Legend:    |                 | HC = Hardwar                        | e Clearable bit  | HS = Hardwa           | re Settable bi  | t               |                |

| R = Reada  | able bit        | W = Writable b                      | bit              | U = Unimplen          | nented bit, rea | ad as '0'       |                |

| -n = Value | at all Resets   | '1' = Bit is set                    |                  | '0' = Bit is clea     | ared            | x = Bit is unkn | own            |

|            |                 |                                     |                  |                       |                 |                 |                |

| bit 7      | ON: Refere      | nce Clock Outpu                     | it Enable bit    |                       |                 |                 |                |

|            |                 | nce clock module                    |                  |                       |                 |                 |                |

| 1.11.0     |                 | nce clock module                    |                  |                       |                 |                 |                |

| bit 6      |                 | ented: Read as '                    |                  |                       |                 |                 |                |

| bit 5      |                 | heral Stop in Idle                  |                  | aviaa antara Idl      | a maada         |                 |                |

|            |                 | inues module op<br>les module opera |                  |                       | emode           |                 |                |

| bit 4      |                 | nce Clock Outpu                     |                  |                       |                 |                 |                |

|            |                 | nce clock is drive                  |                  | x pin                 |                 |                 |                |

|            |                 | nce clock is NOT                    |                  |                       |                 |                 |                |

| bit 3      | RSLP: Refe      | erence Clock Ou                     | tput Run in Slee | ep bit <sup>(1)</sup> |                 |                 |                |

|            |                 | nce Clock Output                    |                  |                       |                 |                 |                |

|            |                 | nce Clock Output                    |                  | Sleep                 |                 |                 |                |

| bit 2      | •               | ented: Read as '                    |                  | <b>.</b>              |                 |                 |                |

| bit 1      | _               | I: Clock RODIV S                    |                  |                       |                 |                 |                |

|            |                 | Vivider Switching                   | • •              | gress                 |                 |                 |                |

| L:1 0      |                 | ivider Switching                    | •                | Otatus hit            |                 |                 |                |

| bit 0      |                 | eference Clock (                    |                  |                       | ata tha DOSE    | EL and RODIV re | aistor fields) |

|            |                 |                                     | · ·              |                       |                 | and RODIV regi  | <b>U</b> ,     |

| Note 1:    | This bit has no | effect when ROS                     | SEL<3:0> = 000   | 00/0001, as the       | system clock    | and peripheral  | clock are      |

|            | always disabled | d in Sleep mode                     | on PIC18 devic   | es.                   |                 |                 |                |

#### REGISTER 3-6: REFOXCON: REFERENCE CLOCK OUTPUT CONTROL REGISTER

| R/W-0           | R/W-0                           | R/W-0                              | R/W-0       | R/W-0            | R/W-0            | R/W-0            | R/W-0       |  |  |  |

|-----------------|---------------------------------|------------------------------------|-------------|------------------|------------------|------------------|-------------|--|--|--|

| CCP10MD         | CCP9MD                          | CCP8MD                             | CCP7MD      | CCP6MD           | CCP5MD           | CCP4MD           | ECCP3MD     |  |  |  |

| bit 7           |                                 |                                    |             |                  |                  |                  | bit C       |  |  |  |

| Legend:         |                                 |                                    |             |                  |                  |                  |             |  |  |  |

| R = Readable    | bit                             | W = Writable                       | bit         | U = Unimplen     | nented bit, read | d as '0'         |             |  |  |  |

| -n = Value at F | POR                             | '1' = Bit is set                   |             | '0' = Bit is cle | ared             | x = Bit is unk   | nown        |  |  |  |

| bit 7           | CCP10MD: C                      | CP10 Module                        | Disable bit |                  |                  |                  |             |  |  |  |

|                 |                                 | 910 module is o<br>910 module is e |             | CP10 registers   | are held in Re   | set and are no   | t writable. |  |  |  |

| bit 6           | CCP9MD: CO                      | CP9 Module Dis                     | sable bit   |                  |                  |                  |             |  |  |  |

|                 |                                 | 9 module is dis<br>9 module is ena |             | 9 registers are  | held in Reset a  | and are not wri  | table.      |  |  |  |

| bit 5           | CCP8MD: CC                      | P8 Module Disa                     | able bit    |                  |                  |                  |             |  |  |  |

|                 |                                 | 3 module is dis<br>3 module is ena |             | 8 registers are  | held in Reset a  | and are not wri  | table.      |  |  |  |

| bit 4           | CCP7MD: CC                      | P7 Module Disa                     | able bit    |                  |                  |                  |             |  |  |  |

|                 |                                 | 7 module is dis<br>7 module is ena |             | 7 registers are  | held in Reset a  | and are not wri  | table.      |  |  |  |

| bit 3           | CCP6MD: CCP6 Module Disable bit |                                    |             |                  |                  |                  |             |  |  |  |

|                 |                                 | 6 module is dis<br>6 module is ena |             | 6 registers are  | held in Reset a  | and are not wri  | table.      |  |  |  |

| bit 2           | CCP5MD: CC                      | P5 Module Disa                     | able bit    |                  |                  |                  |             |  |  |  |

|                 |                                 | 5 module is dis<br>5 module is ena |             | 5 registers are  | held in Reset a  | and are not wri  | table.      |  |  |  |

| bit 1           | CCP4MD: CC                      | P4 Module Disa                     | able bit    |                  |                  |                  |             |  |  |  |

|                 |                                 | 4 module is dis<br>4 module is ena |             | 4 registers are  | held in Reset a  | and are not wri  | table.      |  |  |  |

| bit 0           | ECCP3MD: E                      | CCP3 Module                        | Disable bit |                  |                  |                  |             |  |  |  |

|                 |                                 | P3 module is di<br>P3 module is er |             | CP3 registers a  | re held in Rese  | et and are not v | vritable.   |  |  |  |

#### REGISTER 4-5: PMD0: PERIPHERAL MODULE DISABLE REGISTER 0

| Register              | Applicable Devi |        |         | Power-on Reset,<br>Brown-out<br>Reset | MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets | Wake-up via<br>WDT or Interrupt |  |

|-----------------------|-----------------|--------|---------|---------------------------------------|------------------------------------------------------------------|---------------------------------|--|

| SSP2CON3              | 64-pin          | 80-pin | 100-pin | 0000 0000                             | 0000 0000                                                        | uuuu uuuu                       |  |

| CM2CON                | 64-pin          | 80-pin | 100-pin | 0001 1111                             | 0001 1111                                                        | uuuu uuuu                       |  |

| CM3CON                | 64-pin          | 80-pin | 100-pin | 0001 1111                             | 0001 1111                                                        | uuuu uuuu                       |  |

| CCPTMRS0              | 64-pin          | 80-pin | 100-pin | 0000 0000                             | 0000 0000                                                        | uuuu uuuu                       |  |

| CCPTMRS1              | 64-pin          | 80-pin | 100-pin | 00-0 -000                             | 00-0 -000                                                        | uuuu uuuu                       |  |

| CCPTMRS2              | 64-pin          | 80-pin | 100-pin | 0 -000                                | 0 -000                                                           | uuuu uuuu                       |  |

| RCSTA2                | 64-pin          | 80-pin | 100-pin | 0000 000x                             | 0000 000x                                                        | uuuu uuuu                       |  |

| TXSTA2                | 64-pin          | 80-pin | 100-pin | 0000 0010                             | 0000 0010                                                        | uuuu uuuu                       |  |

| BAUDCON2              | 64-pin          | 80-pin | 100-pin | 01x0 0000                             | 01x0 0000                                                        | uuuu uuuu                       |  |

| SPBRGH1               | 64-pin          | 80-pin | 100-pin | 0000 0000                             | 0000 0000                                                        | uuuu uuuu                       |  |

| RCSTA3                | 64-pin          | 80-pin | 100-pin | 0000 000x                             | 0000 000x                                                        | uuuu uuuu                       |  |

| TXSTA3                | 64-pin          | 80-pin | 100-pin | 0000 0010                             | 0000 0010                                                        | uuuu uuuu                       |  |

| BAUDCON3              | 64-pin          | 80-pin | 100-pin | 01x0 0000                             | 01x0 0000                                                        | uuuu uuuu                       |  |

| SPBRGH3               | 64-pin          | 80-pin | 100-pin | 0000 0000                             | 0000 0000                                                        | uuuu uuuu                       |  |

| SPBRG3                | 64-pin          | 80-pin | 100-pin | 0000 0000                             | 0000 0000                                                        | uuuu uuuu                       |  |

| RCREG3                | 64-pin          | 80-pin | 100-pin | 0000 0000                             | 0000 0000                                                        | uuuu uuuu                       |  |

| TXREG3                | 64-pin          | 80-pin | 100-pin | 0000 0000                             | 0000 0000                                                        | uuuu uuuu                       |  |

| DSCONL                | 64-pin          | 80-pin | 100-pin | 000                                   | 000                                                              | uuu                             |  |

| DSCONH                | 64-pin          | 80-pin | 100-pin | 0-00                                  | u-uu                                                             | u-uu                            |  |

| DSWAKEL               | 64-pin          | 80-pin | 100-pin | 0000 0001                             | uuuu uuuu                                                        | uuuu uuuu                       |  |

| DSWAKEH               | 64-pin          | 80-pin | 100-pin | 0                                     | u                                                                | d                               |  |

| DSGPR0 <sup>(6)</sup> | 64-pin          | 80-pin | 100-pin | xxxx xxxx                             | uuuu uuuu                                                        | uuuu uuuu                       |  |

| DSGPR1 <sup>(6)</sup> | 64-pin          | 80-pin | 100-pin | xxxx xxxx                             | uuuu uuuu                                                        | uuuu uuuu                       |  |

| DSGPR2 <sup>(6)</sup> | 64-pin          | 80-pin | 100-pin | xxxx xxxx                             | uuuu uuuu                                                        | uuuu uuuu                       |  |

| DSGPR3                | 64-pin          | 80-pin | 100-pin | xxxx xxxx                             | uuuu uuuu                                                        | uuuu uuuu                       |  |

| SPBRGH2               | 64-pin          | 80-pin | 100-pin | 0000 0000                             | 0000 0000                                                        | uuuu uuuu                       |  |

| SPBRG2                | 64-pin          | 80-pin | 100-pin | 0000 0000                             | 0000 0000                                                        | uuuu uuuu                       |  |

| RCREG2                | 64-pin          | 80-pin | 100-pin | 0000 0000                             | 0000 0000                                                        | uuuu uuuu                       |  |

| TXREG2                | 64-pin          | 80-pin | 100-pin | 0000 0000                             | 0000 0000                                                        | uuuu uuuu                       |  |

| PSTR2CON              | 64-pin          | 80-pin | 100-pin | 00-0 0001                             | 00-0 0001                                                        | uu-u uuuu                       |  |

| PSTR3CON              | 64-pin          | 80-pin | 100-pin | 00-0 0001                             | 00-0 0001                                                        | uu-u uuuu                       |  |

| SSP2STAT              | 64-pin          | 80-pin | 100-pin | 0000 0000                             | 0000 0000                                                        | uuuu uuuu                       |  |

| SSP2CON1              | 64-pin          | 80-pin | 100-pin | 0000 0000                             | 0000 0000                                                        | uuuu uuuu                       |  |

| TABLE 5-3: | INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED | ) |

|------------|--------------------------------------------------------|---|

|            |                                                        |   |

**Legend:** u = unchanged; x = unknown; - = unimplemented bit, read as '0'; q = value depends on condition. Shaded cells indicate that conditions do not apply for the designated device.

**Note 1:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

**2:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

3: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

4: See Table 5-2 for Reset value for specific condition.

- 5: Bits 7,6 are unimplemented on 64 and 80-pin devices.

- 6: If the VBAT is always powered, the DSGPx register values will remain unchanged after the first POR.

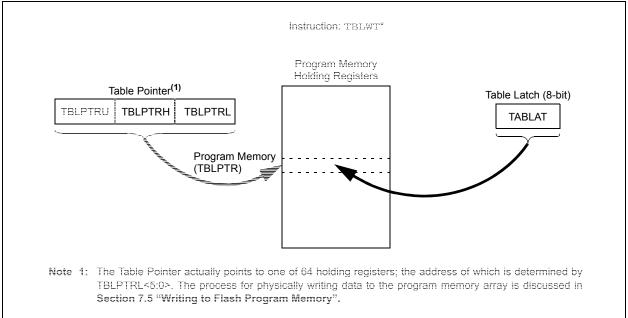

# 7.2 Control Registers

Several control registers are used in conjunction with the TBLRD and TBLWT instructions. These include:

- EECON1 register

- EECON2 register

- TABLAT register

- TBLPTR registers

# 7.2.1 EECON1 AND EECON2 REGISTERS

The EECON1 register (Register 7-1) is the control register for memory accesses. The EECON2 register is not a physical register; it is used exclusively in the memory write and erase sequences. Reading EECON2 will read all '0's.

The WWPROG bit, when set, will allow programming two bytes per word on the execution of the WR command. If this bit is cleared, the WR command will result in programming on a block of 64 bytes.

The FREE bit, when set, will allow a program memory erase operation. When FREE is set, the erase operation is initiated on the next WR command. When FREE is clear, only writes are enabled.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set in hardware when the WR bit is set, and cleared when the internal programming timer expires and the write operation is complete.

**Note:** During normal operation, the WRERR is read as '1'. This can indicate that a write operation was prematurely terminated by a Reset or a write operation was attempted improperly.

# 8.1 External Memory Bus Control

The operation of the interface is controlled by the MEMCON register (Register 8-1). This register is available in all program memory operating modes, except Microcontroller mode. In this mode, the register is disabled and cannot be written to.

The EBDIS bit (MEMCON<7>) controls the operation of the bus and related port functions. Clearing EBDIS enables the interface and disables the I/O functions of the ports, as well as any other functions multiplexed to those pins. Setting the bit enables the I/O ports and other functions, but allows the interface to override everything else on the pins when an external memory operation is required. By default, the external bus is always enabled and disables all other I/O. The operation of the EBDIS bit is also influenced by the program memory mode being used. This is discussed in more detail in Section 8.5 "Program Memory Modes and the External Memory Bus".

The WAITx bits allow for the addition of Wait states to external memory operations. The use of these bits is discussed in **Section 8.3 "Wait States**".

The WMx bits select the particular operating mode used when the bus is operating in 16-Bit Data Width mode. This is discussed in more detail in **Section 8.6 "16-Bit Data Width Modes"**. These bits have no effect when an 8-Bit Data Width mode is selected.

| REGISTER 8-1: | MEMCON: EXTERNAL MEMORY BUS CONTROL REGISTER <sup>(1)</sup> |

|---------------|-------------------------------------------------------------|

| KLOISTLK 0-1. | WEWCON, EXTERNAL WEWORT DOS CONTROL REGISTER                |

| R/W-0                                                                                             | U-0         | R/W-0            | R/W-0 | U-0                                | U-0  | R/W-0              | R/W-0 |  |

|---------------------------------------------------------------------------------------------------|-------------|------------------|-------|------------------------------------|------|--------------------|-------|--|

| EBDIS                                                                                             |             | WAIT1            | WAIT0 | —                                  |      | WM1                | WM0   |  |

| bit 7                                                                                             |             |                  |       |                                    |      |                    | bit 0 |  |

|                                                                                                   |             |                  |       |                                    |      |                    |       |  |

| Legend:                                                                                           |             |                  |       |                                    |      |                    |       |  |

| R = Readable bit                                                                                  |             | W = Writable b   | oit   | U = Unimplemented bit, read as '0' |      |                    |       |  |

| -n = Value at PO                                                                                  | २           | '1' = Bit is set |       | '0' = Bit is clea                  | ared | x = Bit is unknown |       |  |

|                                                                                                   |             |                  |       |                                    |      |                    |       |  |

| bit 7 EE                                                                                          | BDIS: Exter | nal Bus Disable  | bit   |                                    |      |                    |       |  |

| 1 = External bus is enabled when microcontroller accesses external memory otherwise, all external |             |                  |       |                                    |      |                    |       |  |

|         | 1 = External bus is enabled when microcontroller accesses external memory; otherwise, all external bus drivers are mapped as I/O ports                                                                                                                                            |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 0 = External bus is always enabled, I/O ports are disabled                                                                                                                                                                                                                        |

| bit 6   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                        |

| bit 5-4 | WAIT<1:0>: Table Reads and Writes Bus Cycle Wait Count bits                                                                                                                                                                                                                       |

|         | 11 = Table reads and writes will wait 0 Tcy                                                                                                                                                                                                                                       |

|         | 10 = Table reads and writes will wait 1 Tcy                                                                                                                                                                                                                                       |

|         | 01 = Table reads and writes will wait 2 TCY                                                                                                                                                                                                                                       |

|         | 00 = Table reads and writes will wait 3 TCY                                                                                                                                                                                                                                       |

| bit 3-2 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                        |

| bit 1-0 | WM<1:0>: TBLWT Operation with 16-Bit Data Bus Width Select bits                                                                                                                                                                                                                   |

|         | 1x = Word Write mode: TABLAT word output, WRH is active when TABLAT is written<br>01 = Byte Select mode: TABLAT data is copied on both MSB and LSB, WRH and (UB or LB) will activate<br>00 = Byte Write mode: TABLAT data is copied on both MSB and LSB, WRH or WRL will activate |

|         |                                                                                                                                                                                                                                                                                   |

Note 1: This register is unimplemented on 64-pin devices, read as '0'.

# 9.0 8 x 8 HARDWARE MULTIPLIER

### 9.1 Introduction

All PIC18 devices include an 8 x 8 hardware multiplier as part of the ALU. The multiplier performs an unsigned operation and yields a 16-bit result that is stored in the product register pair, PRODH:PRODL. The multiplier's operation does not affect any flags in the STATUS register.

Making multiplication a hardware operation allows it to be completed in a single instruction cycle. This has the advantages of higher computational throughput and reduced code size for multiplication algorithms and allows PIC18 devices to be used in many applications previously reserved for digital-signal processors. A comparison of various hardware and software multiply operations, along with the savings in memory and execution time, is shown in Table 9-1.

### 9.2 Operation

Example 9-1 shows the instruction sequence for an 8 x 8 unsigned multiplication. Only one instruction is required when one of the arguments is already loaded in the WREG register.

Example 9-2 shows the sequence to do an 8 x 8 signed multiplication. To account for the sign bits of the arguments, each argument's Most Significant bit (MSb) is tested and the appropriate subtractions are done.

#### EXAMPLE 9-1: 8 x 8 UNSIGNED MULTIPLY ROUTINE

| MOVF  | ARG1, | W | ; |                |

|-------|-------|---|---|----------------|

| MULWF | ARG2  |   | ; | ARG1 * ARG2 -> |

|       |       |   | ; | PRODH:PRODL    |

#### EXAMPLE 9-2: 8 x 8 SIGNED MULTIPLY ROUTINE

| MOVF  | ARG1, W  |                  |  |

|-------|----------|------------------|--|

| MULWF | ARG2     | ; ARG1 * ARG2 -> |  |

|       |          | ; PRODH:PRODL    |  |

| BTFSC | ARG2, SB | ; Test Sign Bit  |  |

| SUBWF | PRODH, F | ; PRODH = PRODH  |  |

|       |          | ; – ARG1         |  |

| MOVF  | ARG2, W  |                  |  |

| BTFSC | ARG1, SB | ; Test Sign Bit  |  |

| SUBWF | PRODH, F | ; PRODH = PRODH  |  |

|       |          | ; – ARG2         |  |

|       |          |                  |  |

| TABLE 5-1.     | PERFORMANCE COMPARISON FOR VARIOUS MULTIPLE OPERATIONS |                   |        |          |          |          |         |  |  |  |

|----------------|--------------------------------------------------------|-------------------|--------|----------|----------|----------|---------|--|--|--|

|                |                                                        | Program           | Cycles | Time     |          |          |         |  |  |  |

| Routine        | Multiply Method                                        | Memory<br>(Words) | (Max)  | @ 64 MHz | @ 48 MHz | @ 10 MHz | @ 4 MHz |  |  |  |

| 8 x 8 Unsigned | Without Hardware Multiply                              | 13                | 69     | 4.3 μs   | 5.7 μs   | 27.6 μs  | 69 μs   |  |  |  |

| o x o onsigned | Hardware Multiply                                      | 1                 | 1      | 62.5 ns  | 83.3 ns  | 400 ns   | 1 μs    |  |  |  |

| 9 y 9 Signod   | Without Hardware Multiply                              | 33                | 91     | 5.6 μs   | 7.5 μs   | 36.4 μs  | 91 μs   |  |  |  |

| 8 x 8 Signed   | Hardware Multiply                                      | 6                 | 6      | 375 ns   | 500 ns   | 2.4 μs   | 6 μs    |  |  |  |

| 16 x 16        | Without Hardware Multiply                              | 21                | 242    | 15.1 μs  | 20.1 μs  | 96.8 μs  | 242 μS  |  |  |  |

| Unsigned       | Hardware Multiply                                      | 28                | 28     | 1.7 μs   | 2.3 μs   | 11.2 μs  | 28 μs   |  |  |  |

| 16 x 16 Signod | Without Hardware Multiply                              | 52                | 254    | 15.8 μs  | 21.2 μs  | 101.6 μs | 254 μs  |  |  |  |

| 16 x 16 Signed | Hardware Multiply                                      | 35                | 40     | 2.5 μs   | 3.3 μs   | 16.0 μs  | 40 μs   |  |  |  |

# TABLE 9-1: PERFORMANCE COMPARISON FOR VARIOUS MULTIPLY OPERATIONS

# REGISTER 10-8: PIR5: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 5

| U-0   | R/W-0    | R/W-0     | R/W-0  | U-0 | R/W-0  | R/W-0  | R/W-0  |

|-------|----------|-----------|--------|-----|--------|--------|--------|

| —     | ACTORSIF | ACTLOCKIF | TMR8IF | —   | TMR6IF | TMR5IF | TMR4IF |

| bit 7 |          |           |        |     |        |        | bit 0  |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 7          | Unimplemented: Read as '0'                                                                                                                                                        |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6          | ACTORSIF: Active Clock Tuning Out-of-Range Interrupt Flag bit<br>1 = Active clock tuning out-of-range occurred<br>0 = Active tuning out-of-range did not occur                    |

| bit 5          | ACTLOCKIF: Active Clock Tuning Lock Interrupt Flag bit<br>1 = Active clock tuning lock/unlock occurred<br>0 = Active clock tuning lock/unlock did not occur                       |

| bit 4          | <b>TMR8IF:</b> TMR8 to PR8 Match Interrupt Flag bit<br>1 = TMR8 to PR8 match occurred (must be cleared in software)<br>0 = No TMR8 to PR8 match occurred                          |

| bit 3          | Unimplemented: Read as '0'                                                                                                                                                        |

|                |                                                                                                                                                                                   |

| bit 2          | <ul> <li>TMR6IF: TMR6 to PR6 Match Interrupt Flag bit</li> <li>1 = TMR6 to PR6 match occurred (must be cleared in software)</li> <li>0 = No TMR6 to PR6 match occurred</li> </ul> |

| bit 2<br>bit 1 | 1 = TMR6 to PR6 match occurred (must be cleared in software)                                                                                                                      |

### REGISTER 10-12: PIE3: PERIPHERAL INTERRUPT ENABLE REGISTER 3

| R/W-0         | R/W-0                                        | R/W-0            | R/W-0          | R/W-0             | R/W-0            | R/W-0           | R/W-0  |  |  |

|---------------|----------------------------------------------|------------------|----------------|-------------------|------------------|-----------------|--------|--|--|

| TMR5GIE       | LCDIE                                        | RC2IE            | TX2IE          | CTMUIE            | CCP2IE           | CCP1IE          | RTCCIE |  |  |

| bit 7         |                                              |                  | •              |                   | I                | I               | bit 0  |  |  |

|               |                                              |                  |                |                   |                  |                 |        |  |  |

| Legend:       |                                              |                  |                |                   |                  |                 |        |  |  |

| R = Readabl   | e bit                                        | W = Writable     | bit            | U = Unimplem      | nented bit, read | l as '0'        |        |  |  |

| -n = Value at | POR                                          | '1' = Bit is set |                | '0' = Bit is clea | ared             | x = Bit is unkr | nown   |  |  |

|               |                                              |                  |                |                   |                  |                 |        |  |  |

| bit 7         |                                              | MR5 Gate Inter   | rupt Enable bi | t                 |                  |                 |        |  |  |

|               | 1 = Enabled<br>0 = Disabled                  |                  |                |                   |                  |                 |        |  |  |

| bit 6         | LCDIE: LCD                                   | Ready Interrup   | t Enable bit   |                   |                  |                 |        |  |  |

|               | 1 = Enabled<br>0 = Disabled                  |                  |                |                   |                  |                 |        |  |  |

| bit 5         | RC2IE: EUSART2 Receive Interrupt Enable bit  |                  |                |                   |                  |                 |        |  |  |

|               | 1 = Enabled<br>0 = Disabled                  |                  |                |                   |                  |                 |        |  |  |

| bit 4         | TX2IE: EUSART2 Transmit Interrupt Enable bit |                  |                |                   |                  |                 |        |  |  |

|               | 1 = Enabled<br>0 = Disabled                  |                  |                |                   |                  |                 |        |  |  |

| bit 3         | CTMUIE: CT                                   | MU Interrupt E   | nable bit      |                   |                  |                 |        |  |  |

|               | 1 = Enabled<br>0 = Disabled                  |                  |                |                   |                  |                 |        |  |  |

| bit 2         | CCP2IE: CC                                   | P2 Interrupt En  | able bit       |                   |                  |                 |        |  |  |

|               | 1 = Enabled                                  |                  |                |                   |                  |                 |        |  |  |

|               | 0 = Disabled                                 |                  |                |                   |                  |                 |        |  |  |

| bit 1         | CCP1IE: ECCP1 Interrupt Enable bit           |                  |                |                   |                  |                 |        |  |  |

|               | 1 = Enabled<br>0 = Disabled                  |                  |                |                   |                  |                 |        |  |  |

| bit 0         | RTCCIE: RT                                   | CC Interrupt Er  | able bit       |                   |                  |                 |        |  |  |

|               | 1 = Enabled                                  | -                |                |                   |                  |                 |        |  |  |

|               | 0 = Disabled                                 | 4                |                |                   |                  |                 |        |  |  |

# 11.12 PORTL, LATL and TRISL Registers

| Note: | PORTL    | is | available | only | on | 100-pin |

|-------|----------|----|-----------|------|----|---------|

|       | devices. |    |           |      |    |         |

PORTL is an 8-bit wide, bidirectional port. The corresponding Data Direction and Output Latch registers are TRISL and LATL.

All pins on PORTL are implemented with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

Each of the PORTL pins has a weak internal pull-up.

The pull-ups are provided to keep the inputs at a known state for the external memory interface while powering up. A single control bit can turn off all the pull-ups. This is performed by clearing bit, RLPU (PADCFG<0>).

The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on any device Reset.

#### EXAMPLE 11-11: INITIALIZING PORTL

| BANKSEL | PORTL | ; select correct bank     |

|---------|-------|---------------------------|

| CLRF    | PORTL | ; Initialize PORTL by     |

|         |       | ; clearing output latches |

| CLRF    | LATL  | ; Alternate method        |

|         |       | ; to clear output latches |

| MOVLW   | 0CFh  | ; Value used to           |

|         |       | ; initialize data         |

|         |       | ; direction               |

| MOVWF   | TRISL | ; Set RL3:RL0 as inputs   |

|         |       | ; RL5:RL4 as output       |

|         |       | ; RL7:RL6 as inputs       |

|         |       | -                         |

| Pin Name  | Function | TRIS<br>Setting | I/O | I/O Type | Description                                              |

|-----------|----------|-----------------|-----|----------|----------------------------------------------------------|

| RL0/SEG48 | RL0      | 0               | 0   | DIG      | LATL<0> data output.                                     |

|           |          | 1               | I   | ST       | PORTL<0> data input.                                     |

|           | SEG48    | 0               | 0   | ANA      | LCD Segment 48 output; disables all other pin functions. |

| RL1/SEG49 | RL1      | 0               | 0   | DIG      | LATL<1> data output.                                     |

|           |          | 1               | I   | ST       | PORTL<1> data input.                                     |

|           | SEG49    | 0               | 0   | ANA      | LCD Segment 49 output; disables all other pin functions. |

| RL2/SEG50 | RL2      | 0               | 0   | DIG      | LATL<2> data output.                                     |

|           |          | 1               | I   | ST       | PORTL<2> data input.                                     |

|           | SEG50    | 0               | 0   | ANA      | LCD Segment 50 output; disables all other pin functions. |

| RL3/SEG51 | RL3      | 0               | 0   | DIG      | LATL<3> data output.                                     |

|           |          | 1               | I   | ST       | PORTL<3> data input.                                     |

|           | SEG51    | 0               | 0   | ANA      | LCD Segment 51 output; disables all other pin functions. |

| RL4/SEG52 | RL4      | 0               | 0   | DIG      | LATL<4> data output.                                     |

|           |          | 1               | I   | ST       | PORTL<4> data input.                                     |

|           | SEG52    | 0               | 0   | ANA      | LCD Segment 52 output; disables all other pin functions. |

| RL5/SEG53 | RL5      | 0               | 0   | DIG      | LATL<5> data output.                                     |

|           |          | 1               | I   | ST       | PORTL<5> data input.                                     |

|           | SEG53    | 0               | 0   | ANA      | LCD Segment 53 output; disables all other pin functions. |

| RL6/SEG54 | RL6      | 0               | 0   | DIG      | LATL<6> data output.                                     |

|           |          | 1               | I   | ST       | PORTL<6> data input.                                     |

|           | SEG54    | 0               | 0   | ANA      | LCD Segment 54 output; disables all other pin functions. |

| RL7/SEG55 | RL7      | 0               | 0   | DIG      | LATL<7> data output.                                     |

|           |          | 1               | I   | ST       | PORTL<7> data input.                                     |

|           | SEG55    | 0               | 0   | ANA      | LCD Segment 55 output; disables all other pin functions. |

### TABLE 11-11: PORTL FUNCTIONS

Legend: O = Output, I = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Trigger Buffer Input,

x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

# 13.4 LCD Bias Types

The LCD module can be configured in one of three bias types:

- Static bias (two voltage levels: Vss and VDD)

- 1/2 bias (three voltage levels: Vss, 1/2 VDD and VDD)

- 1/3 bias (four voltage levels: Vss, 1/3 VDD, 2/3 VDD and VDD)

LCD bias voltages can be generated with internal resistor ladders, internal bias generator or external resistor ladder.

### 13.5 Internal Resistor Biasing

This mode does not use external resistors, but rather internal resistor ladders that are configured to generate the bias voltage.

The internal reference ladder actually consists of three separate ladders. Disabling the internal reference ladder disconnects all of the ladders, allowing external voltages to be supplied.

Depending on the total resistance of the resistor ladders, the biasing can be classified as low, medium or high power.

Table 13-3 shows the total resistance of each of the ladders. Table 13-3 shows the internal resister ladder connections. When the internal resistor ladder is selected, the bias voltage can either be from VDD or from VDDCORE, depending on the LCDIRS setting. It can also provide software contrast control (using LCDCST<2:0>)

| Power Mode | Nominal<br>Resistance of<br>Entire Ladder | IDD    |

|------------|-------------------------------------------|--------|

| Low        | 3 MΩ                                      | 1 µA   |

| Medium     | 300 kΩ                                    | 10 µA  |

| High       | 30 kΩ                                     | 100 µA |

#### TABLE 13-3: INTERNAL RESISTANCE LADDER POWER MODES

# 17.1.4 RTCEN BIT WRITE

RTCWREN (RTCCON1<5>) must be set before a write to RTCEN can take place. Any write to the RTCEN bit, while RTCWREN = 0, will be ignored.

Like the RTCEN bit, the RTCVALH and RTCVALL registers can only be written to when RTCWREN = 1. A write to these registers, while RTCWREN = 0, will be ignored.

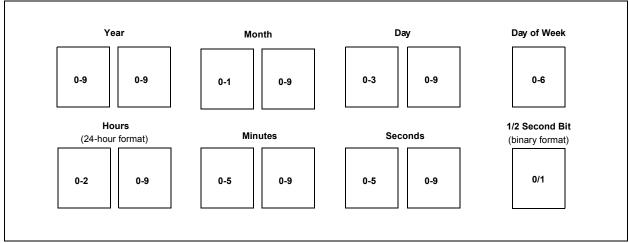

### FIGURE 17-2: TIMER DIGIT FORMAT

# 17.2 Operation

#### 17.2.1 REGISTER INTERFACE

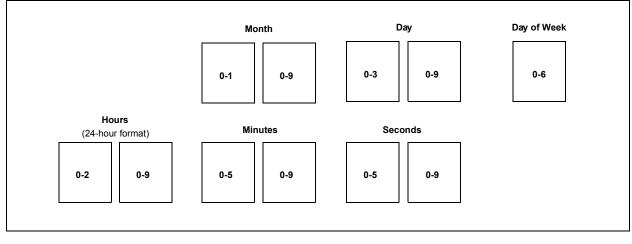

The register interface for the RTCC and alarm values is implemented using the Binary Coded Decimal (BCD) format. This simplifies the firmware when using the module, as each of the digits is contained within its own 4-bit value (see Figure 17-2 and Figure 17-3).

### FIGURE 17-3: ALARM DIGIT FORMAT

#### 20.3.7 SLAVE MODE

In Slave mode, the data is transmitted and received as the external clock pulses appear on SCKx. When the last bit is latched, the SSPxIF interrupt flag bit is set.

While in Slave mode, the external clock is supplied by the external clock source on the SCKx pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. When a byte is received, the device can be configured to wake-up from Sleep.

#### 20.3.8 SLAVE SELECT SYNCHRONIZATION

The  $\overline{SSx}$  pin allows a Synchronous Slave mode. The SPI must be in Slave mode with the  $\overline{SSx}$  pin control enabled (SSPxCON1<3:0> = 04h). When the  $\overline{SSx}$  pin is low, transmission and reception are enabled and the SDOx pin is driven. When the  $\overline{SSx}$  pin goes high, the SDOx pin is no longer driven, even if in the middle of a

transmitted byte and becomes a floating output. External pull-up/pull-down resistors may be desirable depending on the application.

| Note: | When the SPI is in Slave mode with                                                       |

|-------|------------------------------------------------------------------------------------------|

|       | SSx pin control enabled                                                                  |

|       | (SSPxCON1<3:0> = 0100), the SPI                                                          |

|       | module will reset if the $\overline{SSx}$ pin is set to VDD.                             |

|       | If the SPI is used in Slave mode with CKE set, then the SSx pin control must be enabled. |

When the SPI module resets, the bit counter is forced to '0'. This can be done by either forcing the SSx pin to a high level or clearing the SSPEN bit.

To emulate two-wire communication, the SDOx pin can be connected to the SDIx pin. When the SPI needs to operate as a receiver, the SDOx pin can be configured as an input. This disables transmissions from the SDOx. The SDIx can always be left as an input (SDIx function) since it cannot create a bus conflict.

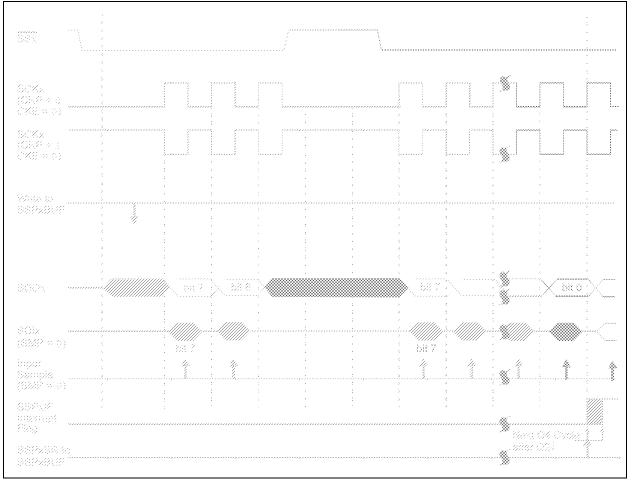

### FIGURE 20-4: SLAVE SYNCHRONIZATION WAVEFORM

#### 20.5.9 MASTER MODE

Master mode is enabled by setting and clearing the appropriate SSPMx bits in SSPxCON1, and by setting the SSPEN bit. In Master mode, the SCLx and SDAx lines are manipulated by the MSSPx hardware if the TRIS bits are set.

The Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSPx module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is Idle, with both the S and P bits clear.

In Firmware Controlled Master mode, user code conducts all  $I^2C$  bus operations based on Start and Stop bit conditions.

Once Master mode is enabled, the user has six options.

- 1. Assert a Start condition on SDAx and SCLx.

- 2. Assert a Repeated Start condition on SDAx and SCLx.

- 3. Write to the SSPxBUF register initiating transmission of data/address.

- 4. Configure the I<sup>2</sup>C port to receive data.

- 5. Generate an Acknowledge condition at the end of a received byte of data.

- 6. Generate a Stop condition on SDAx and SCLx.

- Note: The MSSPx module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPxBUF register to initiate transmission before the Start condition is complete. In this case, the SSPxBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPxBUF did not occur.

The following events will cause the MSSPx Interrupt Flag bit, SSPxIF, to be set (and MSSPx interrupt if enabled):

- Start condition

- Stop condition

- Data transfer byte transmitted/received

- · Acknowledge transmitted

- Repeated Start

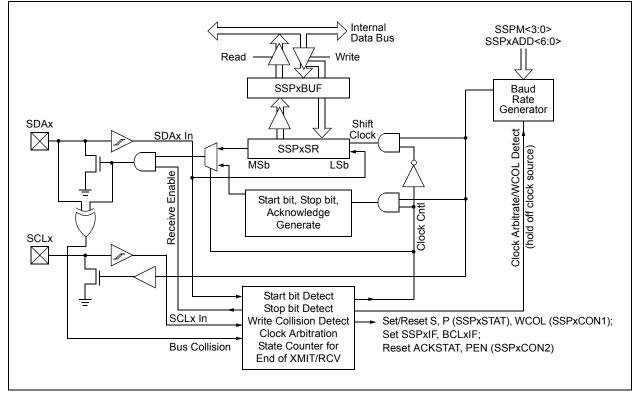

# FIGURE 20-18: MSSPx BLOCK DIAGRAM (I<sup>2</sup>C MASTER MODE)

| BRG Value                | XXXXh         | 0000h                                     | ////////////////////////////////////// |

|--------------------------|---------------|-------------------------------------------|----------------------------------------|

| RXx Pin                  |               | Edge #1 Edge #<br>Start Bit 0 Bit 1 Bit 2 |                                        |

| BRG Clock                |               | www.www.www                               |                                        |

| ABDEN bit                | Set by User - |                                           | Auto-Cleared                           |

| RCxIF bit<br>(Interrupt) |               |                                           |                                        |

| Read<br>RCREGx           |               |                                           |                                        |

| SPBRGx                   |               | XXXXh                                     | ↓                                      |

| SPBRGHx                  |               | XXXXh                                     | <u>х 00h</u>                           |

#### FIGURE 21-2: BRG OVERFLOW SEQUENCE

| BRG Clock  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ABDEN bit  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| RXx Pin    | Start Bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ABDOVF bit |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| BRG Value  | XXXxh         0000h         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X |

# REGISTER 22-6: ADCON2H: A/D CONTROL REGISTER 2 HIGH

| R/W-0        | R/W-0                                                                                                                                                                                         | R/W-0                                                                                       | R/W-0           | R/W-0                                     | R/W-0           | U-0      | U-0   |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------|-------------------------------------------|-----------------|----------|-------|

| PVCFG1       | PVCFG0                                                                                                                                                                                        | NVCFG0                                                                                      | OFFCAL          | BUFREGEN                                  | CSCNA           |          | —     |

| bit 7        | •                                                                                                                                                                                             | •                                                                                           |                 |                                           |                 | •        | bit 0 |

| Legend:      |                                                                                                                                                                                               |                                                                                             |                 |                                           |                 |          |       |

| R = Readab   | ole bit                                                                                                                                                                                       | W = Writable I                                                                              | oit             | U = Unimplem                              | ented bit, read | l as '0' |       |

| -n = Value a | at POR                                                                                                                                                                                        | '1' = Bit is set                                                                            |                 | '0' = Bit is cleared x = Bit is unki      |                 |          | Iown  |

|              | <b>PVCFG&lt;1:0&gt;:</b> Converter Positive Voltage Reference Configuration bits<br>1x =Unimplemented, do not use<br>01 =External VREF+<br>00 =AVDD                                           |                                                                                             |                 |                                           |                 |          |       |

| bit 5        |                                                                                                                                                                                               | <b>NVCFG0:</b> Converter Negative Voltage Reference Configuration bit<br>1 = External VREF- |                 |                                           |                 |          |       |

| bit 4        | 1 = Inverting                                                                                                                                                                                 |                                                                                             | ng inputs of cl | bit<br>hannel Sample-a<br>hannel Sample-a |                 |          |       |

| bit 3        | <b>BUFREGEN:</b> A/D Buffer Register Enable bit<br>1 = Conversion result is loaded into the buffer location determined by the converted channel<br>0 = A/D result buffer is treated as a FIFO |                                                                                             |                 |                                           |                 |          |       |

| bit 2        | <b>CSCNA:</b> Scan Input Selections for CH0+ During Sample A bit<br>1 = Scans inputs<br>0 = Does not scan inputs                                                                              |                                                                                             |                 |                                           |                 |          |       |

| bit 1-0      | Unimplemer                                                                                                                                                                                    | •                                                                                           |                 |                                           |                 |          |       |

The LPENA bit (ADCON5H<6>) allows Threshold Detect to function with a low-power feature. By design, Threshold Detect can perform comparison operations when the device is in Sleep or Idle modes, waking the CPU when it generates an interrupt. Setting LPENA configures the device to return to low-power operation after the interrupt has been serviced.

The Compare Mode bits, CM<1:0> (ADCON5L<1:0>), select the type of comparison to be performed. Four types are available:

- The result of the current conversion is greater than a reference threshold

- The result of the current conversion is less than a reference threshold

- The result of the current conversion is between two predefined thresholds ("Inside Window")

- The result of the current conversion is outside of the predefined thresholds ("Outside Window")

The Write Mode bits, WM<1:0> (ADCON5L<3:2>), determine the disposition of the conversion. Three options are available:

- Discard the conversion after the comparison has been performed

- Store the conversion after the comparison has been performed

- Store the conversion without comparison (Legacy mode)

#### 22.7.1.1 Buffer Operation And Comparisons

For Buffer Write modes that involve storing conversions (WM<1:0> = 0x), the BUFM and BUFREGEN bits control how the buffer functions (as a channel indexed, single FIFO or split FIFO buffer). However, when the compare and store option is selected (WM<1:0> = 01), using a FIFO mode may overwrite the buffers of other channels and cause unpredictable comparison results. For that reason, always use Channel Indexed Buffer mode (BUFREGEN = 1) when using the compare and store option.

#### 22.7.1.2 Buffer Operation In Windowed Comparisons (Channel Mirroring)

The use of windowed comparisons changes the available options for the results buffer. To accommodate the storage of two threshold values, the buffer is automatically split into halves, similar to Split FIFO mode. Buffer addresses in each half are paired, with the lowest address in one buffer, matched to the buffer address in the upper half. (For example, in a 16-word buffer, ADC-BUF0 is paired with ADCBUF9, ADCBUF1 is paired with ADCBUF10, and so on.) This pairing is referred to as "channel mirroring". Mirroring can obviously be applied only to the lower A/ D channels; for most devices, this corresponds to the lower half of the external analog channels. This does not mean that those buffer locations cannot be used for other purposes. However, storing any other data in a particular buffer location, where channel mirroring is being used, may result in misleading comparison evaluations.

#### 22.7.2 SETTING COMPARISON THRESHOLDS

The comparison thresholds for Threshold Detect are set by writing the desired values to an appropriate location in the A/D results buffer. This can only be done when the module is deactivated (ADCON1H<7> = 0).

The location of the threshold is determined by the comparison type. For simple greater than, and less than, comparisons, the value is written to the buffer location corresponding to the input channel to be monitored. For example, if AN0 is to be monitored for a voltage over a certain level, the ceiling threshold is stored in ADCBUF0.

The location of the thresholds for windowed comparisons are written to two addresses. The lower value is written to the address corresponding to the monitored channel. The upper value is stored in the corresponding mirrored address in the upper half of the buffer. To expand on the previous example, if the conversion on AN0 is to be a windowed comparison, the floor threshold is stored in ADCBUF0, while the ceiling threshold is stored in ADCBUF9.

# 22.7.3 COMPARE HIT REGISTERS

To determine if a particular event has occurred, the A/ D module uses two registers to record match events. These registers are referred to as the Compare Hit registers and are designated, ADCHIT1H/L and ADCHIT0H/L. The registers map their individual bits sequentially to each of the (up to) 32 analog channels. If a particular channel in a device is not implemented, the corresponding Compare Hit bit (CHHn) is not implemented.

Each bit serves as an event semaphore for its corresponding channel. When the programmed event occurs on that channel, the bit becomes set and stays set until it is cleared by the application. It is the user's responsibility to clear the bits after the application has evaluated them.

Depending on the event, more than one Compare Hit bit may be set. The significance of a set bit must be interpreted by the application in the context of the Compare mode selected. Particular examples are covered in **Section 22.7.5 "Comparison Mode Examples"**.

#### 22.7.4 THRESHOLD DETECT INTERRUPTS

The A/D module can generate an interrupt and set the ADIF flag based on Threshold Detect operation. This is based on completion of a Threshold Detect sequence and/or the occurrence of a valid comparison. When Threshold Detect is enabled (ASENA = 1), A/D module interrupt generation is governed by the ASINTMDx bits (ADCON5H<1:0>), superseding any configuration implemented by the SMPIx bits (ADCON2L<6:2>). For information on alternative interrupt settings, refer to Section 22.6.1 "Number of Conversions Per Interrupt".

The Threshold Detect interrupt is configured by the ASINTMD<1:0> bits (ADCON5H<1:0>). Options include interrupt after a scan sequence, interrupt after a scan sequence with a valid match, interrupt after a valid match (without waiting for the sequence to end) or no interrupt.

#### 22.7.5 COMPARISON MODE EXAMPLES

The following examples show the effect of valid comparisons on the results buffer and the

Compare Hit registers. In each figure, changes within the registers are indicated in bold.

For the sake of simplicity, the examples assume a device with only 16 analog inputs. Devices with a greater number of channels, and thus, larger results buffers and two Compare Hit registers, will function in a similar fashion.

| Note: | When using any comparison mode,         |

|-------|-----------------------------------------|

|       | always use channel indexed buffer       |

|       | storage (BUFREGEN = 1). Otherwise,      |

|       | the threshold values for other channels |

|       | may be overwritten, resulting in        |

|       | unpredictable comparisons.              |

# 22.7.5.1 Simple Comparisons (Greater And Less Than Results)

When the Compare Mode bits, CM<1:0> (ADCON5L<1:0>), are programmed as '0x', the converter compares the sampled value to see if it is greater than (CM<1:0> = 01), or less than (CM<1:0> = 00), the threshold value in the buffer location. If the condition is met, both of the following occur:

- The Compare Hit bit (CHHn) for the corresponding channel is set.

- If the Write Mode bits, WM<1:0>

(ADCON5L<3:2>), are programmed to '01', the

converted value is written to the buffer, replacing

the threshold value. If WM<1:0> = 10, the

converted value is discarded.

The changes to the result buffer and the Compare Hit register are shown in Figure 22-13. Note that they are the same for both types of simple comparison.

The PPBRST bit (UCON<6>) controls the Reset status when Double-Buffering mode (ping-pong buffering) is used. When the PPBRST bit is set, all Ping-Pong Buffer Pointers are set to the Even buffers. PPBRST has to be cleared by firmware. This bit is ignored in buffering modes not using ping-pong buffering.

The PKTDIS bit (UCON<4>) is a flag indicating that the SIE has disabled packet transmission and reception. This bit is set by the SIE when a SETUP token is received to allow setup processing. This bit cannot be set by the microcontroller, only cleared; clearing it allows the SIE to continue transmission and/or reception. Any pending events within the Buffer Descriptor Table (BDT) will still be available, indicated within the USTAT register's FIFO buffer.

The RESUME bit (UCON<2>) allows the peripheral to perform a remote wake-up by executing resume signaling. To generate a valid remote wake-up, firmware must set RESUME for 10 ms and then clear the bit. For more information on resume signaling, see Sections 7.1.7.5, 11.4.4 and 11.9 in the "USB 2.0 Specification".

The SUSPND bit (UCON<1>) places the module and supporting circuitry in a Low-Power mode. The input clock to the SIE is also disabled. This bit should be set by the software in response to an IDLEIF interrupt. It should be reset by the microcontroller firmware after an ACTVIF interrupt is observed. When this bit is active, the device remains attached to the bus but the transceiver outputs remain Idle. The voltage on the VUSB3V3 pin may vary depending on the value of this bit. Setting this bit before a IDLEIF request will result in unpredictable bus behavior.

**Note:** While in Suspend mode, a typical buspowered USB device is limited to 2.5 mA of current. This is the complete current which may be drawn by the PIC MCU device and its supporting circuitry. Care should be taken to assure minimum current draw when the device enters Suspend mode.

### 27.2.2 USB CONFIGURATION REGISTER (UCFG)

Prior to communicating over USB, the module's associated internal and/or external hardware must be configured. Most of the configuration is performed with the UCFG register (Register 27-2).The UFCG register contains most of the bits that control the system-level behavior of the USB module. These include:

- Bus Speed (full speed versus low speed)

- On-Chip Pull-up Resistor Enable

- On-Chip Transceiver Enable

- Ping-Pong Buffer Usage

The UCFG register also contains two bits, which aid in module testing, debugging and USB certifications. These bits control output enable state monitoring and eye pattern generation.

| Note: | The USB speed, transceiver and pull-up should only be configured during the module setup phase. It is not recom- |

|-------|------------------------------------------------------------------------------------------------------------------|

|       | mended to switch these settings while the module is enabled.                                                     |

### 27.2.2.1 Internal Transceiver

The USB peripheral has a built-in, "USB 2.0 Specification", full-speed and low-speed capable transceiver, internally connected to the SIE. This feature is useful for low-cost, single chip applications. The UTRDIS bit (UCFG<3>) controls the transceiver; it is enabled by default (UTRDIS = 0). The FSEN bit (UCFG<2>) controls the transceiver speed; setting this bit enables full-speed operation.

The on-chip USB pull-up resistors are controlled by the UPUEN bit (UCFG<4>). They can only be selected when the on-chip transceiver is enabled.

The internal USB transceiver obtains power from the VUSB3V3 pin. In order to meet USB signalling level specifications, VUSB3V3 must be supplied with a voltage source between 3.0V and 3.6V. The best electrical signal quality is obtained when a 3.3V supply is used and locally bypassed with a high quality ceramic capacitor (ex: 0.1  $\mu$ F). The capacitor should be placed as close as possible to the VUSB3V3 and VSS pins.

VUSB3V3 should always be maintained  $\geq$  VDD. If the USB module is not used, but RC4 or RC5 are used as general purpose inputs, VUSB3V3 should still be connected to a power source (such as VDD). The input thresholds for the RC4 and RC5 pins are dependent upon the VUSB3V3 supply level.

The D+ and D- signal lines can be routed directly to their respective pins on the USB connector or cable (for hard-wired applications). No additional resistors, capacitors or magnetic components are required, as the D+ and D- drivers have controlled slew rate and output impedance, intended to match with the characteristic impedance of the USB cable.