Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                       |

| Peripherals                | Brown-out Detect/Reset, HLVD, LCD, POR, PWM, WDT                           |

| Number of I/O              | 52                                                                         |

| Program Memory Size        | 128KB (64K x 16)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                  |

| Data Converters            | A/D 16x10b/12b                                                             |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 64-QFN (9x9)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f67j94-i-mr |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### REGISTER 3-8: REFOXCON2: REFERENCE CLOCK OUTPUT CONTROL REGISTER 2

| R/W-0 <sup>(1)</sup> | R/W -0 <sup>(1)</sup> | R/W -0 <sup>(1)</sup> |

|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|-----------------------|-----------------------|

| RODIV7               | RODIV6               | RODIV5               | RODIV4               | RODIV3               | RODIV2               | RODIV1                | RODIV0                |

| bit 7                |                      |                      |                      |                      |                      |                       | bit 0                 |

| Legend:                  |                  |                            |                    |

|--------------------------|------------------|----------------------------|--------------------|

| R = Readable bit         | W = Writable bit | U = Unimplemented bit, rea | ad as '0'          |

| -n = Value at all Resets | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 7-0 **RODIV<7:0>:** Reference Clock Output Divider bits<sup>(1)</sup> Reserved for expansion of RODIV<15>.

#### REGISTER 3-9: REFOXCON3: REFERENCE CLOCK OUTPUT CONTROL REGISTER 3

| U-0   | R/W-0 <sup>(1)</sup> |

|-------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| —     | RODIV14              | RODIV13              | RODIV12              | RODIV11              | RODIV10              | RODIV9               | RODIV8               |

| bit 7 |                      |                      |                      |                      |                      |                      | bit 0                |

| Legend:                  |                  |                             |                    |

|--------------------------|------------------|-----------------------------|--------------------|

| R = Readable bit         | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at all Resets | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 7 Unimplemented: Read as '0'

| bit 6-0 | <b>RODIV&lt;14:8&gt;:</b> Reference Clock Output Divider bits <sup>(1)</sup><br>Used in conjunction with RODIV<7:0> to specify clock divider frequency.                   |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 11111111111111 = REFO clock is base clock frequency divided by 65,534 (32,767 * 2)<br>111111111111110 = REFO clock is base clock frequency divided by 65,532 (32,766 * 2) |

|         | •                                                                                                                                                                         |

|         | •                                                                                                                                                                         |

|         | 0000000000011 = REFO clock is base clock frequency divided by 6 (3 * 2)                                                                                                   |

|         | 00000000000000000000000000000000000000                                                                                                                                    |

|         | 00000000000000 = REFO clock is the same frequency as the base clock (no divider)                                                                                          |

### **Note 1:** The RODIV register field should not be written while the ACTIVE (REFOxCON<0>) bit is '1'; undefined behavior will result.

**Note 1:** The RODIV register field should not be written while the ACTIVE (REFOxCON<0>) bit is '1'; Undefined behavior will result.

#### REGISTER 4-1: DSCONL: DEEP SLEEP CONTROL REGISTER LOW

| U-0   | U-0 | U-0 | U-0 | U-0 | R-0 | R/W-0, HSC           | R/W-0, HS              |

|-------|-----|-----|-----|-----|-----|----------------------|------------------------|

|       | —   | _   | —   | —   | r   | DSBOR <sup>(1)</sup> | RELEASE <sup>(1)</sup> |

| bit 7 |     |     |     |     |     |                      | bit 0                  |

|       |     |     |     |     |     |                      |                        |

| Legend:                | r = Reserved bit | HSC = Hardware Settable | HSC = Hardware Settable/Clearable bit |  |  |

|------------------------|------------------|-------------------------|---------------------------------------|--|--|

| R = Readable bit       | W = Writable bit | U = Unimplemented bit,  | U = Unimplemented bit, read as '0'    |  |  |

| -n = Value at POR      | '1' = Bit is set | '0' = Bit is cleared    | x = Bit is unknown                    |  |  |

| HS = Hardware Settable | bit              |                         |                                       |  |  |

| bit 7-3 | Unimplemented: Read as '0' |

|---------|----------------------------|

|---------|----------------------------|

bit 2 Reserved: Maintained as '0'

bit 1 **DSBOR:** Deep Sleep BOR Event Status bit<sup>(1)</sup> 1 = DSBOR was enabled and VDD dropped below the DSBOR threshold during Deep Sleep<sup>(2)</sup> 0 = DSBOR disabled while device is in Deep Sleep mode

- bit 0 **RELEASE:** I/O Pin State Release bit<sup>(1)</sup> Upon waking from Deep Sleep, the I/O pins maintain their previous states. Clearing this bit will release the I/O pins and allow their respective TRIS and LAT bits to control their states.

- **Note 1:** This is the value when VDD is initially applied.

- 2: Unlike all other events, a Deep Sleep BOR event will not cause a wake-up from Deep Sleep; this bit is present only as a Status bit.

| R/W-0               | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0, HS <sup>(2)</sup> |

|---------------------|-----|-----|-----|-----|-----|-----|--------------------------|

| DSEN <sup>(1)</sup> | —   | _   | —   | —   | —   | -   | RTCCWDIS                 |

| bit 7               |     |     |     |     |     |     | bit 0                    |

|                     |     |     |     |     |     |     |                          |

#### REGISTER 4-2: DSCONH: DEEP SLEEP CONTROL REGISTER HIGH

| Legend:           | HS = Hardware Settable bit |                            |                    |

|-------------------|----------------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, rea | id as '0'          |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared       | x = Bit is unknown |

| bit 7 <b>DSEN:</b> Deep Sleep Mode Enable bit <sup>(1)</sup> |  |

|--------------------------------------------------------------|--|

|--------------------------------------------------------------|--|

- 1 = Deep Sleep mode is enabled and device will enter Deep Sleep mode when the SLEEP instruction is executed

- 0 = Deep Sleep mode is not enabled

- bit 6-1 Unimplemented: Read as '0'

bit 0 RTCCWDIS: RTCC Wake-up Disable bit<sup>(2)</sup>

- 1 = Wake-up from RTCC is disabled

- 0 = Wake-up from RTCC is enabled

- **Note 1:** In order to enter Deep Sleep, DSEN must be written to in two separate operations. The write operations do not need to be consecutive. Before writing DSEN, the DSCON1 register should be cleared twice.

- 2: This is the value when VDD is initially applied.

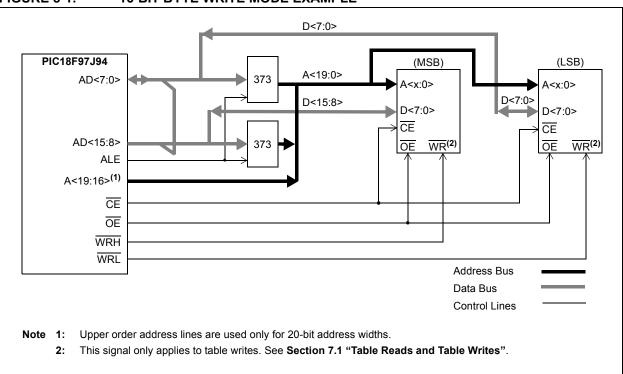

#### 8.6.1 16-BIT BYTE WRITE MODE

Figure 8-1 shows an example of 16-Bit Byte Write mode for PIC18FXXJ94 devices. This mode is used for two separate 8-bit memories connected for 16-bit operation. This generally includes basic EPROM and Flash devices. It allows table writes to byte-wide external memories. During a TBLWT instruction cycle, the TABLAT data is presented on the upper and lower bytes of the AD<15:0> bus. The appropriate WRH or WRL control line is strobed on the LSb of the TBLPTR.

#### FIGURE 8-1: 16-BIT BYTE WRITE MODE EXAMPLE

| R/W-0         | R/W-0                                                                                                             | R-0                                                                                                                             | R-0                                             | R/W-0                      | R/W-0           | R/W-0           | R/W-0  |

|---------------|-------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|----------------------------|-----------------|-----------------|--------|

| TMR5GIF       | LCDIF                                                                                                             | RC2IF                                                                                                                           | TX2IF                                           | CTMUIF                     | CCP2IF          | CCP1IF          | RTCCIF |

| bit 7         | •                                                                                                                 | 1                                                                                                                               |                                                 |                            |                 | 1               | bit (  |

| Legend:       |                                                                                                                   |                                                                                                                                 |                                                 |                            |                 |                 |        |

| R = Readable  | e bit                                                                                                             | W = Writable                                                                                                                    | bit                                             | U = Unimpler               | nented bit, rea | d as '0'        |        |

| -n = Value at | POR                                                                                                               | '1' = Bit is set                                                                                                                |                                                 | '0' = Bit is cle           | ared            | x = Bit is unkr | nown   |

| bit 7         | 1 = TMR ga                                                                                                        | MR5 Gate Inter<br>te interrupt occu<br>gate occurred                                                                            |                                                 | e cleared in soft          | ware)           |                 |        |

| bit 6         | LCDIF: LCD<br>1 = A write is                                                                                      | Interrupt Flag b<br>s allowed to the<br>s not allowed to                                                                        | Segment Data                                    | •                          |                 |                 |        |

| bit 5         | <b>RC2IF:</b> EUS<br>1 = The EU                                                                                   | ART2 Receive I<br>SART2 receive I<br>SART2 receive I                                                                            | nterrupt Flag                                   | bit<br>G2, is full (cleare | ed when RCRE    | EG2 is read)    |        |

| bit 4         | 1 = The EU                                                                                                        | ART2 Transmit I<br>SART2 transmit<br>SART2 transmit                                                                             | buffer, TXRE                                    |                            | eared when T>   | KREG2 is writte | n)     |

| bit 3         | 1 = CTMU i                                                                                                        | TMU Interrupt Fla<br>nterrupt occurre<br>1U interrupt occu                                                                      | d (must be cle                                  | eared in softwar           | e)              |                 |        |

| bit 2         | Capture mod           1 = A TMR1           0 = No TMR           Compare mod           1 = A TMR1                  | I/TMR3 register<br>R1/TMR3 registe<br>2 <u>ode:</u><br>I/TMR3 register<br>R1/TMR3 registe                                       | capture occur<br>r capture occu<br>compare mate | urred<br>ch occurred (mu   |                 |                 |        |

| bit 1         | Unused in the<br>CCP1IF: EC<br><u>Capture moo</u><br>1 = A TMR1<br>0 = No TMF<br><u>Compare moo</u><br>1 = A TMR1 | is mode.<br>CP1 Interrupt Fl<br>de:<br>I/TMR3 register<br>A1/TMR3 registe<br><u>ode:</u><br>I/TMR3 register<br>A1/TMR3 register | capture occur<br>r capture occu<br>compare mate | urred<br>ch occurred (mu   |                 |                 |        |

| bit 0         | Unused in th<br>RTCCIF: RT<br>1 = RTCC in                                                                         |                                                                                                                                 | d (must be cle                                  | ared in software           | e)              |                 |        |

#### REGISTER 10-6: PIR3: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 3

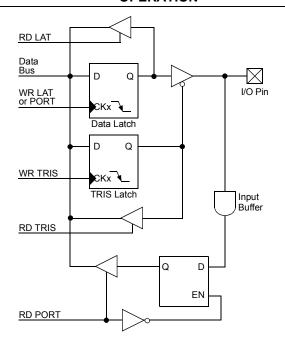

#### 11.0 I/O PORTS

Depending on the device selected and features enabled, there are up to eleven ports available. Some pins of the I/O ports are multiplexed with an alternate function from the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Each port has three memory mapped registers for its operation:

- TRIS register (Data Direction register)

- PORT register (reads the levels on the pins of the device)

- LAT register (Output Latch register)

Reading the PORT register reads the current status of the pins, whereas writing to the PORT register, writes to the Output Latch (LAT) register.

Setting a TRIS bit (= 1) makes the corresponding PORT pin an input (putting the corresponding output driver in a High-Impedance mode). Clearing a TRIS bit (= 0) makes the corresponding port pin an output (i.e., driving the contents of the corresponding LAT bit on the selected pin).

The Output Latch (LAT register) is useful for readmodify-write operations on the value that the I/O pins are driving. Read-modify-write operations on the LAT register read and write the latched output value for the PORT register.

A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 11-1.

FIGURE 11-1: GENERIC I/O PORT OPERATION

#### 11.1 I/O Port Pin Capabilities

When developing an application, the capabilities of the port pins must be considered.

The Absolute Maximum Ratings of the I/O pins are as follows:

- RA2, RA3 = -300mV to (VDD + 300 mV)

- RA6, RA7, RC0, RC1 = -300 mV to (VDD +300 mV)<sup>(1)</sup>

- RF3/RF4 (the USB D+/D- pins) = supports "USB specific levels" (e.g.: -1.0V to +4.6V, but only when the external source impedance is >/= 28 ohms, and the VUSB3V3 pin voltage is >/= 3.0V, otherwise: -500 mV to (VUSB3V3 +500 mV)

- All other general purpose I/O pins (including  $\overline{\text{MCLR}}$ ), when VDD is < 2.0V: -300 mV to +4.0V.

- All other general purpose I/O pins (including MCLR), when VDD is >= 2.0V: -300 mV to +6.0V<sup>(2)</sup>.

- Note 1: When the pins are used to drive a crystal or ceramic resonator, natural oscillation waveforms slightly exceeding the -300 mV to (VDD +300 mV) range may sometimes occur, and if present, such waveforms are allowed. If these pins are instead used as general purpose inputs, the external driving source should adhere to the -300 mV to (VDD +300 mV) specification.

- 2: In addition to the above absolute maximums, any I/O pin voltage that is actively selected at runtime by the ADC channel select MUX must also meet the VAIN requirements (parameter A25 in Table 30-40).

| REGISTER 12-3: | MDCARH: MODULATION CARRIER HIGH CONTROL REGISTER |

|----------------|--------------------------------------------------|

|----------------|--------------------------------------------------|

| R/W-x           | R/W-x                                                                                                                                      | R/W-x                                      | U-0          | R/W-x                | R/W-x                | R/W-x                | R/W-x                |  |  |  |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--------------|----------------------|----------------------|----------------------|----------------------|--|--|--|--|

| MDCHODIS        | MDCHPOL                                                                                                                                    | MDCHSYNC                                   | _            | MDCH3 <sup>(1)</sup> | MDCH2 <sup>(1)</sup> | MDCH1 <sup>(1)</sup> | MDCH0 <sup>(1)</sup> |  |  |  |  |

| bit 7           |                                                                                                                                            | · · ·                                      |              |                      |                      |                      | bit                  |  |  |  |  |

| Legend:         |                                                                                                                                            |                                            |              |                      |                      |                      |                      |  |  |  |  |

| R = Readable    | bit                                                                                                                                        | W = Writable bit                           |              | U = Unimplen         | nented bit, read     | 1 as '0'             |                      |  |  |  |  |

| -n = Value at P | OR                                                                                                                                         | '1' = Bit is set                           |              | '0' = Bit is clea    | ared                 | x = Bit is unkr      | nown                 |  |  |  |  |

| bit 7           | MDCHODIS:                                                                                                                                  | Modulator Carrie                           | r High Out   | put Disable bit      |                      |                      |                      |  |  |  |  |

|                 |                                                                                                                                            | ignal driving the p<br>ignal driving the p |              |                      |                      |                      |                      |  |  |  |  |

| bit 6           | •                                                                                                                                          | Vodulator Carrier                          | •            |                      | ,                    | ,                    |                      |  |  |  |  |

|                 |                                                                                                                                            | Carrier High sigr                          | -            | -                    |                      |                      |                      |  |  |  |  |

|                 | 0 = Selected                                                                                                                               | Carrier High sigr                          | al is not in | verted               |                      |                      |                      |  |  |  |  |

| bit 5           |                                                                                                                                            | : Modulator Carrie                         | • •          |                      |                      |                      |                      |  |  |  |  |

|                 | 1 = Modulator waits for a falling edge on the Carrier High time signal before allowing a switch to the<br>Carrier Low time                 |                                            |              |                      |                      |                      |                      |  |  |  |  |

|                 |                                                                                                                                            | ow time<br>or output is not sy             | nchronized   | to the Carrier H     | liah time siana      | ı(1)                 |                      |  |  |  |  |

| bit 4           |                                                                                                                                            |                                            |              |                      | light time signa     | 1                    |                      |  |  |  |  |

| bit 3-0         | Unimplemented: Read as '0'                                                                                                                 |                                            |              |                      |                      |                      |                      |  |  |  |  |

| bit 3-0         | <b>MDCH&lt;3:0&gt;:</b> Modulator Data Carrier High Selection bits <sup>(1)</sup><br>1111 = Reference Clock Output Module 2 (REFO2) signal |                                            |              |                      |                      |                      |                      |  |  |  |  |

|                 | 1111 = Reference Clock Output Module 2 (REFO2) signal<br>1110 = System clock                                                               |                                            |              |                      |                      |                      |                      |  |  |  |  |

|                 | 1101 = CCP10 output (PWM Output mode only)                                                                                                 |                                            |              |                      |                      |                      |                      |  |  |  |  |

|                 | 1100 = CCP9 output (PWM Output mode only)                                                                                                  |                                            |              |                      |                      |                      |                      |  |  |  |  |

|                 | 1011 = CCP8 output (PWM Output mode only)<br>1010 = CCP7 output (PWM Output mode only)                                                     |                                            |              |                      |                      |                      |                      |  |  |  |  |

|                 |                                                                                                                                            | 6 output (PWM O                            |              | • •                  |                      |                      |                      |  |  |  |  |

|                 |                                                                                                                                            | 5 output (PWM O                            |              |                      |                      |                      |                      |  |  |  |  |

|                 |                                                                                                                                            | 4 output (PWM O                            |              |                      |                      |                      |                      |  |  |  |  |

|                 |                                                                                                                                            | P3 output (PWM (<br>P2 output (PWM (       |              |                      |                      |                      |                      |  |  |  |  |

|                 |                                                                                                                                            | P1 output (PWM (                           |              |                      |                      |                      |                      |  |  |  |  |

|                 |                                                                                                                                            | ence Clock Outp                            | ut Module    | 1 (REFO1) sign       | al                   |                      |                      |  |  |  |  |

|                 | 0010 = MDC                                                                                                                                 | •                                          |              |                      |                      |                      |                      |  |  |  |  |

|                 | 0001 = MDC                                                                                                                                 | INI1 nin                                   |              |                      |                      |                      |                      |  |  |  |  |

Note 1: Narrowed carrier pulse widths or spurs may occur in the signal stream during transitions.

### 17.1 RTCC MODULE REGISTERS

The RTCC module registers are divided into the following categories:

#### **RTCC Control Registers**

- RTCCON1

- RTCCON2

- RTCCAL

- PADCFG

- ALRMCFG

- ALRMRPT

#### **RTCC Value Registers**

- RTCVALH

- RTCVALL

- Both registers access the following registers:

- YEAR

- MONTH

- DAY

- WEEKDAY

- HOUR

- MINUTE

- SECOND

#### **Alarm Value Registers**

- ALRMVALH

- ALRMVALL Both registers access the following registers:

- ALRMMNTH

- ALRMDAY

- ALRMWD

- ALRMHR

- ALRMMIN

- ALRMSEC

- Note: The RTCVALH and RTCVALL registers can be accessed through RTCRPT<1:0> (RTCCON1<1:0>). ALRMVALH and ALRMVALL can be accessed through ALRMPTR<1:0> (ALRMCFG<1:0>).

| R/W-0         | R/W-0                                       | U-0                                                 | R/W-0                                                                      | R/W-0                            | R/W-0              | R/W-0           | R/W-1 |

|---------------|---------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------|----------------------------------|--------------------|-----------------|-------|

| CMPL1         | CMPL0                                       | _                                                   | STRSYNC                                                                    | STRD                             | STRC               | STRB            | STRA  |

| bit 7         |                                             |                                                     |                                                                            |                                  |                    |                 | bit 0 |

| Legend:       |                                             |                                                     |                                                                            |                                  |                    |                 |       |

| R = Readabl   | e bit                                       | W = Writable                                        | e bit                                                                      | U = Unimpler                     | nented bit, rea    | d as '0'        |       |

| -n = Value at | POR                                         | '1' = Bit is se                                     | et                                                                         | '0' = Bit is cle                 | ared               | x = Bit is unkr | nown  |

| bit 7-6       | 00 =See STF<br>01 =PA and F<br>10 =PA and F | R <d:a><br/>PB are selecte<br/>PC are selecte</d:a> | ary Mode Outpu<br>ed as the comple<br>ed as the comple<br>ed as the comple | ementary outpu<br>ementary outpu | ıt pair<br>ıt pair | bits            |       |

| bit 5         |                                             | nted: Read as                                       |                                                                            |                                  |                    |                 |       |

| bit 4         | 1 = Output s                                | • •                                                 | bit<br>e occurs on the<br>e occurs at the b                                |                                  |                    | cle boundary    |       |

| bit 3         | 1 = PxD pin                                 | ing Enable bit<br>has the PWM<br>is assigned to     | waveform with                                                              | polarity control                 | from CCPxM<        | <1:0>           |       |

| bit 2         | STRC: Steer                                 | ing Enable bit                                      | C<br>waveform with                                                         | polarity control                 | from CCPxM<        | <1:0>           |       |

| bit 1         | STRB: Steer                                 | ing Enable bit                                      | B<br>waveform with                                                         | polarity control                 | from CCPxM<        | :1:0>           |       |

| bit 0         |                                             |                                                     | waveform with                                                              | polarity control                 | from CCPxM<        | :1:0>           |       |

Note 1: The PWM Steering mode is available only when the CCPxCON register bits, CCPxM<3:2> = 11 and PxM<1:0> = 00.

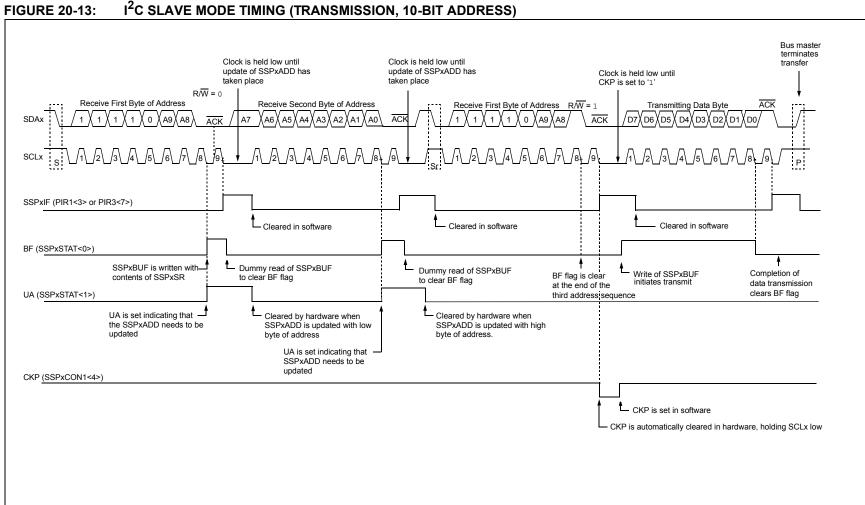

#### 20.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

#### 20.1 Master SSP (MSSP) Module Overview

The Master Synchronous Serial Port (MSSP) module is a serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D Converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit<sup>™</sup> (I<sup>2</sup>C)

- Full Master mode

- Slave mode (with general address call)

The I<sup>2</sup>C interface supports the following modes in hardware:

- Master mode

- Multi-Master mode

- Slave mode with 5-bit and 7-bit address masking (with address masking for both 10-bit and 7-bit addressing)

All members of the PIC18FXXJ94 have two MSSP modules, designated as MSSP1 and MSSP2. Each module operates independently of the other.

Note: Throughout this section, generic references to an MSSP module in any of its operating modes may be interpreted as being equally applicable to MSSP1 or MSSP2. Register names and module I/O signals use the generic designator 'x' to indicate the use of a numeral to distinguish a particular module when required. Control bit names are not individuated.

#### 20.2 Control Registers

Each MSSP module has four associated control registers. These include a STATUS register (SSPxSTAT) and three control registers (SSPxCON1, SSPxCON2, and SSPxCON3). The use of these registers and their individual Configuration bits differ significantly depending on whether the MSSP module is operated in SPI or  $I^2C$  mode.

Additional details are provided under the individual sections. On all PIC18F97J94 family devices, the SPI DMA capability can only be used in conjunction with MSSP1. The SPI DMA feature is described in **Section 20.4 "SPI DMA Module"**.

Note: In devices with more than one MSSP module, it is very important to pay close attention to SSPxCON register names. SSP1CON1 and SSP1CON2 control different operational aspects of the same module, while SSP1CON1 and SSP2CON1 control the same features for two different modules.

Note: The SSPxBUF register cannot be used with read-modify-write instructions, such as BCF, COMF, etc. To avoid lost data in Master mode, a read of the SSPxBUF must be performed to clear the Duffer Full (PF)

formed to clear the Buffer Full (BF) detect bit (SSPSTAT<0>) between each transmission.

#### 20.4.4.2 DMACON2

The DMACON2 register contains control bits for controlling interrupt generation and inter-byte delay behavior. The INTLVL<3:0> bits are used to select when an SSP1IF interrupt should be generated. The function of the DLYCYC<3:0> bits depends on the SPI operating mode (Master/Slave), as well as the DLYINTEN setting. In SPI Master mode, the DLYCYC<3:0> bits can be used to control how much time the module will Idle between bytes in a transfer. By default, the hardware requires a minimum delay of 8 TcY for FOSC/4, 9 TcY for FOSC/16 and 15 TcY for FOSC/64. An additional delay can be added with the DLYCYCx bits. In SPI Slave modes, the DLYCYC<3:0> bits may optionally be used to trigger an additional time-out based interrupt.

#### REGISTER 20-5: DMACON2: DMA CONTROL REGISTER 2

| R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| DLYCYC3 | DLYCYC2 | DLYCYC1 | DLYCYC0 | INTLVL3 | INTLVL2 | INTLVL1 | INTLVL0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend:                                                              |                  |                      |                    |

|----------------------------------------------------------------------|------------------|----------------------|--------------------|

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |                      |                    |

| -n = Value at POR                                                    | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 7-4 DLYCYC<3:0>: Delay Cycle Selection bits

When DLYINTEN = 0, these bits specify the additional delay (above the base overhead of the hardware), in number of TCY cycles, before the SSP2BUF register is written again for the next transfer. When DLYINTEN = 1, these bits specify the delay in number of TCY cycles from the latest completed transfer before an interrupt to the CPU is invoked. In this case, the additional delay before the SSP2BUF register is written again is 1 TCY + (base overhead of hardware).

| Sol 2001 register is written again is i fer i (base overhead of he |

|--------------------------------------------------------------------|

| 1111 = Delay time in number of instruction cycles is 2,048 cycles  |

| 1110 = Delay time in number of instruction cycles is 1,024 cycles  |

| 1101 = Delay time in number of instruction cycles is 896 cycles    |

| 1100 = Delay time in number of instruction cycles is 768 cycles    |

| 1011 = Delay time in number of instruction cycles is 640 cycles    |

| 1010 = Delay time in number of instruction cycles is 512 cycles    |

| 1001 = Delay time in number of instruction cycles is 384 cycles    |

| 1000 = Delay time in number of instruction cycles is 256 cycles    |

| 0111 = Delay time in number of instruction cycles is 128 cycles    |

| 0110 = Delay time in number of instruction cycles is 64 cycles     |

| 0101 = Delay time in number of instruction cycles is 32 cycles     |

| 0100 = Delay time in number of instruction cycles is 16 cycles     |

| 0011 = Delay time in number of instruction cycles is 8 cycles      |

| 0010 = Delay time in number of instruction cycles is 4 cycles      |

| 0001 = Delay time in number of instruction cycles is 2 cycles      |

| 0000 = Delay time in number of instruction cycles is 1 cycle       |

bit 0

|          | 2-24. ADCI |          |          |          |          |         |         |

|----------|------------|----------|----------|----------|----------|---------|---------|

| R/W-0    | R/W-0      | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0   | R/W-0   |

| CTMUEN15 | CTMUEN14   | CTMUEN13 | CTMUEN12 | CTMUEN11 | CTMUEN10 | CTMUEN9 | CTMUEN8 |

#### REGISTER 22-24: ADCTMUEN0H: CTMU ENABLE REGISTER 0 HIGH (HIGH WORD)<sup>(1)</sup>

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 7-0 CTMUEN<15:8>: CTMU Enabled During Conversion bits

bit 7

- 1 = CTMU is enabled and connected to the selected channel during conversion

- 0 = CTMU is not connected to this channel

#### REGISTER 22-25: ADCTMUEN0L: CTMU ENABLE REGISTER 0 LOW (LOW WORD)<sup>(1)</sup>

| R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| CTMUEN7 | CTMUEN6 | CTMUEN5 | CTMUEN4 | CTMUEN3 | CTMUEN2 | CTMUEN1 | CTMUEN0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 7-0 CTMUEN<7:0>: CTMU Enabled During Conversion bits

- 1 = CTMU is enabled and connected to the selected channel during conversion

- 0 = CTMU is not connected to this channel

- **Note 1:** The actual number of channels available depends on which channels are implemented on a specific device; refer to the device data sheet for details. Unimplemented channels are read as '0'.

**Note 1:** The actual number of channels available depends on which channels are implemented on a specific device; refer to the device data sheet for details. Unimplemented channels are read as '0'.

#### **REGISTER 22-26: ANCFG – ANALOG INPUT REGISTER**

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0 |

|-------|-----|-----|-----|-----|--------|--------|-------|

| —     |     |     |     | —   | VBG6EN | VBG2EN | VBGEN |

| bit 7 |     |     |     |     |        |        | bit 0 |

| Legend:            |                            |                                                       |  |  |  |  |  |  |

|--------------------|----------------------------|-------------------------------------------------------|--|--|--|--|--|--|

| R = Readable bit   | W = Writable bit           | U = Unimplemented bit, read as '0'                    |  |  |  |  |  |  |

| u = Bit is unchang | ged x = Bit is unknown     | -n/n = Value at POR and BOR/Value at all other Resets |  |  |  |  |  |  |

| '1' = Bit is set   | '0' = Bit is cleared       |                                                       |  |  |  |  |  |  |

|                    |                            |                                                       |  |  |  |  |  |  |

| bit 7-3 U          | Unimplemented: Read as '0' |                                                       |  |  |  |  |  |  |

| bit 2 | VBG6EN: Band Gap Divide-by-6 Control bit |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|

|       | 1 = Reference voltage on                 |  |  |  |  |  |

|       | 0 = Reference voltage off                |  |  |  |  |  |

| bit 1 | VBG2EN: Band Gap Divide-by-2 Control bit |  |  |  |  |  |

|       | 1 = Reference voltage on                 |  |  |  |  |  |

|       | 0 = Reference voltage off                |  |  |  |  |  |

| bit 0 | VBGEN: Band Gap Control bit              |  |  |  |  |  |

|       | 1 = Reference voltage on                 |  |  |  |  |  |

|       |                                          |  |  |  |  |  |

0 = Reference voltage off

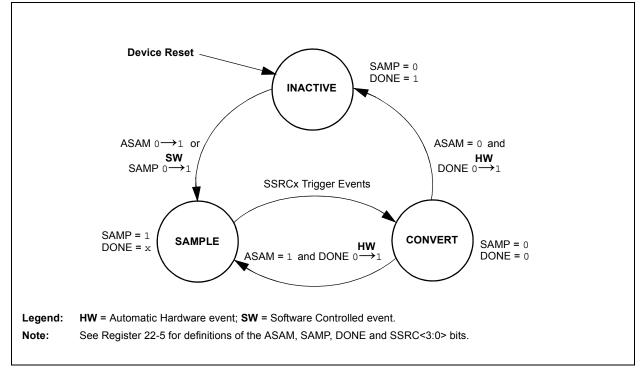

#### 22.2.1 OPERATION AS A STATE MACHINE

The A/D conversion process can be thought of in terms of a finite state machine (Figure 22-3). The sample state represents the time that the input channel is connected to the S/H amplifier and the signal is passed to the converter input. The convert state is transitory. The module enters this state as soon as it exits the sample state and transitions to a different state when that is done. The inactive state is the default state prior to module initialization and following a software-controlled conversion; it can be avoided in operation by using Auto-Sample mode. Machine states are identified by the state of several control and Status bits in ADCON1H/L. If the module is configured for Auto-Sample mode, the operation "ping-pongs" continuously between the sample and convert states. The module automatically selects the input channels to be sampled (if channel scanning is enabled), while the selected conversion trigger source paces the entire operation. Any time that Auto-Sample mode is not used for conversion, it is available for the sample state. The user needs to make certain that acquisition time is sufficient, in addition to accounting for the normal concerns about system throughput.

Whenever the issue of sampling time is important, the significant event is the transition from sample to convert state. This is the point where the Sample-and-Hold aperture closes, and it is essentially the signal value at this instant, which is applied to the A/D for conversion to digital.

#### FIGURE 22-3: A/D MODULE STATE MACHINE MODEL

#### 26.2.5 INTERRUPTS

The CTMU sets its interrupt flag (PIR3<3>) whenever the current source is enabled, then disabled. An interrupt is generated only if the corresponding interrupt enable bit (PIE3<3>) is also set. If edge sequencing is not enabled (i.e., Edge 1 must occur before Edge 2), it is necessary to monitor the Edge Status bits, and determine which edge occurred last and caused the interrupt.

#### 26.3 CTMU Module Initialization

The following sequence is a general guideline used to initialize the CTMU module:

- 1. Select the current source range using the IRNGx bits (CTMUCON1<1:0>).

- 2. Adjust the current source trim using the ITRIMx bits (CTMUCON1<7:2>).

- Configure the edge input sources for Edge 1 and Edge 2 by setting the EDG1SELx and EDG2SELx bits (CTMUCON3<5:2> and CTMU-CON2<5:2>, respectively).

- Configure the input polarities for the edge inputs using the EDG1POL and EDG2POL bits (CTMUCON3<6> and CTMUCON2<6>).

The default configuration is for negative edge polarity (high-to-low transitions).

- Enable edge sequencing using the EDGSEQEN bit (CTMUCON<2>).

By default, edge sequencing is disabled.

Select the operating mode (Measurement or Time Delay) with the TGEN bit (CTMUCON<4>).

The default mode is Time/Capacitance Measurement mode.

Configure the module to automatically trigger an A/D conversion when the second edge event has occurred using the CTTRIG bit (CTMUCON<0>).

The conversion trigger is disabled by default.

- 8. Discharge the connected circuit by setting the IDISSEN bit (CTMUCON<1>).

- 9. After waiting a sufficient time for the circuit to discharge, clear the IDISSEN bit.

- 10. Disable the module by clearing the CTMUEN bit (CTMUCON<7>).

- Clear the Edge Status bits, EDG2STAT and EDG1STAT (CTMUCON3<1:0>).

Both bits should be cleared simultaneously, if possible, to avoid re-enabling the CTMU current source.

- 12. Enable both edge inputs by setting the EDGEN bit (CTMUCON<3>).

- 13. Enable the module by setting the CTMUEN bit.

Depending on the type of measurement or pulse generation being performed, one or more additional modules may also need to be initialized and configured with the CTMU module:

- Edge Source Generation: In addition to the external edge input pins, CCP1/CCP2 Special Event Triggers can be used as edge sources for the CTMU.

- Capacitance or Time Measurement: The CTMU module uses the A/D Converter to measure the voltage across a capacitor that is connected to one of the analog input channels.

- Pulse Generation: When generating system clock independent, output pulses, the CTMU module uses Comparator 2 and the associated comparator voltage reference.

#### 26.4 Calibrating the CTMU Module

The CTMU requires calibration for precise measurements of capacitance and time, as well as for accurate time delay. If the application only requires measurement of a relative change in capacitance or time, calibration is usually not necessary. An example of a less precise application is a capacitive touch switch, in which the touch circuit has a baseline capacitance and the added capacitance of the human body changes the overall capacitance of a circuit.

If actual capacitance or time measurement is required, two hardware calibrations must take place:

- The current source needs calibration to set it to a precise current.

- The circuit being measured needs calibration to measure or nullify any capacitance other than that to be measured.

#### 26.4.1 CURRENT SOURCE CALIBRATION

The current source on board the CTMU module has a range of  $\pm 62\%$  nominal for each of three current ranges. For precise measurements, it is possible to measure and adjust this current source by placing a high-precision resistor, RCAL, onto an unused analog channel. An example circuit is shown in Figure 26-2.

To measure the current source:

- 1. Initialize the A/D Converter.

- 2. Initialize the CTMU.

- Enable the current source by setting EDG1STAT (CTMUCON3<0>).

- 4. Issue time delay for voltage across RCAL to stabilize and the A/D Sample-and-Hold (S/H) capacitor to charge.

- 5. Perform the A/D conversion.

- 6. Calculate the current source current using I = V/RCAL, where RCAL is a high-precision resistance and V is measured by performing an A/D conversion.

#### 27.0 UNIVERSAL SERIAL BUS (USB)

This section describes the details of the USB peripheral. Because of the very specific nature of the module, some knowledge of USB is expected. Some high-level USB information is provided in **Section 27.9** "**Overview of USB**" only for application design reference. Designers are encouraged to refer to the official specification published by the USB Implementers Forum (USB-IF) for the latest information. USB Specification Revision 2.0 is the most current specification at the time of publication of this document.

#### 27.1 Overview of the USB Peripheral

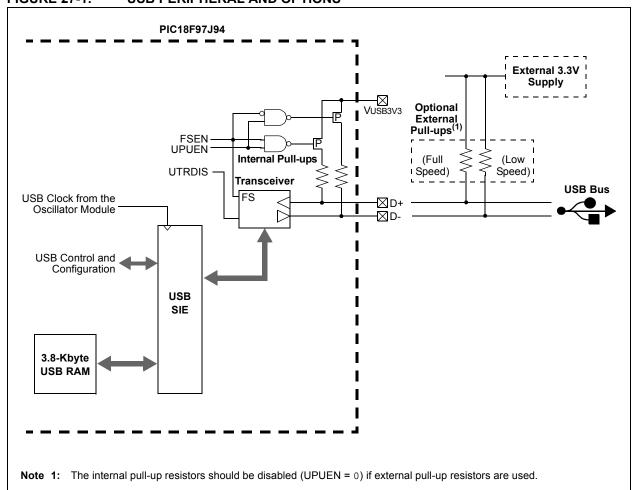

PIC18FXXJ94 devices contain a full-speed and lowspeed, compatible USB Serial Interface Engine (SIE) that allows fast communication between any USB host and the PIC<sup>®</sup> MCU. The SIE can be interfaced directly to the USB, utilizing the internal transceiver.

Some special hardware features have been included to improve performance. Dual access port memory in the device's data memory space (USB RAM) has been supplied to share Direct Memory Access (DMA) between the microcontroller core and the SIE. Buffer descriptors are also provided, allowing users to freely program endpoint memory usage within the USB RAM space. Figure 27-1 provides a general overview of the USB peripheral and its features.

FIGURE 27-1: USB PERIPHERAL AND OPTIONS

#### 28.4 Fail-Safe Clock Monitor

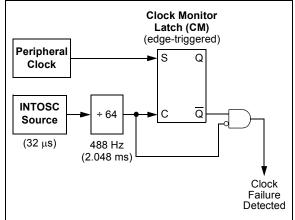

The Fail-Safe Clock Monitor (FSCM) allows the microcontroller to continue operation in the event of an external oscillator failure by automatically switching the device clock to the internal oscillator block. The FSCM function is enabled by clearing the FSCMx Configuration bits.

When FSCM is enabled, the LF-INTOSC Oscillator runs at all times to monitor clocks to peripherals and provides a backup clock in the event of a clock failure. Clock monitoring (shown in Figure 28-3) is accomplished by creating a sample clock signal, which is the output from the LF-INTOSC, divided by 64. This allows ample time between FSCM sample clocks for a peripheral clock edge to occur. The peripheral device clock and the sample clock are presented as inputs to the Clock Monitor (CM) latch. The CM is set on the falling edge of the device clock source, but cleared on the rising edge of the sample clock.

Clock failure is tested for on the falling edge of the sample clock. If a sample clock falling edge occurs while CM is still set, a clock failure has been detected (Figure 28-4). This causes the following:

- The FSCM generates an oscillator fail interrupt by setting bit, OSCFIF (PIR2<7>)

- The device clock source switches to the internal oscillator block (OSCCON is not updated to show the current clock source – this is the fail-safe condition)

- The WDT is reset

During switchover, the postscaler frequency from the internal oscillator block may not be sufficiently stable for timing-sensitive applications. In these cases, it may be desirable to select another clock configuration and enter an alternate power-managed mode. This can be done to attempt a partial recovery or execute a controlled shutdown. See Section 28.3.1 "Special Considerations for Using Two-Speed Start-up" for more details.

To use a higher clock speed on wake-up, the INTOSC or postscaler clock sources can be selected to provide a higher clock speed by setting bits, IRCF<2:0>, immediately after Reset. For wake-ups from Sleep, the INTOSC or postscaler clock sources can be selected by setting the IRCF<2:0> bits prior to entering Sleep mode.

The FSCM will detect only failures of the primary or secondary clock sources. If the internal oscillator block fails, no failure would be detected nor would any action be possible.

#### 28.4.1 FSCM AND THE WATCHDOG TIMER

Both the FSCM and the WDT are clocked by the INTOSC Oscillator. Since the WDT operates with a separate divider and counter, disabling the WDT has no effect on the operation of the INTOSC Oscillator when the FSCM is enabled.

As already noted, the clock source is switched to the INTOSC clock when a clock failure is detected. Depending on the frequency selected by the IRCF<2:0> bits, this may mean a substantial change in the speed of code execution. If the WDT is enabled with a small prescale value, a decrease in clock speed allows a WDT time-out to occur and a subsequent device Reset. For this reason, Fail-Safe Clock events also reset the WDT and postscaler, allowing it to start timing from when execution speed was changed and decreasing the likelihood of an erroneous time-out.

#### 28.4.2 EXITING FAIL-SAFE OPERATION

The Fail-Safe condition is terminated by either a device Reset or by entering a power-managed mode. On Reset, the controller starts the primary clock source, specified in Configuration Register 1H (with any required start-up delays that are required for the oscillator mode, such as the OST or PLL timer). The INTOSC multiplexer provides the device clock until the primary clock source becomes ready (similar to a Two-Speed Start-up). The clock source is then switched to the primary clock automatically after an OST. The Fail-Safe Clock Monitor then resumes monitoring the peripheral clock.

The primary clock source may never become ready during start-up. In this case, operation is clocked by the INTOSC multiplexer. The OSCCON register will remain in its Reset state until a power-managed mode is entered.

| DAW                 | Decimal Adjust W Register         |                           | DECF        | Decrement f       |                          |                                           |                                      |  |

|---------------------|-----------------------------------|---------------------------|-------------|-------------------|--------------------------|-------------------------------------------|--------------------------------------|--|

| Syntax:             | DAW                               |                           |             | Syntax:           | DECF f{,                 | d {,a}}                                   |                                      |  |

| Operands:           | None                              |                           |             | Operands:         | $0 \le f \le 255$        |                                           |                                      |  |

| Operation:          | If [W<3:0> > 9] or [DC = 1], then |                           |             | d ∈ [0,1]         |                          |                                           |                                      |  |

|                     | · /                               | $6 \rightarrow W < 3:0>;$ |             | <b>A</b>          | a ∈ [0,1]                |                                           |                                      |  |

|                     | else<br>(W<3:0>) –                | → W<3·0>                  |             | Operation:        | $(f) - 1 \rightarrow de$ |                                           |                                      |  |

|                     | (***0.0*) =                       | 7 11 3.02                 |             | Status Affected:  | C, DC, N, 0              | DV, Z                                     |                                      |  |

|                     | •                                 | > 9] or [C = 1],          | then        | Encoding:         | 0000                     | 01da ff                                   | ff ffff                              |  |

|                     | (W<7:4>) +<br>C = 1;              | $6 \rightarrow W < 7:4>;$ |             | Description:      |                          | register, 'f'. It                         |                                      |  |

|                     | C = ⊥,<br>else                    |                           |             |                   |                          | ored in W. If 'c<br>ored back in re       | ,                                    |  |

|                     | (W<7:4>) –                        | → W<7:4>                  |             |                   |                          |                                           | 0                                    |  |

| Status Affected:    | С                                 |                           |             |                   | ,                        |                                           | ank is selected.<br>ed to select the |  |

| Encoding:           | 0000                              | 0000 000                  | 0 0111      |                   | GPR bank.                |                                           |                                      |  |

| Description:        |                                   | ts the 8-bit valu         |             |                   | lf 'a' is '0' a          | nd the extend                             | ded instruction                      |  |

| Description         |                                   | om the earlier a          |             |                   | set is enab              | set is enabled, this instruction operates |                                      |  |

|                     | variables (e                      | each in packed            | BCD format) |                   |                          | Literal Offset                            | 0                                    |  |

|                     | •                                 | es a correct pa           | cked BCD    |                   |                          | never f ≤ 95 (8                           |                                      |  |

|                     | result.                           |                           |             |                   |                          | .2.3 "Byte-O                              | ns in Indexed                        |  |

| Words:              | 1                                 |                           |             |                   |                          | set Mode" fo                              |                                      |  |

| Cycles:             | 1                                 |                           |             | Words:            | 1                        |                                           |                                      |  |

| Q Cycle Activity:   |                                   |                           |             | Cycles:           | 1                        |                                           |                                      |  |

| Q1                  | Q2                                | Q3                        | Q4          | Q Cycle Activity: |                          |                                           |                                      |  |

| Decode              | Read                              | Process                   | Write       | Q1                | Q2                       | Q3                                        | Q4                                   |  |

|                     | register W                        | Data                      | W           | Decode            | Read                     | Process                                   | Write to                             |  |

| Example 1:          | DAW                               |                           |             |                   | register 'f'             | Data                                      | destination                          |  |

| Before Instruc      |                                   |                           |             |                   |                          |                                           |                                      |  |

| W                   | = A5h                             |                           |             | Example:          | DECF                     | CNT, 1,                                   | C                                    |  |

| C<br>DC             | = 0<br>= 0                        |                           |             | Before Instruc    | ction                    |                                           |                                      |  |

| After Instructi     | 0                                 |                           |             | CNT<br>Z          | = 01h<br>= 0             |                                           |                                      |  |

| W                   | = 05h                             |                           |             | After Instruction | Ũ                        |                                           |                                      |  |

| C<br>DC             | = 1<br>= 0                        |                           |             | CNT               | = 00h                    |                                           |                                      |  |

|                     | - 0                               |                           |             | Z                 | = 1                      |                                           |                                      |  |

| Example 2:          |                                   |                           |             |                   |                          |                                           |                                      |  |

| Before Instrue<br>W | ction<br>= CEh                    |                           |             |                   |                          |                                           |                                      |  |

| C                   | = CEn<br>= 0                      |                           |             |                   |                          |                                           |                                      |  |

| DC                  | = 0                               |                           |             |                   |                          |                                           |                                      |  |

| After Instructi     |                                   |                           |             |                   |                          |                                           |                                      |  |

| W<br>C              | = 34h<br>= 1                      |                           |             |                   |                          |                                           |                                      |  |

|                     |                                   |                           |             |                   |                          |                                           |                                      |  |

## TABLE 30-2: DC CHARACTERISTICS: POWER-DOWN AND SUPPLY CURRENT PIC18FXXJ94 (INDUSTRIAL)

| PIC18FXX<br>(Industrial) |                     |               |       |                | Standard Operating Conditions: 2V to 3.6V (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |                                                      |  |  |  |  |

|--------------------------|---------------------|---------------|-------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--|--|--|--|

| Param<br>No.             | Typ. <sup>(1)</sup> | Max.          | Units |                | Conditions                                                                                                                                         |                                                      |  |  |  |  |

| DC60                     | 3.7                 | 7.0           | μA    | -40°C          |                                                                                                                                                    |                                                      |  |  |  |  |

|                          | 3.7                 | 7.0           | μA    | +25°C          | 2.0V                                                                                                                                               |                                                      |  |  |  |  |

|                          | 5.0                 | 9.0           | μA    | +60°C          | 2.00                                                                                                                                               |                                                      |  |  |  |  |

|                          | 9.0                 | 18            | μA    | +85°C          |                                                                                                                                                    | Sleep <sup>(2)</sup>                                 |  |  |  |  |

|                          | 3.7                 | 8.0           | μA    | -40°C          |                                                                                                                                                    | Sieep <sup>,-,</sup>                                 |  |  |  |  |

|                          | 3.7                 | 8.0           | μA    | +25°C          | 2.014                                                                                                                                              |                                                      |  |  |  |  |

|                          | 5.0                 | 11.0          | μA    | +60°C          | 3.3V                                                                                                                                               |                                                      |  |  |  |  |

|                          | 10                  | 20            | μA    | +85°C          |                                                                                                                                                    |                                                      |  |  |  |  |

| DC61                     | 0.07                | 0.55 μA -40°C |       |                |                                                                                                                                                    |                                                      |  |  |  |  |

|                          | 0.09                | 0.55          | μA    | +25°C          | 2.0V<br>3.3V                                                                                                                                       |                                                      |  |  |  |  |

|                          | 2.0                 | 3.2           | μA    | +60°C          |                                                                                                                                                    |                                                      |  |  |  |  |

|                          | 7.0                 | 8.5           | μA    | +85°C          |                                                                                                                                                    | Retention Sleep or                                   |  |  |  |  |

|                          | 0.10                | 0.65          | μA    | -40°C          |                                                                                                                                                    | Retention Deep Sleep <sup>(3)</sup>                  |  |  |  |  |

|                          | 0.15                | 0.65          | μA    | +25°C          |                                                                                                                                                    |                                                      |  |  |  |  |

|                          | 2.0                 | 3.5           | μA    | +60°C          |                                                                                                                                                    |                                                      |  |  |  |  |

|                          | 7.2                 | 9.0           | μA    | +85°C          |                                                                                                                                                    |                                                      |  |  |  |  |

| DC70                     | 0.06                | 0.5           | μA    | -40°C          |                                                                                                                                                    |                                                      |  |  |  |  |

|                          | 0.08                | 0.5           | μA    | +25°C          | 0.01/                                                                                                                                              |                                                      |  |  |  |  |

|                          | 0.21                | 0.8           | μA    | +60°C          | 2.0V                                                                                                                                               |                                                      |  |  |  |  |

|                          | 0.41                | 1.5           | μA    | +85°C          |                                                                                                                                                    | Deen Sleen                                           |  |  |  |  |

| -                        | 0.09                | 0.6           | μA    | -40°C          | 3.3V                                                                                                                                               | Deep Sleep                                           |  |  |  |  |

|                          | 0.11                | 0.6           | μA    | +25°C          |                                                                                                                                                    |                                                      |  |  |  |  |

|                          | 0.42                | 1.2           | μA    | +60°C          |                                                                                                                                                    |                                                      |  |  |  |  |

|                          | 0.8                 | 4.8           | μA    | +85°C          |                                                                                                                                                    |                                                      |  |  |  |  |

|                          | 0.4                 | 3.0           | μA    | -40°C to +85°C | 0                                                                                                                                                  | RTCC with VBAT mode (LPRC or<br>SOSC) <sup>(4)</sup> |  |  |  |  |

Note 1: Data in the Typical column is at 3.3V, 25°C; typical parameters are for design guidance only and are not tested.

2: Retention regulator is disabled; SRETEN (RCON4<4>= 0), RETEN (CONFIG7L<0>= 1).

3: Retention regulator is enabled; SRETEN (RCON4<4> = 1), RETEN (CONFIG7L<0> = 0).

**4:** VBAT pin is connected to the battery and RTCC is running with VDD = 0.

### TABLE 30-3:DC CHARACTERISTICS: POWER-DOWN AND SUPPLY CURRENT<br/>PIC18F97J94 FAMILY (INDUSTRIAL)

| Param<br>No. | Device               | Тур. | Max. | Units | Conditions     |            |                               |  |  |  |  |

|--------------|----------------------|------|------|-------|----------------|------------|-------------------------------|--|--|--|--|

|              | Supply Current (IDD) |      |      |       |                |            |                               |  |  |  |  |

|              | All Devices          | 22   | 55   | μA    | -40°C to +85°C | VDD = 2.0V | Fosc = 31 kHz, <b>RC RUN</b>  |  |  |  |  |

|              |                      | 23   | 56   | μA    | -40°C to +85°C | VDD = 3.3V | 1030 - 31 KHZ, <b>KC_KUN</b>  |  |  |  |  |

|              |                      | 21   | 54   | μA    | -40°C to +85°C | VDD = 2.0V | Fosc = 31 kHz, RC IDLE        |  |  |  |  |

|              |                      | 22   | 55   | μA    | -40°C to +85°C | VDD = 3.3V | 1030 - 31 KHZ, <b>RC_IDLE</b> |  |  |  |  |

## TABLE 30-4:DC CHARACTERISTICS: POWER-DOWN AND SUPPLY CURRENT<br/>PIC18F97J94 FAMILY (INDUSTRIAL)

| Param<br>No. | Device      | Тур.      | Max. | Units | Conditions     |            |                                |  |  |

|--------------|-------------|-----------|------|-------|----------------|------------|--------------------------------|--|--|

|              | Supply Curr | ent (IDD) | _    |       |                |            |                                |  |  |

|              | All Devices | 22        | 55   | μA    | -40°C to +85°C | VDD = 2.0V | Fosc = 32 kHz, SEC RUN         |  |  |

|              |             | 23        | 56   | μA    | -40°C to +85°C | VDD = 3.3V | F03C - 32 KHZ, <b>3EC_KUN</b>  |  |  |

|              |             | 21        | 54   | μA    | -40°C to +85°C | VDD =2.0V  | Fosc = 32 kHz, SEC_IDLE        |  |  |

|              |             | 22        | 55   | μA    | -40°C to +85°C | VDD = 3.3V | 1030 - 32 NIZ, <b>3EC_IDLE</b> |  |  |

## TABLE 30-5:DC CHARACTERISTICS: POWER-DOWN AND SUPPLY CURRENT<br/>PIC18F97J94 FAMILY (INDUSTRIAL)

| Param<br>No. | Device               | Тур. | Max. | Units | Conditions     |            |                                |  |  |  |  |

|--------------|----------------------|------|------|-------|----------------|------------|--------------------------------|--|--|--|--|

|              | Supply Current (IDD) |      |      |       |                |            |                                |  |  |  |  |

|              |                      | 325  | 430  | μA    | -40°C to +85°C | VDD = 2.0V |                                |  |  |  |  |

|              |                      | 325  | 430  | μA    | -40°C to +85°C | VDD = 3.3V | Fosc = 1 MHz, <b>RC_RUN</b>    |  |  |  |  |