Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I²C, IrDA, LINbus, SPI, UART/USART, USB                                     |

| Peripherals                | Brown-out Detect/Reset, HLVD, LCD, POR, PWM, WDT                            |

| Number of I/O              | 68                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 4K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                   |

| Data Converters            | A/D 24x12b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 80-TQFP                                                                     |

| Supplier Device Package    | 80-TQFP (12x12)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f86j94t-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 2          |                        | 64-PI | N ALLO          | JUATI |       | DLE (PI | C18F6XJ         | 94) (CC |     | IED)      | _    | _                       | _       |                  |

|------------------|------------------------|-------|-----------------|-------|-------|---------|-----------------|---------|-----|-----------|------|-------------------------|---------|------------------|

| 0/1              | 64-Pin TQFP/QFN        | ADC   | Comparator      | нгир  | стми  | USB     | LCD             | MSSP    | РSР | Interrupt | REFO | PPS-Lite <sup>(1)</sup> | Pull-up | Basic            |

| RE6              | 60                     |       | _               | _     | _     | _       | COM3            | _       |     | _         |      | RP34                    | Y       |                  |

| RE7              | 59                     | _     | _               |       | _     |         | LCDBIAS0        | _       | _   |           | _    | RP31                    | Y       |                  |

| RF2              | 16                     | AN7   | C2INB           | -     | CTMUI | -       | SEG20           | -       | _   | _         | _    | RP36                    | Y       |                  |

| RF3              | 15                     | _     | —               |       | _     | D-      | _               |         | _   | _         | _    | _                       | Y       | _                |

| RF4              | 14                     | _     | —               | -     | _     | D+      | _               | -       | _   | _         | _    | —                       | Y       | _                |

| RF5              | 13                     | AN10  | C1INB/<br>CVREF | _     | —     | _       | SEG23           | _       | —   | _         | —    | RP35                    | Y       | -                |

| RF6              | 12                     | AN11  | C1INA           | _     | _     | _       | SEG24           | _       | _   | _         | _    | RP40                    | Y       | _                |

| RF7              | 11                     | AN5   | —               |       | _     | _       | SEG25           | _       | _   | _         | _    | RP38                    | Y       | _                |

| RG0              | 3                      | AN8   | —               | _     | —     | _       | COM4/<br>SEG28  | _       | —   | _         | —    | RP46                    | Y       | _                |

| RG1              | 4                      | AN19  | -               |       | —     | -       | COM5/<br>SEG29  | _       | —   |           | —    | RP39                    | Y       | _                |

| RG2              | 5                      | AN18  | C3INA           | _     | —     | _       | COM6/<br>SEG30  | _       | —   | _         | —    | RP42                    | Y       | _                |

| RG3              | 6                      | AN17  | C3INB           |       | —     | -       | COM7/<br>SEG31  | _       | —   |           | —    | RP43                    | Y       | _                |

| RG4              | 8                      | AN16  | C3INC           | _     | _     | _       | SEG26           | _       | _   | _         | _    | RP44                    | Y       | _                |

| RG5/<br>MCLR     | 7                      | —     | —               | _     | —     | _       | —               | _       | —   | _         | —    | _                       | Y       | MCLR             |

| AVDD             | 19                     | AVDD  | _               | _     | _     | _       | _               | _       | _   | _         | _    | _                       | _       | _                |

| AVss             | 20                     | AVSS  | _               | _     | _     | _       | _               | _       | _   | _         | _    | _                       | _       | _                |

| VBAT             | 18                     | _     | _               | _     | _     | _       | _               | _       | _   | _         | _    | _                       | _       | VBAT             |

| Vcap/<br>Vddcore | 10                     | —     | —               |       | —     | -       | -               | _       | —   |           | —    | —                       | -       | Vcap/<br>Vddcore |

| VDD              | 26,<br>38,<br>57       | _     | _               |       | _     |         | _               | _       | _   |           | —    | _                       | _       | Vdd              |

| Vss              | 9,<br>25,<br>41,<br>56 | _     | —               | —     | _     | —       | —               | —       | —   | —         | —    | —                       | _       | Vss              |

| VUSB3V3          | 17                     | _     | —               | —     | _     | —       | _               | _       | _   | —         | _    | —                       | —       | VUSB3V3          |

| Note 1:          |                        |       |                 |       | 4     |         | ve no default n | • • •   |     |           |      |                         |         |                  |

#### TABLE 2: 64-PIN ALLOCATION TABLE (PIC18F6XJ94) (CONTINUED)

Note 1: The peripheral inputs and outputs that support PPS have no default pins.

#### TABLE 1-4: PIC18FXXJ94 PINOUT I/O DESCRIPTIONS (CONTINUED)

| Dia Nama                                      | Pin  | Num | ber | Pin        | Buffer           | Description                                                           |

|-----------------------------------------------|------|-----|-----|------------|------------------|-----------------------------------------------------------------------|

| Pin Name                                      | 100  | 80  | 64  | Туре       | Туре             | Description                                                           |

| SEG19/AN0/AN1-/RP0/RA0                        | 37   | 30  | 24  |            |                  |                                                                       |

| SEG19                                         |      |     |     | 0          | Analog           | SEG19 output for LCD.                                                 |

| ANO                                           |      |     |     | I          | Analog           | Analog Input 0.                                                       |

| AN1-                                          |      |     |     | I          | Analog           | A/D negative input channel.                                           |

| RP0                                           |      |     |     | I/O        | ST/DIG           | Remappable Peripheral Pin 0 input/output.                             |

| RA0                                           |      |     |     | I/O        | ST/DIG           | General purpose I/O pin.                                              |

| SEG18/AN1/RP1/RA1                             | 36   | 29  | 23  |            |                  |                                                                       |

| SEG18                                         |      |     |     | 0          | Analog           | SEG18 output for LCD.                                                 |

| AN1                                           |      |     |     | I          | Analog           | Analog Input 1.                                                       |

| RP1                                           |      |     |     | I/O        | ST/DIG           | Remappable Peripheral Pin 1 input/output.                             |

| RA1                                           |      |     |     | I/O        | ST/DIG           | General purpose I/O pin.                                              |

| SEG21/VREF-/AN2/RP2/RA2                       | 34   | 28  | 22  |            |                  |                                                                       |

| SEG21                                         |      |     |     | 0          | Analog           | SEG21 output for LCD.                                                 |

| VREF-                                         |      |     |     | I          | Analog           | A/D reference voltage (low) input.                                    |

| AN2                                           |      |     |     |            | Analog           | Analog Input 2.                                                       |

| RP2                                           |      |     |     | 1/O<br>1/O | ST/DIG<br>ST/DIG | Remappable Peripheral Pin 2 input/output.                             |

| RA2                                           |      |     |     | 1/0        | 51/DIG           | General purpose I/O pin.                                              |

| VREF+/AN3/RP3/RA3                             | 33   | 27  | 21  |            |                  |                                                                       |

| VREF+                                         |      |     |     |            | Analog           | A/D reference voltage (high) input.                                   |

| AN3                                           |      |     |     | <br> /O    | Analog<br>ST/DIG | Analog Input 3.                                                       |

| RP3                                           |      |     |     | 1/O        | ST/DIG           | Remappable Peripheral Pin 3 input/output.<br>General purpose I/O pin. |

| RA3                                           |      |     |     | 1/0        | 31/DIO           |                                                                       |

| SEG14/AN6/RP4/RA4                             | 43   | 34  | 28  | ~          |                  |                                                                       |

| SEG14                                         |      |     |     | 0          | Analog           | SEG14 output for LCD.                                                 |

| AN6                                           |      |     |     | <br> /O    | Analog<br>ST/DIG | Analog Input 6.<br>Remappable Peripheral Pin 4 input/output.          |

| RP4                                           |      |     |     | 1/O        | ST/DIG           | General purpose I/O pin.                                              |

| RA4                                           |      |     |     | 1/0        | 51/010           |                                                                       |

| SEG15/AN4/LVDIN/C1INA/<br>C2INA/C3INA/RP5/RA5 | 42   | 33  | 27  |            |                  |                                                                       |

| SEG15                                         |      |     |     | 0          | Analog           | SEG15 output for LCD.                                                 |

| AN4                                           |      |     |     | I          | Analog           | Analog Input 4.                                                       |

| LVDIN                                         |      |     |     |            | Analog           | High/Low-Voltage Detect (HLVD) input.                                 |

| C1INA                                         |      |     |     |            | Analog           | Comparator 1 Input A.                                                 |

| C2INA                                         |      |     |     |            | Analog           | Comparator 2 Input A.                                                 |

| C3INA                                         |      |     |     | 1/0        | Analog<br>ST/DIG | Comparator 3 Input A.<br>Remappable Peripheral Pin 5 input/output.    |

| RP5                                           |      |     |     | 1/O        | ST/DIG<br>ST/DIG | General purpose I/O pin.                                              |

| RA5                                           | nnut |     |     | "0         | 51/013           |                                                                       |

Legend: TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels CMOS = CMOS compatible input or output

Analog = Analog input

I = Input

P = Power

$I^2C = I^2C/SMBus$

O = Output

OD = Open-Drain (no P diode to VDD)

|                                                                      | Pin | Num | ber | Pin Buffer           |                                        |                                                                                                                                                                   |

|----------------------------------------------------------------------|-----|-----|-----|----------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                                             | 100 | 80  | 64  | Туре                 | Туре                                   | Description                                                                                                                                                       |

| VLCAP1/RP8/CTED13/INT0/RB0<br>VLCAP1<br>RP8<br>CTED13<br>INT0<br>RB0 | 73  | 58  | 48  | <br> /O<br> <br> /O  | Analog<br>ST/DIG<br>ST<br>ST<br>ST/DIG | LCD Drive Charge Pump Capacitor Input 1.<br>Remappable Peripheral Pin 8 input/output.<br>CTMU Edge 13 input.<br>External Interrupt 0.<br>General purpose I/O pin. |

| VLCAP2/RP9/RB1<br>VLCAP2<br>RP9<br>RB1                               | 72  | 57  | 47  | <br> /O<br> /O       | Analog<br>ST/DIG<br>ST/DIG             | LCD Drive Charge Pump Capacitor Input 2.<br>Remappable Peripheral Pin 9 input/output.<br>General purpose I/O pin.                                                 |

| SEG9/RP14/CTED1/RB2<br>SEG9<br>RP14<br>CTED1<br>RB2                  | 70  | 56  | 46  | 0<br>I/O<br>I<br>I/O | Analog<br>ST/DIG<br>ST<br>ST/DIG       | SEG9 output for LCD.<br>Remappable Peripheral Pin 14 input/output.<br>CTMU Edge 1 input.<br>General purpose I/O pin.                                              |

| SEG10/RP7/CTED2/RB3<br>SEG10<br>RP7<br>CTED2<br>RB3                  | 69  | 55  | 45  | 0<br>I/O<br>I<br>I/O | Analog<br>ST/DIG<br>ST<br>ST/DIG       | SEG10 output for LCD.<br>Remappable Peripheral Pin 7 input/output.<br>CTMU Edge 2 input.<br>General purpose I/O pin.                                              |

| SEG11/RP12/CTED3/RB4<br>SEG11<br>RP12<br>CTED3<br>RB4                | 68  | 54  | 44  | 0<br>I/O<br>I<br>I/O | Analog<br>ST/DIG<br>ST<br>ST/DIG       | SEG11 output for LCD.<br>Remappable Peripheral Pin 12 input/output.<br>CTMU Edge 3 input.<br>General purpose I/O pin.                                             |

| SEG8/RP13/CTED4/RB5<br>SEG8<br>RP13<br>CTED4<br>RB5                  | 67  | 53  | 43  | 0<br>I/O<br>I<br>I/O | Analog<br>ST/DIG<br>ST<br>ST/DIG       | SEG8 output for LCD.<br>Remappable Peripheral Pin 13 input/output.<br>CTMU Edge 4 input.<br>General purpose I/O pin.                                              |

| PGC/CTED5/RB6<br>PGC<br>CTED5<br>RB6                                 | 65  | 52  | 42  | I/O<br>I<br>I/O      | ST/DIG<br>ST<br>ST/DIG                 | In-Circuit Debugger and ICSP™ programming clock pin.<br>CTMU Edge Input.<br>General purpose I/O pin.                                                              |

| PGD/CTED6/RB7<br>PGD<br>CTED6<br>RB7                                 | 58  | 47  | 37  | I/O<br>I<br>I/O      | ST/DIG<br>ST<br>ST/DIG                 | In-Circuit Debugger and ICSP™ programming data pin.<br>CTMU Edge 6 input.<br>General purpose I/O pin.                                                             |

#### TABLE 1-4: PIC18FXXJ94 PINOUT I/O DESCRIPTIONS (CONTINUED)

**Legend:** TTL = TTL compatible input

ST = Schmitt Trigger input with CMOS levels

I = Input

P = Power

$I^2C = I^2C/SMBus$

CMOS = CMOS compatible input or output

- Analog = Analog input

- O = Output

OD = Open-Drain (no P diode to VDD)

### 4.0 POWER-MANAGED MODES

All PIC18F97J94 Family devices offer a number of built-in strategies for reducing power consumption. These strategies can be particularly useful in applications, which are both power-constrained (such as battery operation), yet require periods of full-power operation for timing-sensitive routines (such as serial communications).

Aside from their low-power architecture, these devices include an expanded range of dedicated hardware features that allow the microcontroller to reduce power consumption to even lower levels when long-term hibernation is required, and still be able to resume operation on short notice.

The device has four power-saving features:

- · Instruction-Based Power-Saving Modes

- Hardware-Based Power Reduction Features

- Microcontroller Clock Manipulation

- Selective Peripheral Control

Combinations of these methods can be used to selectively tailor an application's power consumption, while still maintaining critical or timing-sensitive application features. However, it is more convenient to discuss the strategies separately.

#### 4.1 Overview of Power-Saving Modes

In addition to full-power operation, otherwise known as Run mode, PIC18F97J94 Family devices offer three instruction-based, power-saving modes and one hardware-based mode. In descending order of power consumption, they are:

- Idle

- Sleep (including retention Sleep)

- · Deep Sleep (with and without retention)

- VBAT (with and without RTCC)

By powering down all four modes, different functional areas of the microcontroller allow progressive reductions of operating and Idle power consumption. In addition, three of the modes can be tailored for more power reduction at a trade-off of some operating features. Table 4-1 lists all of the operating modes (including Run mode, for comparison) in order of increasing power savings and summarizes how the microcontroller exits the different modes.

### 4.4.10 CONTROL BIT SUMMARY FOR SLEEP MODES

Table 4-5 shows the settings for the bits relevant to Deep Sleep modes.

| Instruction-Based    | DSEN        | Retention Regulator                         |   |          |                          |  |  |

|----------------------|-------------|---------------------------------------------|---|----------|--------------------------|--|--|

| Mode                 | (DSCONH<7>) | >) RETEN SRETEN<br>(CONFIG7L<0>) (RCON4<4>) |   | State    | DSWDTEN<br>(CONFIG8H<0>) |  |  |

| Retention Deep Sleep | 1           | 0                                           | 1 | Enabled  | 0                        |  |  |

| Deep Sleep           | 1           | 1                                           | х | Disabled | х                        |  |  |

#### TABLE 4-5: BIT SETTINGS FOR ALL DEEP SLEEP MODES

#### 4.4.11 WAKE-UP DELAYS

The Reset delays associated with wake-up from Deep Sleep and Retention Deep Sleep modes, in different oscillator modes, are provided in Table 4-6 and Table 4-7, respectively. Note: The PMSLP bit (RCON4<0>) allows the voltage regulator to be maintained during Sleep modes.

#### TABLE 4-6: DELAY TIMES FOR EXITING FROM DEEP SLEEP MODE

|          | Clock Source       | Exit Delay | Oscillator Delay | Notes   |

|----------|--------------------|------------|------------------|---------|

| EC       |                    | TDSWU      | _                |         |

| ECPLL    |                    | TDSWU      | ТLОСК            | 1, 3    |

| MS, HS   |                    | TDSWU      | Tost             | 1, 2    |

| MSPLL, H | SPLL               | TDSWU      | TOST + TLOCK     | 1, 2, 3 |

| SOSC     | (Off during Sleep) | TDSWU      | Tost             | 1, 2    |

|          | (On during Sleep)  | TDSWU      | —                | 1       |

| FRC, FRC | DIV                | TDSWU      | TFRC             | 1, 4    |

| LPRC     | (Off during Sleep) | TDSWU      | TLPRC            | 1, 4    |

|          | (On during Sleep)  | TDSWU      | —                | 1       |

| FRCPLL   |                    | TDSWU      | TFRC + TLOCK     | 1, 3, 4 |

**Note 1:** TDSWU = Deep Sleep wake-up delay.

2: TOST = Oscillator Start-up Timer; a delay of 1024 oscillator periods before the oscillator clock is released to the system.

- **3:** TLOCK = PLL lock time.

- 4: TFRC and TLPRC are RC Oscillator start-up times.

| Register | Арг    | blicable Dev | vices   | Power-on Reset,<br>Brown-out<br>Reset | MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets | Wake-up via<br>WDT or Interrupt |

|----------|--------|--------------|---------|---------------------------------------|------------------------------------------------------------------|---------------------------------|

| ALRMRPT  | 64-pin | 80-pin       | 100-pin | 0000 0000                             | uuuu uuuu                                                        | uuuu uuuu                       |

| ALRMVALH | 64-pin | 80-pin       | 100-pin | xxxx xxxx                             | uuuu uuuu                                                        | uuuu uuuu                       |

| ALRMVALL | 64-pin | 80-pin       | 100-pin | xxxx xxxx                             | uuuu uuuu                                                        | uuuu uuuu                       |

| RTCCON2  | 64-pin | 80-pin       | 100-pin | 0000 0000                             | uuuu uuuu                                                        | uuuu uuuu                       |

| IOCP     | 64-pin | 80-pin       | 100-pin | 0000 0000                             | 0000 0000                                                        | սսսս սսսս                       |

| IOCN     | 64-pin | 80-pin       | 100-pin | 0000 0000                             | 0000 0000                                                        | սսսս սսսս                       |

| PADCFG1  | 64-pin | 80-pin       | 100-pin | 0000 0000                             | 0000 0000                                                        | uuuu uuuu                       |

| CM1CON   | 64-pin | 80-pin       | 100-pin | 0001 1111                             | 0001 1111                                                        | uuuu uuuu                       |

| ECCP2AS  | 64-pin | 80-pin       | 100-pin | 0000 0000                             | 0000 0000                                                        | uuuu uuuu                       |

| ECCP2DEL | 64-pin | 80-pin       | 100-pin | 0000 0000                             | 0000 0000                                                        | uuuu uuuu                       |

| CCPR2H   | 64-pin | 80-pin       | 100-pin | xxxx xxxx                             | xxxx xxxx                                                        | uuuu uuuu                       |

| CCPR2L   | 64-pin | 80-pin       | 100-pin | xxxx xxxx                             | XXXX XXXX                                                        | uuuu uuuu                       |

| ECCP2CON | 64-pin | 80-pin       | 100-pin | 0000 0000                             | 0000 0000                                                        | uuuu uuuu                       |

| ECCP3AS  | 64-pin | 80-pin       | 100-pin | 0000 0000                             | 0000 0000                                                        | uuuu uuuu                       |

| ECCP3DEL | 64-pin | 80-pin       | 100-pin | 0000 0000                             | 0000 0000                                                        | uuuu uuuu                       |

| CCPR3H   | 64-pin | 80-pin       | 100-pin | xxxx xxxx                             | XXXX XXXX                                                        | uuuu uuuu                       |

| CCPR3L   | 64-pin | 80-pin       | 100-pin | xxxx xxxx                             | xxxx xxxx                                                        | uuuu uuuu                       |

| ECCP3CON | 64-pin | 80-pin       | 100-pin | 0000 0000                             | 0000 0000                                                        | uuuu uuuu                       |

| CCPR8H   | 64-pin | 80-pin       | 100-pin | xxxx xxxx                             | XXXX XXXX                                                        | uuuu uuuu                       |

| CCPR8L   | 64-pin | 80-pin       | 100-pin | xxxx xxxx                             | xxxx xxxx                                                        | uuuu uuuu                       |

| CCP8CON  | 64-pin | 80-pin       | 100-pin | 00 0000                               | 00 0000                                                          | uu uuuu                         |

| CCPR9H   | 64-pin | 80-pin       | 100-pin | xxxx xxxx                             | XXXX XXXX                                                        | uuuu uuuu                       |

| CCPR9L   | 64-pin | 80-pin       | 100-pin | xxxx xxxx                             | xxxx xxxx                                                        | uuuu uuuu                       |

| CCP9CON  | 64-pin | 80-pin       | 100-pin | 00 0000                               | 00 0000                                                          | uu uuuu                         |

| CCPR10H  | 64-pin | 80-pin       | 100-pin | xxxx xxxx                             | XXXX XXXX                                                        | uuuu uuuu                       |

| CCPR10L  | 64-pin | 80-pin       | 100-pin | xxxx xxxx                             | xxxx xxxx                                                        | uuuu uuuu                       |

| CCP10CON | 64-pin | 80-pin       | 100-pin | 00 0000                               | 00 0000                                                          | uu uuuu                         |

| TMR6     | 64-pin | 80-pin       | 100-pin | 0000 0000                             | 0000 0000                                                        | uuuu uuuu                       |

| PR6      | 64-pin | 80-pin       | 100-pin | 1111 1111                             | 1111 1111                                                        | uuuu uuuu                       |

| T6CON    | 64-pin | 80-pin       | 100-pin | -000 0000                             | -000 0000                                                        | -uuu uuuu                       |

| TMR8     | 64-pin | 80-pin       | 100-pin | 0000 0000                             | 0000 0000                                                        | uuuu uuuu                       |

| PR8      | 64-pin | 80-pin       | 100-pin | 1111 1111                             | 1111 1111                                                        | uuuu uuuu                       |

| T8CON    | 64-pin | 80-pin       | 100-pin | -000 0000                             | -000 0000                                                        | -uuu uuuu                       |

#### TABLE 5-3: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged; x = unknown; - = unimplemented bit, read as '0'; q = value depends on condition. Shaded cells indicate that conditions do not apply for the designated device.

**Note 1:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

3: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- 4: See Table 5-2 for Reset value for specific condition.

- 5: Bits 7,6 are unimplemented on 64 and 80-pin devices.

- 6: If the VBAT is always powered, the DSGPx register values will remain unchanged after the first POR.

The BSR specifies the bank

used by the instruction.

Access Bank

Access RAM Low

Access RAM High

(SFRs)

00h

5Fh

60h

FFh

#### FIGURE 6-6: DATA MEMORY MAP FOR PIC18F97J94 FAMILY DEVICES BSR<3:0> **Data Memory Map** 00h 000h Access RAM = 0000 05Fh When a = 0: Bank 0 060h GPR The BSR is ignored and the 0FFh FFh Access Bank is used. 00h 100h = 0001 The first 96 bytes are general Bank 1 GPR purpose RAM (from Bank 0). FFh 1FFh The second 160 bytes are 00h 200h = 0010 Special Function Registers Bank 2 GPR (from Bank 15). FFh 2FFh 300h 00h = 0011 When a = 1: Bank 3 GPR

SFR

SFR

SFR

FFh

00h

FFh 00h

FAh

FFh

00h

FFh 00h

FFh

= 0100

= 0101

= 0110

= 0111

= 1000

= 1001

= 1010

= 1011

= 1100

= 1101

= 1110

= 1111

Bank 4

Bank 5

Bank 6

Bank 7

Bank 8

Bank 9

Bank 10

Bank 11

Bank 12

Bank 13

Bank 14

Bank 15

3FFh

400h

4FFh

500h

5FFh

600h

6FFh

700h

7FFh

800h

8FFh

900h

9FFh

A00h

AFFh

B00h

BFFh

C00h

CFFh

D00h

DFAh

DFFh

E00h

EFFh

F00h

F5Fh

F60h/ FFFh

**Note 1:** Addresses, DFAh through F5Fh, are also SFRs, but are not part of the Access RAM. Users must always use the complete address, or load the proper BSR value, to access these registers.

#### REGISTER 10-18: IPR3: PERIPHERAL INTERRUPT PRIORITY REGISTER 3

| R/W-1                                                                | R/W-1                                 | R/W-1                                     | R/W-1            | R/W-1             | R/W-1  | R/W-1           | R/W-1  |  |  |  |  |  |

|----------------------------------------------------------------------|---------------------------------------|-------------------------------------------|------------------|-------------------|--------|-----------------|--------|--|--|--|--|--|

| TMR5GIP                                                              | LCDIP                                 | RC2IP                                     | TX2IP            | CTMUIP            | CCP2IP | CCP1IP          | RTCCIP |  |  |  |  |  |

| bit 7                                                                |                                       |                                           |                  | ÷                 |        |                 | bit 0  |  |  |  |  |  |

|                                                                      |                                       |                                           |                  |                   |        |                 |        |  |  |  |  |  |

| Legend:                                                              |                                       |                                           |                  |                   |        |                 |        |  |  |  |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                       |                                           |                  |                   |        |                 |        |  |  |  |  |  |

| -n = Value at                                                        | POR                                   | '1' = Bit is set                          |                  | '0' = Bit is clea | ared   | x = Bit is unkr | iown   |  |  |  |  |  |

|                                                                      |                                       |                                           |                  |                   |        |                 |        |  |  |  |  |  |

| bit 7                                                                |                                       | TMR5GIP: TMR5 Gate Interrupt Priority bit |                  |                   |        |                 |        |  |  |  |  |  |

|                                                                      | 1 = High priority<br>0 = Low priority |                                           |                  |                   |        |                 |        |  |  |  |  |  |

| bit 6                                                                | •                                     | •                                         | t Duiouitu (hit  |                   |        |                 |        |  |  |  |  |  |

| DILO                                                                 | 1 = High pri                          | Ready Interrup                            | ot Priority bit  |                   |        |                 |        |  |  |  |  |  |

|                                                                      | 0 = Low price                         |                                           |                  |                   |        |                 |        |  |  |  |  |  |

| bit 5                                                                |                                       | SART2 Receive                             | Priority Flag bi | t                 |        |                 |        |  |  |  |  |  |

|                                                                      | 1 = High priority                     |                                           |                  |                   |        |                 |        |  |  |  |  |  |

|                                                                      | 0 = Low price                         | ority                                     |                  |                   |        |                 |        |  |  |  |  |  |

| bit 4                                                                |                                       | ART2 Transmit                             | Interrupt Priori | ty bit            |        |                 |        |  |  |  |  |  |

|                                                                      | 1 = High priority                     |                                           |                  |                   |        |                 |        |  |  |  |  |  |

|                                                                      | 0 = Low pric                          | •                                         | ,,               |                   |        |                 |        |  |  |  |  |  |

| bit 3                                                                |                                       | FMU Interrupt P                           | riority bit      |                   |        |                 |        |  |  |  |  |  |

|                                                                      | 1 = High pri<br>0 = Low pric          | •                                         |                  |                   |        |                 |        |  |  |  |  |  |

| bit 2                                                                | •                                     | P2 Interrupt Pri                          | oritv bit        |                   |        |                 |        |  |  |  |  |  |

|                                                                      | 1 = High pri                          | •                                         | ,                |                   |        |                 |        |  |  |  |  |  |

|                                                                      | 0 = Low price                         |                                           |                  |                   |        |                 |        |  |  |  |  |  |

| bit 1                                                                | CCP1IP: EC                            | CP1 Interrupt F                           | riority bit      |                   |        |                 |        |  |  |  |  |  |

|                                                                      | 1 = High pri                          |                                           |                  |                   |        |                 |        |  |  |  |  |  |

|                                                                      | 0 = Low price                         | •                                         |                  |                   |        |                 |        |  |  |  |  |  |

| bit 0                                                                | RTCCIP: RTCC Interrupt Priority bit   |                                           |                  |                   |        |                 |        |  |  |  |  |  |

|                                                                      | 1 = High pri<br>0 = Low pric          | •                                         |                  |                   |        |                 |        |  |  |  |  |  |

|                                                                      |                                       | JIIIY                                     |                  |                   |        |                 |        |  |  |  |  |  |

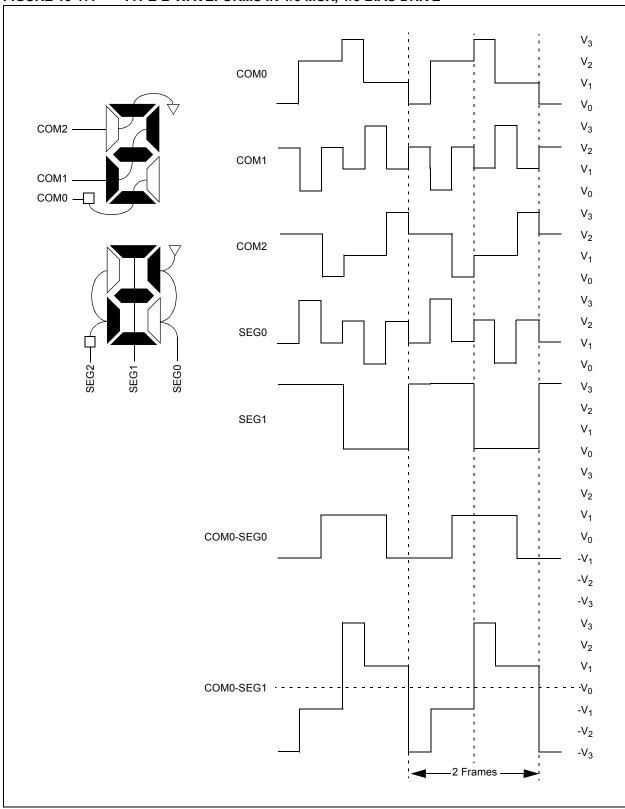

#### FIGURE 13-17: TYPE-B WAVEFORMS IN 1/3 MUX, 1/3 BIAS DRIVE

#### 17.6 Register Maps

Table 17-5, Table 17-6 and Table 17-7 summarize the registers associated with the RTCC module.

| File Name | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3      | Bit 2      | Bit 1      | Bit 0     |

|-----------|--------|--------|---------|---------|------------|------------|------------|-----------|

| RTCCON1   | RTCEN  | _      | RTCWREN | RTCSYNC | HALFSEC    | RTCOE      | RTCPTR1    | RTCPTR0   |

| RTCCAL    | CAL7   | CAL6   | CAL5    | CAL4    | CAL3       | CAL2       | CAL1       | CAL0      |

| RTCCON2   | PWCEN  | PWCPOL | PWCCPRE | PWCSPRE | RTCCLKSEL1 | RTCCLKSEL0 | RTCSECSEL1 | RTCSECSEL |

| ALRMCFG   | ALRMEN | CHIME  | AMASK3  | AMASK2  | AMASK1     | AMASK0     | ALRMPTR1   | ALRMPTR0  |

| ALRMRPT   | ARPT7  | ARPT6  | ARPT5   | ARPT4   | ARPT3      | ARPT2      | ARPT1      | ARPT0     |

| PMD3      | DSMMD  | CTMUMD | ADCMD   | RTCCMD  | LCDMD      | PSPMD      | REFO1MD    | REFO2MD   |

#### TABLE 17-5: RTCC CONTROL REGISTERS

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal for 80-pin devices.

#### TABLE 17-6: RTCC VALUE REGISTERS

| File Name | Bit 7 | Bit 6                                                | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |

|-----------|-------|------------------------------------------------------|-------|-------|-------|-------|-------|-------|--|

| RTCVALH   |       | RTCC Value High Register Window based on RTCPTR<1:0> |       |       |       |       |       |       |  |

| RTCVALL   |       | RTCC Value Low Register Window based on RTCPTR<1:0>  |       |       |       |       |       |       |  |

#### TABLE 17-7: ALARM VALUE REGISTERS

| File Name | Bit 7 | Bit 6                                                  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |

|-----------|-------|--------------------------------------------------------|-------|-------|-------|-------|-------|-------|--|

| ALRMVALH  |       | Alarm Value High Register Window based on ALRMPTR<1:0> |       |       |       |       |       |       |  |

| ALRMVALL  |       | Alarm Value Low Register Window based on ALRMPTR<1:0>  |       |       |       |       |       |       |  |

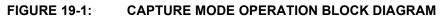

#### 19.2.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCP4IE bit (PIE4<1>) clear to avoid false interrupts and should clear the flag bit, CCP4IF, following any such change in operating mode.

#### 19.2.4 CCP PRESCALER

There are four prescaler settings in Capture mode. They are specified as part of the operating mode selected by the mode select bits (CCP4M<3:0>). Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. This means that any Reset will clear the prescaler counter. Switching from one capture prescaler to another may generate an interrupt. Doing that will also not clear the prescaler counter – meaning the first capture may be from a non-zero prescaler.

Example 19-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### EXAMPLE 19-1: CHANGING BETWEEN CAPTURE PRESCALERS

| CLRF  | CCP4CON     | ; | Turn CCP module off |

|-------|-------------|---|---------------------|

| MOVLW | NEW_CAPT_PS | ; | Load WREG with the  |

|       |             | ; | new prescaler mode  |

|       |             | ; | value and CCP ON    |

| MOVWF | CCP4CON     | ; | Load CCP4CON with   |

|       |             | ; | this value          |

|       |             |   |                     |

| R/W-0         | R/W-0                                              | R-0                                                                                                                                                                 | R-0                    | R-0              | R-0                  | R-0               | R-0      |  |  |

|---------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------|----------------------|-------------------|----------|--|--|

| SMP           | CKE                                                | D/A                                                                                                                                                                 | P <sup>(1)</sup>       | S <sup>(1)</sup> | R/W <sup>(2,3)</sup> | UA                | BF       |  |  |

| bit 7         |                                                    |                                                                                                                                                                     |                        |                  |                      |                   | bit (    |  |  |

|               |                                                    |                                                                                                                                                                     |                        |                  |                      |                   |          |  |  |

| Legend:       |                                                    |                                                                                                                                                                     |                        |                  |                      |                   |          |  |  |

| R = Read      |                                                    | W = Writable                                                                                                                                                        |                        | -                | nented bit, read     |                   |          |  |  |

| -n = Value    | e at POR                                           | '1' = Bit is set                                                                                                                                                    |                        | '0' = Bit is cle | ared                 | x = Bit is unkr   | nown     |  |  |

|               |                                                    |                                                                                                                                                                     |                        |                  |                      |                   |          |  |  |

| bit 7         |                                                    | Rate Control bit                                                                                                                                                    |                        |                  |                      |                   |          |  |  |

|               |                                                    | <u>Slave mode:</u><br>te control is disa                                                                                                                            | abled for Stand        | lard Speed mor   | le (100 kHz and      | 1 MHz)            |          |  |  |

|               |                                                    | te control is ena                                                                                                                                                   |                        |                  |                      |                   |          |  |  |

| bit 6         | CKE: SMBu                                          | s Select bit                                                                                                                                                        |                        |                  |                      |                   |          |  |  |

|               |                                                    | Slave mode:                                                                                                                                                         |                        |                  |                      |                   |          |  |  |

|               |                                                    | SMBus-specific<br>SMBus-specific                                                                                                                                    |                        |                  |                      |                   |          |  |  |

| bit 5         | Disables                                           | -                                                                                                                                                                   | 5 inputs               |                  |                      |                   |          |  |  |

| bit 5         | In Master mo                                       |                                                                                                                                                                     |                        |                  |                      |                   |          |  |  |

|               | Reserved.                                          | <u>.</u>                                                                                                                                                            |                        |                  |                      |                   |          |  |  |

|               | In Slave mod                                       | <u>de:</u>                                                                                                                                                          |                        |                  |                      |                   |          |  |  |

|               |                                                    | <ul> <li>1 = Indicates that the last byte received or transmitted was data</li> <li>0 = Indicates that the last byte received or transmitted was address</li> </ul> |                        |                  |                      |                   |          |  |  |

| bit 4         | 0 = Indicates<br><b>P:</b> Stop bit <sup>(1)</sup> |                                                                                                                                                                     | te received of         | transmitted wa   | saudiess             |                   |          |  |  |

| DIL 4         | 1 = Indicates                                      | s that a Stop bit                                                                                                                                                   |                        | ected last       |                      |                   |          |  |  |

|               |                                                    | was not detecte                                                                                                                                                     | d last                 |                  |                      |                   |          |  |  |

| bit 3         | S: Start bit <sup>(1)</sup>                        |                                                                                                                                                                     |                        |                  |                      |                   |          |  |  |

|               |                                                    | s that a Start bit<br>was not detecte                                                                                                                               |                        | ected last       |                      |                   |          |  |  |

| bit 2         | <b>R/W</b> : Read/                                 | Write Information                                                                                                                                                   | n bit <sup>(2,3)</sup> |                  |                      |                   |          |  |  |

|               | In Slave mod                                       | de:                                                                                                                                                                 |                        |                  |                      |                   |          |  |  |

|               | 1 = Read<br>0 = Write                              |                                                                                                                                                                     |                        |                  |                      |                   |          |  |  |

|               | In Master mo                                       | ode:                                                                                                                                                                |                        |                  |                      |                   |          |  |  |

|               |                                                    | is in progress                                                                                                                                                      |                        |                  |                      |                   |          |  |  |

|               |                                                    | is not in progre                                                                                                                                                    |                        |                  |                      |                   |          |  |  |

| bit 1         | •                                                  | Address bit (10-                                                                                                                                                    |                        | • /              |                      |                   |          |  |  |

|               |                                                    | s that the user n<br>does not need                                                                                                                                  |                        | e the address ir | the SSPxADD          | register          |          |  |  |

| bit 0         | BF: Buffer F                                       | ull Status bit                                                                                                                                                      |                        |                  |                      |                   |          |  |  |

|               | <u>In Transmit r</u>                               |                                                                                                                                                                     |                        |                  |                      |                   |          |  |  |

|               | 1 = SSPxBU                                         |                                                                                                                                                                     |                        |                  |                      |                   |          |  |  |

|               | 0 = SSPxBU<br><u>In Receive n</u>                  |                                                                                                                                                                     |                        |                  |                      |                   |          |  |  |

|               | 1 = SSPxBU                                         | IF is full (does n                                                                                                                                                  |                        |                  |                      |                   |          |  |  |

| Note 1:       |                                                    | IF is empty (doe                                                                                                                                                    |                        |                  | oh nira)             |                   |          |  |  |

| Note 1:<br>2: | This bit is cleare<br>This bit holds the           |                                                                                                                                                                     |                        |                  | e match This h       | nit is only valid | from the |  |  |

| ۷.            | address match to                                   |                                                                                                                                                                     |                        |                  | 55 maton. 1115 D     | nt is uniy vallu  |          |  |  |

### REGISTER 20-6: SSPxSTAT: MSSPx STATUS REGISTER (I<sup>2</sup>C MODE)

3: ORing this bit with SEN, RSEN, PEN, RCEN or ACKEN will indicate if the MSSPx is in Active mode.

#### 21.2 EUSARTx Asynchronous Mode

The Asynchronous mode of operation is selected by clearing the SYNC bit (TXSTAx<4>). In this mode, the EUSARTx uses standard Non-Return-to-Zero (NRZ) format (one Start bit, eight or nine data bits and one Stop bit). The most common data format is 8 bits. An on-chip, dedicated 8-bit/16-bit Baud Rate Generator can be used to derive standard baud rate frequencies from the oscillator.

The EUSARTx transmits and receives the LSb first. The EUSARTx's transmitter and receiver are functionally independent but use the same data format and baud rate. The Baud Rate Generator produces a clock, either x16 or x64 of the bit shift rate, depending on the BRGH and BRG16 bits (TXSTAx<2> and BAUDCONx<3>). Parity is not supported by the hardware but can be implemented in software and stored as the 9th data bit.

When operating in Asynchronous mode, the EUSARTx module consists of the following important elements:

- · Baud Rate Generator

- · Sampling Circuit

- Asynchronous Transmitter

- · Asynchronous Receiver

- Auto-Wake-up on Sync Break Character

- 12-Bit Break Character Transmit

- Auto-Baud Rate Detection

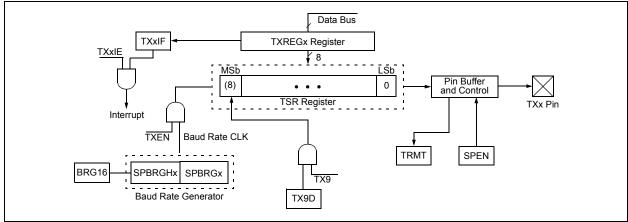

#### 21.2.1 EUSARTx ASYNCHRONOUS TRANSMITTER

The EUSARTx transmitter block diagram is shown in Figure 21-3. The heart of the transmitter is the Transmit (Serial) Shift Register (TSR). The Shift register obtains its data from the Read/Write Transmit Buffer register, TXREGx. The TXREGx register is loaded with data in software. The TSR register is not loaded until the Stop bit has been transmitted from the previous load. As soon as the Stop bit is transmitted, the TSR is loaded with new data from the TXREGx register (if available).

Once the TXREGx register transfers the data to the TSR register (occurs in one TCY), the TXREGx register is empty and the TXxIF flag bit is set. This interrupt can be enabled or disabled by setting or clearing the interrupt enable bit, TXxIE. TXxIF will be set regardless of the state of TXxIE; it cannot be cleared in software. TXxIF is also not cleared immediately upon loading TXREGx, but becomes valid in the second instruction cycle following the load instruction. Polling TXxIF immediately following a load of TXREGx will return invalid results.

While TXxIF indicates the status of the TXREGx register, another bit, TRMT (TXSTAx<1>), shows the status of the TSR register. TRMT is a read-only bit which is set when the TSR register is empty. No interrupt logic is tied to this bit so the user has to poll this bit in order to determine if the TSR register is empty.

| Note 1: | The TSR register is not mapped in data memory, so it is not available to the user. |

|---------|------------------------------------------------------------------------------------|

| 2:      | Flag bit, TXxIF, is set when enable bit, TXEN, is set.                             |

To set up an Asynchronous Transmission:

- 1. Initialize the SPBRGHx:SPBRGx registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the asynchronous serial port by clearing bit, SYNC, and setting bit, SPEN.

- 3. If interrupts are desired, set enable bit, TXxIE.

- 4. If 9-bit transmission is desired, set transmit bit, TX9. Can be used as address/data bit.

- 5. Enable the transmission by setting bit, TXEN, which will also set bit, TXxIF.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 7. Load data to the TXREGx register (starts transmission).

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

#### FIGURE 21-3: EUSARTx TRANSMIT BLOCK DIAGRAM

#### REGISTER 22-11: ADCON5L: A/D CONTROL REGISTER 5 LOW

| U-0   | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-----|-------|-------|-------|-------|

| —     | —   | _   | —   | WM1   | WM0   | CM1   | CM0   |

| bit 7 |     |     |     |       |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 7-4 Unimplemented: Read as '0'

bit 3-2 **WM<1:0>:** Write Mode bits

- 11 = Reserved

- 10 = Auto-compare only (conversion results are not saved, but interrupts are generated when a valid match occurs, as defined by the CM<1:0> and ASINTMD<1:0> bits)

- 01 = Convert and save (conversion results are saved to locations as determined by the register bits when a match occurs, as defined by the CMx bits)

- 00 = Legacy operation (conversion data is saved to a location determined by the buffer register bits)

#### bit 1-0 CM<1:0>: Compare Mode bits

- 11 = Outside Window mode (valid match occurs if the conversion result is outside of the window, defined by the corresponding buffer pair)

- 10 = Inside Window mode (valid match occurs if the conversion result is inside the window, defined by the corresponding buffer pair)

- 01 = Greater Than mode (valid match occurs if the result is greater than the value in the corresponding buffer register)

- 00 = Less Than mode (valid match occurs if the result is less than the value in the corresponding buffer register)

#### 26.1 CTMU Registers

The control registers for the CTMU are:

- CTMUCON1

- CTMUCON2

- CTMUCON3

- CTMUCON4

The CTMUCON1 and CTMUCON3 registers (Register 26-1 and Register 26-3) contain control bits for configuring the CTMU module edge source selection, edge source polarity selection, edge sequencing, A/D trigger, analog circuit capacitor discharge and enables. The CTMUCON2 register (Register 26-2) has bits for selecting the current source range and current source trim.

#### REGISTER 26-1: CTMUCON1: CTMU CONTROL REGISTER 1

| R/W-0  | U-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0    | R/W-0   | R/W-0  |

|--------|-----|----------|-------|-------|----------|---------|--------|

| CTMUEN | —   | CTMUSIDL | TGEN  | EDGEN | EDGSEQEN | IDISSEN | CTTRIG |

| bit 7  |     |          |       |       |          |         | bit 0  |

|        |     |          |       |       |          |         |        |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 7 | CTMUEN: CTMU Enable bit                                                                                                              |

|-------|--------------------------------------------------------------------------------------------------------------------------------------|

|       | 1 = Module is enabled                                                                                                                |

|       | 0 = Module is disabled                                                                                                               |

| bit 6 | Unimplemented: Read as '0'                                                                                                           |

| bit 5 | CTMUSIDL: Stop in Idle Mode bit                                                                                                      |

|       | <ul><li>1 = Discontinues module operation when device enters Idle mode</li><li>0 = Continues module operation in Idle mode</li></ul> |

| bit 4 | TGEN: Time Generation Enable bit                                                                                                     |

|       | 1 = Enables edge delay generation                                                                                                    |

|       | 0 = Disables edge delay generation                                                                                                   |

| bit 3 | EDGEN: Edge Enable bit                                                                                                               |

|       | 1 = Edges are not blocked                                                                                                            |

|       | 0 = Edges are blocked                                                                                                                |

| bit 2 | ESGSEQEN: Edge Sequence Enable bit                                                                                                   |

|       | 1 = Edge 1 event must occur before Edge 2 event can occur                                                                            |

|       | 0 = No edge sequence is needed                                                                                                       |

| bit 1 | IDISSEN: Analog Current Source Control bit                                                                                           |

|       | 1 = Analog current source output is grounded                                                                                         |

|       | 0 = Analog current source output is not grounded                                                                                     |

| bit 0 | CTTRIG: CTMU Special Event Trigger bit                                                                                               |

|       | 1 = CTMU Special Event Trigger is enabled                                                                                            |

|       | 0 = CTMU Special Event Trigger is disabled                                                                                           |

|       |                                                                                                                                      |

#### EXAMPLE 26-3: CTMU CAPACITANCE CALIBRATION ROUTINE

```

#include "pl8cxxx.h"

#define COUNT 25

//@ 8MHz INTFRC = 62.5 us.

#define ETIME COUNT*2.5

//time in uS

#define DELAY for(i=0;i<COUNT;i++)</pre>

#define ADSCALE 1023

//for unsigned conversion 10 sig bits

#define ADREF 3.3

//Vdd connected to A/D Vr+

#define RCAL .027

//R value is 4200000 (4.2M)

//scaled so that result is in

//1/100th of uA

int main(void)

{

int i;

int j = 0;

//index for loop

unsigned int Vread = 0;

float CTMUISrc, CTMUCap, Vavg, VTot, Vcal;

//assume CTMU and A/D have been setup correctly

//see Example 25-1 for CTMU & A/D setup

setup();

CTMUCONbits.CTMUEN = 1;

//Enable the CTMU

for(j=0;j<10;j++)</pre>

{

CTMUCONbits.IDISSEN = 1;

//drain charge on the circuit

DELAY;

//wait 125us

CTMUCONbits.IDISSEN = 0;

//end drain of circuit

CTMUCON3bits.EDG1STAT = 1;

//Begin charging the circuit

//using CTMU current source

DELAY;

//wait for 125us

CTMUCON3bits.EDG1STAT = 0;

//Stop charging circuit

PIR1bits.ADIF = 0;

//make sure A/D Int not set

ADCON1Lbits.SAMP=1;

//and begin A/D conv.

while(!PIR1bits.ADIF);

//Wait for A/D convert complete

Vread = ADRES;

//Get the value from the A/D

PIR1bits.ADIF = 0;

//Clear A/D Interrupt Flag

VTot += Vread;

/\,/\text{Add} the reading to the total

}

Vavg = (float)(VTot/10.000);

//Average of 10 readings

Vcal = (float)(Vavg/ADSCALE*ADREF);

//CTMUISrc is in 1/100ths of uA

CTMUISrc = Vcal/RCAL;

CTMUCap = (CTMUISrc*ETIME/Vcal)/100;

}

```

#### REGISTER 28-8: CONFIG5L: CONFIGURATION REGISTER 5 LOW (BYTE ADDRESS 300008h)

| R/WO-1              | R/WO-1 | R/WO-1 | R/WO-1 | R/WO-1 | U-1 | R/WO-1  | R/WO-1 |

|---------------------|--------|--------|--------|--------|-----|---------|--------|

| WAIT <sup>(1)</sup> | BW     | ABW1   | ABW0   | EASHFT | —   | CINASEL | T5GSEL |

| bit 7               |        |        |        |        |     |         | bit 0  |

| Legend:           | P = Programmable bit | WO = Write-Once bit   |                    |

|-------------------|----------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7   | WAIT: External Bus Wait Enable bit <sup>(1)</sup>                                                                                                                                                                                                                              |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Wait selections from WAIT&lt;1:0&gt; (MEMCON&lt;5:4&gt;) are unavailable and the device will not wait</li> <li>0 = Wait is programmed by WAIT&lt;1:0&gt; (MEMCON&lt;5:4&gt;)</li> </ul>                                                                           |

| bit 6   | BW: Data Bus Width Select bit                                                                                                                                                                                                                                                  |

|         | 1 = 16-Bit External Bus mode                                                                                                                                                                                                                                                   |

|         | 0 = 8-Bit External Bus mode                                                                                                                                                                                                                                                    |

| bit 5-4 | ABW<1:0>: External Memory Bus Configuration bits                                                                                                                                                                                                                               |

|         | 00 =Extended Microcontroller Mode – 20-Bit Address mode                                                                                                                                                                                                                        |

|         | 01 =Extended Microcontroller Mode – 16-Bit Address mode                                                                                                                                                                                                                        |

|         | 10 =Extended Microcontroller Mode – 12-Bit Address mode                                                                                                                                                                                                                        |

|         | 11 =Microcontroller Mode – External bus is disabled                                                                                                                                                                                                                            |

| bit 3   | EASHFT: External Address Bus Shift Enable bit                                                                                                                                                                                                                                  |

|         | <ul> <li>1 = Address shifting is enabled – External address bus is shifted to start at 000000h</li> <li>0 = Address shifting is disabled – External address bus reflects the PC value</li> </ul>                                                                               |

| bit 2   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                     |

| bit 1   | CINASEL: CxINA Gate Select bit                                                                                                                                                                                                                                                 |

|         | 1 = C1INA and C3INA are on their default pin locations                                                                                                                                                                                                                         |

|         | 0 = C1INA and C3INA are all remapped to pin, RA5                                                                                                                                                                                                                               |

| bit 0   | T5GSEL: TMR5 Gate Select bit                                                                                                                                                                                                                                                   |

|         | 1 = TMR5 gate is driven by the T5G input                                                                                                                                                                                                                                       |

|         | 0 = TMR5 gate is driven by the T3G input                                                                                                                                                                                                                                       |

| Note 1: | This bit was previously referred to as 'WAIT', but a set condition actually indicates the case where the EMB does not wait and the name was therefore changed to reflect this. No change in functionality or polarity occurred, only a change in the name of the register bit. |

© 2012-2016 Microchip Technology Inc.

| CLRF                                                | Clear f                                                                                                                                           | CLRWDT                                 | Clear Watchdog Timer                                                                                                                     |