Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                       |

| Peripherals                | Brown-out Detect/Reset, HLVD, LCD, POR, PWM, WDT                           |

| Number of I/O              | 86                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                  |

| Data Converters            | A/D 24x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 100-TQFP                                                                   |

| Supplier Device Package    | 100-TQFP (14x14)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f95j94-i-pf |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| R/W-0        | R-x                                                                                                    | R-x                                   | R-x              | U-0             | R/W-x           | R/W-x           | R/W-x |  |  |

|--------------|--------------------------------------------------------------------------------------------------------|---------------------------------------|------------------|-----------------|-----------------|-----------------|-------|--|--|

| IDLEN        | COSC2                                                                                                  | COSC1                                 | COSC0            |                 | NOSC2           | NOSC1           | NOSC0 |  |  |

| bit 7        |                                                                                                        |                                       |                  |                 |                 |                 | bit ( |  |  |

|              |                                                                                                        |                                       |                  |                 |                 |                 |       |  |  |

| Legend:      |                                                                                                        |                                       |                  |                 |                 |                 |       |  |  |

| R = Readab   |                                                                                                        | W = Writable                          |                  |                 | emented bit, re |                 |       |  |  |

| -n = Value a | t POR                                                                                                  | '1' = Bit is set                      |                  | '0' = Bit is c  | eared           | x = Bit is unkn | own   |  |  |

|              |                                                                                                        |                                       |                  |                 |                 |                 |       |  |  |

| bit 7        | IDLEN: Idle                                                                                            |                                       |                  |                 |                 |                 |       |  |  |

|              |                                                                                                        | nstruction invok<br>Instruction invok |                  | ,<br>,          |                 |                 |       |  |  |

| bit 6-4      |                                                                                                        | : Current Oscill                      |                  |                 | 0               |                 |       |  |  |

| DIL 0-4      |                                                                                                        |                                       |                  | bits (read-only | ()              |                 |       |  |  |

|              | 000 = Fast RC Oscillator (FRC)                                                                         |                                       |                  |                 |                 |                 |       |  |  |

|              | 001 = Fast RC Oscillator (FRC), divided by N, with PLL module<br>010 = Primary Oscillator (MS, HS, EC) |                                       |                  |                 |                 |                 |       |  |  |

|              |                                                                                                        | ry Oscillator (M                      |                  | h PLL module    | 9               |                 |       |  |  |

|              |                                                                                                        | dary Oscillator                       | ,                |                 |                 |                 |       |  |  |

|              | 101 = Low-Power RC Oscillator (LPRC)                                                                   |                                       |                  |                 |                 |                 |       |  |  |

|              | 110 = Fast RC Oscillator (FRC) divided by 16 (500 kHz)                                                 |                                       |                  |                 |                 |                 |       |  |  |

|              |                                                                                                        | RC Oscillator (F                      | , ,              | ' N             |                 |                 |       |  |  |

| bit 3        | Unimpleme                                                                                              | nted: Read as '                       | 0'               |                 |                 |                 |       |  |  |

| bit 2-0      | NOSC<2:0>                                                                                              | : New Oscillato                       | r Selection bits |                 |                 |                 |       |  |  |

|              |                                                                                                        | 000 = Fast RC Oscillator (FRC)        |                  |                 |                 |                 |       |  |  |

|              | 001 = Fast RC Oscillator (FRC), divided by N, with PLL module                                          |                                       |                  |                 |                 |                 |       |  |  |

|              | 010 = Primary Oscillator (MS, HS, EC)                                                                  |                                       |                  |                 |                 |                 |       |  |  |

|              | 011 = Primary Oscillator (MS, HS, EC) with PLL module<br>100 = Secondary Oscillator (SOSC)             |                                       |                  |                 |                 |                 |       |  |  |

|              |                                                                                                        | •                                     | · · ·            |                 |                 |                 |       |  |  |

|              | 101 = Low-Power RC Oscillator (LPRC)                                                                   |                                       |                  |                 |                 |                 |       |  |  |

|              | 101 = Low-Power RC Oscillator (LPRC)<br>110 = Fast RC Oscillator (FRC) divided by 16 (500 kHz)         |                                       |                  |                 |                 |                 |       |  |  |

| EXTR <sup>(1)</sup> —         SWDTEN <sup>(2)</sup> —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         … <th…< th="">         …</th…<> | R/W-0, HS           | U-0 | R/W-0                 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----|-----------------------|-----|-----|-----|-----|-------|

| bit 7 bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | EXTR <sup>(1)</sup> | _   | SWDTEN <sup>(2)</sup> | _   | —   | —   | —   | —     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | bit 7               |     |                       |     |     |     |     | bit 0 |

#### REGISTER 5-2: RCON2: RESET CONTROL REGISTER 2

| Legend:           | HS = Hardware Settable bit |                             |                    |  |

|-------------------|----------------------------|-----------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |  |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |  |

| bit 7   | EXTR: External Reset (MCLR) Pin bit <sup>(1)</sup>                                                                       |

|---------|--------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = A Master Clear (pin) Reset has occurred</li> <li>0 = A Master Clear (pin) Reset has not occurred</li> </ul> |

| bit 6   | Unimplemented: Read as '0'                                                                                               |

| bit 5   | SWDTEN: Software Controlled Watchdog Timer Enable bit <sup>(2)</sup>                                                     |

|         | <ol> <li>1 = Watchdog Timer is on</li> <li>0 = Watchdog Timer is off</li> </ol>                                          |

| bit 4-0 | Unimplemented: Read as '0'                                                                                               |

|         |                                                                                                                          |

Note 1: This bit is set in hardware; it can be cleared in software.

2: This bit has no effect unless the Configuration bits, WDTEN<1:0> = 10.

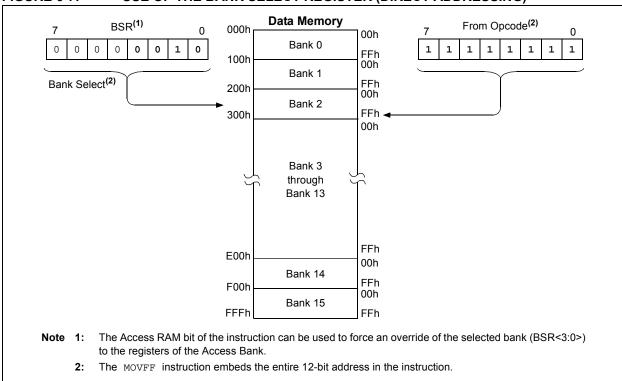

#### FIGURE 6-7: USE OF THE BANK SELECT REGISTER (DIRECT ADDRESSING)

## 6.3.2 ACCESS BANK

While the use of the BSR, with an embedded 8-bit address, allows users to address the entire range of data memory, it also means that the user must ensure that the correct bank is selected. If not, data may be read from, or written to, the wrong location. This can be disastrous if a GPR is the intended target of an operation, but an SFR is written to instead. Verifying and/or changing the BSR for each read or write to data memory can become very inefficient.

To streamline access for the most commonly used data memory locations, the data memory is configured with an Access Bank, which allows users to access a mapped block of memory without specifying a BSR. The Access Bank consists of the first 96 bytes of memory (00h-5Fh) in Bank 0 and the last 160 bytes of memory (60h-FFh) in Bank 15. The lower half is known as the "Access RAM" and is composed of GPRs. The upper half is where the device's SFRs are mapped. These two areas are mapped contiguously in the Access Bank and can be addressed in a linear fashion by an 8-bit address (Figure 6-6).

The Access Bank is used by core PIC18 instructions that include the Access RAM bit (the 'a' parameter in the instruction). When 'a' is equal to '1', the instruction uses the BSR and the 8-bit address included in the opcode for the data memory address. When 'a' is '0', however, the instruction is forced to use the Access Bank address map. In that case, the current value of the BSR is ignored entirely.

Using this "forced" addressing allows the instruction to operate on a data address in a single cycle without updating the BSR first. For 8-bit addresses of 60h and above, this means that users can evaluate and operate on SFRs more efficiently. The Access RAM below 60h is a good place for data values that the user might need to access rapidly, such as immediate computational results or common program variables.

Access RAM also allows for faster and more code efficient context saving and switching of variables.

The mapping of the Access Bank is slightly different when the extended instruction set is enabled (XINST Configuration bit = 1). This is discussed in more detail in Section 6.6.3 "Mapping the Access Bank in Indexed Literal Offset Mode".

#### 6.3.3 GENERAL PURPOSE REGISTER FILE

PIC18 devices may have banked memory in the GPR area. This is data RAM which is available for use by all instructions. GPRs start at the bottom of Bank 0 (address 000h) and grow upwards towards the bottom of the SFR area. GPRs are not initialized by a Power-on Reset and are unchanged on all other Resets.

# 10.7 IPR Registers

The IPR registers contain the individual priority bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are six Peripheral Interrupt Priority registers (IPR1 through IPR6). Using the priority bits requires that the Interrupt Priority Enable (IPEN) bit (RCON<7>) be set.

## REGISTER 10-16: IPR1: PERIPHERAL INTERRUPT PRIORITY REGISTER 1

| Logondy |       |       |       |        |         |        |        |

|---------|-------|-------|-------|--------|---------|--------|--------|

| bit 7   |       |       |       |        |         |        | bit 0  |

| PSPIP   | ADIP  | RC1IP | TX1IP | SSP1IP | TMR1GIP | TMR2IP | TMR1IP |

| R/W-1   | R/W-1 | R/W-1 | R/W-1 | R/W-1  | R/W-1   | R/W-1  | R/W-1  |

| Legena:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 7 | PSPIP: Parallel Slave Port Read/Write Interrupt Priority bit    |

|-------|-----------------------------------------------------------------|

|       | 1 = High priority                                               |

|       | 0 = Low priority                                                |

| bit 6 | ADIP: A/D Converter Interrupt Priority bit                      |

|       | 1 = High priority                                               |

|       | 0 = Low priority                                                |

| bit 5 | RC1IP: EUSART1 Receive Interrupt Priority bit                   |

|       | 1 = High priority                                               |

|       | 0 = Low priority                                                |

| bit 4 | TX1IP: EUSART1 Transmit Interrupt Priority bit                  |

|       | 1 = High priority                                               |

|       | 0 = Low priority                                                |

| bit 3 | SSP1IP: Master Synchronous Serial Port 1 Interrupt Priority bit |

|       | 1 = High priority                                               |

|       | 0 = Low priority                                                |

| bit 2 | TMR1GIP: Timer1 Gate Interrupt Priority bit                     |

|       | 1 = High priority                                               |

|       | 0 = Low priority                                                |

| bit 1 | TMR2IP: TMR2 to PR2 Match Interrupt Priority bit                |

|       |                                                                 |

|       | 1 = High priority                                               |

|       | 1 = High priority<br>0 = Low priority                           |

| bit 0 |                                                                 |

| bit 0 | 0 = Low priority                                                |

| R/W-1                                            | R/W-1                         | R/W-1            | R/W-1         | R/W-1            | R/W-1           | R/W-1          | R/W-1   |

|--------------------------------------------------|-------------------------------|------------------|---------------|------------------|-----------------|----------------|---------|

| CCP10IP                                          | CCP9IP                        | CCP8IP           | CCP7IP        | CCP6IP           | CCP5IP          | CCP4IP         | ECCP3IP |

| bit 7                                            |                               |                  |               |                  |                 |                | bit (   |

|                                                  |                               |                  |               |                  |                 |                |         |

| Legend:                                          |                               |                  |               |                  |                 |                |         |

| R = Readable                                     |                               | W = Writable     |               | •                | nented bit, rea |                |         |

| -n = Value at                                    | POR                           | '1' = Bit is set |               | '0' = Bit is cle | ared            | x = Bit is unk | nown    |

| bit 7                                            | <b>CCP10IP:</b> CC            | CP10 Interrupt   | Priority bit  |                  |                 |                |         |

|                                                  | 1 = High pric                 |                  |               |                  |                 |                |         |

|                                                  | 0 = Low prio                  | rity             |               |                  |                 |                |         |

| bit 6                                            |                               | P9 Interrupt Pr  | ority bit     |                  |                 |                |         |

|                                                  | 1 = High pric                 |                  |               |                  |                 |                |         |

| L:1 F                                            | 0 = Low prior                 | -                |               |                  |                 |                |         |

| bit 5                                            | 1 = High pric                 | P8 Interrupt Pr  | ority dit     |                  |                 |                |         |

|                                                  | 1 = High pho0 = Low prior     |                  |               |                  |                 |                |         |

| bit 4                                            | •                             | P7 Interrupt Pr  | ority bit     |                  |                 |                |         |

|                                                  | 1 = High pric                 | •                |               |                  |                 |                |         |

|                                                  | 0 = Low prio                  | rity             |               |                  |                 |                |         |

| bit 3                                            | CCP6IP: CCI                   | P6 Interrupt Pr  | ority bit     |                  |                 |                |         |

|                                                  | 1 = High pric                 | •                |               |                  |                 |                |         |

|                                                  | 0 = Low prio                  | •                |               |                  |                 |                |         |

| bit 2 <b>CCP5IP:</b> CCP5 Interrupt Priority bit |                               |                  | ority bit     |                  |                 |                |         |

|                                                  | 1 = High pric<br>0 = Low pric |                  |               |                  |                 |                |         |

| bit 1 <b>CCP4IP:</b> CCP4 Interrupt Priority bit |                               |                  | oritv bit     |                  |                 |                |         |

|                                                  | 1 = High priority             |                  |               |                  |                 |                |         |

|                                                  | 0 = Low prio                  | rity             |               |                  |                 |                |         |

| bit 0                                            | ECCP3IP: EC                   | CCP3 Interrupt   | Priority bits |                  |                 |                |         |

|                                                  | 1 = High pric                 |                  |               |                  |                 |                |         |

|                                                  | 0 = Low prio                  | rity             |               |                  |                 |                |         |

# REGISTER 10-19: IPR4: PERIPHERAL INTERRUPT PRIORITY REGISTER 4

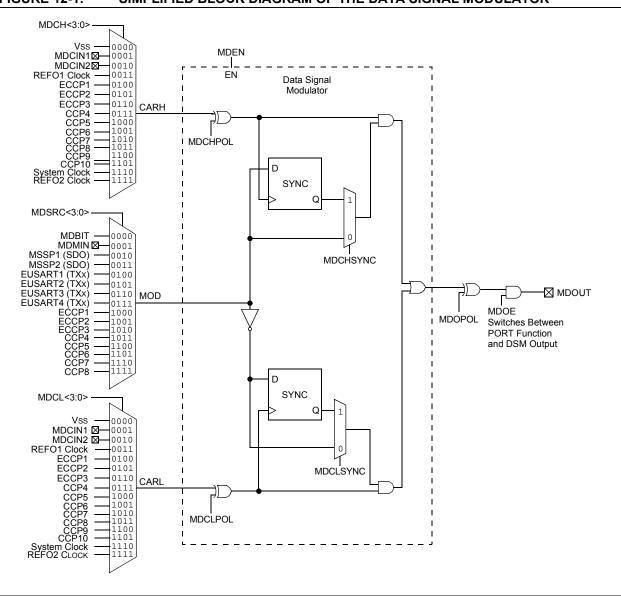

#### FIGURE 12-1: SIMPLIFIED BLOCK DIAGRAM OF THE DATA SIGNAL MODULATOR

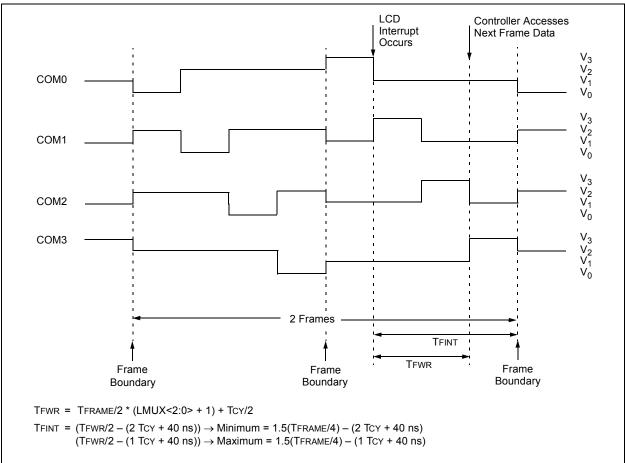

# 13.13 LCD Interrupts

The LCD timing generation provides an interrupt that defines the LCD frame timing. This interrupt can be used to coordinate the writing of the pixel data with the start of a new frame, which produces a visually crisp transition of the image.

This interrupt can also be used to synchronize external events to the LCD. For example, the interface to an external segment driver can be synchronized for segment data updates to the LCD frame.

A new frame is defined as beginning at the leading edge of the COM0 common signal. The interrupt will be set immediately after the LCD controller completes accessing all pixel data required for a frame. This will occur at a fixed interval before the frame boundary (TFINT), as shown in Figure 13-22.

The LCD controller will begin to access data for the next frame within the interval from the interrupt to when the controller begins accessing data after the interrupt (TFWR). New data must be written within TFWR, as this is when the LCD controller will begin to access the data for the next frame.

When the LCD driver is running with Type-B waveforms, and the LMUX<2:0> bits are not equal to '000', there are some additional issues.

Since the DC voltage on the pixel takes two frames to maintain 0V, the pixel data must not change between subsequent frames. If the pixel data were allowed to change, the waveform for the odd frames would not necessarily be the complement of the waveform generated in the even frames and a DC component would be introduced into the panel.

Because of this, using Type-B waveforms requires synchronizing the LCD pixel updates to occur within a subframe after the frame interrupt.

To correctly sequence writing in Type-B, the interrupt only occurs on complete phase intervals. If the user attempts to write when the write is disabled, the WERR bit (LCDCON<5>) is set.

**Note:** The interrupt is not generated when the Type-A waveform is selected and when the Type-B with no multiplex (static) is selected.

FIGURE 13-22: EXAMPLE WAVEFORMS AND INTERRUPT TIMING IN QUARTER DUTY CYCLE DRIVE

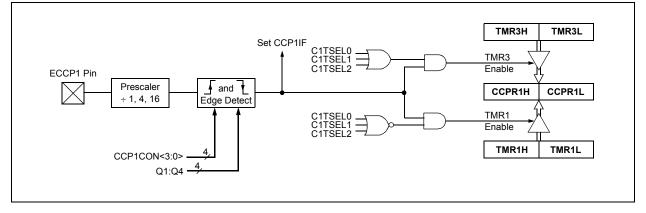

# 18.2 Capture Mode

In Capture mode, the CCPRxH:CCPRxL register pair captures the 16-bit value of the TMR1 or TMR3 registers when an event occurs on the corresponding ECCPx pin. An event is defined as one of the following:

- · Every falling edge

- Every rising edge

- Every fourth rising edge

- Every 16<sup>th</sup> rising edge

The event is selected by the mode select bits, CCPxM<3:0> (CCPxCON<3:0>). When a capture is made, the interrupt request flag bit, CCPxIF, is set (see Table 18-2). The flag must be cleared by software. If another capture occurs before the value in the CCPRxH/L register is read, the old captured value is overwritten by the new captured value.

#### TABLE 18-2: ECCP1/2/3 INTERRUPT FLAG BITS

| ECCP Module | Flag Bit |

|-------------|----------|

| 1           | PIR3<1>  |

| 2           | PIR3<2>  |

| 3           | PIR4<0>  |

## 18.2.1 ECCP PIN CONFIGURATION

In Capture mode, the appropriate ECCPx pin should be configured as an input by setting the corresponding TRIS direction bit.

| Note: | If the ECCPx pin is configured as an out-    |

|-------|----------------------------------------------|

|       | put, a write to the port can cause a capture |

|       | condition.                                   |

# 18.2.2 TIMER1/2/3/4/5/6/8 MODE SELECTION

The timers that are to be used with the capture feature (Timer1/2/3/4/5/6 or 8) must be running in Timer mode or Synchronized Counter mode. In Asynchronous Counter mode, the capture operation will not work. The timer to be used with each ECCP module is selected in the CCPTMRS0 register (Register 18-2).

# 18.2.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit clear to avoid false interrupts. The interrupt flag bit, CCPxIF, should also be cleared following any such change in operating mode.

# 18.2.4 ECCP PRESCALER

There are four prescaler settings in Capture mode; they are specified as part of the operating mode selected by the mode select bits (CCPxM<3:0>). Whenever the ECCP module is turned off, or Capture mode is disabled, the prescaler counter is cleared. This means that any Reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared; therefore, the first capture may be from a non-zero prescaler. Example 18-1 provides the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

## EXAMPLE 18-1: CHANGING BETWEEN CAPTURE PRESCALERS

| CLRF  | CCP1CON     | ; | Turn ECCP module off |

|-------|-------------|---|----------------------|

| MOVLW | NEW_CAPT_PS | ; | Load WREG with the   |

|       |             | ; | new prescaler mode   |

|       |             | ; | value and ECCP ON    |

| MOVWF | CCP1CON     | ; | Load CCP1CON with    |

|       |             | ; | this value           |

# FIGURE 18-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

# 18.4.8 OPERATION IN POWER-MANAGED MODES

In Sleep mode, all clock sources are disabled. Timer2/ 4/6/8 will not increment and the state of the module will not change. If the ECCPx pin is driving a value, it will continue to drive that value. When the device wakes up, it will continue from this state. If Two-Speed Startups are enabled, the initial start-up frequency from HF-INTOSC and the postscaler may not be stable immediately.

In PRI\_IDLE mode, the primary clock will continue to clock the ECCPx module without change.

# 18.4.8.1 Operation with Fail-Safe Clock Monitor (FSCM)

If the Fail-Safe Clock Monitor (FSCM) is enabled, a clock failure will force the device into the power-managed RC\_RUN mode and the OSCFIF bit of the PIR2 register will be set. The ECCPx will then be clocked from the internal oscillator clock source, which may have a different clock frequency than the primary clock.

# 18.4.9 EFFECTS OF A RESET

Both Power-on Reset and subsequent Resets will force all ports to Input mode and the ECCP registers to their Reset states.

This forces the ECCP module to reset to a state compatible with previous, non-enhanced CCP modules used on other PIC18 and PIC16 devices.

| R/W-0      | R/W-0                                                                                                                                                                                      | R/W-0                                                                              | R/W-0           | R/W-0                | R/W-0                  | R/W-0                                 | R/W-0                               |  |  |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------|----------------------|------------------------|---------------------------------------|-------------------------------------|--|--|--|

| WCOL       | SSPOV                                                                                                                                                                                      | SSPEN <sup>(1)</sup>                                                               | CKP             | SSPM3 <sup>(2)</sup> | SSPM2 <sup>(2)</sup>   | SSPM1 <sup>(2)</sup>                  | SSPM0 <sup>(2)</sup>                |  |  |  |

| bit 7      |                                                                                                                                                                                            |                                                                                    |                 |                      |                        |                                       | bit 0                               |  |  |  |

| Legend:    |                                                                                                                                                                                            |                                                                                    |                 |                      |                        |                                       |                                     |  |  |  |

| R = Reada  | able bit                                                                                                                                                                                   | W = Writable b                                                                     | it              | U = Unimplem         | nented bit, read       | 1 as '0'                              |                                     |  |  |  |

| -n = Value |                                                                                                                                                                                            | '1' = Bit is set                                                                   |                 | '0' = Bit is clea    |                        | x = Bit is unkr                       | NOWD                                |  |  |  |

|            |                                                                                                                                                                                            |                                                                                    |                 |                      |                        |                                       | lowin                               |  |  |  |

| bit 7      | WCOL: Write                                                                                                                                                                                | e Collision Detec                                                                  | t bit           |                      |                        |                                       |                                     |  |  |  |

|            | In Master Tra                                                                                                                                                                              |                                                                                    |                 |                      |                        |                                       |                                     |  |  |  |

|            |                                                                                                                                                                                            | to the SSPxBU                                                                      |                 |                      |                        | nditions were                         | not valid for a                     |  |  |  |

|            | transmis<br>0 = No collis                                                                                                                                                                  | sion to be starte                                                                  | d (must be cl   | eared in softwar     | re)                    |                                       |                                     |  |  |  |

|            | In Slave Tran                                                                                                                                                                              |                                                                                    |                 |                      |                        |                                       |                                     |  |  |  |

|            |                                                                                                                                                                                            | PxBUF register is                                                                  | s written while | e it is still transm | nittina the previ      | ous word (mus                         | t be cleared in                     |  |  |  |

|            | software                                                                                                                                                                                   | -                                                                                  |                 |                      | 0                      | , , , , , , , , , , , , , , , , , , , |                                     |  |  |  |

|            | 0 = No collis                                                                                                                                                                              | 0 = No collision                                                                   |                 |                      |                        |                                       |                                     |  |  |  |

|            |                                                                                                                                                                                            | In Receive mode (Master or Slave modes):                                           |                 |                      |                        |                                       |                                     |  |  |  |

|            |                                                                                                                                                                                            | This is a "don't care" bit.                                                        |                 |                      |                        |                                       |                                     |  |  |  |

| bit 6      | SSPOV: Receive Overflow Indicator bit                                                                                                                                                      |                                                                                    |                 |                      |                        |                                       |                                     |  |  |  |

|            | In Receive mode:<br>1 = A byte is received while the SSPxBUF register is still holding the previous byte (must be cleared in                                                               |                                                                                    |                 |                      |                        |                                       |                                     |  |  |  |

|            | -                                                                                                                                                                                          | software)                                                                          |                 |                      |                        |                                       |                                     |  |  |  |

|            |                                                                                                                                                                                            | 0 = No overflow                                                                    |                 |                      |                        |                                       |                                     |  |  |  |

|            | In Transmit mode:                                                                                                                                                                          |                                                                                    |                 |                      |                        |                                       |                                     |  |  |  |

|            |                                                                                                                                                                                            | This is a "don't care" bit in Transmit mode.                                       |                 |                      |                        |                                       |                                     |  |  |  |

| bit 5      |                                                                                                                                                                                            | ter Synchronous                                                                    |                 |                      |                        |                                       |                                     |  |  |  |

|            | <ul> <li>1 = Enables the serial port and configures the SDAx and SCLx pins as the serial port pins</li> <li>0 = Disables serial port and configures these pins as I/O port pins</li> </ul> |                                                                                    |                 |                      |                        |                                       |                                     |  |  |  |

| bit 4      | CKP: SCKx I                                                                                                                                                                                | Release Control                                                                    | bit             |                      | -                      |                                       |                                     |  |  |  |

|            | In Slave mode:                                                                                                                                                                             |                                                                                    |                 |                      |                        |                                       |                                     |  |  |  |

|            |                                                                                                                                                                                            | 1 = Releases clock                                                                 |                 |                      |                        |                                       |                                     |  |  |  |

|            | 0 = Holds clock low (clock stretch), used to ensure data setup time                                                                                                                        |                                                                                    |                 |                      |                        |                                       |                                     |  |  |  |

|            | <u>In Master mo</u><br>Unused in thi                                                                                                                                                       |                                                                                    |                 |                      |                        |                                       |                                     |  |  |  |

| bit 3-0    | SSPM<3:0>:                                                                                                                                                                                 | Master Synchro                                                                     | nous Serial F   | Port Mode Selec      | ct bits <sup>(2)</sup> |                                       |                                     |  |  |  |

|            | <b>SSPM&lt;3:0&gt;:</b> Master Synchronous Serial Port Mode Select bits <sup>(2)</sup><br>1111 = I <sup>2</sup> C Slave mode: 10-bit address with Start and Stop bit interrupts enabled    |                                                                                    |                 |                      |                        |                                       |                                     |  |  |  |

|            | $1110 = I^2 C S$                                                                                                                                                                           | 1110 = $I^2C$ Slave mode: 7-bit address with Start and Stop bit interrupts enabled |                 |                      |                        |                                       |                                     |  |  |  |

|            | $1011 = I^2 C F$                                                                                                                                                                           | 1011 = I <sup>2</sup> C Firmware Controlled Master mode (slave Idle)               |                 |                      |                        |                                       |                                     |  |  |  |

|            |                                                                                                                                                                                            | 1001 = Load SSPxMSK register at SSPxADD SFR address <sup>(3,4)</sup>               |                 |                      |                        |                                       |                                     |  |  |  |

|            | 1000 = I <sup>2</sup> C Master mode: Clock = Fosc/(4 * (SSPxADD + 1))<br>0111 = I <sup>2</sup> C Slave mode: 10-bit address <sup>(3,4)</sup>                                               |                                                                                    |                 |                      |                        |                                       |                                     |  |  |  |

|            | $0110 = I^2 C S$                                                                                                                                                                           | Blave mode: 7-bi                                                                   | address         |                      |                        |                                       |                                     |  |  |  |

| Note 1:    | When enabled, th                                                                                                                                                                           | ne SDAx and SC                                                                     | Lx pins must    | t be configured a    | as inputs.             |                                       |                                     |  |  |  |

|            | Bit combinations                                                                                                                                                                           | not specifically I                                                                 | isted here are  | e either reserved    | d or implement         | ed in SPI mode                        | e only.                             |  |  |  |

| 2:         |                                                                                                                                                                                            | not op oom oan y i                                                                 |                 |                      |                        |                                       | · · · · · · · · · · · · · · · · · · |  |  |  |

| 2:<br>3:   | When SSPM<3:0                                                                                                                                                                              |                                                                                    |                 |                      | DD SFR addre           | ss actually acc                       | -                                   |  |  |  |

|            | When SSPM<3:0<br>SSPxMSK regist<br>This mode is only                                                                                                                                       | )> = 1001, any r<br>er.                                                            | eads or write   | s to the SSPxAI      |                        | -                                     | esses the                           |  |  |  |

# 20.5.7 CLOCK STRETCHING

Both 7-Bit and 10-Bit Slave modes implement automatic clock stretching during a transmit sequence.

The SEN bit (SSPxCON2<0>) allows clock stretching to be enabled during receives. Setting SEN will cause the SCLx pin to be held low at the end of each data receive sequence.

# 20.5.7.1 Clock Stretching for 7-Bit Slave Receive Mode (SEN = 1)

In 7-Bit Slave Receive mode, on the falling edge of the ninth clock at the end of the ACK sequence, if the BF bit is set, the CKP bit in the SSPxCON1 register is automatically cleared, forcing the SCLx output to be held low. The CKP bit, being cleared to '0', will assert the SCLx line low. The CKP bit must be set in the user's ISR before reception is allowed to continue. By holding the SCLx line low, the user has time to service the ISR and read the contents of the SSPxBUF before the master device can initiate another receive sequence. This will prevent buffer overruns from occurring (see Figure 20-15).

- Note 1: If the user reads the contents of the SSPxBUF before the falling edge of the ninth clock, thus clearing the BF bit, the CKP bit will not be cleared and clock stretching will not occur.

- 2: The CKP bit can be set in software regardless of the state of the BF bit. The user should be careful to clear the BF bit in the ISR before the next receive sequence in order to prevent an overflow condition.

# 20.5.7.2 Clock Stretching for 10-Bit Slave Receive Mode (SEN = 1)

In 10-Bit Slave Receive mode, during the address sequence, clock stretching automatically takes place but CKP is not cleared. During this time, if the UA bit is set after the ninth clock, clock stretching is initiated. The UA bit is set after receiving the upper byte of the 10-bit address, and following the receive of the second byte of the 10-bit address, with the R/W bit cleared to '0'. The release of the clock line occurs upon updating SSPxADD. Clock stretching will occur on each data receive sequence as described in 7-bit mode.

**Note:** If the user polls the UA bit and clears it by updating the SSPxADD register before the falling edge of the ninth clock occurs, and if the user hasn't cleared the BF bit by reading the SSPxBUF register before that time, then the CKP bit will still NOT be asserted low. Clock stretching, on the basis of the state of the BF bit, only occurs during a data sequence, not an address sequence.

# 20.5.7.3 Clock Stretching for 7-Bit Slave Transmit Mode

The 7-Bit Slave Transmit mode implements clock stretching by clearing the CKP bit after the falling edge of the ninth clock if the BF bit is clear. This occurs regardless of the state of the SEN bit.

The user's ISR must set the CKP bit before transmission is allowed to continue. By holding the SCLx line low, the user has time to service the ISR and load the contents of the SSPxBUF before the master device can initiate another transmit sequence (see Figure 20-10).

- Note 1: If the user loads the contents of SSPxBUF, setting the BF bit before the falling edge of the ninth clock, the CKP bit will not be cleared and clock stretching will not occur.

- **2:** The CKP bit can be set in software, regardless of the state of the BF bit.

# 20.5.7.4 Clock Stretching for 10-Bit Slave Transmit Mode

In 10-Bit Slave Transmit mode, clock stretching is controlled during the first two address sequences by the state of the UA bit, just as it is in 10-Bit Slave Receive mode. The first two addresses are followed by a third address sequence, which contains the highorder bits of the 10-bit address and the R/W bit set to '1'. After the third address sequence is performed, the UA bit is not set, the module is now configured in Transmit mode and clock stretching is controlled by the BF flag as in 7-Bit Slave Transmit mode (see Figure 20-13).

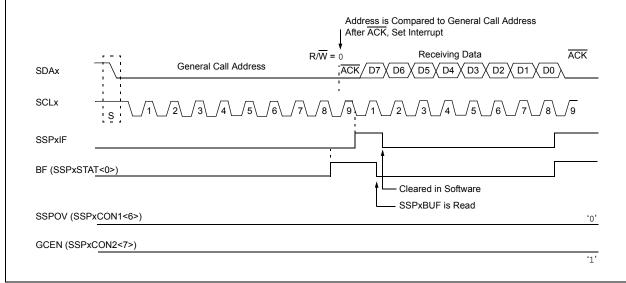

#### 20.5.8 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the I<sup>2</sup>C bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an Acknowledge.

The general call address is one of eight addresses reserved for specific purposes by the I<sup>2</sup>C protocol. It consists of all '0's with R/W = 0.

The general call address is recognized when the General Call Enable bit, GCEN, is enabled (SSPx-CON2<7> set). Following a Start bit detect, eight bits are shifted into the SSPxSR and the address is compared against the SSPxADD. It is also compared to the general call address and fixed in hardware.

If the general call address matches, the SSPxSR is transferred to the SSPxBUF, the BF flag bit is set (eighth bit), and on the falling edge of the ninth bit (ACK bit), the SSPxIF interrupt flag bit is set.

When the interrupt is serviced, the source for the interrupt can be checked by reading the contents of the SSPxBUF. The value can be used to determine if the address was device-specific or a general call address.

In 10-Bit Addressing mode, the SSPxADD is required to be updated for the second half of the address to match and the UA bit is set (SSPxSTAT<1>). If the general call address is sampled when the GCEN bit is set, while the slave is configured in 10-Bit Addressing mode, then the second half of the address is not necessary, the UA bit will not be set and the slave will begin receiving data after the Acknowledge (Figure 20-17).

| R/W-0         | R/W-0                   | R/W-0                                  | R/W-0           | R/W-0           | R/W-0            | R/W-0          | R/W-0  |

|---------------|-------------------------|----------------------------------------|-----------------|-----------------|------------------|----------------|--------|

| CH0NB2        | CH0NB1                  | CH0NB0                                 | CH0SB4          | CH0SB3          | CH0SB2           | CH0SB1         | CH0SB0 |

| bit 7         | ·                       |                                        | ·               | ·               |                  |                | bit (  |

| Legend:       |                         |                                        |                 |                 |                  |                |        |

| R = Readable  | e bit                   | W = Writable                           | bit             | U = Unimple     | emented bit, rea | id as '0'      |        |

| -n = Value at | POR                     | '1' = Bit is set                       |                 | '0' = Bit is cl | eared            | x = Bit is unk | nown   |

| bit 7-5       | CH0NB<2:0               | >: Sample B Ch                         | annel 0 Negat   | ive Input Sele  | ct bits          |                |        |

|               | 1xx = Unim              | -                                      |                 |                 |                  |                |        |

|               | 011 = Unim              |                                        |                 |                 |                  |                |        |

|               | 010 = AN1               | pionioniou                             |                 |                 |                  |                |        |

|               | 001 = Unim              | plemented                              |                 |                 |                  |                |        |

|               | 000 = VREF-             |                                        |                 |                 |                  |                |        |

| bit 4-0       |                         | Sample B Ch                            | annel A Positiv | ve Innut Selec  | t hite           |                |        |

| 511 4-0       | 11111 = VBA             |                                        |                 | liput Selec     |                  |                |        |

|               | 11111 - VBA             |                                        |                 |                 |                  |                |        |

|               | 11110 - AVL             |                                        |                 |                 |                  |                |        |

|               |                         |                                        | (1,3)           |                 |                  |                |        |

|               |                         | nd gap reference<br>3/2 <sup>(1)</sup> |                 |                 |                  |                |        |

|               | 11010 = VBG             | 5/2(1)                                 |                 |                 |                  |                |        |

|               | 11001 = CTN             |                                        |                 |                 |                  |                |        |

|               |                         | MU temperature                         | sensor input    | does not real   |                  | 11H<0> to be s | et)    |

|               | 10111 = AN2             |                                        |                 |                 |                  |                | 01)    |

|               | 10110 = AN2             |                                        |                 |                 |                  |                |        |

|               | 10101 = AN2             |                                        |                 |                 |                  |                |        |

|               | 10100 = AN2             |                                        |                 |                 |                  |                |        |

|               | 10011 = AN <sup>2</sup> |                                        |                 |                 |                  |                |        |

|               | 10010 = AN'             | -                                      |                 |                 |                  |                |        |

|               | 10001 <b>= AN</b>       |                                        |                 |                 |                  |                |        |

|               | 10000 <b>= AN</b>       | 16                                     |                 |                 |                  |                |        |

|               | 01111 = AN'             | 15                                     |                 |                 |                  |                |        |

|               | 01110 = AN <sup>2</sup> | 14                                     |                 |                 |                  |                |        |

|               | 01101 = AN <sup>2</sup> | 13                                     |                 |                 |                  |                |        |

|               | 01100 = AN <sup>2</sup> | 12                                     |                 |                 |                  |                |        |

|               | 01011 = AN <sup>2</sup> | 11                                     |                 |                 |                  |                |        |

|               | 01010 = AN <sup>2</sup> | 10                                     |                 |                 |                  |                |        |

|               | 01001 = ANS             | 9                                      |                 |                 |                  |                |        |

|               | 01000 = AN8             | 3                                      |                 |                 |                  |                |        |

|               | 00111 = AN7             | 7                                      |                 |                 |                  |                |        |

|               | 00110 =AN6              |                                        |                 |                 |                  |                |        |

|               | 00101 <b>= AN</b>       |                                        |                 |                 |                  |                |        |

|               | 00100 = AN4             | -                                      |                 |                 |                  |                |        |

|               | 00011 <b>= AN</b> 3     | -                                      |                 |                 |                  |                |        |

|               | 00010 = AN2             |                                        |                 |                 |                  |                |        |

|               | 00001 = AN <sup>2</sup> |                                        |                 |                 |                  |                |        |

|               | 00000 = ANG             | )                                      |                 |                 |                  |                |        |

- **Note 1:** These input channels do not have corresponding memory mapped result buffers.

- 2: These channels are implemented in 80-pin and 100-pin devices only.

- **3:** For accurately sampling the band gap set SMPI bits in ADCON2L register to 0, so that the ADC samples the band gap only once on every trigger. When the band gap is sampled multiple times, a large capacitive load is connected to the output of the band gap multiple times, which could cause the output to become unstable for a while and an overshoot or undershoot could be sampled.

## 22.8.2.2 A/D Conversions While Scanning Through All Analog Inputs

Figure 22-17 and Example 22-5 illustrate a typical setup, where all available analog input channels are sampled and converted. In this instance, 16 analog inputs are assumed. The set CSCNA bit specifies scanning of the A/D inputs to the S/H positive input.

Other conditions are similar to those located in Section Section 22.8.2.1 "Sampling and Converting a Single Channel Multiple Times".

Initially, the AN0 input is sampled and converted. The result is stored in the ADCBUFn buffer. Then, the AN1 input is sampled and converted. This process of scanning the inputs repeats 16 times, until the buffer is full, and then the module generates an interrupt. The entire process will then repeat.

| Conversion<br>Trigger ——— | -TSAMP       |                    | -Tsamp- | ۰<br>۲<br>۲ | TSAMP>      | <b>⊸</b> Ts/ | AMP-> |              |

|---------------------------|--------------|--------------------|---------|-------------|-------------|--------------|-------|--------------|

| A/D CLK                   | 1<br>1<br>1  |                    |         | ₩ <u></u>   |             |              |       | ∩∩∩ <u>¦</u> |

| Analog Input              | <u>'</u>     | AN0 X              | AN1     |             | X AN14      | X            | AN15  | X            |

| ASAM                      |              | I<br>I             |         |             | 1<br>1<br>1 | <br>         |       | 1            |

| SAMP                      |              |                    |         | SS          |             |              |       |              |

| DONE                      | 1<br>1<br>1  | 1<br>1<br>1        |         |             | <br> <br>   | 1<br>1<br>1  |       |              |

| ADC1BUF0                  | <br> <br>    | X                  |         | <u></u>     |             |              |       | 1            |

| ADC1BUF1                  | <br> <br>    | <br> <br>          |         |             | <br> <br>   | 1            |       | <br> <br>    |

| ADC1BUFE                  | 1            | <br> <br>          |         |             | <br> <br>   | X            |       | <br> <br>    |

| ADC1BUFF                  | 1            | 1                  |         |             | <br> <br>   | <br> <br>    |       |              |

| AD1IF                     | 1            | 1                  |         |             | <br> <br>   | 1<br>1       |       |              |

| BSET ADICONI              | , #ASAM X II | nstruction Executi | ion     | 1           |             | 1            |       | 1            |

FIGURE 22-17: SCANNING ALL 16 INPUTS PER SINGLE INTERRUPT

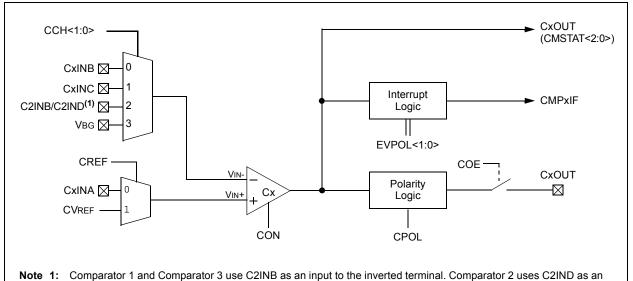

# 23.0 COMPARATOR MODULE

The analog comparator module contains three comparators that can be independently configured in a variety of ways. The inputs can be selected from the analog inputs and two internal voltage references. The digital outputs are available at the pin level, via PPS-Lite, and can also be read through the control register. Multiple output and interrupt event generations are also available. A generic single comparator from the module is shown in Figure 23-1.

Key features of the module includes:

- Independent comparator control

- Programmable input configuration

- · Output to both pin and register levels

- · Programmable output polarity

- Independent interrupt generation for each comparator with configurable interrupt-on-change

input to the inverted terminal.

# 23.1 Registers

The CMxCON registers (CM1CON, CM2CON and CM3CON) select the input and output configuration for each comparator, as well as the settings for interrupt generation (see Register 23-1).

The CMSTAT register (Register 23-2) provides the output results of the comparators. The bits in this register are read-only.

# FIGURE 23-1: COMPARATOR SIMPLIFIED BLOCK DIAGRAM

## REGISTER 27-1: UCON: USB CONTROL REGISTER

| U-0   | R/W-0                 | R-x | R/C-0  | R/W-0                | R/W-0  | R/W-0  | U-0   |

|-------|-----------------------|-----|--------|----------------------|--------|--------|-------|

| —     | PPBRST <sup>(2)</sup> | SE0 | PKTDIS | USBEN <sup>(1)</sup> | RESUME | SUSPND | —     |

| bit 7 |                       |     |        |                      |        |        | bit 0 |

| Legend:           | C = Clearable bit |                       |                    |

|-------------------|-------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7 | Unimplemented: Read as '0'                                                                                                                                                                                                    |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | PPBRST: Ping-Pong Buffers Reset bit <sup>(2)</sup>                                                                                                                                                                            |

|       | <ul> <li>1 = Reset all Ping-Pong Buffer Pointers to the Even Buffer Descriptor (BD) banks</li> <li>0 = Ping-Pong Buffer Pointers are not being reset</li> </ul>                                                               |

| bit 5 | SE0: Live Single-Ended Zero Flag bit                                                                                                                                                                                          |

|       | <ul><li>1 = Single-ended zero is active on the USB bus</li><li>0 = No single-ended zero is detected</li></ul>                                                                                                                 |

| bit 4 | PKTDIS: Packet Transfer Disable bit                                                                                                                                                                                           |

|       | <ul> <li>1 = SIE token and packet processing are disabled, automatically set when a SETUP token is received</li> <li>0 = SIE token and packet processing are enabled</li> </ul>                                               |

| bit 3 | USBEN: USB Module Enable bit <sup>(1)</sup>                                                                                                                                                                                   |

|       | <ul><li>1 = USB module and supporting circuitry are enabled (device attached)</li><li>0 = USB module and supporting circuitry are disabled (device detached)</li></ul>                                                        |

| bit 2 | RESUME: Resume Signaling Enable bit                                                                                                                                                                                           |

|       | <ul><li>1 = Resume signaling is activated</li><li>0 = Resume signaling is disabled</li></ul>                                                                                                                                  |

| bit 1 | SUSPND: Suspend USB bit                                                                                                                                                                                                       |

|       | <ul> <li>1 = USB module and supporting circuitry are in Power Conserve mode, SIE clock is inactive</li> <li>0 = USB module and supporting circuitry are in normal operation, SIE is clocked at the configured rate</li> </ul> |

| bit 0 | Unimplemented: Read as '0'                                                                                                                                                                                                    |

- Note 1: Make sure the USB clock source is correctly configured before setting this bit.

- 2: There should be at least four cycles of delay between the setting and PPBRST.

| XORWF                        | Exclusive OR W with f                                                                                                                                                                                                                                                                |                                 |           |                       |  |  |  |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-----------|-----------------------|--|--|--|

| Syntax:                      | XORWF                                                                                                                                                                                                                                                                                | f {,d {,a}}                     |           |                       |  |  |  |

| Operands:                    | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                                                  |                                 |           |                       |  |  |  |

| Operation:                   | (W) .XOR.                                                                                                                                                                                                                                                                            | (f) $\rightarrow$ dest          |           |                       |  |  |  |

| Status Affected:             | N, Z                                                                                                                                                                                                                                                                                 |                                 |           |                       |  |  |  |