and the second sec

What is "<u>Embedded - Microcontrollers</u>"? "<u>Embedded - Microcontrollers</u>" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics,

Welcome to E-XFL.COM

range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

providing the intelligence and control needed for a wide

#### Details

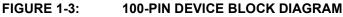

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                        |

| Peripherals                | Brown-out Detect/Reset, HLVD, LCD, POR, PWM, WDT                            |

| Number of I/O              | 86                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 4K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                   |

| Data Converters            | A/D 24x12b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 100-TQFP                                                                    |

| Supplier Device Package    | 100-TQFP (14x14)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f96j94t-i-pf |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.2.4.1 Retention Sleep Mode

Retention Sleep mode allows for additional power savings over Sleep mode by maintaining key systems from the lower power retention regulator. When the retention regulator is used, the normal on-chip voltage regulator (operating at 1.8V nominal) is turned off and will enable a low-power (1.2V typical) regulator. By using a lower voltage, a lower total power consumption is achieved.

Retention Sleep also offers the advantage of maintaining the contents of the data RAM. As a trade-off, the wake-up time is longer than that for Sleep mode.

Retention Sleep mode is controlled by the SRETEN bit (RCON4<4>) and the RETEN Configuration bit, as described in Section 4.2.2, Retention Regulator.

### 4.3 Clock Source Considerations

When the device wakes up from either of the Sleep modes, it will restart the same clock source that was active when Sleep mode was entered. Wake-up delays for the different oscillator modes are shown in Table 4-3 and Table 4-4, respectively.

If the system clock source is derived from a crystal oscillator and/or the PLL, the Oscillator Start-up Timer (OST) and/or PLL lock times must be applied before the system clock source is made available to the device. As an exception to this rule, no oscillator delays are necessary if the system clock source is the Secondary Oscillator and it was running while in Sleep mode.

#### 4.3.1 SLOW OSCILLATOR START-UP

The OST and PLL lock times may not have expired when the power-up delays have expired.

To avoid this condition, one can enable Two-Speed Start-up by the device that will run on FRC until the clock source is stable. Once the clock source is stable, the device will switch to the selected clock source.

#### 4.3.2 WAKE-UP FROM SLEEP ON INTERRUPT

Any source of interrupt that is individually enabled, using its corresponding control bit in the PIEx registers, can wake-up the processor from Sleep mode. When the device wakes from Sleep mode, one of two following actions may occur:

- If the GIE bit is set, the processor will wake and the Program Counter will begin execution at the interrupt vector.

- If the GIE bit is not set, the processor will wake and the Program Counter will continue execution following the SLEEP instruction that initiated Sleep mode.

#### 4.3.3 WAKE-UP FROM SLEEP ON RESET

All sources of device Reset will wake-up the processor from Sleep mode.

#### 4.3.4 WAKE-UP FROM SLEEP ON WATCHDOG TIME-OUT

If the Watchdog Timer (WDT) is enabled and expires while the device is in Sleep mode, the processor will wake-up. The SWDTEN Status bit (RCON2<5>) is set to indicate that the device resumed operation due to the WDT expiration. Note that this event does not reset the device. Operation continues from the instruction following the SLEEP instruction that initiated Sleep mode.

## 4.3.5 CONTROL BIT SUMMARY FOR SLEEP MODES

Table 4-2 shows the settings for the bits relevant to Sleep modes.

| TABLE 4-2: | BIT SETTINGS FOR ALL |

|------------|----------------------|

|            | SLEEP MODES          |

|                    | DSEN      | Retention Regulator  |                    |          |  |  |

|--------------------|-----------|----------------------|--------------------|----------|--|--|

| Mode               | DSCONH<7> | RETEN<br>CONFIG7L<0> | SRETEN<br>RCON4<4> | State    |  |  |

| Sleep              | x         | 1                    | x                  | Disabled |  |  |

|                    | x         | 0                    | 0                  | Disabled |  |  |

| Retention<br>Sleep | x         | 0                    | 1                  | Enabled  |  |  |

#### 4.3.6 WAKE-UP DELAYS

The restart delay, associated with waking up from Sleep and Retention Sleep modes, parallel each other in terms of clock start-up times. They differ in the time it takes to switch over from their respective regulators. The delays for the different oscillator modes are shown in Table 4-3 and Table 4-4, respectively.

| U-0        | U-0                                     | U-0                           | U-0          | R/C-0                 | R/C-0                   | R/C-0                  | R/W-0 |

|------------|-----------------------------------------|-------------------------------|--------------|-----------------------|-------------------------|------------------------|-------|

| —          | —                                       | —                             | _            | VDDBOR <sup>(1)</sup> | VDDPOR <sup>(1,2)</sup> | VBPOR <sup>(1,3)</sup> | VBAT  |

| bit 7      | -                                       |                               |              |                       |                         |                        | bit 0 |

|            |                                         |                               |              |                       |                         |                        |       |

| Legend:    |                                         | C = Clearable                 | bit          |                       |                         |                        |       |

| R = Reada  | able bit                                | W = Writable b                | oit          | U = Unimpler          | mented bit, read        | as '0'                 |       |

| -n = Value | at POR                                  | '1' = Bit is set              |              | '0' = Bit is cle      | ared                    | x = Bit is unkn        | own   |

|            |                                         |                               |              |                       |                         |                        |       |

| bit 7-4    | Unimpleme                               | nted: Read as '0              | )'           |                       |                         |                        |       |

| bit 3      | VDDBOR: \                               | DD Brown-out R                | eset Flag bi | (1)                   |                         |                        |       |

|            |                                         | Brown-out Reset               |              | -                     |                         |                        |       |

|            |                                         | Brown-out Reset               |              |                       |                         |                        |       |

| bit 2      |                                         | DD Power-On Re                | •            |                       |                         |                        |       |

|            |                                         | Power-up Reset I              |              |                       |                         |                        |       |

|            |                                         | Power-up Reset I              |              | urred                 |                         |                        |       |

| bit 1      |                                         | POR Flag bit <sup>(1,3)</sup> |              |                       |                         |                        |       |

|            |                                         | POR has occurre               |              |                       |                         |                        |       |

|            | • • • • • • • • • • • • • • • • • • • • | POR has not occ               | curred       |                       |                         |                        |       |

| bit 0      | <b>VBAT</b> : VBAT                      | 0                             |              |                       |                         |                        |       |

|            |                                         | exit has occurred             | •            | • •                   | o VBAT pin              |                        |       |

|            | • /:: <b>•</b> ::                       | exit from VBAT ha             |              |                       |                         |                        |       |

| Note 1:    | This bit is set in h                    | -                             |              |                       |                         | _                      |       |

| 2:         | Indicates a VDD F                       | POR. Setting the              | POR bit (R   | CON<0>) indica        | tes a VCORE PO          | R.                     |       |

#### REGISTER 5-3: RCON3: RESET CONTROL REGISTER 3

- 2: Indicates a VDD POR. Setting the POR bit (RCON<0>) indicates a VCORE POR.

- 3: This bit is set when the device is originally powered up, even if power is present on VBAT.

| TABLE 5-3: |        |                    |         | Power-on Reset, | MCLR Resets,                                     |                                 |  |

|------------|--------|--------------------|---------|-----------------|--------------------------------------------------|---------------------------------|--|

| Register   | Арр    | Applicable Devices |         |                 | WDT Reset,<br>RESET Instruction,<br>Stack Resets | Wake-up via<br>WDT or Interrupt |  |

| TOSU       | 64-pin | 80-pin             | 100-pin | 0 0000          | 0 0000                                           | 0 uuuu <b>(1)</b>               |  |

| TOSH       | 64-pin | 80-pin             | 100-pin | 0000 0000       | 0000 0000                                        | uuuu uuuu <b>(1)</b>            |  |

| TOSL       | 64-pin | 80-pin             | 100-pin | 0000 0000       | 0000 0000                                        | uuuu uuuu <sup>(1)</sup>        |  |

| STKPTR     | 64-pin | 80-pin             | 100-pin | 00-0 0000       | uu-0 0000                                        | uu-u uuuu <b>(1)</b>            |  |

| PCLATU     | 64-pin | 80-pin             | 100-pin | 0 0000          | 0 0000                                           | u uuuu                          |  |

| PCLATH     | 64-pin | 80-pin             | 100-pin | 0000 0000       | 0000 0000                                        | սսսս սսսս                       |  |

| PCL        | 64-pin | 80-pin             | 100-pin | 0000 0000       | 0000 0000                                        | PC + 2 <sup>(2)</sup>           |  |

| TBLPTRU    | 64-pin | 80-pin             | 100-pin | 00 0000         | 00 0000                                          | uu uuuu                         |  |

| TBLPTRH    | 64-pin | 80-pin             | 100-pin | 0000 0000       | 0000 0000                                        | uuuu uuuu                       |  |

| TBLPTRL    | 64-pin | 80-pin             | 100-pin | 0000 0000       | 0000 0000                                        | uuuu uuuu                       |  |

| TABLAT     | 64-pin | 80-pin             | 100-pin | 0000 0000       | 0000 0000                                        | uuuu uuuu                       |  |

| PRODH      | 64-pin | 80-pin             | 100-pin | xxxx xxxx       | uuuu uuuu                                        | uuuu uuuu                       |  |

| PRODL      | 64-pin | 80-pin             | 100-pin | xxxx xxxx       | uuuu uuuu                                        | uuuu uuuu                       |  |

| INTCON     | 64-pin | 80-pin             | 100-pin | 0000 000x       | 0000 000x                                        | uuuu uuuu <sup>(3)</sup>        |  |

| INTCON2    | 64-pin | 80-pin             | 100-pin | 1111 1111       | 1111 1111                                        | uuuu uuuu <sup>(3)</sup>        |  |

| INTCON3    | 64-pin | 80-pin             | 100-pin | 1100 0000       | 1100 0000                                        | uuuu uuuu <sup>(3)</sup>        |  |

| INDF0      | 64-pin | 80-pin             | 100-pin | N/A             | N/A                                              | N/A                             |  |

| POSTINC0   | 64-pin | 80-pin             | 100-pin | N/A             | N/A                                              | N/A                             |  |

| POSTDEC0   | 64-pin | 80-pin             | 100-pin | N/A             | N/A                                              | N/A                             |  |

| PREINC0    | 64-pin | 80-pin             | 100-pin | N/A             | N/A                                              | N/A                             |  |

| PLUSW0     | 64-pin | 80-pin             | 100-pin | N/A             | N/A                                              | N/A                             |  |

| FSR0H      | 64-pin | 80-pin             | 100-pin | xxxx            | uuuu                                             | uuuu                            |  |

| FSR0L      | 64-pin | 80-pin             | 100-pin | xxxx xxxx       | uuuu uuuu                                        | uuuu uuuu                       |  |

| WREG       | 64-pin | 80-pin             | 100-pin | xxxx xxxx       | uuuu uuuu                                        | սսսս սսսս                       |  |

| INDF1      | 64-pin | 80-pin             | 100-pin | N/A             | N/A                                              | N/A                             |  |

| POSTINC1   | 64-pin | 80-pin             | 100-pin | N/A             | N/A                                              | N/A                             |  |

| POSTDEC1   | 64-pin | 80-pin             | 100-pin | N/A             | N/A                                              | N/A                             |  |

| PREINC1    | 64-pin | 80-pin             | 100-pin | N/A             | N/A                                              | N/A                             |  |

| PLUSW1     | 64-pin | 80-pin             | 100-pin | N/A             | N/A                                              | N/A                             |  |

| FSR1H      | 64-pin | 80-pin             | 100-pin | xxxx            | uuuu                                             | uuuu                            |  |

| FSR1L      | 64-pin | 80-pin             | 100-pin | XXXX XXXX       | uuuu uuuu                                        | uuuu uuuu                       |  |

| BSR        | 64-pin | 80-pin             | 100-pin | 0000            | 0000                                             | uuuu                            |  |

| INDF2      | 64-pin | 80-pin             | 100-pin | N/A             | N/A                                              | N/A                             |  |

TABLE 5-3:

INITIALIZATION CONDITIONS FOR ALL REGISTERS

**Legend:** u = unchanged; x = unknown; - = unimplemented bit, read as '0'; q = value depends on condition. Shaded cells indicate that conditions do not apply for the designated device.

**Note 1:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

**2:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

3: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

4: See Table 5-2 for Reset value for specific condition.

- 5: Bits 7,6 are unimplemented on 64 and 80-pin devices.

- 6: If the VBAT is always powered, the DSGPx register values will remain unchanged after the first POR.

#### 6.1.3 **PROGRAM COUNTER**

The Program Counter (PC) specifies the address of the instruction to fetch for execution. The PC is 21 bits wide and contained in three separate 8-bit registers.

The low byte, known as the PCL register, is both readable and writable. The high byte, or PCH register, contains the PC<15:8> bits and is not directly readable or writable. Updates to the PCH register are performed through the PCLATH register. The upper byte is called PCU. This register contains the PC<20:16> bits; it is also not directly readable or writable. Updates to the PCU register are performed through the PCLATU register.

The contents of PCLATH and PCLATU are transferred to the Program Counter by any operation that writes PCL. Similarly, the upper two bytes of the Program Counter are transferred to PCLATH and PCLATU by an operation that reads PCL. This is useful for computed offsets to the PC (see Section 6.1.6.1 "Computed GOTO").

The PC addresses bytes in the program memory. To prevent the PC from becoming misaligned with word instructions, the Least Significant bit of PCL is fixed to a value of '0'. The PC increments by two to address sequential instructions in the program memory.

The CALL, RCALL, GOTO and program branch instructions write to the Program Counter directly. For these instructions, the contents of PCLATH and PCLATU are not transferred to the Program Counter.

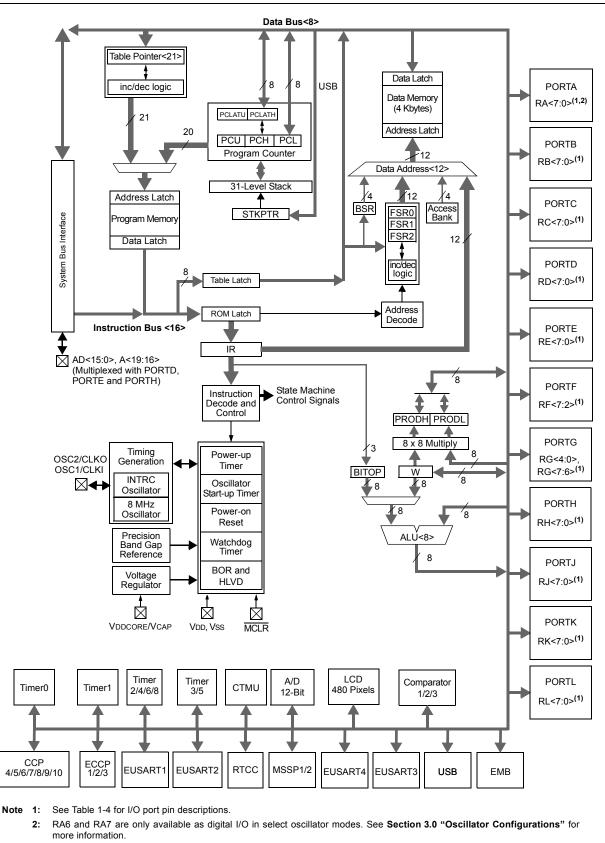

#### 6.1.4 RETURN ADDRESS STACK

The return address stack enables execution of any combination of up to 31 program calls and interrupts. The PC is pushed onto the stack when a CALL or RCALL instruction is executed or an interrupt is Acknowledged. The PC value is pulled off the stack on a RETURN, RETLW or a RETFIE instruction. The value also is pulled off the stack on ADDULNK and SUBULNK instructions, if the extended instruction set is enabled. PCLATU and PCLATH are not affected by any of the RETURN or CALL instructions.

The stack operates as a 31-word by 21-bit RAM and a 5-bit Stack Pointer, STKPTR. The stack space is not part of either program or data space. The Stack Pointer is readable and writable and the address on the top of the stack is readable and writable through the Top-of-Stack Special Function Registers. Data can also be pushed to, or popped from, the stack using these registers.

A CALL type instruction causes a push onto the stack. The Stack Pointer is first incremented and the location pointed to by the Stack Pointer is written with the contents of the PC (already pointing to the instruction following the CALL). A RETURN type instruction causes a pop from the stack. The contents of the location pointed to by the STKPTR are transferred to the PC and then the Stack Pointer is decremented.

The Stack Pointer is initialized to '00000' after all Resets. There is no RAM associated with the location corresponding to a Stack Pointer value of '00000'; this is only a Reset value. Status bits indicate if the stack is full, has overflowed or has underflowed.

#### 6.1.4.1 **Top-of-Stack Access**

Only the top of the return address stack (TOS) is readable and writable. A set of three registers, TOSU:TOSH:TOSL, holds the contents of the stack location pointed to by the STKPTR register (Figure 6-3). This allows users to implement a software stack, if necessary. After a CALL, RCALL or interrupt (or ADDULNK and SUBULNK instructions, if the extended instruction set is enabled), the software can read the pushed value by reading the TOSU:TOSH:TOSL registers. These values can be placed on a user-defined software stack. At return time, the software can return these values to TOSU:TOSH:TOSL and do a return.

While accessing the stack, users must disable the Global Interrupt Enable bits to prevent inadvertent stack corruption.

#### FIGURE 6-3:

#### 6.4 Data Addressing Modes

| Note: | The execution of some instructions in the  |

|-------|--------------------------------------------|

|       | core PIC18 instruction set are changed     |

|       | when the PIC18 extended instruction set is |

|       | enabled. For more information, see         |

|       | Section 6.6 "Data Memory and the           |

|       | Extended Instruction Set".                 |

While the program memory can be addressed in only one way, through the Program Counter, information in the data memory space can be addressed in several ways. For most instructions, the addressing mode is fixed. Other instructions may use up to three modes, depending on which operands are used and whether or not the extended instruction set is enabled.

The addressing modes are:

- Inherent

- Literal

- Direct

- Indirect

An additional addressing mode, Indexed Literal Offset, is available when the extended instruction set is enabled (XINST Configuration bit = 1). For details on this mode's operation, see **Section 6.6.1 "Indexed Addressing with Literal Offset**".

## 6.4.1 INHERENT AND LITERAL ADDRESSING

Many PIC18 control instructions do not need any argument at all. They either perform an operation that globally affects the device or they operate implicitly on one register. This addressing mode is known as Inherent Addressing. Examples of this mode include SLEEP, RESET and DAW.

Other instructions work in a similar way, but require an additional explicit argument in the opcode. This method is known as the Literal Addressing mode because the instructions require some literal value as an argument. Examples of this include ADDLW and MOVLW which, respectively, add or move a literal value to the W register. Other examples include CALL and GOTO, which include a 20-bit program memory address.

#### 6.4.2 DIRECT ADDRESSING

Direct Addressing specifies all or part of the source and/or destination address of the operation within the opcode itself. The options are specified by the arguments accompanying the instruction.

In the core PIC18 instruction set, bit-oriented and byteoriented instructions use some version of Direct Addressing by default. All of these instructions include some 8-bit literal address as their Least Significant Byte. This address specifies the instruction's data source as either a register address in one of the banks of data RAM (see Section 6.3.3 "General Purpose Register File") or a location in the Access Bank (see Section 6.3.2 "Access Bank").

The Access RAM bit, 'a', determines how the address is interpreted. When 'a' is '1', the contents of the BSR (Section 6.3.1 "Bank Select Register") are used with the address to determine the complete 12-bit address of the register. When 'a' is '0', the address is interpreted as being a register in the Access Bank. Addressing that uses the Access RAM is sometimes also known as Direct Forced Addressing mode.

A few instructions, such as MOVFF, include the entire 12-bit address (either source or destination) in their opcodes. In these cases, the BSR is ignored entirely.

The destination of the operation's results is determined by the destination bit, 'd'. When 'd' is '1', the results are stored back in the source register, overwriting its original contents. When 'd' is '0', the results are stored in the W register. Instructions without the 'd' argument have a destination that is implicit in the instruction, either the target register being operated on or the W register.

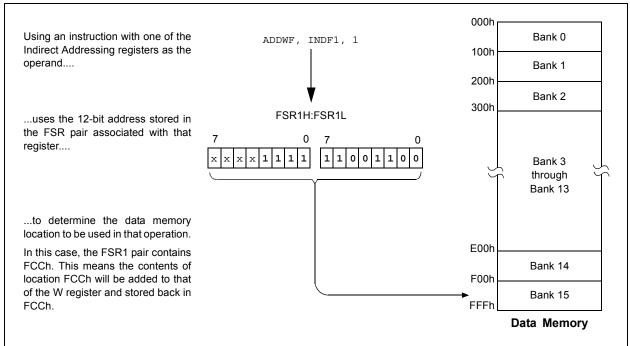

#### 6.4.3 INDIRECT ADDRESSING

Indirect Addressing allows the user to access a location in data memory without giving a fixed address in the instruction. This is done by using File Select Registers (FSRs) as pointers to the locations to be read or written to. Since the FSRs are themselves located in RAM as Special Function Registers, they can also be directly manipulated under program control. This makes FSRs very useful in implementing data structures such as tables and arrays in data memory.

The registers for Indirect Addressing are also implemented with Indirect File Operands (INDFs) that permit automatic manipulation of the pointer value with auto-incrementing, auto-decrementing or offsetting with another value. This allows for efficient code using loops, such as the example of clearing an entire RAM bank in Example 6-5. It also enables users to perform Indexed Addressing and other Stack Pointer operations for program memory in data memory.

#### EXAMPLE 6-5: HOW TO CLEAR RAM (BANK 1) USING INDIRECT ADDRESSING

|         | LFSR  | FSR0, 100h | ; |                |

|---------|-------|------------|---|----------------|

| NEXT    | CLRF  | POSTINC0   | ; | Clear INDF     |

|         |       |            | ; | register then  |

|         |       |            | ; | inc pointer    |

|         | BTFSS | FSROH, 1   | ; | All done with  |

|         |       |            | ; | Bank1?         |

|         | BRA   | NEXT       | ; | NO, clear next |

| CONTINU | JE    |            | ; | YES, continue  |

|         |       |            |   |                |

## 6.4.3.1 FSR Registers and the INDF Operand

At the core of Indirect Addressing are three sets of registers: FSR0, FSR1 and FSR2. Each represents a pair of 8-bit registers: FSRnH and FSRnL. The four upper bits of the FSRnH register are not used, so each FSR pair holds a 12-bit value. This represents a value that can address the entire range of the data memory in a linear fashion. The FSR register pairs, then, serve as pointers to data memory locations.

Indirect Addressing is accomplished with a set of Indirect File Operands, INDF0 through INDF2. These can be thought of as "virtual" registers. The operands are

#### mapped in the SFR space, but are not physically implemented. Reading or writing to a particular INDF register actually accesses its corresponding FSR register pair. A read from INDF1, for example, reads the data at the address indicated by FSR1H:FSR1L.

Instructions that use the INDF registers as operands actually use the contents of their corresponding FSR as a pointer to the instruction's target. The INDF operand is just a convenient way of using the pointer.

Because Indirect Addressing uses a full 12-bit address, data RAM banking is not necessary. Thus, the current contents of the BSR and the Access RAM bit have no effect on determining the target address.

#### FIGURE 6-8: INDIRECT ADDRESSING

#### TABLE 11-13: RPIN REGISTERS AND AVAILABLE FUNCTIONS

| PPS-Lite Input Peripheral Group 4n |                                     |  |  |  |

|------------------------------------|-------------------------------------|--|--|--|

| (1) To Map this signal             | (4) to the Associated RPIN Register |  |  |  |

| SDI1                               | RPINR8_9<7:4>                       |  |  |  |

| FLT0                               | RPINR14_15<3:0>                     |  |  |  |

| IOC0                               | RPINR18_19<3:0>                     |  |  |  |

| IOC4                               | RPINR22_23<3:0>                     |  |  |  |

| MDCIN1                             | RPINR30_31<3:0>                     |  |  |  |

| TOCKI                              | RPINR38_39<7:4>                     |  |  |  |

| T5G                                | RPINR44_45<3:0>                     |  |  |  |

| U3RX                               | RPINR4_5<3:0>                       |  |  |  |

| U4RX                               | RPINR6_7<3:0>                       |  |  |  |

| CCP5                               | RPINR32_33<7:4>                     |  |  |  |

| CCP8                               | RPINR36_37<3:0>                     |  |  |  |

| RVP0                               | RPINR46_47<3:0>                     |  |  |  |

| RVP4                               | RPINR50_51<3:0>                     |  |  |  |

| (2) with this RPn Pin              | (3) Write this Corresponding Value  |  |  |  |

| RP0                                | h'0                                 |  |  |  |

| RP4                                | h'1                                 |  |  |  |

| RP8                                | h'2                                 |  |  |  |

| RP12                               | h'3                                 |  |  |  |

| RP16                               | h'4                                 |  |  |  |

| RP20                               | h'5                                 |  |  |  |

| RP24                               | h'6                                 |  |  |  |

| RP28                               | h'7                                 |  |  |  |

|                                    |                                     |  |  |  |

h'8

h'9

h'A

h'B h'C

h'D

h'E h'F

| PPS-Lite Inp           | PPS-Lite Input Peripheral Group 4n + 1 |  |  |  |  |

|------------------------|----------------------------------------|--|--|--|--|

| (1) To Map this Signal | (4) to the Associated RPIN Register    |  |  |  |  |

| SDI2                   | RPINR12_13<3:0>                        |  |  |  |  |

| INT1                   | RPINR26_27<3:0>                        |  |  |  |  |

| IOC1                   | RPINR18_19<7:4>                        |  |  |  |  |

| IOC5                   | RPINR22_23<7:4>                        |  |  |  |  |

| MDCIN2                 | RPINR30_31<7:4>                        |  |  |  |  |

| T1CKI                  | RPINR40_41<7:4>                        |  |  |  |  |

| T1G                    | RPINR40_41<3:0>                        |  |  |  |  |

| T3CKI                  | RPINR42_43<7:4>                        |  |  |  |  |

| T3G                    | RPINR42_43<3:0>                        |  |  |  |  |

| T5CKI                  | RPINR44_45<7:4>                        |  |  |  |  |

| U3TX                   | RPINR4_5<7:4>                          |  |  |  |  |

| U4TX                   | RPINR6_7<7:4>                          |  |  |  |  |

| CCP7                   | RPINR34_35<7:4>                        |  |  |  |  |

| CCP9                   | RPINR36_37<7:4>                        |  |  |  |  |

| RVP1                   | RPINR46_47<7:4>                        |  |  |  |  |

| RVP5                   | RPINR50_51<7:4>                        |  |  |  |  |

|                        |                                        |  |  |  |  |

| (2) with this RPn Pin  | (3) Write this Corresponding Value     |  |  |  |  |

| RP1                    | h'0                                    |  |  |  |  |

| RP5                    | h'1                                    |  |  |  |  |

| RP9                    | h'2                                    |  |  |  |  |

| RP13                   | h'3                                    |  |  |  |  |

| RP17                   | h'4                                    |  |  |  |  |

| RP21                   | h'5                                    |  |  |  |  |

| RP25                   | h'6                                    |  |  |  |  |

| RP29                   | h'7                                    |  |  |  |  |

| RP33                   | h'8                                    |  |  |  |  |

| RP37                   | h'9                                    |  |  |  |  |

| RP41                   | h'A                                    |  |  |  |  |

| RP45                   | h'B                                    |  |  |  |  |

| —                      | h'C                                    |  |  |  |  |

| _                      | h'D                                    |  |  |  |  |

| _                      | h'E                                    |  |  |  |  |

| Vss                    | h'F                                    |  |  |  |  |

RP32

RP36

RP40

RP44

\_

\_

Vss

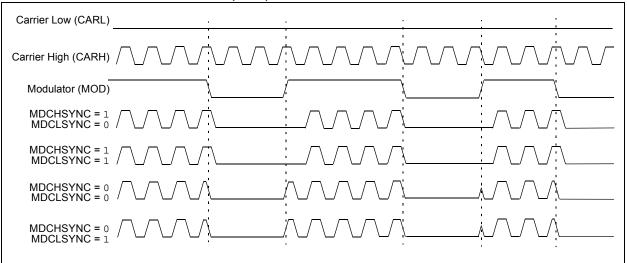

#### FIGURE 12-2: ON-OFF KEYING (OOK) SYNCHRONIZATION

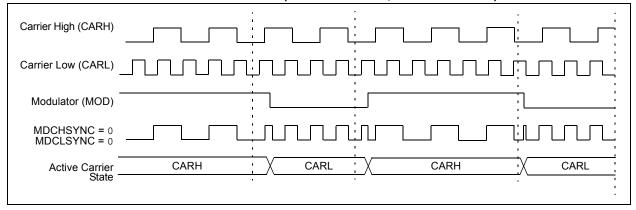

#### FIGURE 12-3: NO SYNCHRONIZATION (MDCHSYNC = 0, MDCLSYNC = 0)

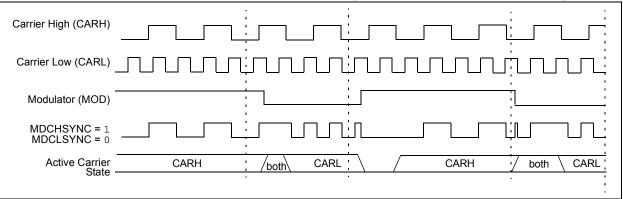

#### FIGURE 12-4: CARRIER HIGH SYNCHRONIZATION (MDCHSYNC = 1, MDCLSYNC = 0)

| R/W-0      | R/W-0                            | R/W-0                                              | R/W-0                | R/W-0                       | R/W-0              | R/W-0               | R/W-0              |

|------------|----------------------------------|----------------------------------------------------|----------------------|-----------------------------|--------------------|---------------------|--------------------|

| GCEN       | ACKSTAT                          | ACKDT <sup>(1)</sup>                               | ACKEN <sup>(2)</sup> | RCEN <sup>(2)</sup>         | PEN <sup>(2)</sup> | RSEN <sup>(2)</sup> | SEN <sup>(2)</sup> |

| bit 7      |                                  |                                                    |                      |                             |                    |                     | bit (              |

|            |                                  |                                                    |                      |                             |                    |                     |                    |

| Legend:    |                                  |                                                    |                      |                             |                    |                     |                    |

| R = Reada  |                                  | W = Writable                                       |                      | •                           | nented bit, rea    | d as '0'            |                    |

| -n = Value | e at POR                         | '1' = Bit is set                                   |                      | '0' = Bit is cle            | ared               | x = Bit is unkn     | own                |

| bit 7      | GCEN: Gene                       | eral Call Enable                                   | bit                  |                             |                    |                     |                    |

|            | Unused in Ma                     | aster mode.                                        |                      |                             |                    |                     |                    |

| bit 6      | ACKSTAT: A                       | cknowledge Sta                                     | atus bit (Maste      | r Transmit mod              | e only)            |                     |                    |

|            |                                  | edge was not re<br>edge was receiv                 |                      | ave                         |                    |                     |                    |

| bit 5      | ACKDT: Ack                       | nowledge Data                                      | bit (Master Re       | ceive mode on               | ly) <sup>(1)</sup> |                     |                    |

|            | 1 = Not Ackn<br>0 = Acknowle     | •                                                  |                      |                             |                    |                     |                    |

| bit 4      | ACKEN: Ack                       | nowledge Sequ                                      | ience Enable b       | oit <sup>(2)</sup>          |                    |                     |                    |

|            | automati                         | Acknowledge s<br>cally cleared by<br>edge sequence | / hardware           | DAx and SCLx                | pins and trans     | mits ACKDT dat      | ta bit;            |

| bit 3      |                                  | ive Enable bit (                                   |                      | e mode only) <sup>(2)</sup> | )                  |                     |                    |

|            |                                  | Receive mode f                                     |                      | <b>,</b> ,                  |                    |                     |                    |

| bit 2      | PEN: Stop C                      | ondition Enable                                    | bit <sup>(2)</sup>   |                             |                    |                     |                    |

|            | 1 = Initiates S<br>0 = Stop cond |                                                    | n SDAx and S         | CLx pins; auto              | matically cleare   | ed by hardware      |                    |

| bit 1      |                                  | ated Start Cond                                    | lition Enable b      | it <sup>(2)</sup>           |                    |                     |                    |

|            | 1 = Initiates                    |                                                    | condition on S       |                             | c pins; automat    | tically cleared by  | / hardware         |

| bit 0      |                                  | ondition Enable                                    |                      |                             |                    |                     |                    |

|            |                                  | Start condition c                                  |                      | CLx pins; auto              | matically clear    | ed by hardware      |                    |

| Note 1:    | The value that wi receive.       | II be transmitte                                   | d when the use       | er initiates an A           | cknowledge se      | equence at the e    | end of a           |

| 2:         | If the I <sup>2</sup> C module   | is active these                                    | hits may not l       | ne set (no spor             | ling) and the S    | SPyBLIE may n       | ot he written      |

### 2: If the I<sup>2</sup>C module is active, these bits may not be set (no spooling) and the SSPxBUF may not be written (or writes to the SSPxBUF are disabled).

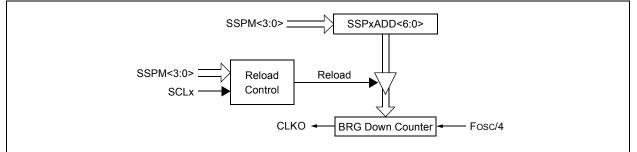

#### 20.5.10 BAUD RATE

In I<sup>2</sup>C Master mode, the Baud Rate Generator (BRG) reload value is placed in the lower 7 bits of the SSPxADD register (Figure 20-19). When a write occurs to SSPxBUF, the Baud Rate Generator will automatically begin counting. The BRG counts down to 0 and stops until another reload has taken place. The BRG count is decremented, twice per instruction cycle (TcY), on the Q2 and Q4 clocks. In I<sup>2</sup>C Master mode, the BRG is reloaded automatically.

Once the given operation is complete (i.e., transmission of the last data bit is followed by ACK), the internal clock will automatically stop counting and the SCLx pin will remain in its last state.

Table 20-2 demonstrates clock rates based on instruction cycles and the BRG value loaded into SSPxADD. The SSPxADD BRG value of  $(0 \times 0.0)$  is not supported.

#### 20.5.10.1 Baud Rate and Module Interdependence

Because MSSP1 and MSSP2 are independent, they can operate simultaneously in I<sup>2</sup>C Master mode at different baud rates. This is done by using different BRG reload values for each module.

Because this mode derives its basic clock source from the system clock, any changes to the clock will affect both modules in the same proportion. It may be possible to change one or both baud rates back to a previous value by changing the BRG reload value.

#### FIGURE 20-19: BAUD RATE GENERATOR BLOCK DIAGRAM

#### TABLE 20-2: I<sup>2</sup>C CLOCK RATE w/BRG

| Fosc   | Fcy    | Fcy * 2 | BRG Value | FscL<br>(2 Rollovers of BRG) |

|--------|--------|---------|-----------|------------------------------|

| 64 MHz | 16 MHz | 32 MHz  | 27h       | 400 kHz <sup>(1)</sup>       |

| 64 MHz | 16 MHz | 32 MHz  | 32h       | 313.72 kHz                   |

| 64 MHz | 16 MHz | 32 MHz  | 9Fh       | 100 kHz                      |

| 16 MHz | 4 MHz  | 8 MHz   | 09h       | 400 kHz <sup>(1)</sup>       |

| 16 MHz | 4 MHz  | 8 MHz   | 0Ch       | 308 kHz                      |

| 16 MHz | 4 MHz  | 8 MHz   | 27h       | 100 kHz                      |

| 4 MHz  | 1 MHz  | 2 MHz   | 02h       | 333 kHz <sup>(1)</sup>       |

| 4 MHz  | 1 MHz  | 2 MHz   | 09h       | 100 kHz                      |

| 16 MHz | 4 MHz  | 8 MHz   | 03h       | 1 MHz <sup>(1,1)</sup>       |

**Note 1:** A minimum of 16 MHz FOSC is required to get 1 MHz  $I^2C$ .

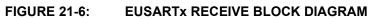

#### 21.2.2 EUSARTx ASYNCHRONOUS RECEIVER

The receiver block diagram is shown in Figure 21-6. The data is received on the RXx pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at x16 times the baud rate, whereas the main receive serial shifter operates at the bit rate or at Fosc. This mode would typically be used in RS-232 systems.

To set up an Asynchronous Reception:

- 1. Initialize the SPBRGHx:SPBRGx registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the asynchronous serial port by clearing bit, SYNC, and setting bit, SPEN.

- 3. If interrupts are desired, set enable bit, RCxIE.

- 4. If 9-bit reception is desired, set bit, RX9.

- 5. Enable the reception by setting bit, CREN.

- Flag bit, RCxIF, will be set when reception is complete and an interrupt will be generated if enable bit, RCxIE, was set.

- 7. Read the RCSTAx register to get the 9th bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREGx register.

- 9. If any error occurred, clear the error by clearing enable bit, CREN.

- 10. If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

#### 21.2.3 SETTING UP 9-BIT MODE WITH ADDRESS DETECT

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- 1. Initialize the SPBRGHx:SPBRGx registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If interrupts are required, set the RCEN bit and select the desired priority level with the RCxIP bit.

- 4. Set the RX9 bit to enable 9-bit reception.

- 5. Set the ADDEN bit to enable address detect.

- 6. Enable reception by setting the CREN bit.

- 7. The RCxIF bit will be set when reception is complete. The interrupt will be Acknowledged if the RCxIE and GIE bits are set.

- 8. Read the RCSTAx register to determine if any error occurred during reception, as well as read bit 9 of data (if applicable).

- 9. Read RCREGx to determine if the device is being addressed.

- 10. If any error occurred, clear the CREN bit.

- 11. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and interrupt the CPU.

### REGISTER 22-6: ADCON2H: A/D CONTROL REGISTER 2 HIGH

| R/W-0        | R/W-0                                            | R/W-0                                                         | R/W-0           | R/W-0                                     | R/W-0           | U-0             | U-0   |

|--------------|--------------------------------------------------|---------------------------------------------------------------|-----------------|-------------------------------------------|-----------------|-----------------|-------|

| PVCFG1       | PVCFG0                                           | NVCFG0                                                        | OFFCAL          | BUFREGEN                                  | CSCNA           |                 | —     |

| bit 7        | •                                                | •                                                             |                 |                                           |                 | •               | bit 0 |

| Legend:      |                                                  |                                                               |                 |                                           |                 |                 |       |

| R = Readab   | ole bit                                          | W = Writable I                                                | oit             | U = Unimplem                              | ented bit, read | l as '0'        |       |

| -n = Value a | at POR                                           | '1' = Bit is set                                              |                 | '0' = Bit is clea                         | ired            | x = Bit is unkn | iown  |

|              |                                                  | mented, do not                                                | 0               | Reference Confi                           | <u>.</u>        |                 |       |

| bit 5        | <b>NVCFG0:</b> Co<br>1 = External<br>0 = AVss    | 0                                                             | e Voltage Ref   | erence Configur                           | ation bit       |                 |       |

| bit 4        | 1 = Inverting                                    |                                                               | ng inputs of cl | bit<br>hannel Sample-a<br>hannel Sample-a |                 |                 |       |

| bit 3        | 1 = Convers                                      | : A/D Buffer Reg<br>ion result is load<br>It buffer is treate | led into the bu | bit<br>Iffer location det                 | ermined by the  | e converted cha | annel |

| bit 2        | <b>CSCNA:</b> Sca<br>1 = Scans in<br>0 = Does no | puts                                                          | ns for CH0+ [   | During Sample A                           | s bit           |                 |       |

| bit 1-0      | Unimplemer                                       | •                                                             |                 |                                           |                 |                 |       |

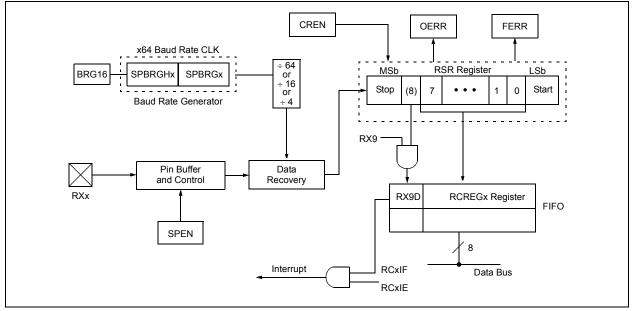

The module is enabled by setting the HLVDEN bit (HLVDCON<4>). Each time the HLVD module is enabled, the circuitry requires some time to stabilize. The IRVST bit (HLVDCON<5>) is a read-only bit used to indicate when the circuit is stable. The module can only generate an interrupt after the circuit is stable and IRVST is set.

The VDIRMAG bit (HLVDCON<7>) determines the overall operation of the module. When VDIRMAG is cleared, the module monitors for drops in VDD below a predetermined set point. When the bit is set, the module monitors for rises in VDD above the set point.

### 25.1 Operation

When the HLVD module is enabled, a comparator uses an internally generated reference voltage as the set point. The set point is compared with the trip point, where each node in the resistor divider represents a trip point voltage. The "trip point" voltage is the voltage level at which the device detects a high or low-voltage event, depending on the configuration of the module.

When the supply voltage is equal to the trip point, the voltage tapped off of the resistor array is equal to the internal reference voltage generated by the voltage reference module. The comparator then generates an interrupt signal by setting the HLVDIF bit.

The trip point voltage is software programmable to any of 16 values. The trip point is selected by programming the HLVDL<3:0> bits (HLVDCON<3:0>).

The HLVD module has an additional feature that allows the user to supply the trip voltage to the module from an external source. This mode is enabled when bits, HLVDL<3:0>, are set to '1111'. In this state, the comparator input is multiplexed from the external input pin, HLVDIN. This gives users the flexibility of configuring the High/Low-Voltage Detect interrupt to occur at any voltage in the valid operating range.

FIGURE 25-1: HLVD MODULE BLOCK DIAGRAM (WITH EXTERNAL INPUT)

### REGISTER 27-2: UCFG: USB CONFIGURATION REGISTER

| R/W-0       | R/W-0                                        | U-0                                                                                                                                                                    | R/W-0                              | R/W-0                                                 | R/W-0               | R/W-0             | R/W-0        |  |  |  |

|-------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-------------------------------------------------------|---------------------|-------------------|--------------|--|--|--|

| UTEYE       | UOEMON                                       | _                                                                                                                                                                      | UPUEN <sup>(1,2)</sup>             | UTRDIS <sup>(1,3)</sup>                               | FSEN <sup>(1)</sup> | PPB1              | PPB0         |  |  |  |

| pit 7       |                                              |                                                                                                                                                                        |                                    |                                                       |                     |                   | bit (        |  |  |  |

|             |                                              |                                                                                                                                                                        |                                    |                                                       |                     |                   |              |  |  |  |

| Legend:     |                                              |                                                                                                                                                                        |                                    |                                                       |                     |                   |              |  |  |  |

| R = Readab  | le bit                                       | W = Writable                                                                                                                                                           | e bit                              | U = Unimplem                                          | nented bit, read    | as '0'            |              |  |  |  |

| n = Value a | t POR                                        | '1' = Bit is se                                                                                                                                                        | et                                 | '0' = Bit is clea                                     | ared                | x = Bit is unkr   | nown         |  |  |  |

|             |                                              |                                                                                                                                                                        |                                    |                                                       |                     |                   |              |  |  |  |

| bit 7       | UTEYE: USB                                   | Eye Pattern                                                                                                                                                            | Test Enable bit                    |                                                       |                     |                   |              |  |  |  |

|             | <b>7</b> 1                                   | 1 = Eye pattern test is enabled                                                                                                                                        |                                    |                                                       |                     |                   |              |  |  |  |

|             | 0 = Eye patte                                |                                                                                                                                                                        |                                    |                                                       |                     |                   |              |  |  |  |

| oit 6       |                                              | <b>UOEMON:</b> USB OE Monitor Enable bit<br>1 = UOE signal is active, indicating intervals during which the D+/D- lines are driving                                    |                                    |                                                       |                     |                   |              |  |  |  |

|             | 1 = <u>UOE</u> sigr<br>0 = UOE sigr          |                                                                                                                                                                        |                                    | als during whic                                       | h the D+/D- line    | es are driving    |              |  |  |  |

| oit 5       | Unimplemen                                   |                                                                                                                                                                        |                                    |                                                       |                     |                   |              |  |  |  |

| oit 4       | UPUEN: USE                                   | On-Chip Pu                                                                                                                                                             | I-up Enable bit                    | 1,2)                                                  |                     |                   |              |  |  |  |

|             | 1 = On-chip p<br>0 = On-chip p               |                                                                                                                                                                        |                                    | D+ with FSEN                                          | = 1 or D- with F    | <b>SEN =</b> 0)   |              |  |  |  |

| oit 3       | UTRDIS: On-                                  | Chip Transce                                                                                                                                                           | iver Disable bit                   | (1,3)                                                 |                     |                   |              |  |  |  |

|             | 1 = On-chip tr<br>0 = On-chip tr             |                                                                                                                                                                        |                                    |                                                       |                     |                   |              |  |  |  |

| oit 2       | FSEN: Full-S                                 | peed Enable                                                                                                                                                            | bit <sup>(1)</sup>                 |                                                       |                     |                   |              |  |  |  |

|             |                                              |                                                                                                                                                                        |                                    | er edge rates; re<br>er edge rates; r                 |                     |                   |              |  |  |  |

| oit 1-0     | <b>PPB&lt;1:0&gt;:</b> P                     | <ul> <li>0 = Low-speed device: Controls transceiver edge rates; requires input clock at 6 MHz</li> <li>PPB&lt;1:0&gt;: Ping-Pong Buffers Configuration bits</li> </ul> |                                    |                                                       |                     |                   |              |  |  |  |

|             | 11 = Even/Oc<br>10 = Even/Oc<br>01 = Even/Oc | ld ping-pong<br>ld ping-pong<br>ld ping-pong                                                                                                                           | buffers are ena<br>buffers are ena | bled for Endpoi<br>bled for all end<br>led for OUT En | points              |                   |              |  |  |  |

|             | he UPUEN, UTR<br>alues must be pre           |                                                                                                                                                                        |                                    |                                                       | d while the US      | B module is en    | abled. These |  |  |  |

|             | his bit is only valio                        |                                                                                                                                                                        | -                                  |                                                       | RDIS = 0); other    | wise, it is ignor | ed.          |  |  |  |

|             |                                              |                                                                                                                                                                        |                                    |                                                       |                     |                   |              |  |  |  |

**3:** If UTRDIS is set, the UOE signal will be active, independent of the UOEMON bit setting.

#### 27.2.4 USB ENDPOINT CONTROL

Each of the 16 possible bidirectional endpoints has its own independent control register, UEPn (where 'n' represents the endpoint number). Each register has an identical complement of control bits.

Register 27-4 provides the prototype.

The EPHSHK bit (UEPn<4>) controls handshaking for the endpoint; setting this bit enables USB handshaking. Typically, this bit is always set except when using isochronous endpoints.

The EPCONDIS bit (UEPn<3>) is used to enable or disable USB control operations (SETUP) through the endpoint. Clearing this bit enables SETUP transactions. Note that the corresponding EPINEN and EPOUTEN bits must be set to enable IN and OUT transactions. For Endpoint 0, this bit should always be cleared since the USB specifications identify Endpoint 0 as the default control endpoint.

The EPOUTEN bit (UEPn<2>) is used to enable or disable USB OUT transactions from the host. Setting this bit enables OUT transactions. Similarly, the EPINEN bit (UEPn<1>) enables or disables USB IN transactions from the host.

The EPSTALL bit (UEPn<0>) is used to indicate a STALL condition for the endpoint. If a STALL is issued on a particular endpoint, the EPSTALL bit for that endpoint pair will be set by the SIE. This bit remains set until it is cleared through firmware or until the SIE is reset.

#### REGISTER 27-4: UEPn: USB ENDPOINT n CONTROL REGISTER (UEP0 THROUGH UEP15)

| U-0   | U-0 | U-0 | R/W-0  | R/W-0    | R/W-0   | R/W-0  | R/W-0   |

|-------|-----|-----|--------|----------|---------|--------|---------|

| —     | —   | —   | EPHSHK | EPCONDIS | EPOUTEN | EPINEN | EPSTALL |

| bit 7 |     |     |        |          |         |        | bit 0   |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-5 | Unimplemented: Read as '0'                                                                  |

|---------|---------------------------------------------------------------------------------------------|

| bit 4   | EPHSHK: Endpoint Handshake Enable bit                                                       |

|         | 1 = Endpoint handshake is enabled                                                           |

|         | 0 = Endpoint handshake is disabled (typically used for isochronous endpoints)               |

| bit 3   | EPCONDIS: Bidirectional Endpoint Control bit                                                |

|         | If EPOUTEN = 1 and EPINEN = 1:                                                              |

|         | 1 = Disables Endpoint n from control transfers; only IN and OUT transfers are allowed       |

|         | 0 = Enables Endpoint n for control (SETUP) transfers; IN and OUT transfers are also allowed |

| bit 2   | EPOUTEN: Endpoint Output Enable bit                                                         |

|         | 1 = Endpoint n output is enabled                                                            |

|         | 0 = Endpoint n output is disabled                                                           |

| bit 1   | EPINEN: Endpoint Input Enable bit                                                           |

|         | 1 = Endpoint n input is enabled                                                             |

|         | 0 = Endpoint n input is disabled                                                            |

| bit 0   | EPSTALL: Endpoint Stall Indicator bit                                                       |

|         | 1 = Endpoint n has issued one or more STALL packets                                         |

|         | 0 = Endpoint n has not issued any STALL packets                                             |

|         |                                                                                             |

#### 27.4.1.3 BDnSTAT Register (SIE Mode)

When the BD and its buffer are owned by the SIE, most of the bits in BDnSTAT take on a different meaning. The configuration is shown in Register 27-6. Once UOWN is set, any data or control settings previously written there by the user will be overwritten with data from the SIE.

The BDnSTAT register is updated by the SIE with the token Packet Identifier (PID) which is stored in BDnSTAT<5:2>. The transfer count in the corresponding BDnCNT register is updated. Values that overflow the 8-bit register carry over to the two most significant digits of the count, stored in BDnSTAT<1:0>.

#### 27.4.2 BD BYTE COUNT

The byte count represents the total number of bytes that will be transmitted during an IN transfer. After an IN transfer, the SIE will return the number of bytes sent to the host.

For an OUT transfer, the byte count represents the maximum number of bytes that can be received and stored in USB RAM. After an OUT transfer, the SIE will return the actual number of bytes received. If the number of bytes received exceeds the corresponding byte count, the data packet will be rejected and a NAK handshake will be generated. When this happens, the byte count will not be updated.

The 10-bit byte count is distributed over two registers. The lower 8 bits of the count reside in the BDnCNT register; the upper two bits reside in BDnSTAT<1:0>. This represents a valid byte range of 0 to 1023.

#### 27.4.3 BD ADDRESS VALIDATION

The BD Address register pair contains the starting RAM address location for the corresponding endpoint buffer. No mechanism is available in hardware to validate the BD address.

If the value of the BD address does not point to an address in the USB RAM, or if it points to an address within another endpoint's buffer, data is likely to be lost or overwritten. Similarly, overlapping a receive buffer (OUT endpoint) with a BD location in use can yield unexpected results. When developing USB applications, the user may want to consider the inclusion of software-based address validation in their code.

## REGISTER 27-6: BDnSTAT: BUFFER DESCRIPTOR n STATUS REGISTER (BD0STAT THROUGH BD63STAT), SIE MODE (DATA RETURNED BY THE SIE TO THE MCU)

| R/W-x | r-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|-------|-----|-------|-------|-------|-------|-------|-------|

| UOWN  | r   | PID3  | PID2  | PID1  | PID0  | BC9   | BC8   |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           | r = Reserved bit |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

#### bit 7 UOWN: USB Own bit

1 = The SIE owns the BD and its corresponding buffer

bit 6 **Reserved:** Not written by the SIE

bit 5-2 **PID<3:0>:** Packet Identifier bits

The received token PID value of the last transfer (IN, OUT or SETUP transactions only).

bit 1-0 BC<9:8>: Byte Count 9 and 8 bits These bits are updated by the SIE to reflect the actual number of bytes received on an OUT transfer and the actual number of bytes transmitted on an IN transfer.

#### REGISTER 28-15: DEVID2: DEVICE ID REGISTER 2 FOR THE PIC18FXXJ94

| R     | R    | R    | R    | R    | R    | R    | R     |

|-------|------|------|------|------|------|------|-------|

| DEV10 | DEV9 | DEV8 | DEV7 | DEV6 | DEV5 | DEV4 | DEV3  |

| bit 7 |      |      |      |      |      |      | bit 0 |

|       |      |      |      |      |      |      | ~     |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-0 DEV<10:3>: Device ID bits

Γ.

These bits are used with the DEV<2:0> bits in the Device ID Register 1 to identify the part number.

#### REGISTER 28-16: DEVID1: DEVICE ID REGISTER 1 FOR THE PIC18FXXJ94

| R     | R    | R    | R    | R    | R    | R    | R     |

|-------|------|------|------|------|------|------|-------|

| DEV2  | DEV1 | DEV0 | REV4 | REV3 | REV2 | REV1 | REV0  |

| bit 7 |      |      |      |      |      |      | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 7-5 **DEV<2:0>:** Device ID bits

These bits are used with the DEV<10:3> bits in the Device ID Register 2 to identify the part number:

| 0110 | 0010 | 101 = PIC18F97J94 |

|------|------|-------------------|

| 0110 | 0010 | 111 = PIC18F96J94 |

| 0110 | 0011 | 000 = PIC18F95J94 |

| 0110 | 0011 | 001 = PIC18F87J94 |

| 0110 | 0011 | 011 = PIC18F86J94 |

| 0110 | 0011 | 100 = PIC18F85J94 |

| 0110 | 0011 | 101 = PIC18F67J94 |

| 0110 | 0011 | 111 = PIC18F66J94 |

| 0110 | 0100 | 000 = PIC18F65J94 |

|      |      |                   |

bit 4-0 **REV<4:0>:** Revision ID bits

These bits are used to indicate the device revision.

| RETI        | FIE                                         | Return from                                                                                               | Return from Interrupt                                                                                                                                                                                                                                                                                                                                                    |                                             |  |  |  |

|-------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|--|--|--|

| Synta       | ax:                                         | RETFIE {s                                                                                                 | RETFIE {s}                                                                                                                                                                                                                                                                                                                                                               |                                             |  |  |  |

| Operands:   |                                             | $s \in [0,1]$                                                                                             | s ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                |                                             |  |  |  |

| Oper        | ation:                                      | $1 \rightarrow GIE/GI$<br>if s = 1,<br>(WS) $\rightarrow$ W,<br>(STATUSS)<br>(BSRS) $\rightarrow$ I       |                                                                                                                                                                                                                                                                                                                                                                          |                                             |  |  |  |

| Statu       | s Affected:                                 | GIE/GIEH,                                                                                                 | PEIE/GIEL.                                                                                                                                                                                                                                                                                                                                                               |                                             |  |  |  |

| Enco        | ding:                                       | 0000                                                                                                      | 0000 000                                                                                                                                                                                                                                                                                                                                                                 | 01 000s                                     |  |  |  |

| Desc        | ription:                                    | and Top-of-<br>the PC. Inter<br>setting eithe<br>Global Inter<br>contents of<br>STATUSS a<br>their corres | Return from interrupt. Stack is popped<br>and Top-of-Stack (TOS) is loaded into<br>the PC. Interrupts are enabled by<br>setting either the high or low-priority<br>Global Interrupt Enable bit. If 's' = 1, the<br>contents of the shadow registers WS,<br>STATUSS and BSRS are loaded into<br>their corresponding registers W,<br>STATUS and BSR. If 's' = 0, no update |                                             |  |  |  |

| Word        | ls:                                         | 1                                                                                                         | •                                                                                                                                                                                                                                                                                                                                                                        |                                             |  |  |  |

| Cycle       | es:                                         | 2                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                          |                                             |  |  |  |

| -           | ycle Activity:                              |                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                          |                                             |  |  |  |

|             | Q1                                          | Q2                                                                                                        | Q3                                                                                                                                                                                                                                                                                                                                                                       | Q4                                          |  |  |  |