Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                        |

| Peripherals                | Brown-out Detect/Reset, HLVD, LCD, POR, PWM, WDT                            |

| Number of I/O              | 86                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 4K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                   |

| Data Converters            | A/D 24x12b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

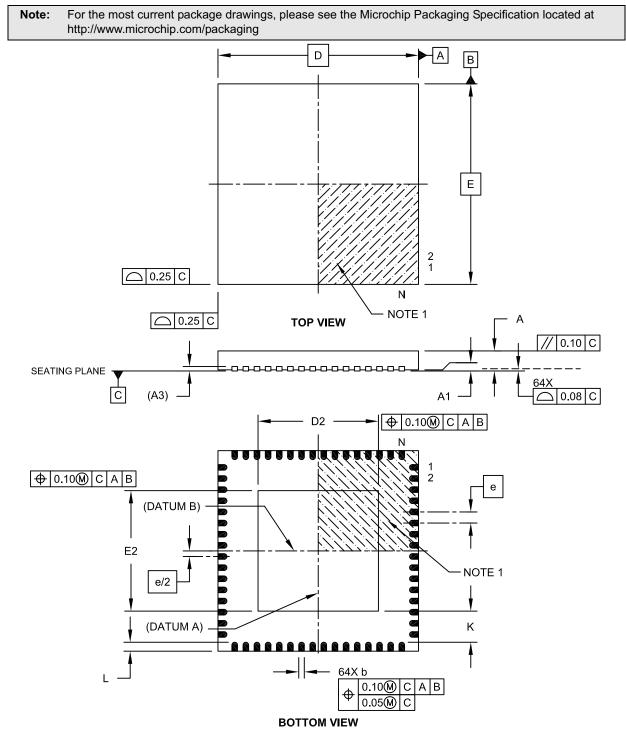

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 100-TQFP                                                                    |

| Supplier Device Package    | 100-TQFP (12x12)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f96j94t-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-3: DEVICE FEATURES FOR       | ABLE 1-3: DEVICE FEATURES FOR THE 100-PIN DEVICES         |                                                                                       |                  |  |  |  |  |  |  |  |  |

|--------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------|------------------|--|--|--|--|--|--|--|--|

| Features                             | PIC18F95J94                                               | PIC18F96J94                                                                           | PIC18F97J94      |  |  |  |  |  |  |  |  |

| Operating Frequency                  |                                                           | DC – 64 MHz                                                                           |                  |  |  |  |  |  |  |  |  |

| Dragram Maman ( (B) tao)             | 32 K                                                      | 64K                                                                                   | 128K             |  |  |  |  |  |  |  |  |

| Program Memory (Bytes)               | (Up to                                                    | 2 Mbytes with Extende                                                                 | ed Memory)       |  |  |  |  |  |  |  |  |

| Program Memory (Instructions)        | 16,384                                                    | 32,768                                                                                | 65,536           |  |  |  |  |  |  |  |  |

| Data Memory (Bytes)                  | 4K                                                        | 4K                                                                                    | 4K               |  |  |  |  |  |  |  |  |

| Interrupt Sources                    | 42                                                        |                                                                                       | 48               |  |  |  |  |  |  |  |  |

| I/O Ports                            | Por                                                       | ts A, B, C, D, E, F, G, H                                                             | I, J, K, L       |  |  |  |  |  |  |  |  |

| Parallel Communications              |                                                           | Parallel Slave Port (F                                                                | PSP)             |  |  |  |  |  |  |  |  |

| Timers                               | 8                                                         |                                                                                       |                  |  |  |  |  |  |  |  |  |

| Comparators                          | 3                                                         |                                                                                       |                  |  |  |  |  |  |  |  |  |

| LCD                                  | 480 pixels                                                |                                                                                       |                  |  |  |  |  |  |  |  |  |

| СТМИ                                 |                                                           | Yes                                                                                   |                  |  |  |  |  |  |  |  |  |

| RTCC                                 |                                                           | Yes                                                                                   |                  |  |  |  |  |  |  |  |  |

| Enhanced Capture/Compare/PWM Modules |                                                           | 3 ECCPs and 7 CC                                                                      | Ps               |  |  |  |  |  |  |  |  |

| Serial Communications                | Two MSSPs, Fo                                             | ur Enhanced USARTs                                                                    | (EUSART) and USB |  |  |  |  |  |  |  |  |

| 12-Bit Analog-to-Digital Module      |                                                           | 24 Input Channels                                                                     | ;                |  |  |  |  |  |  |  |  |

| Resets (and Delays)                  | POR, BOR, CM RESE                                         | POR, BOR, CM RESET Instruction, Stack Full, Stack Underflow, MCLR,<br>WDT (PWRT, OST) |                  |  |  |  |  |  |  |  |  |

| Instruction Set                      | 75 Instructions, 83 with Extended Instruction Set Enabled |                                                                                       |                  |  |  |  |  |  |  |  |  |

| Packages                             |                                                           | 100-Pin TQFP                                                                          |                  |  |  |  |  |  |  |  |  |

## TABLE 1-3: DEVICE FEATURES FOR THE 100-PIN DEVICES

## 3.1 CPU Clocking Scheme

The system clock source can be provided by one of four sources:

- Primary Oscillator (POSC) on the OSC1 and OSC2 pins

- Secondary Oscillator (SOSC) on the SOSCI and SOSCO pins

- Fast Internal RC (FRC) Oscillator

- · Low-Power Internal RC (LPRC) Oscillator

The Primary Oscillator and FRC sources have the option of using the internal USB PLL block, which generates both the USB module clock and a separate system clock from the 96 MHz PLL. Refer to **Section 3.8.1 "Oscillator Modes and USB Operation**" for additional information.

The internal FRC provides an 8 MHz clock source. It can optionally be reduced by the programmable clock divider to provide a range of system clock frequencies.

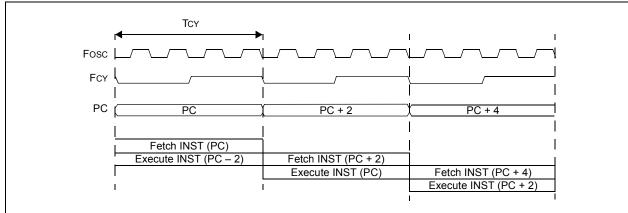

The selected clock source generates the processor and peripheral clock sources. The processor clock source is divided by four to produce the internal instruction cycle clock, FCY. In this document, the instruction cycle clock is also denoted by FOSC/4. The internal instruction cycle clock, FOSC/4, can be provided on the OSC2 I/O pin for some operating modes of the Primary Oscillator. The timing diagram in Figure 3-2 shows the relationship between the processor clock source and instruction execution.

## FIGURE 3-2: CLOCK OR INSTRUCTION CYCLE TIMING

|           | File Name     | Bit 7 | Bit 6  | Bit 5   | Bit 4  | Bit 3       | Bit 2       | Bit 1  | Bit 0   |  |  |

|-----------|---------------|-------|--------|---------|--------|-------------|-------------|--------|---------|--|--|

|           |               | 5117  |        |         | Dit 4  | Dit 3       |             |        | Dit V   |  |  |

| E36h      | RPINR24_25    |       |        | R<3:0>  |        |             | IOC6R«      |        |         |  |  |

| E35h      | RPINR22_23    | -     |        | R<3:0>  |        |             | IOC4R       |        |         |  |  |

| E34h      | RPINR20_21    |       |        | R<3:0>  |        | IOC2R<3:0>  |             |        |         |  |  |

| E33h      | RPINR18_19    |       |        | R<3:0>  |        |             | IOC0R•      | <3:0>  |         |  |  |

| E32h      | RPINR16_17    |       | ECCPS  | 3R<3:0> |        |             | ECCP2F      | <3:0>  |         |  |  |

| E31h      | RPINR14_15    |       | ECCP'  | 1R<3:0> |        |             | FLT0R«      | <3:0>  |         |  |  |

| E30h      | RPINR12_13    |       | SS2F   | ?<3:0>  |        |             | SDI2R«      | <3:0>  |         |  |  |

| E2Fh      | RPINR10_11    |       | SCK2   | R<3:0>  |        |             | SS1R<       | :3:0>  |         |  |  |

| E2Eh      | RPINR8_9      |       | SDI1   | R<3:0>  |        |             | SCK1R       | <3:0>  |         |  |  |

| E2Dh      | RPINR6_7      |       | U4TX   | R<3:0>  |        |             | U4RXR       | <3:0>  |         |  |  |

| E2Ch      | RPINR4_5      |       | U3TX   | R<3:0>  |        |             | U3RXR       | <3:0>  |         |  |  |

| E2Bh      | RPINR2_3      |       | U2TX   | R<3:0>  |        |             | U2RXR       | <3:0>  |         |  |  |

| E2Ah      | RPINR0_1      |       | U1TX   | R<3:0>  |        |             | U1RXR       | <3:0>  |         |  |  |

| E29h      | RPOR46        | _     |        | _       | _      |             | RPO46F      | <3:0>  |         |  |  |

| E28h      | RPOR44_45     |       | RPO45  | 5R<3:0> |        |             | RPO44F      | <3:0>  |         |  |  |

| E27h      | RPOR42_43     |       | RPO43  | 3R<3:0> |        |             | RPO42F      | <3:0>  |         |  |  |

| E26h      | <br>RPOR40_41 |       | RPO4   | 1R<3:0> |        |             | RPO40F      | <3:0>  |         |  |  |

| E25h      | <br>RPOR38_39 |       | RP039  | )R<3:0> |        |             | RPO38F      | <3:0>  |         |  |  |

| =24h      | <br>RPOR36_37 |       |        | 7R<3:0> |        |             | RPO36F      |        |         |  |  |

| =23h      | RPOR34_35     |       |        | 5R<3:0> |        |             | RPO34F      |        |         |  |  |

| =22h      | RPOR32_33     |       |        | 3R<3:0> |        |             | RPO32F      |        |         |  |  |

| =<br>=21h | RPOR30_31     |       |        | 1R<3:0> |        | RP030R<3:0> |             |        |         |  |  |

| =20h      | RPOR28_29     |       |        | )R<3:0> |        |             | RPO28F      |        |         |  |  |

| E1Fh      | RPOR26_27     |       |        | 7R<3:0> |        |             | RPO26F      |        |         |  |  |

| E1Eh      | RPOR24_25     |       |        | 5R<3:0> |        |             | RP024R<3:0> |        |         |  |  |

| E1Dh      | RPOR24_23     |       |        | 3R<3:0> |        |             | RPO24F      |        |         |  |  |

|           |               |       |        |         |        | RPO20R<3:0> |             |        |         |  |  |

| E1Ch      | RPOR20_21     |       |        | 1R<3:0> |        | RP018R<3:0> |             |        |         |  |  |

| E1Bh      | RPOR18_19     |       |        | 9R<3:0> |        |             |             |        |         |  |  |

| E1Ah      | RPOR16_17     |       |        | 7R<3:0> |        | RP016R<3:0> |             |        |         |  |  |

| E19h      | RPOR14_15     |       |        | 5R<3:0> |        | RPO14R<3:0> |             |        |         |  |  |

| E18h      | RPOR12_13     |       |        | 3R<3:0> |        | RP012R<3:0> |             |        |         |  |  |

| E17h      | RPOR10_11     |       |        | IR<3:0> |        |             | RPO10F      |        |         |  |  |

| E16h      | RPOR8_9       |       |        | R<3:0>  |        |             | RPO8R       |        |         |  |  |

| E15h      | RPOR6_7       |       |        | R<3:0>  |        |             | RPO6R       |        |         |  |  |

| E14h      | RPOR4_5       |       |        | R<3:0>  |        |             | RPO4R       |        |         |  |  |

| E13h      | RPOR2_3       |       |        | R<3:0>  |        |             | RPO2R       |        |         |  |  |

| E12h      | RPOR0_1       |       |        | R<3:0>  |        |             | RPOOR       |        | r       |  |  |

| E11h      | UCFG          | UTEYE | UOEMON | _       | UPUEN  | UTRDIS      | FSEN        | PPB1   | PPB0    |  |  |

| E10h      | UIE           |       | SOFIE  | STALLIE | IDLEIE | TRNIE       | ACTVIE      | UERRIE | URSTIE  |  |  |

| E0Fh      | UEIE          | BTSEE | —      | —       | BTOEE  | DFN8EE      | CRC16EE     | CRC5EE | PIDEE   |  |  |

| E0Eh      | UEP15         | —     | _      | —       | EPHSHK | EPCONDIS    | EPOUTEN     | EPINEN | EPSTALL |  |  |

| E0Dh      | UEP14         | —     | —      | —       | EPHSHK | EPCONDIS    | EPOUTEN     | EPINEN | EPSTALL |  |  |

| E0Ch      | UEP13         | —     | —      | —       | EPHSHK | EPCONDIS    | EPOUTEN     | EPINEN | EPSTALL |  |  |

| E0Bh      | UEP12         | —     | —      | —       | EPHSHK | EPCONDIS    | EPOUTEN     | EPINEN | EPSTALL |  |  |

| E0Ah      | UEP11         | —     | —      | —       | EPHSHK | EPCONDIS    | EPOUTEN     | EPINEN | EPSTALL |  |  |

| E09h      | UEP10         | —     | _      | —       | EPHSHK | EPCONDIS    | EPOUTEN     | EPINEN | EPSTALL |  |  |

| E08h      | UEP9          | _     | —      | _       | EPHSHK | EPCONDIS    | EPOUTEN     | EPINEN | EPSTALL |  |  |

| E07h      | UEP8          |       | —      | —       | EPHSHK | EPCONDIS    | EPOUTEN     | EPINEN | EPSTALL |  |  |

| E06h      | UEP7          |       |        | _       | EPHSHK | EPCONDIS    | EPOUTEN     | EPINEN | EPSTALL |  |  |

| E05h      | UEP6          |       | _      | _       | EPHSHK | EPCONDIS    | EPOUTEN     | EPINEN | EPSTALL |  |  |

| E04h      | UEP5          | _     | _      | _       | EPHSHK | EPCONDIS    | EPOUTEN     | EPINEN | EPSTALL |  |  |

TABLE 6-2: REGISTER FILE SUMMARY (CONTINUED)

**Legend:** — = unimplemented, read as '0'.

| R/W-1                 | R/W-1                                                             | R/W-1                                                  | R/W-1            | R/W-1             | R/W-1            | R/W-1           | R/W-1   |  |  |  |  |

|-----------------------|-------------------------------------------------------------------|--------------------------------------------------------|------------------|-------------------|------------------|-----------------|---------|--|--|--|--|

| OSCFIP                | SSP2IP                                                            | BCL2IP                                                 | USBIP            | BCL1IP            | HLVDIP           | TMR3IP          | TMR3GIP |  |  |  |  |

| bit 7                 | ·                                                                 | •                                                      | •                |                   | •                |                 | bit 0   |  |  |  |  |

| Levendu               |                                                                   |                                                        |                  |                   |                  |                 |         |  |  |  |  |

| Legend:<br>R = Readab | la hit                                                            | W = Writable                                           | hit              | II – Unimplon     | nented bit, read | d oo 'O'        |         |  |  |  |  |

| -n = Value a          |                                                                   | '1' = Bit is set                                       |                  | '0' = Bit is clea |                  | x = Bit is unkr |         |  |  |  |  |

|                       | IFUR                                                              | I – DILIS SEL                                          |                  |                   | areu             |                 | IOWI    |  |  |  |  |

| bit 7                 | OSCFIP: Os                                                        | cillator Fail Inter                                    | rupt Priority b  | it                |                  |                 |         |  |  |  |  |

|                       | 1 = High price                                                    |                                                        |                  |                   |                  |                 |         |  |  |  |  |

|                       | 0 = Low prio                                                      |                                                        |                  |                   |                  |                 |         |  |  |  |  |

| bit 6                 | SSP2IP: Mas                                                       | ster Synchronou                                        | is Serial Port 2 | 2 Interrupt Prior | ity bit          |                 |         |  |  |  |  |

|                       | 1 = High priority                                                 |                                                        |                  |                   |                  |                 |         |  |  |  |  |

|                       | 0 = Low prio                                                      |                                                        |                  |                   |                  |                 |         |  |  |  |  |

| bit 5                 | BCL2IP: Bus Collision Interrupt Priority bit (MSSP)               |                                                        |                  |                   |                  |                 |         |  |  |  |  |

|                       | 1 = High priority<br>0 = Low priority                             |                                                        |                  |                   |                  |                 |         |  |  |  |  |

| bit 4                 | •                                                                 | •                                                      | v hit            |                   |                  |                 |         |  |  |  |  |

| DIL 4                 |                                                                   | JSBIP: USB Interrupt Priority bit<br>L = High priority |                  |                   |                  |                 |         |  |  |  |  |

|                       | 0 = Low priority                                                  |                                                        |                  |                   |                  |                 |         |  |  |  |  |

| bit 3                 | •                                                                 | •                                                      | upt Priority bit |                   |                  |                 |         |  |  |  |  |

|                       | BCL1IP: Bus Collision Interrupt Priority bit<br>1 = High priority |                                                        |                  |                   |                  |                 |         |  |  |  |  |

|                       | 0 = Low prio                                                      | rity                                                   |                  |                   |                  |                 |         |  |  |  |  |

| bit 2                 | HLVDIP: High/Low-Voltage Detect Interrupt Priority bit            |                                                        |                  |                   |                  |                 |         |  |  |  |  |

|                       | 1 = High priority                                                 |                                                        |                  |                   |                  |                 |         |  |  |  |  |

|                       | 0 = Low prio                                                      | •                                                      |                  |                   |                  |                 |         |  |  |  |  |

| bit 1                 |                                                                   | R3 Overflow Inf                                        | errupt Priority  | bit               |                  |                 |         |  |  |  |  |

|                       | 1 = High pric<br>0 = Low prio                                     |                                                        |                  |                   |                  |                 |         |  |  |  |  |

| bit 0                 |                                                                   | -                                                      | rupt Driarity bi | +                 |                  |                 |         |  |  |  |  |

|                       | 1 = High price                                                    | MR3 Gate Inter                                         | iupi Priority Di | ι                 |                  |                 |         |  |  |  |  |

|                       | 1 = High pho0 = Low prio                                          | •                                                      |                  |                   |                  |                 |         |  |  |  |  |

## REGISTER 10-17: IPR2: PERIPHERAL INTERRUPT PRIORITY REGISTER 2

| R-0                                                                  | R-0                                    | R/W-0            | R/W-0          | U-0              | U-0             | U-0             | U-0          |  |  |  |  |

|----------------------------------------------------------------------|----------------------------------------|------------------|----------------|------------------|-----------------|-----------------|--------------|--|--|--|--|

| IBF                                                                  | OBF                                    | IBOV             | PSPMODE        | —                | —               | —               | —            |  |  |  |  |

| bit 7                                                                |                                        |                  |                |                  |                 |                 | bit 0        |  |  |  |  |

|                                                                      |                                        |                  |                |                  |                 |                 |              |  |  |  |  |

| Legend:                                                              |                                        |                  |                |                  |                 |                 |              |  |  |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                        |                  |                |                  |                 |                 |              |  |  |  |  |

| -n = Value at                                                        | POR                                    | '1' = Bit is set |                | '0' = Bit is cle | ared            | x = Bit is unkr | iown         |  |  |  |  |

|                                                                      |                                        |                  |                |                  |                 |                 |              |  |  |  |  |

| bit 7                                                                | it 7 IBF: Input Buffer Full Status bit |                  |                |                  |                 |                 |              |  |  |  |  |

|                                                                      |                                        |                  |                | ng to be read l  | by the CPU      |                 |              |  |  |  |  |

|                                                                      | 0 = No word h                          | nas been recei   | ved            |                  |                 |                 |              |  |  |  |  |

| bit 6                                                                |                                        | Buffer Full Sta  |                |                  |                 |                 |              |  |  |  |  |

|                                                                      |                                        |                  |                | ly written word  | l               |                 |              |  |  |  |  |

|                                                                      |                                        | it buffer has be |                |                  |                 |                 |              |  |  |  |  |

| bit 5                                                                | IBOV: Input B                          | uffer Overflow   | Detect bit     |                  |                 |                 |              |  |  |  |  |

|                                                                      | 1 = A write oc<br>0 = No overflo       |                  | previously inp | out word had n   | ot been read (m | nust be cleared | in software) |  |  |  |  |

| bit 4                                                                | PSPMODE: F                             | Parallel Slave F | Port Mode Sele | ect bit          |                 |                 |              |  |  |  |  |

|                                                                      | 1 = Parallel Slave Port mode           |                  |                |                  |                 |                 |              |  |  |  |  |

|                                                                      | 0 = General F                          | Purpose I/O mo   | ode            |                  |                 |                 |              |  |  |  |  |

| bit 3-0                                                              | Unimplemen                             | ted: Read as '   | 0'             |                  |                 |                 |              |  |  |  |  |

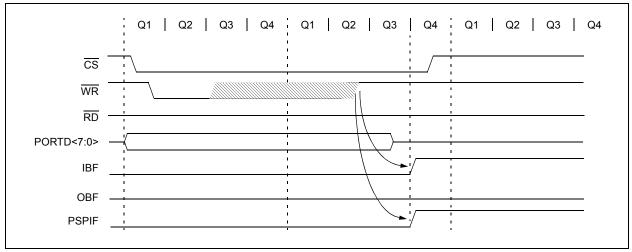

### REGISTER 11-4: PSPCON: PARALLEL SLAVE PORT CONTROL REGISTER

### FIGURE 11-4: PARALLEL SLAVE PORT WRITE WAVEFORMS

PPS-Lite Input Peripheral Group 4n + 3

| PPS-Lite Input Peripheral Group 4n + 2 |  |  |  |  |  |  |  |  |  |

|----------------------------------------|--|--|--|--|--|--|--|--|--|

| Register                               |  |  |  |  |  |  |  |  |  |

|                                        |  |  |  |  |  |  |  |  |  |

|                                        |  |  |  |  |  |  |  |  |  |

|                                        |  |  |  |  |  |  |  |  |  |

|                                        |  |  |  |  |  |  |  |  |  |

|                                        |  |  |  |  |  |  |  |  |  |

|                                        |  |  |  |  |  |  |  |  |  |

|                                        |  |  |  |  |  |  |  |  |  |

|                                        |  |  |  |  |  |  |  |  |  |

|                                        |  |  |  |  |  |  |  |  |  |

|                                        |  |  |  |  |  |  |  |  |  |

|                                        |  |  |  |  |  |  |  |  |  |

|                                        |  |  |  |  |  |  |  |  |  |

|                                        |  |  |  |  |  |  |  |  |  |

|                                        |  |  |  |  |  |  |  |  |  |

| g Value                                |  |  |  |  |  |  |  |  |  |

| g Value                                |  |  |  |  |  |  |  |  |  |

| g Value                                |  |  |  |  |  |  |  |  |  |

| g Value                                |  |  |  |  |  |  |  |  |  |

| g Value                                |  |  |  |  |  |  |  |  |  |

| g Value                                |  |  |  |  |  |  |  |  |  |

| g Value                                |  |  |  |  |  |  |  |  |  |

| g Value                                |  |  |  |  |  |  |  |  |  |

| ) Value                                |  |  |  |  |  |  |  |  |  |

| g Value                                |  |  |  |  |  |  |  |  |  |

| g Value                                |  |  |  |  |  |  |  |  |  |

| g Value                                |  |  |  |  |  |  |  |  |  |

| ) Value                                |  |  |  |  |  |  |  |  |  |

| g Value                                |  |  |  |  |  |  |  |  |  |

| g Value                                |  |  |  |  |  |  |  |  |  |

| ) Value                                |  |  |  |  |  |  |  |  |  |

|                                        |  |  |  |  |  |  |  |  |  |

### TABLE 11-13: RPIN REGISTERS AND AVAILABLE FUNCTIONS (CONTINUED)

#### (1) To Map this Signal (4) to the Associated RPIN Register SS2 RPINR12 13<7:4> INT3 RPINR28 29<3:0> IOC3 RPINR20 21<7:4> IOC7 RPINR24 25<7:4> U1RX RPINR0\_1<3:0> U2TX RPINR2 3<7:4> SCK1 RPINR8 9<3:0> ECCP1 RPINR14\_15<7:4> ECCP2 RPINR16\_17<3:0> CCP4 RPINR32 33<3:0> RPINR48\_49<7:4> RVP3 RVP7 RPINR52\_53<7:4> (2) with this RPn Pin (3) Write this Corresponding Value RP3 h'0 RP7 h'1 **RP11** h'2 **RP15** h'3 **RP19** h'4 RP23 h'5 **RP27** h'6 **RP31** h'7 RP35 h'8 **RP39** h'9 RP43 h'A h'B h'C h'D \_\_\_\_ h'E Vss h'F

## 11.15.3.2 Output Mapping

In contrast to the inputs, the outputs of the Peripheral Pin Select options are mapped on the basis of the pin. In this case, a bit field associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers contain sets of 4-bit fields, with each associated with one RPn pin (see Register 11-5). The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin. Each pin has a limited set of peripherals to choose from.

The PPS-Lite peripheral outputs and associated RPn pins have been organized into four groups. It is not possible to map a peripheral to an RPn pin which is outside of its group. To map a peripheral output signal to

an RPn pin, use the 4-step process, as indicated in Table 11-14. Choose the RPn pin and the signal; the column on the right shows which value to write to the associated RPORx register.

The peripheral outputs that support Peripheral Pin Selection have no default pins. Since the RPORx registers reset to all '0's, the outputs are all disconnected in the device's default (Reset) state.

The list of peripherals for output mapping also includes a null value of b'0000' because of the mapping technique. This allows unused peripherals to not be connected to a pin. Not all peripherals are available on all pins. For example, the "SDO2" signal is only available on RP0, RP4, RP8, etc. The "SDO2" signal is not available on RP1.

## PIC18F97J94 FAMILY

Calibration of the crystal can be done through this module to yield an error of 3 seconds or less per month.

(For further details, see Section 17.2.9 "Calibration".)

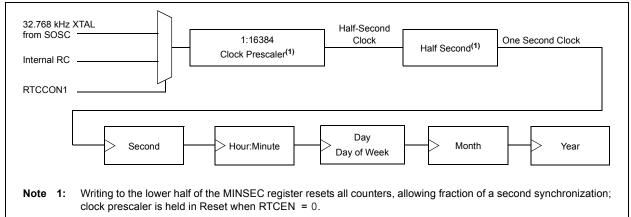

## 17.2.2 CLOCK SOURCE

As mentioned earlier, the RTCC module is intended to be clocked by an external Real-Time Clock (RTC) crystal, oscillating at 32.768 kHz, but an internal oscillator can be used. The RTCC clock selection is decided by the RTCOSC bit (CONFIG3L<0>).

### FIGURE 17-4: CLOCK SOURCE MULTIPLEXING

### 17.2.2.1 Real-Time Clock Enable

The RTCC module can be clocked by an external, 32.768 kHz crystal (SOSC Oscillator) or the LF-INTOSC Oscillator, which can be selected in CONFIG3L<0>.

If the external clock is used, the SOSC Oscillator should be enabled. If LF-INTOSC is providing the clock, the INTOSC clock can be brought out to the RTCC pin by the RTSECSEL<1:0> bits (RTCCON2<1:0>).

### 17.2.3 DIGIT CARRY RULES

This section explains which timer values are affected when there is a rollover:

- Time of Day: From 23:59:59 to 00:00:00 with a carry to the Day field

- Month: From 12/31 to 01/01 with a carry to the Year field

- Day of Week: From 6 to 0 with no carry (see Table 17-1)

- Year Carry: From 99 to 00; this also surpasses the use of the RTCC

For the day-to-month rollover schedule, see Table 17-2.

Because the following values are in BCD format, the carry to the upper BCD digit occurs at the count of 10, not 16 (SECONDS, MINUTES, HOURS, WEEKDAY, DAYS and MONTHS).

### TABLE 17-1: DAY OF WEEK SCHEDULE

| Day of Week |   |  |  |  |  |  |  |  |

|-------------|---|--|--|--|--|--|--|--|

| Sunday      | 0 |  |  |  |  |  |  |  |

| Monday      | 1 |  |  |  |  |  |  |  |

| Tuesday     | 2 |  |  |  |  |  |  |  |

| Wednesday   | 3 |  |  |  |  |  |  |  |

| Thursday    | 4 |  |  |  |  |  |  |  |

| Friday      | 5 |  |  |  |  |  |  |  |

| Saturday    | 6 |  |  |  |  |  |  |  |

### TABLE 17-2: DAY TO MONTH ROLLOVER SCHEDULE

| Month          | Maximum Day Field       |

|----------------|-------------------------|

| 01 (January)   | 31                      |

| 02 (February)  | 28 or 29 <sup>(1)</sup> |

| 03 (March)     | 31                      |

| 04 (April)     | 30                      |

| 05 (May)       | 31                      |

| 06 (June)      | 30                      |

| 07 (July)      | 31                      |

| 08 (August)    | 31                      |

| 09 (September) | 30                      |

| 10 (October)   | 31                      |

| 11 (November)  | 30                      |

| 12 (December)  | 31                      |

Note 1: See Section 17.2.4 "Leap Year".

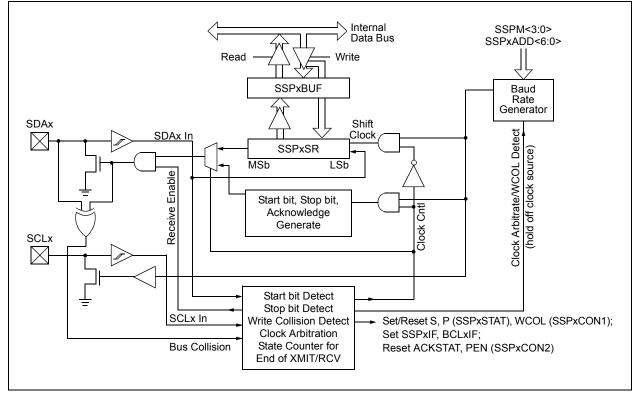

### 20.5.9 MASTER MODE

Master mode is enabled by setting and clearing the appropriate SSPMx bits in SSPxCON1, and by setting the SSPEN bit. In Master mode, the SCLx and SDAx lines are manipulated by the MSSPx hardware if the TRIS bits are set.

The Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSPx module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is Idle, with both the S and P bits clear.

In Firmware Controlled Master mode, user code conducts all  $I^2C$  bus operations based on Start and Stop bit conditions.

Once Master mode is enabled, the user has six options.

- 1. Assert a Start condition on SDAx and SCLx.

- 2. Assert a Repeated Start condition on SDAx and SCLx.

- 3. Write to the SSPxBUF register initiating transmission of data/address.

- 4. Configure the I<sup>2</sup>C port to receive data.

- 5. Generate an Acknowledge condition at the end of a received byte of data.

- 6. Generate a Stop condition on SDAx and SCLx.

- Note: The MSSPx module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPxBUF register to initiate transmission before the Start condition is complete. In this case, the SSPxBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPxBUF did not occur.

The following events will cause the MSSPx Interrupt Flag bit, SSPxIF, to be set (and MSSPx interrupt if enabled):

- Start condition

- Stop condition

- Data transfer byte transmitted/received

- · Acknowledge transmitted

- Repeated Start

## FIGURE 20-18: MSSPx BLOCK DIAGRAM (I<sup>2</sup>C MASTER MODE)

|              |                   | SYNC = 0, BRGH = 0, BRG16 = 0 |                       |                   |                             |                       |                   |                             |                       |                  |                             |     |  |  |

|--------------|-------------------|-------------------------------|-----------------------|-------------------|-----------------------------|-----------------------|-------------------|-----------------------------|-----------------------|------------------|-----------------------------|-----|--|--|

| BAUD<br>RATE | Fosc = 40.000 MHz |                               |                       | Fosc = 20.000 MHz |                             |                       | Fosc = 10.000 MHz |                             |                       | Fosc = 8.000 MHz |                             |     |  |  |

| (K)          | Actual CDDDC      |                               | Actual<br>Rate<br>(K) | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error       | SPBRG<br>value<br>(decimal) |     |  |  |

| 0.3          | —                 |                               |                       | _                 |                             |                       | _                 |                             | _                     | _                |                             | _   |  |  |

| 1.2          | —                 | —                             | —                     | 1.221             | 1.73                        | 255                   | 1.202             | 0.16                        | 129                   | 1.201            | -0.16                       | 103 |  |  |

| 2.4          | 2.441             | 1.73                          | 255                   | 2.404             | 0.16                        | 129                   | 2.404             | 0.16                        | 64                    | 2.403            | -0.16                       | 51  |  |  |

| 9.6          | 9.615             | 0.16                          | 64                    | 9.766             | 1.73                        | 31                    | 9.766             | 1.73                        | 15                    | 9.615            | -0.16                       | 12  |  |  |

| 19.2         | 19.531            | 1.73                          | 31                    | 19.531            | 1.73                        | 15                    | 19.531            | 1.73                        | 7                     | —                | _                           | _   |  |  |

| 57.6         | 56.818            | -1.36                         | 10                    | 62.500            | 8.51                        | 4                     | 52.083            | -9.58                       | 2                     | —                | _                           | _   |  |  |

| 115.2        | 125.000           | 8.51                          | 4                     | 104.167           | -9.58                       | 2                     | 78.125            | -32.18                      | 1                     | —                | _                           | _   |  |  |

## TABLE 21-2: BAUD RATES FOR ASYNCHRONOUS MODES

|              |                       | SYNC = 0, BRGH = 0, BRG16 = 0 |                             |                       |            |                             |                       |            |                             |  |  |  |  |

|--------------|-----------------------|-------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|--|--|--|

| BAUD<br>RATE | Fos                   | c = 4.000                     | MHz                         | Fos                   | c = 2.000  | MHz                         | Fosc = 1.000 MHz      |            |                             |  |  |  |  |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |  |  |

| 0.3          | 0.300                 | 0.16                          | 207                         | 0.300                 | -0.16      | 103                         | 0.300                 | -0.16      | 51                          |  |  |  |  |

| 1.2          | 1.202                 | 0.16                          | 51                          | 1.201                 | -0.16      | 25                          | 1.201                 | -0.16      | 12                          |  |  |  |  |

| 2.4          | 2.404                 | 0.16                          | 25                          | 2.403                 | -0.16      | 12                          | _                     | _          | _                           |  |  |  |  |

| 9.6          | 8.929                 | -6.99                         | 6                           | —                     | _          | _                           | _                     | _          | _                           |  |  |  |  |

| 19.2         | 20.833                | 8.51                          | 2                           | —                     | _          | _                           | _                     | _          | _                           |  |  |  |  |

| 57.6         | 62.500                | 8.51                          | 0                           | —                     | _          | _                           | —                     | _          | _                           |  |  |  |  |

| 115.2        | 62.500                | -45.75                        | 0                           | _                     | _          |                             |                       | _          |                             |  |  |  |  |

|             |                       |            |                             |                       | SYNC       | = 0, BRGH                   | <b>i =</b> 1, BRG     | <b>16 =</b> 0 |                             |                       |            |                             |

|-------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|---------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD        | Fosc = 40.000 MHz     |            |                             | Fosc = 20.000 MHz     |            |                             | Fosc = 10.000 MHz     |               |                             | Fosc = 8.000 MHz      |            |                             |

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3         | —                     | _          |                             | _                     |            |                             | _                     |               |                             | _                     | _          | _                           |

| 1.2         | —                     | _          | _                           | —                     | _          | _                           | —                     | _             | _                           | _                     | —          | —                           |

| 2.4         | —                     | _          | _                           | —                     | _          | _                           | 2.441                 | 1.73          | 255                         | 2.403                 | -0.16      | 207                         |

| 9.6         | 9.766                 | 1.73       | 255                         | 9.615                 | 0.16       | 129                         | 9.615                 | 0.16          | 64                          | 9.615                 | -0.16      | 51                          |

| 19.2        | 19.231                | 0.16       | 129                         | 19.231                | 0.16       | 64                          | 19.531                | 1.73          | 31                          | 19.230                | -0.16      | 25                          |

| 57.6        | 58.140                | 0.94       | 42                          | 56.818                | -1.36      | 21                          | 56.818                | -1.36         | 10                          | 55.555                | 3.55       | 8                           |

| 115.2       | 113.636               | -1.36      | 21                          | 113.636               | -1.36      | 10                          | 125.000               | 8.51          | 4                           | _                     | _          | _                           |

|              | SYNC = 0, BRGH = 1, BRG16 = 0 |            |                             |                       |            |                             |                       |            |                             |  |  |  |

|--------------|-------------------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|--|--|

| BAUD<br>RATE | Foso                          | c = 4.000  | MHz                         | Fos                   | c = 2.000  | MHz                         | Fosc = 1.000 MHz      |            |                             |  |  |  |

| (K)          | Actual<br>Rate<br>(K)         | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |  |

| 0.3          |                               |            | _                           |                       |            | _                           | 0.300                 | -0.16      | 207                         |  |  |  |

| 1.2          | 1.202                         | 0.16       | 207                         | 1.201                 | -0.16      | 103                         | 1.201                 | -0.16      | 51                          |  |  |  |

| 2.4          | 2.404                         | 0.16       | 103                         | 2.403                 | -0.16      | 51                          | 2.403                 | -0.16      | 25                          |  |  |  |

| 9.6          | 9.615                         | 0.16       | 25                          | 9.615                 | -0.16      | 12                          | _                     | _          | —                           |  |  |  |

| 19.2         | 19.231                        | 0.16       | 12                          | _                     | _          | _                           | _                     | _          | —                           |  |  |  |

| 57.6         | 62.500                        | 8.51       | 3                           | _                     | _          | _                           | _                     | _          | _                           |  |  |  |

| 115.2        | 125.000                       | 8.51       | 1                           |                       | —          | —                           |                       |            | —                           |  |  |  |

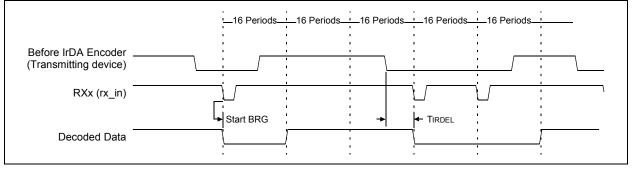

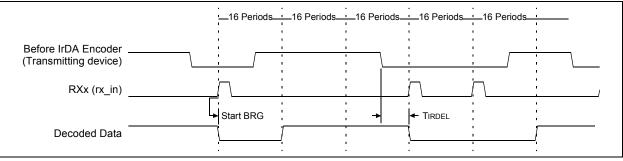

## 21.5.2.3 IrDA Decoder Function

The decoder works by taking the serial data from the RXx pin and replacing it with the decoded data stream. The stream is decoded based on falling edge detection of the RXx input.

Each falling edge of RXx causes the decoded data to be driven low for 16 periods of the 16x Baud Clock. If another falling edge has been detected by the time the 16 periods expire, the decoded data remains low for another 16 periods. If no falling edge was detected, the decoded data is driven high.

Note that the data stream into the device is shifted anywhere from 7 to 8 periods of the 16x Baud Clock from the actual message source. The one clock uncertainty is due to the clock edge resolution. See Figure 21-18 for details.

## 21.5.2.4 IrDA Receive Polarity

The IrDA receive polarity is selected using the RXDTP bit. This bit only affects the receive encoder and does not affect the transmitter.

When RXDTP = 0, the Idle state of the RXx line is '1' (see Figure 21-18). When RXDTP = 1, the Idle state of the RXx line is '0' (see Figure 21-19).

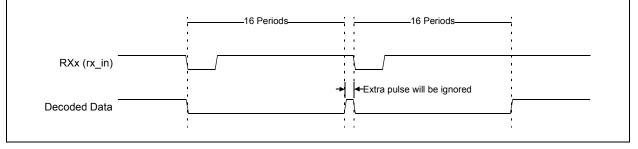

### 21.5.2.5 Clock Jitter

Due to jitter or slight frequency differences between devices, it is possible for the next falling bit edge to be missed for one of the 16x periods. In that case, one clock-wide pulse appears on the decoded data stream. Since the EUSARTx performs a majority detect around the bit center, this does not cause erroneous data. See Figure 21-20 for details.

## FIGURE 21-18: MACRO VIEW OF IrDA<sup>®</sup> DECODING SCHEME (RXDTP = 0)

## FIGURE 21-19: INVERTED POLARITY DECODING RESULTS (RXDTP = 1)

## FIGURE 21-20: CLOCK JITTER CAUSING A PULSE BETWEEN CONSECUTIVE ZEROS

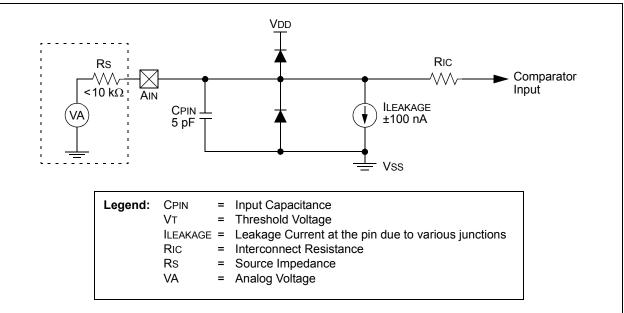

## 23.5 Comparator Control and Configuration

Each comparator has up to eight possible combinations of inputs: up to four external analog inputs and one of two internal voltage references.

All of the comparators allow a selection of the signal from pin, CxINA, or the voltage from the Comparator Reference (CVREF) on the non-inverting channel. This is compared to either CxINB, CxINC, C2IND or the microcontroller's fixed internal reference voltage (VBG, 1.2V nominal) on the inverting channel. The comparator inputs and outputs are tied to fixed I/O pins, defined in Table 23-1. The available comparator configurations and their corresponding bit settings are shown in Figure 23-4.

TABLE 23-1: COMPARATOR INPUTS AND OUTPUTS

| Comparator | Input or Output | I/O Pin <sup>(†)</sup> |  |

|------------|-----------------|------------------------|--|

|            | C1INA (VIN+)    | RA5/RF6                |  |

|            | C1INB (VIN-)    | RF5                    |  |

| 1          | C1INC (VIN-)    | RH6 <sup>(2)</sup>     |  |

| 1          | C2INB(VIN-)     | RF2                    |  |

|            | CVREF (VIN+)    | RF5                    |  |

|            | C1OUT           | RPn <sup>(1)</sup>     |  |

|            | C2INA (VIN+)    | RA5                    |  |

|            | C2INB (VIN-)    | RF2                    |  |

| 2          | C2INC (VIN-)    | RH4 <sup>(2)</sup>     |  |

| 2          | C2IND (VIN-)    | RH5 <sup>(2)</sup>     |  |

|            | CVREF (VIN+)    | RF5                    |  |

|            | C2OUT           | RPn <sup>(1)</sup>     |  |

|            | C3INA (VIN+)    | RA5/RG2                |  |

|            | C3INB (VIN-)    | RG3                    |  |

| 3          | C2INB (VIN-)    | RF2                    |  |

| 5          | C3INC (VIN-)    | RG4                    |  |

|            | CVREF (VIN+)    | RF5                    |  |

|            | C3OUT           | RPn <sup>(1)</sup>     |  |

† The I/O pin is dependent on package type.

Note 1: These pins are remappable I/Os.

2: These pins are not available on 64-pin devices.

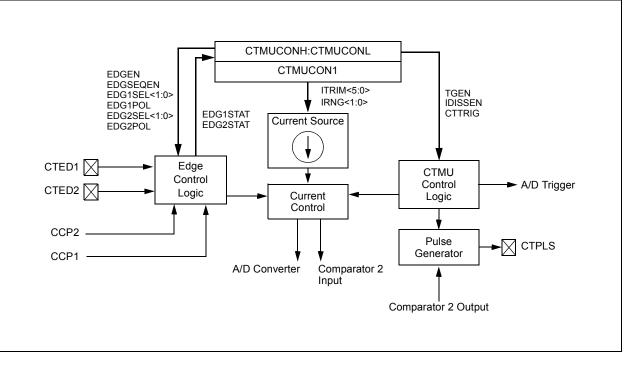

## 26.0 CHARGE TIME MEASUREMENT UNIT (CTMU)

The Charge Time Measurement Unit (CTMU) is a flexible analog module that provides accurate differential time measurement between pulse sources, as well as asynchronous pulse generation. By working with other on-chip analog modules, the CTMU can precisely measure time, capacitance and relative changes in capacitance or generate output pulses with a specific time delay. The CTMU is ideal for interfacing with capacitive-based sensors.

The module includes these key features:

- Up to 24 channels available for capacitive or time measurement input

- Low-cost temperature measurement using on-chip diode channel

- On-chip precision current source

- · Sixteen-edge input trigger sources

- · Polarity control for each edge source

- Provides a trigger for the A/D Converter

- Control of edge sequence

- · Control of response to edges

- · Time measurement resolution of 1 nanosecond

- · High-precision time measurement

- Time delay of external or internal signal asynchronous to system clock

- Accurate current source suitable for capacitive measurement

The CTMU works in conjunction with the A/D Converter to provide up to 24 channels for time or charge measurement, depending on the specific device and the number of A/D channels available. When configured for time delay, the CTMU is connected to one of the analog comparators. The level-sensitive input edge sources can be selected from four sources: two external inputs or the CCP1/CCP2 Special Event Triggers.

The CTMU special event can trigger the Analog-to-Digital Converter module.

Figure 26-1 provides a block diagram of the CTMU.

## FIGURE 26-1: CTMU BLOCK DIAGRAM

## 27.2.2.2 Internal Pull-up Resistors

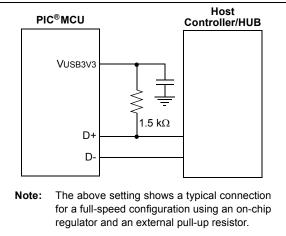

The PIC18FXXJ94 devices have built-in pull-up resistors, designed to meet the requirements for low-speed and full-speed USB. The UPUEN bit (UCFG<4>) enables the internal pull-ups. Figure 27-1 shows the pull-ups and their control.

Note: A compliant USB device should never source any current onto the +5V VBUS line of the USB cable. Additionally, USB devices should not source any current on the D+ and D- data lines whenever the +5V VBUS line is less than 1.17V. In order to be USB compliant, applications which are not purely bus-powered should monitor the VBUS line, and avoid turning on the USB module and the D+ or D- pull-up resistor until VBUS is greater than 1.17V. VBUS can be connected to and monitored by a 5V tolerant I/O pin, or if a resistive divider is used, by an analog capable pin.

## 27.2.2.3 External Pull-up Resistors

External pull-ups may also be used. The VUSB3V3 pin may be used to pull up D+ or D-. The pull-up resistor must be 1.5 k $\Omega$  (±5%) as required by the USB specifications.

Figure 27-2 provides an example of external circuitry.

### FIGURE 27-2: EXTERNAL CIRCUITRY

## 27.2.2.4 Ping-Pong Buffer Configuration

The usage of ping-pong buffers is configured using the PPB<1:0> bits. Refer to **Section 27.4.4** "**Ping-Pong Buffering**" for a complete explanation of the ping-pong buffers.

### 27.2.2.5 Eye Pattern Test Enable

An automatic eye pattern test can be generated by the module when the UCFG<7> bit is set. The eye pattern output will be observable based on module settings, meaning that the user is first responsible for configuring the SIE clock settings, pull-up resistor and Transceiver mode. In addition, the module has to be enabled.

Once UTEYE is set, the module emulates a switch from a receive to transmit state and will start transmitting a J-K-J-K bit sequence (K-J-K-J for full speed). The sequence will be repeated indefinitely while the Eye Pattern Test mode is enabled.

Note that this bit should never be set while the module is connected to an actual USB system. This Test mode is intended for board verification to aid with USB certification tests. It is intended to show a system developer the noise integrity of the USB signals which can be affected by board traces, impedance mismatches and proximity to other system components. It does not properly test the transition from a receive to a transmit state. Although the eye pattern is not meant to replace the more complex USB certification test, it should aid during first order system debugging.

## 27.9 Overview of USB

This section presents some of the basic USB concepts and useful information necessary to design a USB device. Although much information is provided in this section, there is a plethora of information provided within the USB specifications and class specifications. Thus, the reader is encouraged to refer to the USB specifications for more information (www.usb.org). If you are very familiar with the details of USB, then this section serves as a basic, high-level refresher of USB.

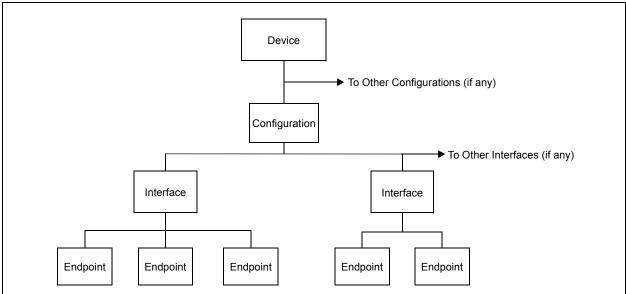

### 27.9.1 LAYERED FRAMEWORK

USB device functionality is structured into a layered framework, graphically illustrated in Figure 27-12. Each level is associated with a functional level within the device. The highest layer, other than the device, is the configuration. A device may have multiple configurations. For example, a particular device may have multiple power requirements based on Self-Power Only or Bus Power Only modes.

For each configuration, there may be multiple interfaces. Each interface could support a particular mode of that configuration.

Below the interface is the endpoint(s). Data is directly moved at this level. There can be as many as 16 bidirectional endpoints. Endpoint 0 is always a control endpoint, and by default, when the device is on the bus, Endpoint 0 must be available to configure the device.

## 27.9.2 FRAMES

Information communicated on the bus is grouped into 1 ms time slots, referred to as frames. Each frame can contain many transactions to various devices and endpoints. See Figure 27-8 for an example of a transaction within a frame.

### 27.9.3 TRANSFERS

There are four transfer types defined in the USB specification.

- **Isochronous:** This type provides a transfer method for large amounts of data (up to 1023 bytes) with timely delivery ensured; however, the data integrity is not ensured. This is good for streaming applications where small data loss is not critical, such as audio.

- **Bulk:** This type of transfer method allows for large amounts of data to be transferred with ensured data integrity; however, the delivery timeliness is not ensured.

- Interrupt: This type of transfer provides for ensured timely delivery for small blocks of data, plus data integrity is ensured.

- **Control:** This type provides for device setup control.

While full-speed devices support all transfer types, lowspeed devices are limited to interrupt and control transfers only.

## 27.9.4 POWER

Power is available from the USB. The USB specification defines the bus power requirements. Devices may either be self-powered or bus-powered. Self-powered devices draw power from an external source, while bus-powered devices use power supplied from the bus.

### FIGURE 27-12: USB LAYERS

# PIC18F97J94 FAMILY

| DAW                 | Decimal A                                                                    | djust W Regist                                                               | ter         | DECF                | Decremen                                                          | t f                                       |                                      |  |

|---------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------|-------------|---------------------|-------------------------------------------------------------------|-------------------------------------------|--------------------------------------|--|

| Syntax:             | DAW                                                                          |                                                                              | Syntax:     | DECF f {,d {,a}}    |                                                                   |                                           |                                      |  |

| Operands:           | None                                                                         |                                                                              | Operands:   | $0 \leq f \leq 255$ | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \end{array}$ |                                           |                                      |  |

| Operation:          | If $[W<3:0> > 9]$ or $[DC = 1]$ , then<br>$(W<3:0>) + 6 \rightarrow W<3:0>;$ |                                                                              |             |                     |                                                                   |                                           |                                      |  |

|                     |                                                                              |                                                                              |             | a ∈ [0,1]           |                                                                   |                                           |                                      |  |

|                     | else<br>(W<3:0>)                                                             | → W<3·0>                                                                     |             | Operation:          | $(f) - 1 \rightarrow de$                                          |                                           |                                      |  |

|                     | $(W<3:0>) \rightarrow W<3:0>$                                                |                                                                              |             | Status Affected:    | C, DC, N, 0                                                       | DV, Z                                     |                                      |  |

|                     | •                                                                            | > 9] or [C = 1],                                                             | then        | Encoding:           | 0000                                                              | 01da ff                                   | ff ffff                              |  |

|                     | (W<7:4>) +<br>C = 1;                                                         | $6 \rightarrow W < 7:4>;$                                                    |             | Description:        |                                                                   | register, 'f'. It                         |                                      |  |

|                     | C = ⊥,<br>else                                                               |                                                                              |             |                     |                                                                   | ored in W. If 'c<br>ored back in re       | ,                                    |  |

|                     | (W<7:4>) –                                                                   | → W<7:4>                                                                     |             |                     |                                                                   |                                           | 0                                    |  |

| Status Affected:    | С                                                                            |                                                                              |             |                     | ,                                                                 |                                           | ank is selected.<br>ed to select the |  |

| Encoding:           | 0000                                                                         | 0000 000                                                                     | 0 0111      |                     | GPR bank.                                                         |                                           |                                      |  |

| Description:        |                                                                              |                                                                              |             |                     | lf 'a' is '0' a                                                   | nd the extend                             | ded instruction                      |  |

| Description         |                                                                              | DAW adjusts the 8-bit value in W, resulting from the earlier addition of two |             |                     | set is enab                                                       | set is enabled, this instruction operates |                                      |  |

|                     | variables (e                                                                 | each in packed                                                               | BCD format) |                     |                                                                   | Literal Offset                            | 0                                    |  |

|                     | •                                                                            | es a correct pa                                                              | cked BCD    |                     |                                                                   | never f ≤ 95 (8                           |                                      |  |

|                     | result.                                                                      |                                                                              |             |                     |                                                                   | .2.3 "Byte-O                              | ns in Indexed                        |  |

| Words:              | 1                                                                            |                                                                              |             |                     |                                                                   | set Mode" fo                              |                                      |  |

| Cycles:             | 1                                                                            |                                                                              |             | Words:              | 1                                                                 |                                           |                                      |  |

| Q Cycle Activity:   |                                                                              |                                                                              |             | Cycles:             | 1                                                                 |                                           |                                      |  |

| Q1                  | Q2                                                                           | Q3                                                                           | Q4          | Q Cycle Activity:   |                                                                   |                                           |                                      |  |

| Decode              | Read                                                                         | Process                                                                      | Write       | Q1                  | Q2                                                                | Q3                                        | Q4                                   |  |

|                     | register W                                                                   | Data                                                                         | W           | Decode              | Read                                                              | Process                                   | Write to                             |  |

| Example 1:          | DAW                                                                          |                                                                              |             |                     | register 'f'                                                      | Data                                      | destination                          |  |

| Before Instruc      |                                                                              |                                                                              |             |                     |                                                                   |                                           |                                      |  |

| W                   | = A5h                                                                        |                                                                              |             | Example:            | DECF                                                              | CNT, 1,                                   | C                                    |  |

| C<br>DC             | = 0<br>= 0                                                                   |                                                                              |             | Before Instruc      | ction                                                             |                                           |                                      |  |

| After Instructi     | 0                                                                            |                                                                              |             | CNT<br>Z            | = 01h<br>= 0                                                      |                                           |                                      |  |

| W                   | = 05h                                                                        |                                                                              |             | After Instruction   | Ũ                                                                 |                                           |                                      |  |

| C<br>DC             | = 1<br>= 0                                                                   |                                                                              |             | CNT                 | = 00h                                                             |                                           |                                      |  |

|                     | - 0                                                                          |                                                                              |             | Z                   | = 1                                                               |                                           |                                      |  |

| Example 2:          |                                                                              |                                                                              |             |                     |                                                                   |                                           |                                      |  |

| Before Instrue<br>W | ction<br>= CEh                                                               |                                                                              |             |                     |                                                                   |                                           |                                      |  |

| C                   | = CEn<br>= 0                                                                 |                                                                              |             |                     |                                                                   |                                           |                                      |  |

| DC                  | = 0                                                                          |                                                                              |             |                     |                                                                   |                                           |                                      |  |

| After Instructi     |                                                                              |                                                                              |             |                     |                                                                   |                                           |                                      |  |

| W<br>C              | = 34h<br>= 1                                                                 |                                                                              |             |                     |                                                                   |                                           |                                      |  |

|                     |                                                                              |                                                                              |             |                     |                                                                   |                                           |                                      |  |

## PIC18F97J94 FAMILY

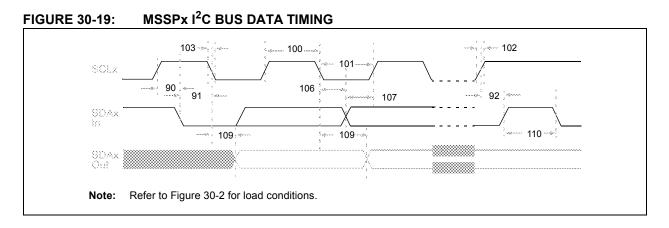

## TABLE 30-37: MSSPx I<sup>2</sup>C BUS DATA REQUIREMENTS

| Param.<br>No. | Symbol                       | Characteristic             |                           | Min.             | Max. | Units                        | Conditions                 |

|---------------|------------------------------|----------------------------|---------------------------|------------------|------|------------------------------|----------------------------|

| 100 Тнідн     | Thigh                        | Clock High                 | 100 kHz mode              | 2(Tosc)(BRG + 1) | _    | _                            |                            |

|               | Time                         | 400 kHz mode               | 2(Tosc)(BRG + 1)          | _                | —    |                              |                            |

|               |                              | 1 MHz mode <sup>(1)</sup>  | 2(Tosc)(BRG + 1)          | —                | _    |                              |                            |

| 101           | TLOW                         | Clock Low                  | 100 kHz mode              | 2(Tosc)(BRG + 1) | —    | _                            |                            |

|               | Time                         | 400 kHz mode               | 2(Tosc)(BRG + 1)          | —                | _    |                              |                            |

|               |                              | 1 MHz mode <sup>(1)</sup>  | 2(Tosc)(BRG + 1)          | —                | _    |                              |                            |

| 102           | 102 TR                       | SDAx and                   | 100 kHz mode              |                  | 1000 | ns                           | CB is specified to be from |

|               | SCLx Rise                    | 400 kHz mode               | 20 + 0.1 Св               | 300              | ns   | 10 to 400 pF                 |                            |

|               |                              | Time                       | 1 MHz mode <sup>(1)</sup> | —                | 300  | ns                           |                            |