Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| D-1-U-                     |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Details                    |                                                                         |

| Product Status             | Obsolete                                                                |

| Core Processor             | HC08                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 3MHz                                                                    |

| Connectivity               | USB                                                                     |

| Peripherals                | LVD, POR, PWM                                                           |

| Number of I/O              | 21                                                                      |

| Program Memory Size        | 8KB (8K x 8)                                                            |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 256 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                               |

| Data Converters            | -                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                          |

| Supplier Device Package    | 28-SOIC                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hc908jb8adw |

| 10.4.6 Commands171                                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10.5 Security                                                                                                                                                                                                                                                                                                                        |

| Section 11. Timer Interface Module (TIM)                                                                                                                                                                                                                                                                                             |

| 11.1 Contents                                                                                                                                                                                                                                                                                                                        |

| 11.2 Introduction                                                                                                                                                                                                                                                                                                                    |

| 11.3 Features                                                                                                                                                                                                                                                                                                                        |

| 11.4 Pin Name Conventions178                                                                                                                                                                                                                                                                                                         |

| 11.5Functional Description17911.5.1TIM Counter Prescaler18111.5.2Input Capture18111.5.3Output Compare18211.5.3.1Unbuffered Output Compare18211.5.3.2Buffered Output Compare18311.5.4Pulse Width Modulation (PWM)18311.5.4.1Unbuffered PWM Signal Generation18411.5.4.2Buffered PWM Signal Generation18511.5.4.3PWM Initialization186 |

| 11.6 Interrupts187                                                                                                                                                                                                                                                                                                                   |

| 11.7 Low-Power Modes       .187         11.7.1 Wait Mode       .188         11.7.2 Stop Mode       .188                                                                                                                                                                                                                              |

| 11.8 TIM During Break Interrupts                                                                                                                                                                                                                                                                                                     |

| 11.9       I/O Signals                                                                                                                                                                                                                                                                                                               |

| 11.10 I/O Registers18911.10.1 TIM Status and Control Register19011.10.2 TIM Counter Registers19211.10.3 TIM Counter Modulo Registers19311.10.4 TIM Channel Status and Control Registers19411.10.5 TIM Channel Registers196                                                                                                           |

${\sf MC68HC908JB8•MC68HC08JB8•MC68HC08JT8} - {\sf Rev.} \ 2.3$

## **Section 1. General Description**

#### 1.1 Contents

| 1.2    | Introduction                                             |

|--------|----------------------------------------------------------|

| 1.3    | Features                                                 |

| 1.4    | MCU Block Diagram                                        |

| 1.5    | Pin Assignments32                                        |

| 1.5.1  | Power Supply Pins (V <sub>DD</sub> , V <sub>SS</sub> )34 |

| 1.5.2  | Voltage Regulator Out (V <sub>REG</sub> )                |

| 1.5.3  | Oscillator Pins (OSC1 and OSC2)                          |

| 1.5.4  | External Reset Pin (RST)35                               |

| 1.5.5  | External Interrupt Pins (IRQ, PTE4/D-)35                 |

| 1.5.6  | Port A Input/Output (I/O) Pins (PTA7/KBA7-PTA0/KBA0)36   |

| 1.5.7  | Port B (I/O) Pins (PTB7–PTB0)                            |

| 1.5.8  | Port C I/O Pins (PTC7–PTC0)                              |

| 1.5.9  | Port D I/O Pins (PTD7–PTD0)                              |

| 1.5.10 | Port E I/O Pins (PTE4/D-, PTE3/D+, PTE2/TCH1,            |

|        | PTE1/TCH0, PTE0/TCLK)36                                  |

#### 1.2 Introduction

The MC68HC908JB8 is a member of the low-cost, high-performance M68HC08 Family of 8-bit microcontroller units (MCUs). All MCUs in the family use the enhanced M68HC08 central processor unit (CPU08) and are available with a variety of modules, memory sizes and types, and package types.

MC68HC908JB8•MC68HC08JB8•MC68HC08JT8 — Rev. 2.3

When the USB module is disabled, the PTE4 and PTE3 pins are general-purpose bidirectional I/O port pins with 10mA sink capability. Each pin is open-drain when configured as an output; and each pin contains a software configurable  $5 \, \mathrm{k} \Omega$  pullup to  $V_{DD}$  when configured as an input. The PTE4 pin can also be enabled to trigger the IRQ interrupt.

When the USB module is enabled, the PTE4/D– and PTE3/D+ pins become the USB module D– and D+ pins. The D– pin contains a software configurable 1.5k $\Omega$  pullup to V<sub>REG</sub>. (See Section 11. Timer Interface Module (TIM), Section 9. Universal Serial Bus Module (USB) and Section 12. Input/Output Ports (I/O).)

Summary of the pin functions are provided in Table 1-1.

**Table 1-1. Summary of Pin Functions**

| PIN NAME         | PIN DESCRIPTION                                                                                     | IN/OUT | VOLTAGE LEVEL                                        |

|------------------|-----------------------------------------------------------------------------------------------------|--------|------------------------------------------------------|

| V <sub>DD</sub>  | Power supply.                                                                                       |        | 4.0 to 5.5 V                                         |

| V <sub>SS</sub>  | Power supply ground.                                                                                | OUT    | 0V                                                   |

| V <sub>REG</sub> | Regulated 3.3V output from MCU.                                                                     | OUT    | V <sub>REG</sub> (3.3V)                              |

| RST              | Reset input; active low. With internal pullup to V <sub>DD</sub> and schmitt trigger input.         | IN/OUT | V <sub>DD</sub>                                      |

| ĪRQ              | External IRQ pin; with programmable internal pullup to $V_{DD}$ and schmitt trigger input.          | IN     | V <sub>DD</sub>                                      |

|                  | Used for mode entry selection.                                                                      | IN     | V <sub>REG</sub> to V <sub>DD</sub> +V <sub>HI</sub> |

| OSC1             | Crystal oscillator input.                                                                           | IN     | V <sub>REG</sub>                                     |

| OSC2             | Crystal oscillator output; inverting of OSC1 signal.                                                |        | V <sub>REG</sub>                                     |

| PTA0/KBA0        | 8-bit general-purpose I/O port.                                                                     | IN/OUT | V <sub>REG</sub>                                     |

| :                | Pins as keyboard interrupts, KBA0-KBA7.                                                             | IN     | V <sub>REG</sub>                                     |

| PTA7/KBA7        | Each pin has programmable internal pullup to $V_{\mbox{\scriptsize REG}}$ when configured as input. | IN     | V <sub>REG</sub>                                     |

|                  | 8-bit general-purpose I/O port.                                                                     | IN/OUT | V <sub>REG</sub>                                     |

| PTB0-PTB7        | Each pin has programmable internal pullup to $V_{\mbox{\scriptsize REG}}$ when configured as input. | IN     | V <sub>REG</sub>                                     |

MC68HC908JB8•MC68HC08JB8•MC68HC08JT8 — Rev. 2.3

## **Section 2. Memory Map**

#### 2.1 Contents

| 2.2 | Introduction | .39 |

|-----|--------------|-----|

| 2.3 | I/O Section  | .41 |

| 2.4 | Monitor ROM  | .41 |

#### 2.2 Introduction

The CPU08 can address 64 Kbytes of memory space. The memory map, shown in **Figure 2-1**, includes:

- 8,192 bytes of user FLASH memory

- 256 bytes of RAM

- 16 bytes of user-defined vectors

- 976 bytes of monitor ROM

## **FLASH Memory**

## Section 5. Configuration Register (CONFIG)

#### 5.1 Contents

| 5.2 | Introduction6          |

|-----|------------------------|

| 5.3 | Functional Description |

#### 5.2 Introduction

This section describes the configuration register (CONFIG). This writeonce-after-reset register controls the following options:

- USB reset

- Low voltage inhibit

- Stop mode recovery time (2048 or 4096 OSCXCLK cycles)

- COP timeout period (2<sup>18</sup> 2<sup>4</sup> or 2<sup>13</sup> 2<sup>4</sup> OSCXCLK cycles)

- STOP instruction

- Computer operating properly module (COP)

## **Oscillator (OSC)**

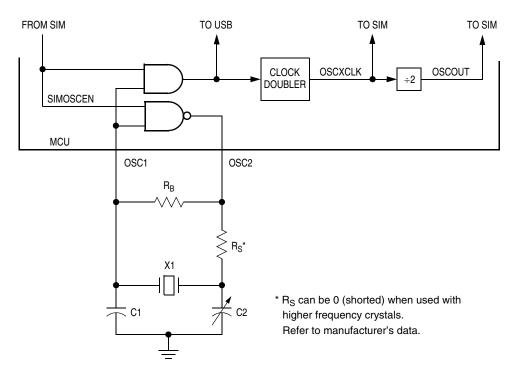

#### 7.3 Oscillator External Connections

In its typical configuration, the oscillator requires five external components. The crystal oscillator is normally connected in a Pierce oscillator configuration, as shown in **Figure 7-1**. This figure shows only the logical representation of the internal components and may not represent actual circuitry. The oscillator configuration uses five components:

- Crystal, X<sub>1</sub>

- Fixed capacitor, C<sub>1</sub>

- Tuning capacitor, C<sub>2</sub> (can also be a fixed capacitor)

- Feedback resistor, R<sub>R</sub>

- Series resistor, R<sub>S</sub> (optional)

Figure 7-1. Oscillator External Connections

Technical Data

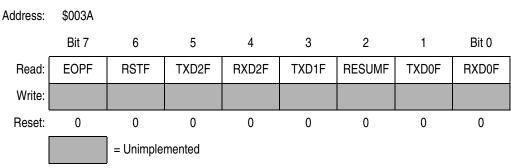

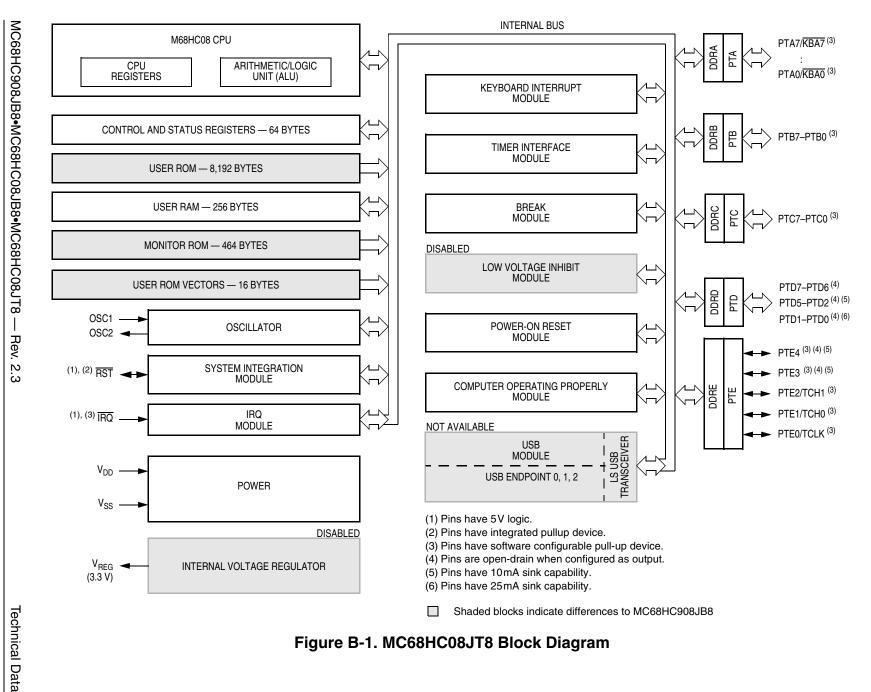

#### 9.8.3 USB Interrupt Register 1

Figure 9-17. USB Interrupt Register 1 (UIR1)

#### EOPF — End-of-Packet Detect Flag

This read-only bit is set when a valid end-of-packet sequence is detected on the D+ and D- lines. Software must clear this flag by writing a logic 1 to the EOPFR bit.

Reset clears this bit. Writing to EOPF has no effect.

- 1 = End-of-packet sequence has been detected

- 0 = End-of-packet sequence has not been detected

#### RSTF — USB Reset Flag

This read-only bit is set when a valid reset signal state is detected on the D+ and D- lines. If the URSTD bit of the configuration register (CONFIG) is clear, this reset detection will generate an internal reset signal to reset the CPU and other peripherals including the USB module. If the URSTD bit is set, this reset detection will generate an USB interrupt. This bit is cleared by writing a logic 1 to the RSTFR bit. This bit also is cleared by a POR reset.

# **NOTE:** The USB bit in the RSR register (see 8.8.2 Reset Status Register) is also a USB reset indicator.

#### TXD2F — Endpoint 2 Data Transmit Flag

This read-only bit is set after the data stored in endpoint 2 transmit buffers has been sent and an ACK handshake packet from the host is received. Once the next set of data is ready in the transmit buffers, software must clear this flag by writing a logic 1 to the TXD2FR bit.

MC68HC908JB8•MC68HC08JB8•MC68HC08JT8 — Rev. 2.3

## **Universal Serial Bus Module (USB)**

#### 9.8.4 USB Interrupt Register 2

Address: \$0018 Bit 7 Bit 0 6 5 4 3 2 1 Read: 0 0 0 0 0 0 0 0 **EOPFR RSTFR** TXD2FR TXD1FR RESUMFR TXD0FR RXD0FR Write: RXD2FR 0 Reset:

Figure 9-18. USB Interrupt Register 2 (UIR2)

#### EOPFR — End-of-Packet Flag Reset

Writing a logic 1 to this write-only bit will clear the EOPF bit if it is set. Writing a logic 0 to the EOPFR has no effect. Reset clears this bit.

#### RSTFR — Clear Reset Indicator Bit

Writing a logic 1 to this write-only bit will clear the RSTF bit if it is set. Writing a logic 0 to the RSTFR has no effect. Reset clears this bit.

#### TXD2FR — Endpoint 2 Transmit Flag Reset

Writing a logic 1 to this write-only bit will clear the TXD2F bit if it is set. Writing a logic 0 to TXD2FR has no effect. Reset clears this bit.

#### RXD2FR — Endpoint 2 Receive Flag Reset

Writing a logic 1 to this write-only bit will clear the RXD2F bit if it is set. Writing a logic 0 to RXD2FR has no effect. Reset clears this bit.

#### TXD1FR — Endpoint 1 Transmit Flag Reset

Writing a logic 1 to this write-only bit will clear the TXD1F bit if it is set. Writing a logic 0 to TXD1FR has no effect. Reset clears this bit.

#### RESUMFR — Resume Flag Reset

Writing a logic 1 to this write-only bit will clear the RESUMF bit if it is set. Writing to RESUMFR has no effect. Reset clears this bit.

#### TXD0FR — Endpoint 0 Transmit Flag Reset

Writing a logic 1 to this write-only bit will clear the TXD0F bit if it is set. Writing a logic 0 to TXD0FR has no effect. Reset clears this bit.

#### RXD0FR — Endpoint 0 Receive Flag Reset

Writing a logic 1 to this write-only bit will clear the RXD0F bit if it is set. Writing a logic 0 to RXD0FR has no effect. Reset clears this bit.

**Technical Data**

### 9.9 USB Interrupts

The USB module is capable of generating interrupts and causing the CPU to execute the USB interrupt service routine. There are three types of USB interrupts:

- End-of-transaction interrupts signify either a completed transaction receive or transmit transaction.

- Resume interrupts signify that the USB bus is reactivated after having been suspended.

- End-of-packet interrupts signify that a low-speed end-of-packet signal was detected.

All USB interrupts share the same interrupt vector. Firmware is responsible for determining which interrupt is active.

#### 9.9.1 USB End-of-Transaction Interrupt

There are five possible end-of-transaction interrupts:

- Endpoint 0 or 2 receive

- Endpoint 0, 1 or 2 transmit

End-of-transaction interrupts occur as detailed in the following sections.

## Timer Interface Module (TIM)

| Addr.  | Register Name                     |        | Bit 7 | 6         | 5         | 4          | 3             | 2      | 1    | Bit 0        |

|--------|-----------------------------------|--------|-------|-----------|-----------|------------|---------------|--------|------|--------------|

|        | •                                 | Read:  | TOF   | TOIL      | TOTOD     | 0          | 0             | DOO    | D04  | DOO          |

| \$000A |                                   | Write: | 0     | TOIE      | TSTOP     | TRST       |               | PS2    | PS1  | PS0          |

|        | (TSC)                             | Reset: | 0     | 0         | 1         | 0          | 0             | 0      | 0    | 0            |

|        |                                   | Read:  | Bit15 | Bit14     | Bit13     | Bit12      | Bit11         | Bit10  | Bit9 | Bit8         |

| \$000C | TIM Counter Register High (TCNTH) | Write: |       |           |           |            |               |        |      |              |

|        | (1.21111)                         | Reset: | 0     | 0         | 0         | 0          | 0             | 0      | 0    | 0            |

|        |                                   | Read:  | Bit7  | Bit6      | Bit5      | Bit4       | Bit3          | Bit2   | Bit1 | Bit0         |

| \$000D | TIM Counter Register Low (TCNTL)  | Write: |       |           |           |            |               |        |      |              |

|        | ,                                 | Reset: | 0     | 0         | 0         | 0          | 0             | 0      | 0    | 0            |

|        | TIM Counter Modulo                | Read:  | Bit15 | Bit14     | Bit13     | Bit12      | Bit11         | Bit10  | Bit9 | Bit8         |

| \$000E | Register High                     | Write: | DILIO | DIL14     | DILIO     | DILIZ      | DILIT         | DILIU  | DIIB | DILO         |

|        | (TMODH)                           | Reset: | 1     | 1         | 1         | 1          | 1             | 1      | 1    | 1            |

|        | TIM Counter Modulo                | Read:  | Bit7  | Bit6      | Bit5      | Bit4       | Bit3          | Bit2   | Bit1 | Bit0         |

| \$000F | Register Low                      | Write: | DILI  | Bito      | Dito      | DIL4       | Dito          | DILE   | Ditt | Dito         |

|        | (TMODL)                           | Reset: | 1     | 1         | 1         | 1          | 1             | 1      | 1    | 1            |

|        | TIM Channel 0 Status and          | Read:  | CH0F  | CH0IE     | MS0B      | MS0A       | ELS0B         | ELS0A  | TOV0 | CH0MAX       |

| \$0010 | Control Register                  | Write: | 0     | OHOL      | WOOD      | WOOA       | LLOOD         | LLOOA  | 1000 | OT IOIVII OX |

|        | (TSC0)                            | Reset: | 0     | 0         | 0         | 0          | 0             | 0      | 0    | 0            |

|        | TIM Channel 0                     | Read:  | Bit15 | Bit14     | Bit13     | Bit12      | Bit11         | Bit10  | Bit9 | Bit8         |

| \$0011 | Register High<br>(TCH0H)          | Write: | DitTO | Ditt      | Ditto     | DICTE      | Ditt          | DitTo  | Dito | Dito         |

|        | (TOHOH)                           | Reset: |       |           | lr        | ndetermina | te after res  | et     |      | ,            |

|        | TIM Channel 0                     | Read:  | Bit7  | Bit6      | Bit5      | Bit4       | Bit3          | Bit2   | Bit1 | Bit0         |

| \$0012 | Register Low<br>(TCH0L)           | Write: | Diti  | Dit/ Dito | DITO DITO | Ditt       | DIL4 DILO     | DILZ   | DILI | Bito         |

|        | (TOHOL)                           | Reset: |       |           | lr        | ndetermina | te after rese | et     |      |              |

|        | TIM Channel 1 Status and          | Read:  | CH1F  | - CH1IE   | 0         | MS1A       | ELS1B         | ELS1A  | TOV1 | CH1MAX       |

| \$0013 | Control Register<br>(TSC1)        | Write: | 0     | 0.7712    |           |            |               | 220171 |      |              |

|        | (1301)                            | Reset: | 0     | 0         | 0         | 0          | 0             | 0      | 0    | 0            |

|        |                                   |        |       | = Unimp   | lemented  |            |               |        |      |              |

Figure 11-2. TIM I/O Register Summary

Technical Data

## Section 13. External Interrupt (IRQ)

#### 13.1 Contents

| 13.2 | Introduction                       | .219 |

|------|------------------------------------|------|

| 13.3 | Features                           | .219 |

| 13.4 | Functional Description             | .220 |

| 13.5 | IRQ Pin                            | .222 |

| 13.6 | PTE4/D- Pin                        | .223 |

| 13.7 | IRQ Module During Break Interrupts | .223 |

| 13.8 | IRQ Status and Control Register    | .224 |

| 13.9 | IRQ Option Control Register        | .225 |

#### 13.2 Introduction

The IRQ module provides two external interrupt inputs: one dedicated IRQ pin and one shared port pin, PTE4/D-.

#### 13.3 Features

Features of the IRQ module include:

- Two external interrupt pins, IRQ (5V) and PTE4/D- (5V)

- IRQ interrupt control bits

- Hysteresis buffer

- Programmable edge-only or edge and level interrupt sensitivity

- Automatic interrupt acknowledge

- Low leakage IRQ pin for external RC wake up input

- Selectable internal pullup resistor

MC68HC908JB8•MC68HC08JB8•MC68HC08JT8 — Rev. 2.3

## **Keyboard Interrupt Module (KBI)**

## 14.5 Functional Description

Writing to the KBIE7–KBIE0 bits in the keyboard interrupt enable register independently enables or disables each port A pin as a keyboard interrupt pin. Enabling a keyboard interrupt pin also enables its internal pullup device. A logic 0 applied to an enabled keyboard interrupt pin latches a keyboard interrupt request.

A keyboard interrupt is latched when one or more keyboard pins goes low after all were high. The MODEK bit in the keyboard status and control register controls the triggering mode of the keyboard interrupt.

- If the keyboard interrupt is edge-sensitive only, a falling edge on a keyboard pin does not latch an interrupt request if another keyboard pin is already low.

- If the keyboard interrupt is falling edge- and low level-sensitive, an interrupt request is present as long as any keyboard pin is low.

**NOTE:** To prevent losing an interrupt request on one pin because another pin is still low, software can disable the latter pin while it is low.

If the MODEK bit is set, the keyboard interrupt pins are both falling edgeand low level-sensitive, and both of the following actions must occur to clear a keyboard interrupt request:

• Vector fetch or software clear — A vector fetch generates an interrupt acknowledge signal to clear the interrupt request. Software may generate the interrupt acknowledge signal by writing a logic 1 to the ACKK bit in the keyboard status and control register (KBSCR). The ACKK bit is useful in applications that poll the keyboard interrupt pins and require software to clear the keyboard interrupt request. Writing to the ACKK bit prior to leaving an interrupt service routine also can prevent spurious interrupts due to noise. Setting ACKK does not affect subsequent transitions on the keyboard interrupt pins. A falling edge that occurs after writing to the ACKK bit latches another interrupt request. If the keyboard interrupt mask bit, IMASKK, is clear, the CPU loads the program counter with the vector address at locations \$FFF0 and \$FFF1.

## **Keyboard Interrupt Module (KBI)**

- 3. Write to the ACKK bit in the keyboard status and control register to clear any false interrupts.

- 4. Clear the IMASKK bit.

An interrupt signal on an edge-triggered pin can be acknowledged immediately after enabling the pin. An interrupt signal on an edge- and level-triggered interrupt pin must be acknowledged after a delay that depends on the external load.

Another way to avoid a false interrupt:

- Configure the keyboard pins as outputs by setting the appropriate DDRA bits in data direction register A.

- 2. Write logic 1s to the appropriate port A data register bits.

- 3. Enable the KBI pins by setting the appropriate KBIEx bits in the keyboard interrupt enable register.

#### 14.7 Low-Power Modes

The WAIT and STOP instructions put the MCU in low-power consumption standby modes.

#### 14.7.1 Wait Mode

The keyboard module remains active in wait mode. Clearing the IMASKK bit in the keyboard status and control register enables keyboard interrupt requests to bring the MCU out of wait mode.

#### **14.7.2 Stop Mode**

The keyboard module remains active in stop mode. Clearing the IMASKK bit in the keyboard status and control register enables keyboard interrupt requests to bring the MCU out of stop mode.

## **Section 20. Ordering Information**

#### 20.1 Contents

| 20.2 | Introduction     | 267 |

|------|------------------|-----|

| 20.3 | MC Order Numbers | 67  |

### 20.2 Introduction

This section contains ordering numbers for the MC68HC908JB8.

#### 20.3 MC Order Numbers

**Table 20-1. MC Order Numbers**

| MC Order Number             | C Order Number Package |             | Compliance       |  |

|-----------------------------|------------------------|-------------|------------------|--|

| MC68HC908JB8JP              | 20-pin PDIP            | 0 to +70 °C |                  |  |

| MC68HC908JB8JDW             | 20-pin SOIC            | 0 to +70 °C |                  |  |

| MC68HC908JB8ADW 28-pin SOIC |                        | 0 to +70 °C | _                |  |

| MC68HC908JB8FB              | 44-pin QFP             | 0 to +70 °C |                  |  |

| MC68HC908JB8JPE             | 20-pin PDIP            | 0 to +70 °C |                  |  |

| MC908JB8JDWE                | 20-pin SOIC            | 0 to +70 °C | Pb-Free and RoHS |  |

| MC908JB8ADWE 28-pin SOIC    |                        | 0 to +70 °C | compliant.       |  |

| MC908JB8FBE                 | 44-pin QFP             | 0 to +70 °C |                  |  |

MC68HC908JB8•MC68HC08JB8•MC68HC08JT8 — Rev. 2.3

#### NOTES:

- 1.  $V_{DD} = 4.0$  to 5.5 Vdc,  $V_{SS} = 0$  Vdc,  $T_A = T_L$  to  $T_H$ , unless otherwise noted.

- 2. Typical values reflect average measurements at midpoint of voltage range, 25 °C only.

- 3. Run (operating)  $I_{DD}$  measured using external square wave clock source ( $f_{XCLK} = 6$  MHz). All inputs 0.2 V from rail. No dc loads. Less than 100 pF on all outputs.  $C_L = 20$  pF on OSC2. All ports configured as inputs. OSC2 capacitance linearly affects run  $I_{DD}$ . Measured with all modules enabled.

- 4. Wait  $I_{DD}$  measured using external square wave clock source ( $f_{XCLK}$  = 6 MHz); all inputs 0.2 V from rail; no dc loads; less than 100 pF on all outputs.  $C_L$  = 20 pF on OSC2; 15 k $\Omega$  ± 5% termination resistors on D+ and D- pins; all ports configured as inputs; OSC2 capacitance linearly affects wait  $I_{DD}$

- 5. STOP I<sub>DD</sub> measured with USB in suspend mode; OSC1 grounded; transceiver pullup resistor of 1.5 k $\Omega$  ± 5% between V<sub>REG</sub> and D– pins and 15 k $\Omega$  ± 5% termination resistor on D+ pin; no port pins sourcing current.

- 6. Maximum is highest voltage that POR is guaranteed.

- 7. If minimum  $V_{REG}$  is not reached before the internal POR reset is released,  $\overline{RST}$  must be driven low externally until minimum  $V_{REG}$  is reached.

#### A.7.2 Memory Characteristics

| Characteristic             | Symbol    | Min | Max | Unit |

|----------------------------|-----------|-----|-----|------|

| RAM data retention voltage | $V_{RDR}$ | 1.3 | _   | V    |

Notes:

Since MC68HC08JB8 is a ROM device, FLASH memory electrical characteristics do not apply.

#### A.8 MC68HC08JB8 Order Numbers

These part numbers are generic numbers only. To place an order, ROM code must be submitted to the ROM Processing Center (RPC).

Table A-2. MC68HC08JB8 Order Numbers

| MC Order Number | Package     | Operating<br>Temperature Range |

|-----------------|-------------|--------------------------------|

| MC68HC08JB8JP   | 20-pin PDIP | 0 to +70 °C                    |

| MC68HC08JB8JDW  | 20-pin SOIC | 0 to +70 °C                    |

| MC68HC08JB8ADW  | 28-pin SOIC | 0 to +70 °C                    |

| MC68HC08JB8FB   | 44-pin QFP  | 0 to +70 °C                    |

MC68HC908JB8•MC68HC08JB8•MC68HC08JT8 — Rev. 2.3

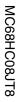

## Appendix B. MC68HC08JT8

### **B.1 Contents**

| B.2    | Introduction                  |

|--------|-------------------------------|

| B.3    | MCU Block Diagram             |

| B.4    | Memory Map                    |

| B.5    | Power Supply Pins             |

| B.6    | Reserved Register Bit281      |

| B.7    | Reserved Registers            |

| B.8    | Monitor ROM                   |

| B.9    | Universal Serial Bus Module   |

| B.10   | Low-Voltage Inhibit Module282 |

| B.11   | Electrical Specifications     |

| B.11.  | 3-                            |

| B.11.2 | 1 3 3                         |

| B.11.  |                               |

| B.11.4 | 4 Control Timing              |

| B.11.  | Memory Characteristics        |

| B.12   | MC68HC08JT8 Order Numbers     |

MC68HC908JB8•MC68HC08JB8•MC68HC08JT8 — Rev. 2.3

Figure B-1. MC68HC08JT8 Block Diagram

#### **B.8 Monitor ROM**

The monitor program (monitor ROM: \$FE10-\$FFDF) on the MC68HC08JT8 is for device testing only. \$FC00-\$FDFF are unused.

#### **B.9 Universal Serial Bus Module**

The USB module is designed for operation with  $V_{DD} = 4V$  to 5.5V, therefore, it should not be used on the MC68HC08JT8 device. To further reduce current consumption in stop mode, set the SUSPND bit in the USB interrupt register 0 (UIR0) to logic 1. Other USB registers should be left in their default state.

## **B.10 Low-Voltage Inhibit Module**

The LVI module is disabled on the MC68HC08JT8.

## **B.11 Electrical Specifications**

Electrical specifications for the MC68HC908JB8 apply to the MC68HC08JT8, except for the parameters indicated below.

### **B.11.1 Absolute Maximum Ratings**

| Characteristic <sup>(1)</sup>                                         | Symbol            | Value                                   | Unit |

|-----------------------------------------------------------------------|-------------------|-----------------------------------------|------|

| Supply voltage                                                        | $V_{DD}$          | -0.3 to +3.9                            | V    |

| Input voltage                                                         | V <sub>IN</sub>   | $V_{SS} - 0.3 \text{ to } V_{DD} + 0.3$ | V    |

| Maximum current per pin excluding V <sub>DD</sub> and V <sub>SS</sub> | I                 | ± 25                                    | mA   |

| Storage temperature                                                   | T <sub>STG</sub>  | -55 to +150                             | °C   |

| Maximum current of PTD0/1 (20-pin package)                            | I <sub>OL</sub>   | -15 to +30                              | mA   |

| Maximum current out of V <sub>SS</sub>                                | I <sub>MVSS</sub> | 100                                     | mA   |

| Maximum current into V <sub>DD</sub>                                  | I <sub>MVDD</sub> | 100                                     | mA   |

#### NOTES:

1. Voltages referenced to V<sub>SS</sub>.

**Technical Data**

#### MC68HC08JT8

#### NOTES:

- 1.  $V_{DD}$  = 2.0 to 3.6 Vdc,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$ , unless otherwise noted.

- 2. Typical values reflect average measurements at 3V, 25 °C only.

- 3. In LDD mode, the specified  $I_{OL}$  is achieved when the external pullup voltage is equal to or higher than the voltage:  $V_{OL}$  + voltage dropped across LED.

- 4. Run (operating)  $I_{DD}$  measured using external square wave clock source ( $f_{XCLK} = 6$  MHz). All inputs 0.2 V from rail. No dc loads. Less than 100 pF on all outputs.  $C_L = 20$  pF on OSC2. All ports configured as inputs. OSC2 capacitance linearly affects run  $I_{DD}$ . Measured with all modules enabled.

- 5. Wait I<sub>DD</sub> measured using external square wave clock source (f<sub>XCLK</sub> = 6 MHz). All inputs 0.2 V from rail. No dc loads. Less than 100 pF on all outputs. C<sub>I</sub> = 20 pF on OSC2. All ports configured as inputs. OSC2 capacitance linearly affects wait I<sub>DD</sub>.

- 6. Stop IDD measured with OSC1 grounded; no port pins sourcing current.

- 7. Maximum is highest voltage that POR is guaranteed.

#### **B.11.4 Control Timing**

| Characteristic                                                 | Symbol          | Min    | Max        | Unit       |

|----------------------------------------------------------------|-----------------|--------|------------|------------|

| Internal operating frequency $V_{DD} = 2.0 V$ $V_{DD} = 3.0 V$ | f <sub>OP</sub> | _<br>_ | 2.5<br>3.0 | MHz<br>MHz |

#### **B.11.5 Memory Characteristics**

| Characteristic             | Symbol    | Min | Max | Unit |

|----------------------------|-----------|-----|-----|------|

| RAM data retention voltage | $V_{RDR}$ | 1.3 | _   | V    |

NOTES: Since MC68HC08JT8 is a ROM device, FLASH memory electrical characteristics do not apply.

#### **B.12 MC68HC08JT8 Order Numbers**

These part numbers are generic numbers only. To place an order, ROM code must be submitted to the ROM Processing Center (RPC).

Table B-2. MC68HC08JT8 Order Numbers

| MC Order Number | Package     | Operating<br>Temperature Range | Compliance                  |

|-----------------|-------------|--------------------------------|-----------------------------|

| MC68HC08JT8ADW  | 28-pin SOIC | 0 to +70 °C                    | _                           |

| MC68HC08JT8FB   | 44-pin QFP  | 0 to +70 °C                    | _                           |

| MC68HC08JT8FBE  | 44-pin QFP  | 0 to +70 °C                    | Pb-Free and RoHS compliant. |

**Technical Data**

MC68HC908JB8•MC68HC08JB8•MC68HC08JT8 — Rev. 2.3

284 MC68HC08JT8 Freescale Semiconductor