Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | HC08                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 3MHz                                                                   |

| Connectivity               | USB                                                                    |

| Peripherals                | LVD, POR, PWM                                                          |

| Number of I/O              | 13                                                                     |

| Program Memory Size        | 8KB (8K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 256 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                              |

| Data Converters            | -                                                                      |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                        |

| Mounting Type              | Through Hole                                                           |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                |

| Supplier Device Package    | 20-DIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hc908jb8jp |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Technical Data — MC68HC908JB8•MC68HC08JB8•MC68HC08JT8

# **List of Sections**

| Section 1. General Description                   |

|--------------------------------------------------|

| Section 2. Memory Map39                          |

| Section 3. Random-Access Memory (RAM)51          |

| Section 4. FLASH Memory53                        |

| Section 5. Configuration Register (CONFIG)65     |

| Section 6. Central Processor Unit (CPU)69        |

| Section 7. Oscillator (OSC)89                    |

| Section 8. System Integration Module (SIM)93     |

| Section 9. Universal Serial Bus Module (USB)117  |

| <b>Section 10. Monitor ROM (MON)</b>             |

| Section 11. Timer Interface Module (TIM)         |

| Section 12. Input/Output Ports (I/O)199          |

| Section 13. External Interrupt (IRQ)219          |

| Section 14. Keyboard Interrupt Module (KBI)227   |

| Section 15. Computer Operating Properly (COP)237 |

| Section 16. Low Voltage Inhibit (LVI)243         |

| Section 17. Break Module (BREAK)245              |

| Section 18. Electrical Specifications253         |

| Section 19. Mechanical Specifications            |

| Section 20. Ordering Information267              |

| Appendix A. MC68HC08JB8269                       |

| Appendix B. MC68HC08JT8                          |

MC68HC908JB8•MC68HC08JB8•MC68HC08JT8 — Rev. 2.3

## **General Description**

### 1.5.6 Port A Input/Output (I/O) Pins (PTA7/KBA7-PTA0/KBA0)

PTA7/KBA7–PTA0/KBA0 are general-purpose bidirectional I/O port pins. (See Section 12. Input/Output Ports (I/O).) Each pin contains a software configurable pullup device to V<sub>REG</sub> when the pin is configured as an input. (See 12.8 Port Options.) Each pin can also be programmed as an external keyboard interrupt pin. (See Section 14. Keyboard Interrupt Module (KBI).)

### 1.5.7 Port B (I/O) Pins (PTB7-PTB0)

PTB7–PTB0 are general-purpose bidirectional I/O port pins. Each pin contains a software configurable pullup device to  $V_{REG}$  when the pin is configured as an input. (See 12.8 Port Options.)

### 1.5.8 Port C I/O Pins (PTC7-PTC0)

PTC7–PTC0 are general-purpose bidirectional I/O port pins. (See Section 12. Input/Output Ports (I/O).) Each pin contains a software configurable pullup device to  $V_{REG}$  when the pin is configured as an input. (See 12.8 Port Options.)

#### 1.5.9 Port D I/O Pins (PTD7-PTD0)

PTD7–PTD0 are general-purpose bidirectional I/O port pins; open-drain when configured as output. (See Section 12. Input/Output Ports (I/O).) PTD5–PTD2 are software configurable to be 10mA sink pins for direct LED connections. PTD1–PTD0 are software configurable to be 25mA sink pins for direct infrared LED connections. (See 12.8 Port Options.)

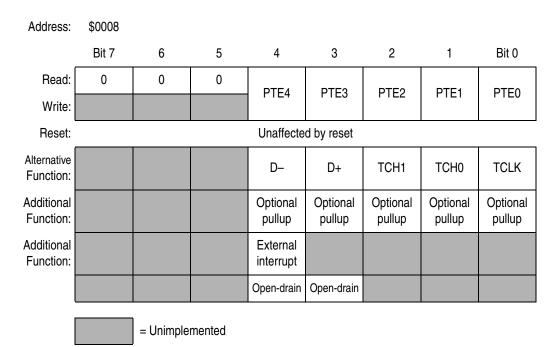

#### 1.5.10 Port E I/O Pins (PTE4/D-, PTE3/D+, PTE2/TCH1, PTE1/TCH0, PTE0/TCLK)

Port E is a 5-bit special function port that shares two of its pins with the USB module and three of its pins with the timer interface module.

Each PTE2-PTE0 pin contains a software configurable pullup device to  $V_{\mbox{\scriptsize REG}}$  when the pin is configured as an input or output.

**Technical Data**

# **General Description**

**Table 1-1. Summary of Pin Functions**

| PIN NAME                            | PIN DESCRIPTION                                                                                     | IN/OUT    | VOLTAGE LEVEL                                           |  |  |

|-------------------------------------|-----------------------------------------------------------------------------------------------------|-----------|---------------------------------------------------------|--|--|

|                                     | 8-bit general-purpose I/O port.                                                                     | IN/OUT    | V <sub>REG</sub>                                        |  |  |

| PTC0-PTC7                           | Each pin has programmable internal pullup to $V_{\mbox{\scriptsize REG}}$ when configured as input. | IN        | V <sub>REG</sub>                                        |  |  |

|                                     | 8-bit general-purpose I/O port; open-drain when configured as output.                               | IN<br>OUT | V <sub>REG</sub><br>V <sub>REG</sub> or V <sub>DD</sub> |  |  |

| PTD0-PTD7                           | PTD0-PTD1 have configurable 25mA sink for infrared LED.                                             | OUT       | V <sub>REG</sub> or V <sub>DD</sub>                     |  |  |

|                                     | PTD2-PTD5 have configurable 10mA sink for LED.                                                      | OUT       | V <sub>REG</sub> or V <sub>DD</sub>                     |  |  |

| PTE0/TCLK<br>PTE1/TCH0<br>PTE2/TCH1 | PTE0-PTE2 are general-purpose I/O pins.                                                             | IN/OUT    | V <sub>REG</sub>                                        |  |  |

|                                     | PTE0-PTE2 have programmable internal pullup to V <sub>REG</sub> when configured as input or output. | IN/OUT    | V <sub>REG</sub>                                        |  |  |

|                                     | PTE0 as TCLK of timer interface module.                                                             | IN        | V <sub>REG</sub>                                        |  |  |

|                                     | PTE1 as TCH0 of timer interface module.                                                             | IN/OUT    | V <sub>REG</sub>                                        |  |  |

|                                     | PTE2 as TCH1 of timer interface module.                                                             | IN/OUT    | V <sub>REG</sub>                                        |  |  |

|                                     | PTE3-PTE4 are general-purpose I/O pins; open-drain when configured as output.                       | IN<br>OUT | V <sub>DD</sub><br>V <sub>REG</sub> or V <sub>DD</sub>  |  |  |

| PTE3/D+                             | PTE3–PTE4 have programmable internal pullup to $V_{DD}$ when configured as input.                   | IN        | V <sub>DD</sub>                                         |  |  |

| PTE4/D-                             | PTE3 as D+ of USB module.                                                                           | IN/OUT    | V <sub>REG</sub>                                        |  |  |

|                                     | PTE4 as D- of USB module.                                                                           | IN/OUT    | V <sub>REG</sub>                                        |  |  |

|                                     | PTE4 as additional IRQ interrupt.                                                                   | IN        | V <sub>DD</sub>                                         |  |  |

**Technical Data**

#### 2.3 I/O Section

Addresses \$0000–\$003F, shown in **Figure 2-2**, contain most of the control, status, and data registers. Additional I/O registers have these addresses:

- \$FE00; break status register, BSR

- \$FE01; reset status register, RSR

- \$FE02; reserved

- \$FE03; break flag control register, BFCR

- \$FE04; interrupt status register 1, INT1

- \$FE05; reserved

- \$FE06; reserved

- \$FE07; reserved

- \$FE08; FLASH control register, FLCR

- \$FE09; FLASH block protect register, FLBPR

- \$FE0A; reserved

- \$FE0B; reserved

- \$FE0C; break Address Register High, BRKH

- \$FE0D; break Address Register Low, BRKL

- \$FE0E; break status and control register, BRKSCR

- \$FFFF; COP control register, COPCTL

#### 2.4 Monitor ROM

The 512 bytes at addresses \$FC00–\$FDFF and 464 bytes at addresses \$FE10–\$FFDF are reserved ROM addresses that contain the instructions for the monitor functions. (See **Section 10. Monitor ROM (MON)**.)

# Central Processor Unit (CPU)

Table 6-1. Instruction Set Summary (Sheet 5 of 9)

| Source                                                                                         | Operation                           | Description                                                                                                                                                             | Effect on CCR |   |   |           |           |    | Address<br>Mode                                     | əpc                                              | Operand                                         | es                                   |

|------------------------------------------------------------------------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---|---|-----------|-----------|----|-----------------------------------------------------|--------------------------------------------------|-------------------------------------------------|--------------------------------------|

| Form                                                                                           |                                     | ·                                                                                                                                                                       | ٧             | Н | I | N         | N Z       |    | Addı                                                | Opcode                                           | Ope                                             | Cycles                               |

| EOR #opr<br>EOR opr<br>EOR opr<br>EOR opr,X<br>EOR opr,X<br>EOR ,X<br>EOR opr,SP<br>EOR opr,SP | Exclusive OR M with A               | A ← (A ⊕ M)                                                                                                                                                             | 0             | _ |   | \$        | \$        | _  | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A8<br>B8<br>C8<br>D8<br>E8<br>F8<br>9EE8<br>9ED8 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| INC opr<br>INCA<br>INCX<br>INC opr,X<br>INC ,X<br>INC opr,SP                                   | Increment                           | $M \leftarrow (M) + 1$<br>$A \leftarrow (A) + 1$<br>$X \leftarrow (X) + 1$<br>$M \leftarrow (M) + 1$<br>$M \leftarrow (M) + 1$<br>$M \leftarrow (M) + 1$                | \$            | _ | _ | \$        | \$        | _  | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3C<br>4C<br>5C<br>6C<br>7C<br>9E6C               | dd<br>ff                                        | 4<br>1<br>1<br>4<br>3<br>5           |

| JMP opr<br>JMP opr<br>JMP opr,X<br>JMP opr,X<br>JMP ,X                                         | Jump                                | PC ← Jump Address                                                                                                                                                       | _             | _ | _ | _         | _         | _  | DIR<br>EXT<br>IX2<br>IX1<br>IX                      | BC<br>CC<br>DC<br>EC<br>FC                       | dd<br>hh II<br>ee ff<br>ff                      | 2<br>3<br>4<br>3<br>2                |

| JSR opr<br>JSR opr<br>JSR opr,X<br>JSR opr,X<br>JSR ,X                                         | Jump to Subroutine                  | PC $\leftarrow$ (PC) + $n$ ( $n$ = 1, 2, or 3)<br>Push (PCL); SP $\leftarrow$ (SP) – 1<br>Push (PCH); SP $\leftarrow$ (SP) – 1<br>PC $\leftarrow$ Unconditional Address | _             | _ | _ | _         | _         | _  | DIR<br>EXT<br>IX2<br>IX1<br>IX                      | BD<br>CD<br>DD<br>ED<br>FD                       | dd<br>hh II<br>ee ff<br>ff                      | 4<br>5<br>6<br>5<br>4                |

| LDA #opr<br>LDA opr<br>LDA opr<br>LDA opr,X<br>LDA opr,X<br>LDA ,X<br>LDA opr,SP<br>LDA opr,SP | Load A from M                       | A ← (M)                                                                                                                                                                 | 0             | _ | _ | <b>\$</b> | <b>\$</b> | _  | IMM DIR EXT IX2 IX1 IX SP1 SP2                      | A6<br>B6<br>C6<br>D6<br>E6<br>F6<br>9EE6         | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff | 2 3 4 4 3 2 4 5                      |

| LDHX #opr<br>LDHX opr                                                                          | Load H:X from M                     | H:X ← (M:M + 1)                                                                                                                                                         | 0             | _ | - | \$        | \$        | -  | IMM<br>DIR                                          | 45<br>55                                         | ii jj<br>dd                                     | 3 4                                  |

| LDX #opr<br>LDX opr<br>LDX opr<br>LDX opr,X<br>LDX opr,X<br>LDX ,X<br>LDX opr,SP<br>LDX opr,SP | Load X from M                       | X ← (M)                                                                                                                                                                 | 0             | _ | _ | <b>\$</b> | \$        | _  | IMM DIR EXT IX2 IX1 IX SP1 SP2                      | AE<br>BE<br>CE<br>DE<br>EE<br>FE<br>9EEE<br>9EDE | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| LSL opr<br>LSLA<br>LSLX<br>LSL opr,X<br>LSL ,X<br>LSL opr,SP                                   | Logical Shift Left<br>(Same as ASL) | D 0 b7 b0                                                                                                                                                               | \$            | _ | _ | \$        | \$        | \$ | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 38<br>48<br>58<br>68<br>78<br>9E68               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

**Technical Data**

# Central Processor Unit (CPU)

Table 6-1. Instruction Set Summary (Sheet 9 of 9)

|       | urce<br>orm | Operation                               | Description           |              |      | v I   | Effe<br>C<br>H I | CF   | l I   | С    | - <u> </u> | Address<br>Mode |     | Opcode  | Operand | Cycles |

|-------|-------------|-----------------------------------------|-----------------------|--------------|------|-------|------------------|------|-------|------|------------|-----------------|-----|---------|---------|--------|

| A     | Accumu      | lator                                   |                       | n            | Any  | bit   |                  |      |       |      |            |                 |     |         |         |        |

| C     | Carry/bo    |                                         |                       | opr          | Ope  |       | l (on            | e c  | r tw  | o b  | vtes       | .)              |     |         |         |        |

| CCR   |             | n code register                         |                       | PC           | Proc |       | •                |      |       |      | ,          | ,               |     |         |         |        |

| dd    |             | ddress of operand                       |                       | PCH          | Proc | gram  | cou              | inte | r hi  | gh   | byte       |                 |     |         |         |        |

| dd rr | Direct ac   | ddress of operand and relative offset   | of branch instruction | PCL          | Prog | gram  | cou              | nte  | r lo  | w t  | yte        |                 |     |         |         |        |

| DD    | Direct to   | direct addressing mode                  |                       | REL          | Rela | ative | addı             | res  | sing  | g m  | ode        |                 |     |         |         |        |

| DIR   | Direct ac   | ddressing mode                          |                       | rel          |      |       |                  |      |       |      |            | offset          | by  | /te     |         |        |

| DIX+  | Direct to   | indexed with post increment address     | sing mode             | rr           | Rela | ative | prog             | gra  | n c   | our  | iter (     | offset          | by  | ⁄te     |         |        |

| ee ff | High and    | d low bytes of offset in indexed, 16-bi | t offset addressing   | SP1          | Stac | k po  | inter            | r, 8 | -bit  | offs | set a      | ddres           | ssi | ng mode | Э       |        |

| EXT   | Extende     | d addressing mode                       |                       | SP2          | Stac | k po  | inter            | r 16 | 3-bit | off  | fset       | addre           | ess | ing mod | le      |        |

| ff    | Offset by   | yte in indexed, 8-bit offset addressing | ]                     | SP           | Stac | k po  | inter            | r    |       |      |            |                 |     |         |         |        |

| Н     | Half-carr   | ry bit                                  |                       | U            | Und  | efine | ed               |      |       |      |            |                 |     |         |         |        |

| Н     | Index re    | gister high byte                        |                       | V            | Ove  | rflow | bit /            |      |       |      |            |                 |     |         |         |        |

| hh II | •           | d low bytes of operand address in ext   | tended addressing     | Χ            | Inde | x re  | giste            | r lo | w b   | yte  | ;          |                 |     |         |         |        |

| I     | Interrupt   |                                         |                       | Z            | Zero |       |                  |      |       |      |            |                 |     |         |         |        |

| ii    |             | ite operand byte                        |                       | &            | Logi |       |                  |      |       |      |            |                 |     |         |         |        |

| IMD   | Immedia     | te source to direct destination addre   | ssing mode            | ı            | Logi | cal ( | DR               |      |       |      |            |                 |     |         |         |        |

| IMM   | Immedia     | ite addressing mode                     |                       | $\oplus$     | Logi | cal E | EXCI             | LU   | SIV   | ΕC   | )R         |                 |     |         |         |        |

| INH   | Inherent    | addressing mode                         |                       | ()           | Con  | tents | s of             |      |       |      |            |                 |     |         |         |        |

| IX    | Indexed,    | no offset addressing mode               |                       | -( )         | Neg  | atior | ı (tw            | o's  | cor   | npl  | eme        | nt)             |     |         |         |        |

| IX+   | Indexed,    | , no offset, post increment addressing  | g mode                | #            | lmm  | edia  | te va            | alu  | Э     |      |            |                 |     |         |         |        |

| IX+D  | Indexed     | with post increment to direct address   | sing mode             | **           | Sign | exte  | end              |      |       |      |            |                 |     |         |         |        |

| IX1   | Indexed,    | 8-bit offset addressing mode            |                       | $\leftarrow$ | Load | ded v | with             |      |       |      |            |                 |     |         |         |        |

| IX1+  | Indexed,    | 8-bit offset, post increment addressi   | ing mode              | ?            | lf   |       |                  |      |       |      |            |                 |     |         |         |        |

| IX2   | Indexed,    | 16-bit offset addressing mode           |                       | :            | Con  | cate  | nate             | d v  | vith  |      |            |                 |     |         |         |        |

| M     | Memory      | location                                |                       | <b>\$</b>    | Set  | or cl | eare             | d    |       |      |            |                 |     |         |         |        |

| N     | Negative    | e bit                                   |                       | _            | Not  | affec | cted             |      |       |      |            |                 |     |         |         |        |

# 6.9 Opcode Map

See Table 6-2.

## **Oscillator (OSC)**

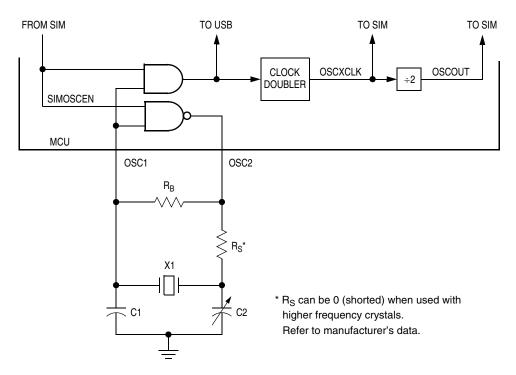

#### 7.3 Oscillator External Connections

In its typical configuration, the oscillator requires five external components. The crystal oscillator is normally connected in a Pierce oscillator configuration, as shown in **Figure 7-1**. This figure shows only the logical representation of the internal components and may not represent actual circuitry. The oscillator configuration uses five components:

- Crystal, X<sub>1</sub>

- Fixed capacitor, C<sub>1</sub>

- Tuning capacitor, C<sub>2</sub> (can also be a fixed capacitor)

- Feedback resistor, R<sub>R</sub>

- Series resistor, R<sub>S</sub> (optional)

Figure 7-1. Oscillator External Connections

Technical Data

## **System Integration Module (SIM)**

#### 8.6.1.2 SWI Instruction

The SWI instruction is a non-maskable instruction that causes an interrupt regardless of the state of the interrupt mask (I bit) in the condition code register.

**NOTE:** A software interrupt pushes PC onto the stack. A software interrupt does **not** push PC–1, as a hardware interrupt does.

#### 8.6.2 Interrupt Status Registers

The flags in the interrupt status registers identify maskable interrupt sources. **Table 8-4** summarizes the interrupt sources and the interrupt status register flags that they set. The interrupt status registers can be useful for debugging.

**Table 8-4. Interrupt Sources**

| Source                    | Flags          | Mask <sup>(1)</sup> | INT Register Flag | Priority <sup>(2)</sup> | Vector Address |  |

|---------------------------|----------------|---------------------|-------------------|-------------------------|----------------|--|

| SWI Instruction           |                |                     | _                 | 0                       | \$FFFC-\$FFFD  |  |

| USB Reset Interrupt       | RSTF           | URSTD               |                   |                         |                |  |

| USB Endpoint 0 Transmit   | TXD0F          | TXD0IE              |                   |                         |                |  |

| USB Endpoint 0 Receive    | RXD0F          | RXD0IE              |                   |                         |                |  |

| USB Endpoint 1 Transmit   | TXD1F          | TXD1IE              | IF2               | 4                       | ¢EEEA ¢EEED    |  |

| USB Endpoint 2 Transmit   | TXD2F          | TXD2IE              | IF2               | 1                       | \$FFFA-\$FFFB  |  |

| USB Endpoint 2 Receive    | RXD2F          | RXD2IE              |                   |                         | l              |  |

| USB End of Packet         | EOPF           | EOPIE               |                   |                         |                |  |

| USB Resume Interrupt      | RESUMF         | _                   |                   |                         |                |  |

| IRQ Interrupt (IRQ, PTE4) | IRQF<br>PTE4IF | IMASK               | IF1               | 2                       | \$FFF8_\$FFF9  |  |

| TIM Channel 0             | CH0F           | CH0IE               | IF3               | 3                       | \$FFF6-\$FFF7  |  |

| TIM Channel 1             | CH1F           | CH1IE               | IF4               | 4                       | \$FFF4-\$FFF5  |  |

| TIM Overflow              | TOF            | TOIE                | IF5               | 5                       | \$FFF2-\$FFF3  |  |

| Keyboard Interrupt        | KEYF           | IMASKK              | IF6               | 6                       | \$FFF0-\$FFF1  |  |

<sup>1.</sup> The I bit in the condition code register is a global mask for all interrupt sources except the SWI instruction.

<sup>2. 0 =</sup> highest priority

## **System Integration Module (SIM)**

### 8.6.5 Status Flag Protection in Break Mode

The SIM controls whether status flags contained in other modules can be cleared during break mode. The user can select whether flags are protected from being cleared by properly initializing the break clear flag enable bit (BCFE) in the break flag control register (BFCR).

Protecting flags in break mode ensures that set flags will not be cleared while in break mode. This protection allows registers to be freely read and written during break mode without losing status flag information.

Setting the BCFE bit enables the clearing mechanisms. Once cleared in break mode, a flag remains cleared even when break mode is exited. Status flags with a 2-step clearing mechanism — for example, a read of one register followed by the read or write of another — are protected, even when the first step is accomplished prior to entering break mode. Upon leaving break mode, execution of the second step will clear the flag as normal.

#### 8.7 Low-Power Modes

Executing the WAIT or STOP instruction puts the MCU in a low-power-consumption mode for standby situations. The SIM holds the CPU in a non-clocked state. The operation of each of these modes is described here. Both STOP and WAIT clear the interrupt mask (I) in the condition code register, allowing interrupts to occur.

#### 8.7.1 Wait Mode

In wait mode, the CPU clocks are inactive while the peripheral clocks continue to run. **Figure 8-13** shows the timing for wait mode entry.

A module that is active during wait mode can wake up the CPU with an interrupt if the interrupt is enabled. Stacking for the interrupt begins one cycle after the WAIT instruction during which the interrupt occurred. In wait mode, the CPU clocks are inactive. Refer to the wait mode subsection of each module to see if the module is active or inactive in wait mode. Some modules can be programmed to be active in wait mode.

**Technical Data**

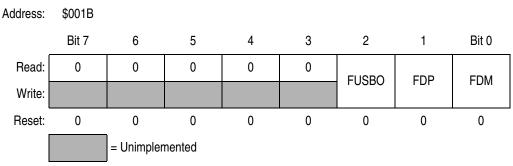

#### 9.8.9 USB Control Register 4

USB control register 4 directly controls the USB data pins D+ and D-. If the FUSBO bit, and the USBEN bit of the USB address register (UADDR) are set, the output buffers of the USB modules are enabled and the corresponding levels of the USB data pins D+ and D- are equal to the values set by the FDP and the FDM bits.

Figure 9-23. USB Control Register 4 (UCR4)

FUSBO — Force USB Output

This read/write bit enables the USB output buffers.

1 = Enables USB output buffers

0 = USB module in normal operation

FDP — Force D+

This read/write bit determinates the output level of D+.

1 = D+ at output high level

0 = D+ at output low level

FDM — Force D-

This read/write bit determinates the output level of D-.

1 = D- at output high level

0 = D- at output low level

**NOTE:**

Customers must be very careful when setting the UCR4 register. When the FUSBO and the USBEN bits are set, the USB module is in output mode and it will not recognize any USB signals including the USB reset signal. The UCR4 register is used for some special applications. Customers are not normally expected to use this register.

MC68HC908JB8•MC68HC08JB8•MC68HC08JT8 — Rev. 2.3

## **Monitor ROM (MON)**

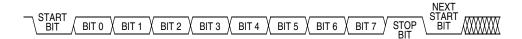

#### 10.4.3 Data Format

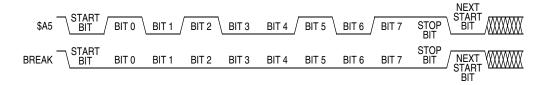

Communication with the monitor ROM is in standard non-return-to-zero (NRZ) mark/space data format. (See Figure 10-3 and Figure 10-4.)

Figure 10-3. Monitor Data Format

Figure 10-4. Sample Monitor Waveforms

The data transmit and receive rate can be anywhere from 4800 baud to 28.8k-baud. Transmit and receive baud rates must be identical.

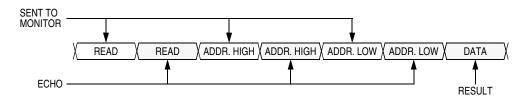

## 10.4.4 Echoing

As shown in **Figure 10-5**, the monitor ROM immediately echoes each received byte back to the PTA0 pin for error checking.

Figure 10-5. Read Transaction

Any result of a command appears after the echo of the last byte of the command.

Technical Data

## Technical Data — MC68HC908JB8•MC68HC08JB8•MC68HC08JT8

# **Section 11. Timer Interface Module (TIM)**

#### 11.1 Contents

| 11.2 Introduction                                                                                                                                                                                                                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11.3 Features                                                                                                                                                                                                                                                                                           |

| 11.4 Pin Name Conventions                                                                                                                                                                                                                                                                               |

| 11.5Functional Description17911.5.1TIM Counter Prescaler18111.5.2Input Capture18111.5.3Output Compare18111.5.3.1Unbuffered Output Compare18211.5.3.2Buffered Output Compare18311.5.4Pulse Width Modulation (PWM)18311.5.4.1Unbuffered PWM Signal Generation18411.5.4.2Puffered PWM Signal Generation184 |

| 11.5.4.2 Buffered PWM Signal Generation                                                                                                                                                                                                                                                                 |

| 11.6 Interrupts187                                                                                                                                                                                                                                                                                      |

| 11.7 Low-Power Modes       187         11.7.1 Wait Mode       188         11.7.2 Stop Mode       188                                                                                                                                                                                                    |

| 11.8 TIM During Break Interrupts                                                                                                                                                                                                                                                                        |

| 11.9       I/O Signals                                                                                                                                                                                                                                                                                  |

| 11.10 I/O Registers.18911.10.1 TIM Status and Control Register19011.10.2 TIM Counter Registers19211.10.3 TIM Counter Modulo Registers19311.10.4 TIM Channel Status and Control Registers19411.10.5 TIM Channel Registers198                                                                             |

|                                                                                                                                                                                                                                                                                                         |

MC68HC908JB8•MC68HC08JB8•MC68HC08JT8 — Rev. 2.3

## **Timer Interface Module (TIM)**

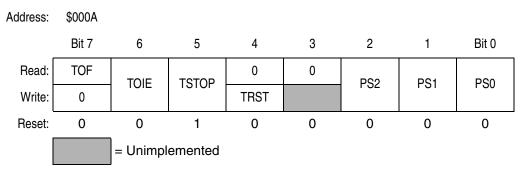

#### 11.10.1 TIM Status and Control Register

The TIM status and control register:

- Enables TIM overflow interrupts

- Flags TIM overflows

- Stops the TIM counter

- Resets the TIM counter

- Prescales the TIM counter clock

Figure 11-4. TIM Status and Control Register (TSC)

#### TOF — TIM Overflow Flag Bit

This read/write flag is set when the TIM counter reaches the modulo value programmed in the TIM counter modulo registers. Clear TOF by reading the TIM status and control register when TOF is set and then writing a logic 0 to TOF. If another TIM overflow occurs before the clearing sequence is complete, then writing logic 0 to TOF has no effect. Therefore, a TOF interrupt request cannot be lost due to inadvertent clearing of TOF. Reset clears the TOF bit. Writing a logic 1 to TOF has no effect.

- 1 = TIM counter has reached modulo value

- 0 = TIM counter has not reached modulo value

#### TOIE — TIM Overflow Interrupt Enable Bit

This read/write bit enables TIM overflow interrupts when the TOF bit becomes set. Reset clears the TOIE bit.

- 1 = TIM overflow interrupts enabled

- 0 = TIM overflow interrupts disabled

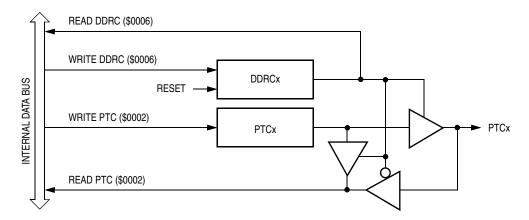

Figure 12-10. Port C I/O Circuit

When bit DDRCx is a logic 1, reading address \$0002 reads the PTCx data latch. When bit DDRCx is a logic 0, reading address \$0002 reads the voltage level on the pin. The data latch can always be written, regardless of the state of its data direction bit. **Table 12-4** summarizes the operation of the port C pins.

| DDRC<br>Bit | PTC Bit          | I/O Pin Mode               | Accesses<br>to DDRC | Access   | cesses to PTC           |  |  |  |

|-------------|------------------|----------------------------|---------------------|----------|-------------------------|--|--|--|

|             |                  |                            | Read/Write          | Read     | Write                   |  |  |  |

| 0           | X <sup>(1)</sup> | Input, Hi-Z <sup>(2)</sup> | DDRC[7:0]           | Pin      | PTC[7:0] <sup>(3)</sup> |  |  |  |

| 1           | Х                | Output                     | DDRC[7:0]           | PTC[7:0] | PTC[7:0]                |  |  |  |

**Table 12-4. Port C Pin Functions**

#### NOTES:

- 1. X = don't care.

- 2. Hi-Z = high impedance.

- 3. Writing affects data register, but does not affect input.

#### 12.6 Port D

Port D is an 8-bit general-purpose bidirectional I/O port. In 20-pin package, PTD1 and PTD0 internal pads are bonded together to PTD0/1 pin. Port D pins are open-drain when configured as output, and can interface with 5V logic.

MC68HC908JB8•MC68HC08JB8•MC68HC08JT8 — Rev. 2.3

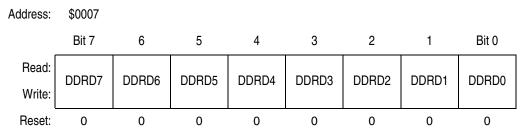

### 12.6.2 Data Direction Register D

Data direction register D determines whether each port D pin is an input or an output. Writing a logic 1 to a DDRD bit enables the output buffer for the corresponding port D pin; a logic 0 disables the output buffer.

Figure 12-12. Data Direction Register D (DDRD)

DDRD[7:0] — Data Direction Register D Bits

These read/write bits control port D data direction. Reset clears DDRD[7:0], configuring all port D pins as inputs.

1 = Corresponding port D pin configured as output

0 = Corresponding port D pin configured as input

Port D pins are open-drain when configured as output.

**NOTE:** Avoid glitches on port D pins by writing to the port D data register before changing data direction register D bits from 0 to 1.

**NOTE:** For those devices packaged in a 20-pin PDIP and 20-pin SOIC package, PTD7–PTD2 are not connected. DDRD7–DDRD2 should be set to a 1 to configure PTD7–PTD2 as outputs.

For those devices packaged in a 28-pin SOIC package, PTD7 is not connected. DDRD7 should be set to a 1 to configure PTD7 as output.

Figure 12-13 shows the port D I/O circuit logic.

### 12.7.1 Port E Data Register

The port E data register contains a data latch for each of the five port E pins.

**NOTE:** PTE2 and PTE0 are not available in the 20-pin PDIP and 20-pin SOIC packages.

Figure 12-14. Port E Data Register (PTE)

PTE[4:0] — Port E Data Bits

PTE[4:0] are read/write, software-programmable bits. Data direction of each port E pin is under the control of the corresponding bit in data direction register E.

The PTE4 and PTE3 pullup enable bits, PTE4P and PTE3P, in the port option control register (POCR) enable  $5k\Omega$  pullups on PTE4 and PTE3 if the respective pin is configured as an input and the USB module is disabled. (See 12.8 Port Options.)

The PTE[2:0] pullup enable bit, PTE20P, in the port option control register (POCR) enables pullups on PTE2–PTE0, regardless of the pin is configured as an input or an output. (See **12.8 Port Options**.)

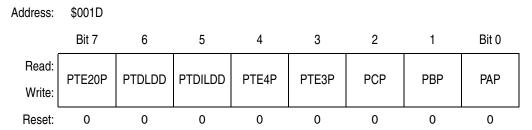

#### 12.8.1 Port Option Control Register

The port option control register controls the pullup options for port A, B, C, and E pins. It also controls the drive configuration on port D.

Figure 12-17. Port Option Control Register (POCR)

#### PTE20P — Port PTE2-PTE0 Pullup Enable

This read/write bit controls the pullup option for the PTE2–PTE0 pins, regardless whether the pins are input or output.

- 1 = Configure PTE2-PTE0 to have internal pullups to V<sub>REG</sub>

- 0 = Disconnect PTE2-PTE0 internal pullups

#### PTDLDD — LED Direct Drive Control

This read/write bit controls the output current capability of PTD5–PTD2 pins. When set, each port pin has 10mA current sink limit. An LED can be connected directly between the port pin and  $V_{DD}$  without the need of a series resistor.

- 1 = PTD5–PTD2 configured for direct LED drive capability; when a pin is set as an output, the pin is an open-drain pin with 10mA current sink limit

- 0 = PTD5-PTD2 configured as standard open-drain I/O port pin

#### PTDILDD — Infrared LED Drive Control

This read/write bit controls the output current capability of PTD1 and PTD0 pins. When set, each port pin has 25 mA current sink capability. An infrared LED can be connected directly between the port pin and  $V_{\rm DD}$ .

- 1 = PTD1 and PTD0 configured for infrared LED drive capability; when a pin is set as an output, the pin is an open-drain pin with 25mA current sink capability

- 0 = PTD1 and PTD0 configured as standard open-drain I/O port pins

MC68HC908JB8•MC68HC08JB8•MC68HC08JT8 — Rev. 2.3

Use the BIH or BIL instruction to read the logic level on the IRQ pin.

NOTE: When using the level-sensitive interrupt trigger, avoid false interrupts by

masking interrupt requests in the interrupt routine.

**NOTE:** An internal pullup resistor to  $V_{DD}$  is connected to  $\overline{IRQ}$  pin; this can be

disabled by setting the IRQPD bit in the IRQ option control register

(\$001C).

#### 13.6 PTE4/D- Pin

The PTE4 pin is configured as an interrupt input to trigger the IRQ interrupt when the following conditions are satisfied:

- The USB module is disabled (USBEN = 0)

- PTE4 pin configured for external interrupt input (PTE4IE = 1)

Setting PTE4IE configures the PTE4 pin to an input pin with an internal pullup device. The PTE4 interrupt is "ORed" with the IRQ input to trigger the IRQ interrupt (see **Figure 13-1**. **IRQ Module Block Diagram**). Therefore, the IRQ status and control register affects both the IRQ pin and the PTE pin. An interrupt on PTE4 also sets the PTE4 interrupt flag, PTE4IF, in the IRQ option control register (IOCR).

## 13.7 IRQ Module During Break Interrupts

The system integration module (SIM) controls whether the IRQ latch can be cleared during the break state. The BCFE bit in the break flag control register (BFCR) enables software to clear the latches during the break state. (See Section 8. System Integration Module (SIM).)

To allow software to clear the IRQ latch during a break interrupt, write a logic 1 to the BCFE bit. If a latch is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect the latches during the break state, write a logic 0 to the BCFE bit. With BCFE at logic 0 (its default state), writing to the ACK bit in the IRQ status and control register during the break state has no effect on the IRQ latch.

MC68HC908JB8•MC68HC08JB8•MC68HC08JT8 — Rev. 2.3

Return of all enabled keyboard interrupt pins to logic 1 — As long as any enabled keyboard interrupt pin is at logic 0, the keyboard interrupt remains set.

The vector fetch or software clear and the return of all enabled keyboard interrupt pins to logic 1 may occur in any order.

If the MODEK bit is clear, the keyboard interrupt pin is falling-edgesensitive only. With MODEK clear, a vector fetch or software clear immediately clears the keyboard interrupt request.

Reset clears the keyboard interrupt request and the MODEK bit, clearing the interrupt request even if a keyboard interrupt pin stays at logic 0.

The keyboard flag bit (KEYF) in the keyboard status and control register can be used to see if a pending interrupt exists. The KEYF bit is not affected by the keyboard interrupt mask bit (IMASKK) which makes it useful in applications where polling is preferred.

To determine the logic level on a keyboard interrupt pin, use the data direction register to configure the pin as an input and read the data register.

#### **NOTE:**

Setting a keyboard interrupt enable bit (KBIEx) forces the corresponding keyboard interrupt pin to be an input, overriding the data direction register. However, the data direction register bit must be a logic 0 for software to read the pin.

## 14.6 Keyboard Initialization

When a keyboard interrupt pin is enabled, it takes time for the pullup device to reach a logic 1. Therefore, a false interrupt can occur as soon as the pin is enabled.

To prevent a false interrupt on keyboard initialization:

- 1. Mask keyboard interrupts by setting the IMASKK bit in the keyboard status and control register.

- 2. Enable the KBI pins by setting the appropriate KBIEx bits in the keyboard interrupt enable register.

MC68HC908JB8•MC68HC08JB8•MC68HC08JT8 — Rev. 2.3

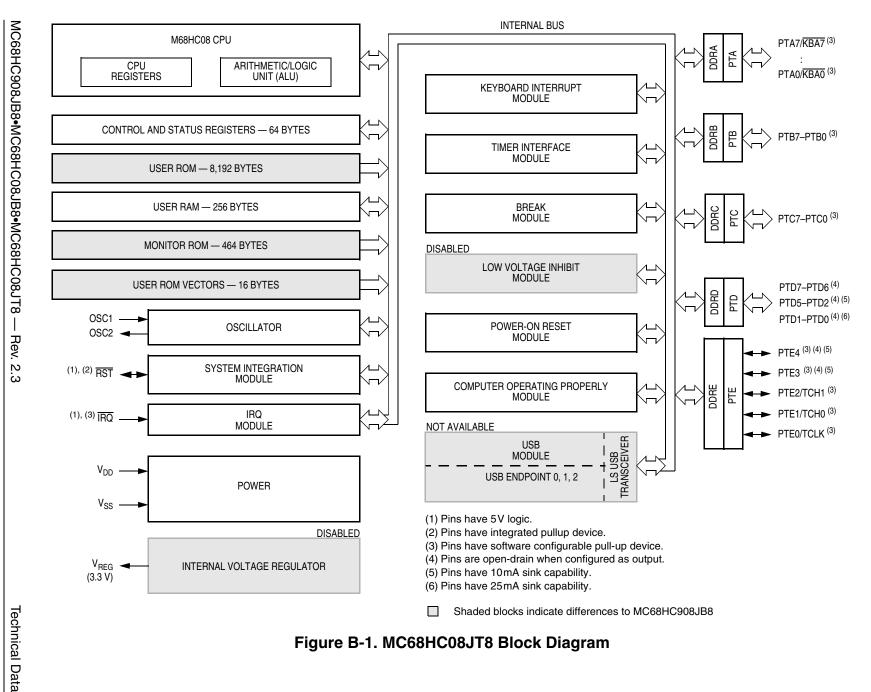

Figure B-1. MC68HC08JT8 Block Diagram