#### Motorola - MC68HC908JB8JPE Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | HC08                                                         |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 3MHz                                                         |

| Connectivity               | USB                                                          |

| Peripherals                | LVD, POR, PWM                                                |

| Number of I/O              | 13                                                           |

| Program Memory Size        | 8KB (8K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | -                                                            |

| RAM Size                   | 256 x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                    |

| Data Converters            | -                                                            |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | 0°C ~ 70°C (TA)                                              |

| Mounting Type              | Through Hole                                                 |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                      |

| Supplier Device Package    | 20-DIP                                                       |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc68hc908jb8jpe |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Section 18. Electrical Specifications

| 18.1  | Contents                                         | :53 |

|-------|--------------------------------------------------|-----|

| 18.2  | Introduction                                     | 53  |

| 18.3  | Absolute Maximum Ratings2                        | 54  |

| 18.4  | Functional Operating Range2                      | 55  |

| 18.5  | Thermal Characteristics2                         | :55 |

| 18.6  | DC Electrical Characteristics2                   | 56  |

| 18.7  | Control Timing                                   | 57  |

| 18.8  | Oscillator Characteristics                       | 57  |

| 18.9  | USB DC Electrical Characteristics                | 58  |

| 18.10 | USB Low-Speed Source Electrical Characteristics2 | :59 |

| 18.11 | USB Signaling Levels                             | 60  |

| 18.12 | TImer Interface Module Characteristics           | 60  |

| 18.13 | Memory Characteristics                           | 61  |

# Section 19. Mechanical Specifications

| 19.1 | Contents                                          |

|------|---------------------------------------------------|

| 19.2 | Introduction                                      |

| 19.3 | 44-Pin Plastic Quad Flat Pack (QFP)               |

| 19.4 | 28-Pin Small Outline Integrated Circuit (SOIC)265 |

| 19.5 | 20-Pin Dual In-Line Package (PDIP)                |

| 19.6 | 20-Pin Small Outline Integrated Circuit (SOIC)    |

# Section 20. Ordering Information

| 20.1 | Contents         |

|------|------------------|

| 20.2 | Introduction     |

| 20.3 | MC Order Numbers |

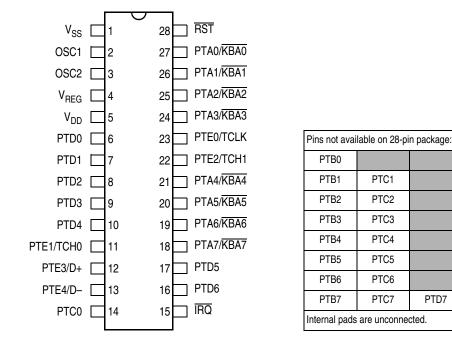

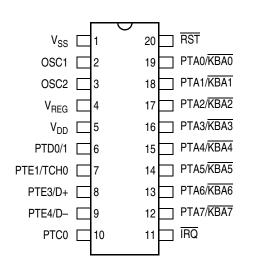

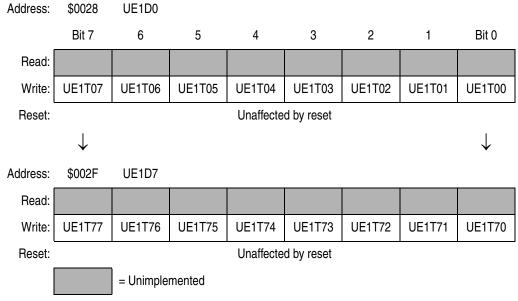

PTD7

| Pins not available on 20-pin package: |      |      |           |  |  |  |  |  |  |

|---------------------------------------|------|------|-----------|--|--|--|--|--|--|

| PTB0                                  |      |      | PTE0/TCLK |  |  |  |  |  |  |

| PTB1                                  | PTC1 |      |           |  |  |  |  |  |  |

| PTB2                                  | PTC2 | PTD2 | PTE2/TCH1 |  |  |  |  |  |  |

| PTB3                                  | PTC3 | PTD3 |           |  |  |  |  |  |  |

| PTB4                                  | PTC4 | PTD4 |           |  |  |  |  |  |  |

| PTB5                                  | PTC5 | PTD5 |           |  |  |  |  |  |  |

| PTB6                                  | PTC6 | PTD6 |           |  |  |  |  |  |  |

| PTB7                                  | PTC7 | PTD7 |           |  |  |  |  |  |  |

| Internal pads are unconnected.        |      |      |           |  |  |  |  |  |  |

NOTE: In 20-pin package, the PTD0 and PTD1 internal pads are bonded together to PTD0/1 pin.

| Addr.  | Register Name                                  |        | Bit 7  | 6         | 5      | 4           | 3             | 2     | 1           | Bit 0        |

|--------|------------------------------------------------|--------|--------|-----------|--------|-------------|---------------|-------|-------------|--------------|

|        | TIM Status and Control                         | Read:  | TOF    | TOIL      | TOTOD  | 0           | 0             | DOO   | DO1         | DOO          |

| \$000A | Register                                       | Write: | 0 TOIE |           | TSTOP  | TRST        |               | PS2   | PS1         | PS0          |

|        | (TSC)                                          | Reset: | 0      | 0         | 1      | 0           | 0             | 0     | 0           | 0            |

|        |                                                | Read:  |        |           |        |             |               |       |             |              |

| \$000B | Unimplemented                                  | Write: |        |           |        |             |               |       |             |              |

|        |                                                | ,      |        |           |        |             |               |       |             |              |

|        | TIM Counter Register                           | Read:  | Bit15  | Bit14     | Bit13  | Bit12       | Bit11         | Bit10 | Bit9        | Bit8         |

| \$000C | High                                           | Write: |        |           |        |             |               |       |             |              |

|        | (TCNTH)                                        | Reset: | 0      | 0         | 0      | 0           | 0             | 0     | 0           | 0            |

|        | TIM Counter Register                           | Read:  | Bit7   | Bit6      | Bit5   | Bit4        | Bit3          | Bit2  | Bit1        | Bit0         |

| \$000D | Low                                            | Write: |        |           |        |             |               |       |             |              |

|        | (TCNTL)                                        | Reset: | 0      | 0         | 0      | 0           | 0             | 0     | 0           | 0            |

|        | TIM Counter Modulo<br>Register High<br>(TMODH) | Read:  | Bit15  | Bit14     | Bit13  | Bit12       | Bit11         | Bit10 | Bit9        | Bit8         |

| \$000E |                                                | Write: | Dit15  | DITA      | Dirio  | DITZ        | DILTI         | DILTO | Dita        | Dito         |

|        |                                                | Reset: | 1      | 1         | 1      | 1           | 1             | 1     | 1           | 1            |

|        |                                                | Read:  | Bit7   | Bit6      | Bit5   | Bit4        | Bit3          | Bit2  | Bit1        | Bit0         |

| \$000F |                                                | Write: | Diti   | Dito      | Dito   | DIL4        | Dito          | DILZ  | Ditt        | Dito         |

|        |                                                | Reset: | 1      | 1         | 1      | 1           | 1             | 1     | 1           | 1            |

|        | TIM Channel 0 Status and                       | Read:  | CH0F   | CH0IE     | MS0B   | MS0A        | ELS0B         | ELS0A | TOV0        | CHOMAX       |

| \$0010 | Control Register                               |        | 0      | ONDE      | MOOD   | MOOA        | LLOOD         | LLOUA | 1000        | OHOMAA       |

|        | (TSC0)                                         | Reset: | 0      | 0         | 0      | 0           | 0             | 0     | 0           | 0            |

|        | TIM Channel 0                                  | Read:  | Bit15  | Bit14     | Bit13  | Bit12       | Bit11         | Bit10 | Bit9        | Bit8         |

| \$0011 | Register High                                  | Write: | Bitro  | BRIT      | Birlo  | DITL        | BRIT          | Bitro | Dito        | Bito         |

|        | (TCH0H)                                        | Reset: |        |           |        | Indetermina | te after rese | t     |             |              |

|        | TIM Channel 0                                  | Read:  | Bit7   | Bit6      | Bit5   | Bit4        | Bit3          | Bit2  | Bit1        | Bit0         |

| \$0012 | Register Low                                   |        | DI     | Dito      | Bito   | Ditt        | Bito          | DAL   | Ditt        | Bito         |

|        | (TCH0L)                                        | Reset: |        |           |        | Indetermina | te after rese | t     |             |              |

|        | TIM Channel 1 Status and                       | Read:  | CH1F   | CH1IE     | 0      | MS1A        | ELS1B         | ELS1A | TOV1        | CH1MAX       |

| \$0013 | Control Register                               |        | 0      |           |        |             |               |       |             |              |

|        | (TSC1)                                         | Reset: | 0      | 0         | 0      | 0           | 0             | 0     | 0           | 0            |

|        |                                                |        |        | = Unimple | mented | R           | = Reserve     | d     | U = Unaffec | ted by reset |

|        |                                                |        |        |           |        |             |               |       |             |              |

Figure 2-2. Control, Status, and Data Registers (Sheet 2 of 8)

# NP

# Memory Map

| Addr.         | Register Name                                                  |                 | Bit 7 | 6          | 5      | 4         | 3          | 2       | 1           | Bit 0        |  |

|---------------|----------------------------------------------------------------|-----------------|-------|------------|--------|-----------|------------|---------|-------------|--------------|--|

| \$003C        | USB Control Register 1<br>(UCR1)                               | Read:<br>Write: | T1SEQ | STALL1     | TX1E   | FRESUM    | TP1SIZ3    | TP1SIZ2 | TP1SIZ1     | TP1SIZ0      |  |

|               | (••••••)                                                       | Reset:          | 0     | 0          | 0      | 0         | 0          | 0       | 0           | 0            |  |

|               |                                                                | Read:           | R0SEQ | SETUP      | 0      | 0         | RP0SIZ3    | RP0SIZ2 | RP0SIZ1     | RP0SIZ0      |  |

| \$003D        | USB Status Register 0<br>(USR0)                                | Write:          |       |            |        |           |            |         |             |              |  |

|               | ()                                                             | Reset:          |       |            |        | Unaffecte | d by reset |         |             |              |  |

|               |                                                                | Read:           | R2SEQ | TXACK      | TXNAK  | TXSTL     | RP2SIZ3    | RP2SIZ2 | RP2SIZ1     | RP2SIZ0      |  |

| \$003E        | USB Status Register 1<br>(USR1)                                | Write:          |       |            |        |           |            |         |             |              |  |

|               | ()                                                             | Reset:          | U     | 0          | 0      | 0         | U          | U       | U           | U            |  |

|               |                                                                | Read:           |       |            |        |           |            |         |             |              |  |

| \$003F        | Unimplemented                                                  | Write:          |       |            |        |           |            |         |             |              |  |

|               |                                                                | •               |       |            |        |           |            |         |             |              |  |

|               |                                                                | Read:           | _     | _          | _      | _         | _          | _       | SBSW        | _            |  |

| \$FE00        | Break Status Register<br>(BSR)                                 | Write:          | R     | R          | R      | R         | R          | R       | See note    | R            |  |

|               | (BON)                                                          | Reset:          |       |            |        |           |            |         | 0           |              |  |

| Note: W       | riting a logic 0 clears SBSW                                   | Ι.              |       |            |        |           |            |         |             |              |  |

|               | )1 Reset Status Register<br>(RSR)                              | Read:           | POR   | PIN        | COP    | ILOP      | ILAD       | USB     | LVI         | 0            |  |

| \$FE01        |                                                                | Write:          |       |            |        |           |            |         |             |              |  |

|               |                                                                | POR:            | 1     | 0          | 0      | 0         | 0          | 0       | 0           | 0            |  |

|               |                                                                | Read:           | R     | R          | R      | Р         | Р          | Р       | Р           | D            |  |

| \$FE02        | Reserved                                                       | Write:          | n     | n          | п      | R         | R          | R       | R           | R            |  |

|               |                                                                | L               |       |            |        | •         |            |         | •           |              |  |

| \$FE03        | Break Flag Control<br>Register                                 | Read:<br>Write: | BCFE  | R          | R      | R         | R          | R       | R           | R            |  |

|               |                                                                | Reset:          | 0     |            |        |           |            |         |             |              |  |

|               |                                                                | Read:           | IF6   | IF5        | IF4    | IF3       | IF2        | IF1     | 0           | 0            |  |

| \$FE04        | Interrupt Status Register 1                                    | Write:          | R     | R          | R      | R         | R          | R       | R           | R            |  |

| ÷. =• !       | (INT1)                                                         | Reset:          | 0     | 0          | 0      | 0         | 0          | 0       | 0           | 0            |  |

|               |                                                                | Read:           |       | -          | -      | -         | -          | -       | -           | -            |  |

| \$FE05        | Reserved                                                       |                 | R     | R          | R      | R         | R          | R       | R           | R            |  |

| Ţ. <b>200</b> | 10001700                                                       |                 |       | [          | [      |           |            |         |             |              |  |

|               |                                                                |                 |       | = Unimplei | mented | R         | = Reserve  | d       | U = Unaffec | ted by reset |  |

|               | Figure 2.2. Control. Status, and Data Degisters (Sheet 7 of 9) |                 |       |            |        |           |            |         |             |              |  |

# Figure 2-2. Control, Status, and Data Registers (Sheet 7 of 8)

Technical Data

# 6.8 Instruction Set Summary

| Source<br>Form                                                                                  | Operation                              | Description                                                              |    | E  | Effect on<br>CCR |    |    |    | Address<br>Mode                                     | ode                                              | Operand                                   | es                                   |

|-------------------------------------------------------------------------------------------------|----------------------------------------|--------------------------------------------------------------------------|----|----|------------------|----|----|----|-----------------------------------------------------|--------------------------------------------------|-------------------------------------------|--------------------------------------|

| FOIII                                                                                           |                                        |                                                                          |    |    | I                | Ν  | z  | С  | Add                                                 | Opcode                                           | Ope                                       | Cycles                               |

| ADC #opr<br>ADC opr<br>ADC opr<br>ADC opr,X<br>ADC opr,X<br>ADC ,X<br>ADC opr,SP<br>ADC opr,SP  | Add with Carry                         | A ← (A) + (M) + (C)                                                      | ¢  | \$ | _                | \$ | \$ | \$ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A9<br>B9<br>C9<br>D9<br>E9<br>F9<br>9EE9<br>9ED9 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ee ff | 2<br>3<br>4<br>3<br>2<br>4<br>5      |

| ADD #opr<br>ADD opr<br>ADD opr,<br>ADD opr,X<br>ADD opr,X<br>ADD ,X<br>ADD opr,SP<br>ADD opr,SP | Add without Carry                      | A ← (A) + (M)                                                            | \$ | \$ | _                | ¢  | \$ | ↔  | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | AB<br>BB<br>CB<br>DB<br>EB<br>FB<br>9EEB<br>9EDB | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ee ff | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| AIS #opr                                                                                        | Add Immediate Value (Signed) to SP     | $SP \leftarrow (SP) + (16 \mathrel{\scriptstyle{\scriptstyle \ll}} M)$   | -  | -  | -                | -  | -  | I  | IMM                                                 | A7                                               | ii                                        | 2                                    |

| AIX #opr                                                                                        | Add Immediate Value (Signed) to H:X    | $H:X \leftarrow (H:X) + (16 \mathrel{\scriptstyle{\scriptstyle \ll}} M)$ | -  | -  | I                |    | -  | -  | IMM                                                 | AF                                               | ii                                        | 2                                    |

| AND #opr<br>AND opr<br>AND opr<br>AND opr,X<br>AND opr,X<br>AND ,X<br>AND opr,SP<br>AND opr,SP  | Logical AND                            | A ← (A) & (M)                                                            | 0  | _  | _                | \$ | \$ | _  | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A4<br>B4<br>C4<br>D4<br>E4<br>F4<br>9EE4<br>9ED4 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ee ff | 2<br>3<br>4<br>3<br>2<br>4<br>5      |

| ASL opr<br>ASLA<br>ASLX<br>ASL opr,X<br>ASL ,X<br>ASL opr,SP                                    | Arithmetic Shift Left<br>(Same as LSL) |                                                                          | \$ | _  | _                | \$ | \$ | \$ | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 38<br>48<br>58<br>68<br>78<br>9E68               | dd<br>ff<br>ff                            | 4<br>1<br>4<br>3<br>5                |

| ASR <i>opr</i><br>ASRA<br>ASRX<br>ASR <i>opr</i> ,X<br>ASR <i>opr</i> ,X<br>ASR <i>opr</i> ,SP  | Arithmetic Shift Right                 |                                                                          | \$ | _  | _                | \$ | \$ | ↔  | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 37<br>47<br>57<br>67<br>77<br>9E67               | dd<br>ff<br>ff                            | 4<br>1<br>4<br>3<br>5                |

### Table 6-1. Instruction Set Summary (Sheet 1 of 9)

**Technical Data**

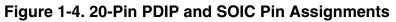

Figure 8-1. SIM Block Diagram

| Table 8-1. SIM Module Signal N | lame Conventions |

|--------------------------------|------------------|

|--------------------------------|------------------|

| Signal Name | Description                                                                                                                                                                             |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSCXCLK     | Clock doubler output which has twice the frequency of OSC1 from the oscillator                                                                                                          |

| OSCOUT      | The OSCXCLK frequency divided by two. This signal is again divided by two in the SIM to generate the internal bus clocks.<br>(Bus clock = OSCXCLK $\div$ 4 = f <sub>OSC</sub> $\div$ 2) |

| IAB         | Internal address bus                                                                                                                                                                    |

| IDB         | Internal data bus                                                                                                                                                                       |

| PORRST      | Signal from the power-on reset module to the SIM                                                                                                                                        |

| IRST        | Internal reset signal                                                                                                                                                                   |

| R/W         | Read/write signal                                                                                                                                                                       |

#### MC68HC908JB8•MC68HC08JB8•MC68HC08JT8 — Rev. 2.3

System Integration Module (SIM)

SBSW can be read within the break state SWI routine. The user can modify the return address on the stack by subtracting one from it. The following code is an example of this. Writing 0 to the SBSW bit clears it.

This code works if the H register has been pushed onto the stack in the break service routine software. This code should be executed at the end of the break service routine software.

| HIBYTE | EQU         | 5                |                                                        |

|--------|-------------|------------------|--------------------------------------------------------|

| LOBYTE | EQU         | 6                |                                                        |

| ;      | If not      | SBSW, do RTI     |                                                        |

|        | BRCLR       | SBSW,BSR, RETURN | ; See if wait mode or stop mode was exited ; by break. |

|        | TST         | LOBYTE, SP       | ; If RETURNLO is not zero,                             |

|        | BNE         | DOLO             | ; then just decrement low byte.                        |

|        | DEC         | HIBYTE, SP       | ; Else deal with high byte, too.                       |

| DOLO   | DEC         | LOBYTE, SP       | ; Point to WAIT/STOP opcode.                           |

| RETURN | PULH<br>RTI |                  | ; Restore H register.                                  |

#### 8.8.2 Reset Status Register

This register contains seven flags that show the source of the last reset. All flag bits are cleared automatically following a read of the register. The register is initialized on power-up as shown with the POR bit set and all other bits cleared. However, during a POR or any other internal reset, the  $\overline{\text{RST}}$  pin is pulled low. After the pin is released, it will be sampled 32 XCLK cycles later. If the pin is not above a V<sub>IH</sub> at that time, then the PIN bit in the RSR may be set in addition to whatever other bits are set.

# Universal Serial Bus Module (USB)

| Addr.  | Register Name                                |        | Bit 7                   | 6          | 5      | 4         | 3             | 2            | 1      | Bit 0  |  |  |  |  |

|--------|----------------------------------------------|--------|-------------------------|------------|--------|-----------|---------------|--------------|--------|--------|--|--|--|--|

| \$002C | USB Endpoint 1 Data                          | Read:  |                         |            |        |           |               |              |        |        |  |  |  |  |

|        | Register 4                                   |        | UE1T47                  | UE1T46     | UE1T45 | UE1T44    | UE1T43        | UE1T42       | UE1T41 | UE1T40 |  |  |  |  |

|        | (UE1D4)                                      | Reset: |                         |            |        | Unaffecte | cted by reset |              |        |        |  |  |  |  |

| \$002D | USB Endpoint 1 Data                          | Read:  |                         |            |        |           |               |              |        |        |  |  |  |  |

|        | Register5                                    |        | UE1T57                  | UE1T56     | UE1T55 | UE1T54    | UE1T53        | UE1T52       | UE1T51 | UE1T50 |  |  |  |  |

|        | (UE1D5)                                      | Reset: |                         |            |        | Unaffecte | d by reset    |              |        |        |  |  |  |  |

| \$002E | USB Endpoint 1 Data                          | Read:  |                         |            |        |           |               |              |        |        |  |  |  |  |

|        | Register 6                                   | Write: | UE1T67                  | UE1T66     | UE1T65 | UE1T64    | UE1T63        | UE1T62       | UE1T61 | UE1T60 |  |  |  |  |

|        | (UE1D6)                                      | Reset: |                         |            |        | Unaffecte | d by reset    |              |        |        |  |  |  |  |

| \$002F | USB Endpoint 1 Data                          | Read:  |                         |            |        |           |               |              |        |        |  |  |  |  |

|        | Register 7                                   | Write: | UE1T77                  | UE1T76     | UE1T75 | UE1T74    | UE1T73        | UE1T72       | UE1T71 | UE1T70 |  |  |  |  |

|        | (UE1D7)                                      | Reset: |                         |            |        | Unaffecte | d by reset    |              |        |        |  |  |  |  |

| \$0030 | USB Endpoint 2 Data<br>Register 0<br>(UE2D0) | Read:  | UE2R07                  | UE2R06     | UE2R05 | UE2R04    | UE2R03        | UE2R02       | UE2R01 | UE2R00 |  |  |  |  |

|        |                                              | Write: | UE2T07                  | UE2T06     | UE2T05 | UE2T04    | UE2T03        | UE2T02       | UE2T01 | UE2T00 |  |  |  |  |

|        |                                              | Reset: | et: Unaffected by reset |            |        |           |               |              |        |        |  |  |  |  |

| \$0031 | USB Endpoint 2 Data                          | Read:  | UE2R17                  | UE2R16     | UE2R15 | UE2R14    | UE2R13        | UE2R12       | UE2R11 | UE2R10 |  |  |  |  |

|        | Register 1                                   | Write: | UE2T17                  | UE2T16     | UE2T15 | UE2T14    | UE2T13        | UE2T12       | UE2T11 | UE2T10 |  |  |  |  |

|        | (UE2D1)                                      | Reset: |                         |            |        | Unaffecte | d by reset    |              |        |        |  |  |  |  |

| \$0032 | USB Endpoint 2 Data                          | Read:  | UE2R27                  | UE2R26     | UE2R25 | UE2R24    | UE2R23        | UE2R22       | UE2R21 | UE2R20 |  |  |  |  |

|        | Register 2                                   | Write: | UE2T27                  | UE2T26     | UE2T25 | UE2T24    | UE2T23        | UE2T22       | UE2T21 | UE2T20 |  |  |  |  |

|        | (UE2D2)                                      | Reset: |                         |            |        | Unaffecte | d by reset    |              |        |        |  |  |  |  |

| \$0033 | USB Endpoint 2 Data                          | Read:  | UE2R37                  | UE2R36     | UE2R35 | UE2R34    | UE2R33        | UE2R32       | UE2R31 | UE2R30 |  |  |  |  |

|        | Register 3                                   | Write: | UE2T37                  | UE2T36     | UE2T35 | UE2T34    | UE2T33        | UE2T32       | UE2T31 | UE2T30 |  |  |  |  |

|        | (UE2D3)                                      | Reset: |                         |            |        |           | d by reset    |              |        |        |  |  |  |  |

| \$0034 | USB Endpoint 2 Data                          | Read:  | UE2R47                  | UE2R46     | UE2R45 | UE2R44    | UE2R43        | UE2R42       | UE2R41 | UE2R40 |  |  |  |  |

|        | Register 4                                   | Write: | UE2T47                  | UE2T46     | UE2T45 | UE2T44    | UE2T43        | UE2T42       | UE2T41 | UE2T40 |  |  |  |  |

|        | (UE2D4)                                      | Reset: |                         |            |        | Unaffecte | d by reset    |              |        |        |  |  |  |  |

| \$0035 | USB Endpoint 2 Data                          | Read:  | UE2R57                  | UE2R56     | UE2R55 | UE2R54    | UE2R53        | UE2R52       | UE2R51 | UE2R50 |  |  |  |  |

|        | Register 5                                   | Write: | UE2T57                  | UE2T56     | UE2T55 | UE2T54    | UE2T53        | UE2T52       | UE2T51 | UE2T50 |  |  |  |  |

|        | (UE2D5)                                      | Reset: | Unaffected by reset     |            |        |           |               |              |        |        |  |  |  |  |

|        |                                              |        |                         | = Unimplei | mented |           | U = Unaffeo   | cted by rese | t      |        |  |  |  |  |

|        |                                              |        |                         |            |        |           |               |              |        |        |  |  |  |  |

Figure 9-1. USB I/O Register Summary (Sheet 3 of 4)

Technical Data

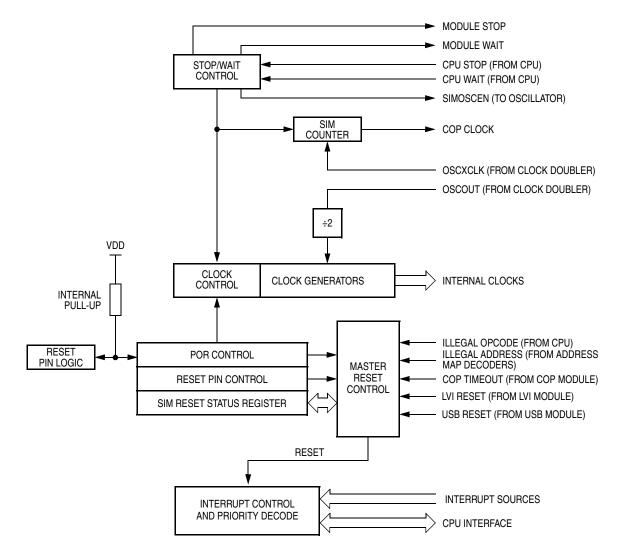

#### 9.8.8 USB Control Register 3

\* PULLEN bit is reset by POR or LVI reset only.

#### Figure 9-22. USB Control Register 3 (UCR3)

TX1ST — Endpoint 0 Transmit First Flag

This read-only bit is set if the endpoint 0 data transmit flag (TXD0F) is set when the USB control logic is setting the endpoint 0 data receive flag (RXD0F). In other words, if an unserviced endpoint 0 transmit flag is still set at the end of an endpoint 0 reception, then this bit will be set. This bit lets the firmware know that the endpoint 0 transmission happened before the endpoint 0 reception.

Reset clears this bit.

1 = IN transaction occurred before SETUP/OUT

0 = IN transaction occurred after SETUP/OUT

TX1STR — Clear Endpoint 0 Transmit First Flag

Writing a logic 1 to this write-only bit will clear the TX1ST bit if it is set. Writing a logic 0 to the TX1STR has no effect. Reset clears this bit.

OSTALL0 — Endpoint 0 Force STALL Bit for OUT token

This read/write bit causes endpoint 0 to return a STALL handshake when polled by an OUT token by the USB host controller. Reset clears this bit.

1 = Send STALL handshake

0 = Default

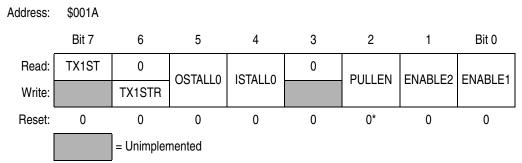

#### 9.8.13 USB Endpoint 1 Data Registers

#### Figure 9-27. USB Endpoint 1 Data Registers (UE1D0–UE1D7)

UE1Tx7–UE1Tx0 — Endpoint 1 Transmit or Receive Data Buffer

These write-only buffers are loaded by software with data to be sent on the USB bus on the next IN token directed at endpoint 1.

**Universal Serial Bus Module (USB)**

### 9.8.14 USB Endpoint 2 Data Registers

| Address:          | \$0030                | UE2D0           |                  |                  |                  |                  |                  |                       |

|-------------------|-----------------------|-----------------|------------------|------------------|------------------|------------------|------------------|-----------------------|

|                   | Bit 7                 | 6               | 5                | 4                | 3                | 2                | 1                | Bit 0                 |

| Read:             | UE2R07                | UE2R06          | UE2R05           | UE2R04           | UE2R03           | UE2R02           | UE2R01           | UE2R00                |

| Write:            | UE2T07                | UE2T06          | UE2T05           | UE2T04           | UE2T03           | UE2T02           | UE2T01           | UE2T00                |

| Reset:            |                       |                 |                  | Unaffecte        | d by reset       |                  |                  |                       |

|                   |                       |                 |                  |                  |                  |                  |                  |                       |

|                   | $\downarrow$          |                 |                  |                  |                  |                  |                  | $\downarrow$          |

| Address:          | ↓<br>\$0037           | UE2D7           |                  |                  |                  |                  |                  | $\downarrow$          |

| Address:<br>Read: | ↓<br>\$0037<br>UE2R77 | UE2D7<br>UE2R76 | UE2R75           | UE2R74           | UE2R73           | UE2R72           | UE2R71           | ↓<br>UE2R70           |

|                   | •                     |                 | UE2R75<br>UE2T75 | UE2R74<br>UE2T74 | UE2R73<br>UE2T73 | UE2R72<br>UE2T72 | UE2R71<br>UE2T71 | ↓<br>UE2R70<br>UE2T70 |

#### Figure 9-28. USB Endpoint 2 Data Registers (UE2D0–UE2D7)

UE2Rx7–UE2Rx0 — Endpoint 2 Receive Data Buffer

These read-only bits are serially loaded with OUT token data directed at endpoint 2. The data is received over the USB's D+ and D– pins.

UE2Tx7-UE2Tx0 — Endpoint 2 Transmit Data Buffer

These write-only buffers are loaded by software with data to be sent on the USB bus on the next IN token directed at endpoint 2.

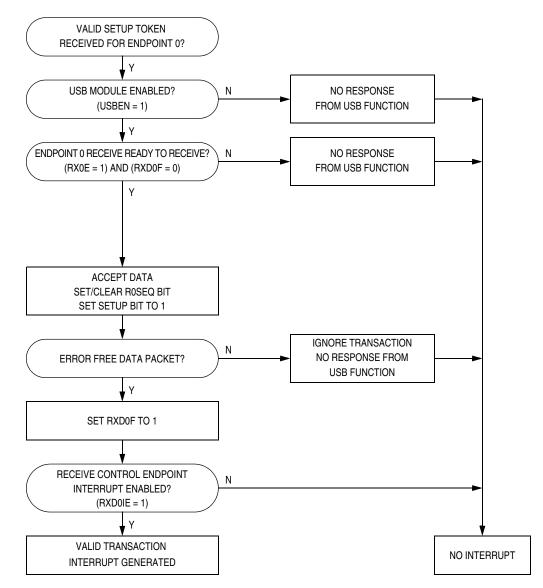

SETUP transactions cannot be stalled by the USB function. A SETUP received by a control endpoint will clear the ISTALL0 and OSTALL0 bits. The conditions for receiving a SETUP interrupt are shown in Figure 9-30.

#### 11.7.1 Wait Mode

The TIM remains active after the execution of a WAIT instruction. In wait mode the TIM registers are not accessible by the CPU. Any enabled CPU interrupt request from the TIM can bring the MCU out of wait mode.

If TIM functions are not required during wait mode, reduce power consumption by stopping the TIM before executing the WAIT instruction.

#### 11.7.2 Stop Mode

The TIM is inactive after the execution of a STOP instruction. The STOP instruction does not affect register conditions or the state of the TIM counter. TIM operation resumes when the MCU exits stop mode after an external interrupt.

#### **11.8 TIM During Break Interrupts**

A break interrupt stops the TIM counter.

The system integration module (SIM) controls whether status bits in other modules can be cleared during the break state. The BCFE bit in the break flag control register (BFCR) enables software to clear status bits during the break state. (See **8.8.3 Break Flag Control Register**.)

To allow software to clear status bits during a break interrupt, write a logic 1 to the BCFE bit. If a status bit is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect status bits during the break state, write a logic 0 to the BCFE bit. With BCFE at logic 0 (its default state), software can read and write I/O registers during the break state without affecting status bits. Some status bits have a 2-step read/write clearing procedure. If software does the first step on such a bit before the break, the bit cannot change during the break state as long as BCFE is at logic 0. After the break, doing the second step clears the status bit.

Technical Data

### 11.9 I/O Signals

Port E shares three of its pins with the TIM. PTE0/TCLK is an external clock input to the TIM prescaler. The two TIM channel I/O pins are PTE1/TCH0 and PTE2/TCH1.

#### 11.9.1 TIM Clock Pin (PTE0/TCLK)

PTE0/TCLK is an external clock input that can be the clock source for the TIM counter instead of the prescaled internal bus clock. Select the PTE0/TCLK input by writing logic 1s to the three prescaler select bits, PS[2:0]. (See **11.10.1 TIM Status and Control Register**.) The minimum TCLK pulse width, TCLK<sub>LMIN</sub> or TCLK<sub>HMIN</sub>, is:

$$\frac{1}{bus frequency} + t_{SU}$$

The maximum TCLK frequency is:

bus frequency ÷ 2

PTE0/TCLK is available as a general-purpose I/O pin when not used as the TIM clock input. When the PTE0/TCLK pin is the TIM clock input, it is an input regardless of the state of the DDRE0 bit in data direction register E.

#### 11.9.2 TIM Channel I/O Pins (PTE1/TCH0:PTE2/TCH1)

Each channel I/O pin is programmable independently as an input capture pin or an output compare pin. PTE1/TCH0 can be configured as buffered output compare or buffered PWM pins.

### 11.10 I/O Registers

The following I/O registers control and monitor operation of the TIM:

- TIM status and control register (TSC)

- TIM counter registers (TCNTH:TCNTL)

- TIM counter modulo registers (TMODH:TMODL)

- TIM channel status and control registers (TSC0 and TSC1)

- TIM channel registers (TCH0H:TCH0L and TCH1H:TCH1L)

#### MC68HC908JB8•MC68HC08JB8•MC68HC08JT8 - Rev. 2.3

When ELSxB:ELSxA = 0:0, this read/write bit selects the initial output level of the TCHx pin. (See **Table 11-3**.) Reset clears the MSxA bit.

- 1 = Initial output level low

- 0 = Initial output level high

- **NOTE:** Before changing a channel function by writing to the MSxB or MSxA bit, set the TSTOP and TRST bits in the TIM status and control register (TSC).

ELSxB and ELSxA — Edge/Level Select Bits

When channel x is an input capture channel, these read/write bits control the active edge-sensing logic on channel x.

When channel x is an output compare channel, ELSxB and ELSxA control the channel x output behavior when an output compare occurs.

When ELSxB and ELSxA are both clear, channel x is not connected to port E, and pin PTEx/TCHx is available as a general-purpose I/O pin. Table 11-3 shows how ELSxB and ELSxA work. Reset clears the ELSxB and ELSxA bits.

| MSxB | MSxA | ELSxB | ELSxA | Mode                 | Configuration                                        |  |  |

|------|------|-------|-------|----------------------|------------------------------------------------------|--|--|

| x    | 0    | 0     | 0     | Output               | Pin under port control;<br>initial output level high |  |  |

| x    | 1    | 0     | 0     | Preset               | Pin under port control;<br>initial output level low  |  |  |

| 0    | 0    | 0     | 1     |                      | Capture on rising edge only                          |  |  |

| 0    | 0    | 1     | 0     | Input<br>Capture     | Capture on falling edge only                         |  |  |

| 0    | 0    | 1     | 1     | e aprai e            | Capture on rising or falling edge                    |  |  |

| 0    | 1    | 0     | 1     | Output               | Toggle output on compare                             |  |  |

| 0    | 1    | 1     | 0     | Compare              | Clear output on compare                              |  |  |

| 0    | 1    | 1     | 1     | or PWM               | Set output on compare                                |  |  |

| 1    | Х    | 0     | 1     | Buffered             | Toggle output on compare                             |  |  |

| 1    | Х    | 1     | 0     | Output<br>Compare or | Clear output on compare                              |  |  |

| 1    | Х    | 1     | 1     | Buffered<br>PWM      | Set output on compare                                |  |  |

Table 11-3. Mode, Edge, and Level Selection

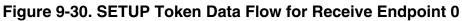

#### 12.3.2 Data Direction Register A

Data direction register A determines whether each port A pin is an input or an output. Writing a logic 1 to a DDRA bit enables the output buffer for the corresponding port A pin; a logic 0 disables the output buffer.

| Address:        | \$0004 |       |       |       |       |       |       |       |

|-----------------|--------|-------|-------|-------|-------|-------|-------|-------|

|                 | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| Read:<br>Write: | DDRA7  | DDRA6 | DDRA5 | DDRA4 | DDRA3 | DDRA2 | DDRA1 | DDRA0 |

| Reset:          | 0*     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

\* DDRA7 bit is reset by POR or LVI reset only.

DDRA[7:0] — Data Direction Register A Bits

These read/write bits control port A data direction. Reset clears DDRA[7:0], configuring all port A pins as inputs.

- 1 = Corresponding port A pin configured as output

- 0 = Corresponding port A pin configured as input

- **NOTE:** Avoid glitches on port A pins by writing to the port A data register before changing data direction register A bits from 0 to 1.

Figure 12-4 shows the port A I/O logic.

Figure 12-4. Port A I/O Circuit

MC68HC908JB8•MC68HC08JB8•MC68HC08JT8 — Rev. 2.3

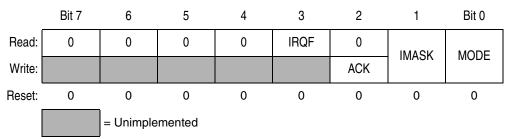

## 13.8 IRQ Status and Control Register

The IRQ status and control register (ISCR) controls and monitors operation of the IRQ module. The ISCR has the following functions:

- Shows the state of the IRQ flag

- Clears the IRQ latch

- Masks IRQ interrupt request

- Controls triggering sensitivity of the IRQ pin

Address: \$001E

IRQF — IRQ Flag

This read-only status bit is high when the IRQ interrupt is pending.

- 1 = IRQ interrupt pending

- 0 = IRQ interrupt not pending

ACK — IRQ Interrupt Request Acknowledge Bit

Writing a logic 1 to this write-only bit clears the IRQ latch. ACK always reads as logic 0. Reset clears ACK.

IMASK — IRQ Interrupt Mask Bit

Writing a logic 1 to this read/write bit disables IRQ interrupt requests. Reset clears IMASK.

- 1 = IRQ interrupt requests disabled

- 0 = IRQ interrupt requests enabled

- MODE IRQ Edge/Level Select Bit

This read/write bit controls the triggering sensitivity of the IRQ pin. Reset clears MODE.

$1 = \overline{IRQ}$  interrupt requests on falling edges and low levels

Technical Data

### Technical Data — MC68HC908JB8•MC68HC08JB8•MC68HC08JT8

# Section 15. Computer Operating Properly (COP)

#### 15.1 Contents

| 15.2 Introduction                 |

|-----------------------------------|

| 15.3 Functional Description       |

| 15.4 I/O Signals                  |

| 15.4.1 OSCXCLK                    |

| 15.4.2 STOP Instruction           |

| 15.4.3 COPCTL Write               |

| 15.4.4 Power-On Reset             |

| 15.4.5 Internal Reset             |

| 15.4.6 Reset Vector Fetch         |

| 15.4.7 COPD (COP Disable)         |

| 15.4.8 COPRS (COP Rate Select)    |

| 15.5 COP Control Register         |

| 15.6 Interrupts                   |

| 15.7 Monitor Mode                 |

| 15.8 Low-Power Modes              |

| 15.8.1 Wait Mode                  |

| 15.8.2 Stop Mode                  |

| 15.9 COP Module During Break Mode |

### 15.2 Introduction

The computer operating properly (COP) module contains a free-running counter that generates a reset if allowed to overflow. The COP module helps software recover from runaway code. Prevent a COP reset by clearing the COP counter periodically. The COP module can be disabled through the COPD bit in the CONFIG register.

MC68HC908JB8•MC68HC08JB8•MC68HC08JT8 — Rev. 2.3

COPRS — COP Rate Select Bit

COPRS selects the COP timeout period. Reset clears COPRS.

- 1 = COP timeout period is  $(2^{13} 2^4) \times OSCXOUT$  cycles

- 0 = COP timeout period is  $(2^{18} 2^4) \times OSCXOUT$  cycles

- COPD COP Disable Bit

COPD disables the COP module.

- 1 = COP module disabled

- 0 = COP module enabled

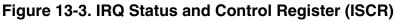

### 15.5 COP Control Register

The COP control register is located at address \$FFFF and overlaps the reset vector. Writing any value to \$FFFF clears the COP counter and starts a new timeout period. Reading location \$FFFF returns the low byte of the reset vector.

Address: \$FFFF

### Figure 15-3. COP Control Register (COPCTL)

### 15.6 Interrupts

The COP does not generate CPU interrupt requests.

### 15.7 Monitor Mode

The COP is disabled in monitor mode when  $V_{DD} + V_{HI}$  is present on the IRQ pin or on the RST pin.

### A.5 Reserved Registers

The two registers at \$FE08 and \$FE09 are reserved locations on the MC68HC08JB8.

On the MC68HC908JB8, these two locations are the FLASH control register and the FLASH block protect register respectively.

#### A.6 Monitor ROM

The monitor program (monitor ROM: \$FE10–\$FFDF) on the MC68HC08JB8 is for device testing only. \$FC00–\$FDFF are unused.

### A.7 Electrical Specifications

Electrical specifications for the MC68HC908JB8 apply to the MC68HC08JB8, except for the parameters indicated below.

MC68HC908JB8•MC68HC08JB8•MC68HC08JT8 — Rev. 2.3