Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                               |

| Number of I/O              | 24                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 5x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-VQFN Exposed Pad                                                      |

| Supplier Device Package    | 28-QFN (6x6)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f913-e-ml |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 1-1: PIC16F91X/946 PINOUT DESCRIPTIONS (CONTINUED)

|         | Name                                                         | Function    | Input<br>Type | Output<br>Type | Description                                                                            |  |

|---------|--------------------------------------------------------------|-------------|---------------|----------------|----------------------------------------------------------------------------------------|--|

| Vss     |                                                              | Vss         | Р             | _              | Ground reference for microcontroller.                                                  |  |

| Legend: | AN = Analog input<br>TTL = TTL compatib<br>HV = High Voltage | le input    | ST =          |                | compatible input or output OD = Open Drain<br>Trigger input with CMOS levels P = Power |  |

| Noto 1  | COM3 is available on                                         | DA3 for the |               | 013/016 9      | nd on PD0 for the PIC16E014/017 and PIC16E046                                          |  |

Note 1: COM3 is available on RA3 for the PIC16F913/916 and on RD0 for the PIC16F914/917 and PIC16F946.

2: Pins available on PIC16F914/917 and PIC16F946 only.

**3:** Pins available on PIC16F946 only.

4: I<sup>2</sup>C Schmitt trigger inputs have special input levels.

### 3.3 PORTB and TRISB Registers

PORTB is an 8-bit bidirectional I/O port. All PORTB pins can have a weak pull-up feature, and PORTB<7:4> implements an interrupt-on-input change function.

PORTB is also used for the Serial Flash programming interface and ICD interface.

#### EXAMPLE 3-2: INITIALIZING PORTB

| ;Init PORTB            |

|------------------------|

| ;                      |

| ;Set RB<7:0> as inputs |

| ;                      |

|                        |

### 3.4 Additional PORTB Pin Functions

RB<7:6> are used as data and clock signals, respectively, for both serial programming and the in-circuit debugger features on the device. Also, RB0 can be configured as an external interrupt input.

#### 3.4.1 WEAK PULL-UPS

Each of the PORTB pins has an individually configurable internal weak pull-up. Control bits WPUB<7:0> enable or disable each pull-up. Refer to Register 3-7. Each weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset by the RBPU bit of the OPTION register.

#### 3.4.2 INTERRUPT-ON-CHANGE

Four of the PORTB pins are individually configurable as an interrupt-on-change pin. Control bits IOCB<7:4> enable or disable the interrupt function for each pin. Refer to Register 3-6. The interrupt-on-change feature is disabled on a Power-on Reset.

For enabled interrupt-on-change pins, the values are compared with the old value latched on the last read of PORTB. The 'mismatch' outputs of the last read are OR'd together to set the PORTB Change Interrupt flag bit (RBIF) in the INTCON register (Register 2-3).

This interrupt can wake the device from Sleep. The user, in the Interrupt Service Routine, clears the interrupt by:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear the flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading or writing PORTB will end the mismatch condition and allow flag bit RBIF to be cleared. The latch holding the last read value is not affected by a MCLR nor Brown-out Reset. After these Resets, the RBIF flag will continue to be set if a mismatch is present.

| Note: | If a change on the I/O pin should occur<br>when the read operation is being executed<br>(start of the Q2 cycle), then the RBIF |  |  |  |  |  |  |

|-------|--------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|       | interrupt flag may not get set. Furthermore, since a read or write on a port affects all bits                                  |  |  |  |  |  |  |

|       | of that port, care must be taken when using                                                                                    |  |  |  |  |  |  |

|       | multiple pins in Interrupt-on-change mode.                                                                                     |  |  |  |  |  |  |

|       | Changes on one pin may not be seen while                                                                                       |  |  |  |  |  |  |

|       | servicing changes on another pin.                                                                                              |  |  |  |  |  |  |

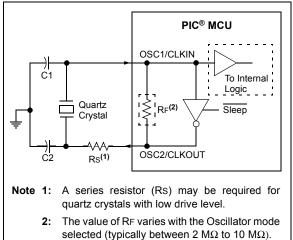

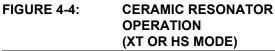

## 4.4.3 LP, XT, HS MODES

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 4-3). The mode selects a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

**LP** Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is designed to drive only 32.768 kHz tuning-fork type crystals (watch crystals).

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 4-3 and Figure 4-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

- Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- **2:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Applications Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices" (DS00826)

- AN849, "Basic PIC<sup>®</sup> Oscillator Design" (DS00849)

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design" (DS00943)

- AN949, "Making Your Oscillator Work" (DS00949)

- 2: The value of RF varies with the Oscillator mode selected (typically between 2 M $\Omega$  to 10 M $\Omega$ ).

- **3:** An additional parallel feedback resistor (RP) may be required for proper ceramic resonator operation.

## 4.8 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the device to continue operating should the external oscillator fail. The FSCM can detect oscillator failure any time after the Oscillator Start-up Timer (OST) has expired. The FSCM is enabled by setting the FCMEN bit in the Configuration Word register (CONFIG). The FSCM is applicable to all external oscillator modes (LP, XT, HS, EC, RC and RCIO).

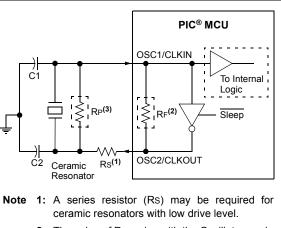

FIGURE 4-8: FSCM BLOCK DIAGRAM

### 4.8.1 FAIL-SAFE DETECTION

The FSCM module detects a failed oscillator by comparing the external oscillator to the FSCM sample clock. The sample clock is generated by dividing the LFINTOSC by 64. See Figure 4-8. Inside the fail detector block is a latch. The external clock sets the latch on each falling edge of the external clock. The sample clock clears the latch on each rising edge of the sample clock. A failure is detected when an entire half-cycle of the sample clock elapses before the primary clock goes low.

## 4.8.2 FAIL-SAFE OPERATION

When the external clock fails, the FSCM switches the device clock to an internal clock source and sets the bit flag OSFIF of the PIR2 register. Setting this flag will generate an interrupt if the OSFIE bit of the PIE2 register is also set. The device firmware can then take steps to mitigate the problems that may arise from a failed clock. The system clock will continue to be sourced from the internal clock source until the device firmware successfully restarts the external oscillator and switches back to external operation.

The internal clock source chosen by the FSCM is determined by the IRCF<2:0> bits of the OSCCON register. This allows the internal oscillator to be configured before a failure occurs.

## 4.8.3 FAIL-SAFE CONDITION CLEARING

The Fail-Safe condition is cleared after a Reset, executing a SLEEP instruction or toggling the SCS bit of the OSCCON register. When the SCS bit is toggled, the OST is restarted. While the OST is running, the device continues to operate from the INTOSC selected in OSCCON. When the OST times out, the Fail-Safe condition is cleared and the device will be operating from the external clock source. The Fail-Safe condition must be cleared before the OSFIF flag can be cleared.

#### 4.8.4 RESET OR WAKE-UP FROM SLEEP

The FSCM is designed to detect an oscillator failure after the Oscillator Start-up Timer (OST) has expired. The OST is used after waking up from Sleep and after any type of Reset. The OST is not used with the EC or RC Clock modes so that the FSCM will be active as soon as the Reset or wake-up has completed. When the FSCM is enabled, the Two-Speed Start-up is also enabled. Therefore, the device will always be executing code while the OST is operating.

Note: Due to the wide range of oscillator start-up times, the Fail-Safe circuit is not active during oscillator start-up (i.e., after exiting Reset or Sleep). After an appropriate amount of time, the user should check the OSTS bit of the OSCCON register to verify the oscillator start-up and that the system clock switchover has successfully completed.

| REGISTER /      | -1. 1200                    |                  |               | LOISTER           |                 |                |         |

|-----------------|-----------------------------|------------------|---------------|-------------------|-----------------|----------------|---------|

| U-0             | R/W-0                       | R/W-0            | R/W-0         | R/W-0             | R/W-0           | R/W-0          | R/W-0   |

| —               | TOUTPS3                     | TOUTPS2          | TOUTPS1       | TOUTPS0           | TMR2ON          | T2CKPS1        | T2CKPS0 |

| bit 7           | ·                           |                  |               |                   |                 | ·              | bit 0   |

|                 |                             |                  |               |                   |                 |                |         |

| Legend:         |                             |                  |               |                   |                 |                |         |

| R = Readable    | bit                         | W = Writable     | bit           | U = Unimplen      | nented bit, rea | d as '0'       |         |

| -n = Value at F | POR                         | '1' = Bit is set |               | '0' = Bit is clea | ared            | x = Bit is unk | nown    |

|                 |                             |                  |               |                   |                 |                |         |

| bit 7           | Unimplemen                  | ted: Read as '   | 0'            |                   |                 |                |         |

| bit 6-3         | -                           | )>: Timer2 Out   |               | Select bits       |                 |                |         |

|                 | 0000 <b>= 1:1 P</b>         |                  |               |                   |                 |                |         |

|                 | 0001 <b>= 1:2</b> P         |                  |               |                   |                 |                |         |

|                 | 0010 <b>= 1:3 P</b>         | ostscaler        |               |                   |                 |                |         |

|                 | 0011 <b>= 1:4 P</b>         | ostscaler        |               |                   |                 |                |         |

|                 | 0100 <b>= 1:5 P</b>         |                  |               |                   |                 |                |         |

|                 | 0101 <b>= 1:6 P</b>         |                  |               |                   |                 |                |         |

|                 | 0110 = 1:7 P                |                  |               |                   |                 |                |         |

|                 | 0111 = 1:8 P                |                  |               |                   |                 |                |         |

|                 | 1000 = 1:9 P<br>1001 = 1:10 |                  |               |                   |                 |                |         |

|                 | 1010 = 1.101                |                  |               |                   |                 |                |         |

|                 | 1011 = 1:12                 |                  |               |                   |                 |                |         |

|                 | 1100 = 1:13                 |                  |               |                   |                 |                |         |

|                 | 1101 <b>= 1:14</b>          | Postscaler       |               |                   |                 |                |         |

|                 | 1110 <b>= 1:15</b>          | Postscaler       |               |                   |                 |                |         |

|                 | 1111 = 1:16                 | Postscaler       |               |                   |                 |                |         |

| bit 2           | TMR2ON: Tir                 | mer2 On bit      |               |                   |                 |                |         |

|                 | 1 = Timer2 is               |                  |               |                   |                 |                |         |

|                 | 0 = Timer2 is               | s off            |               |                   |                 |                |         |

| bit 1-0         | T2CKPS<1:0                  | >: Timer2 Cloc   | k Prescale Se | lect bits         |                 |                |         |

|                 | 00 = Prescale               | er is 1          |               |                   |                 |                |         |

|                 | 01 = Prescale               |                  |               |                   |                 |                |         |

|                 | 1x = Prescale               | er is 16         |               |                   |                 |                |         |

| TABLE 7-1:      |                             | V OF REGIS       | TERS ASSO     | CIATED WITH       |                 |                |         |

|                 |                             |                  |               |                   |                 |                |         |

### REGISTER 7-1: T2CON: TIMER 2 CONTROL REGISTER

| Name   | Bit 7                                        | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|----------------------------------------------|---------|---------|---------|---------|--------|---------|---------|----------------------|---------------------------------|

| INTCON | GIE                                          | PEIE    | T0IE    | INTE    | RBIE    | T0IF   | INTF    | RBIF    | x000 0000x           | 0000 000x                       |

| PIE1   | EEIE                                         | ADIE    | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000 0000            | 0000 0000                       |

| PIR1   | EEIF                                         | ADIF    | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000 0000            | 0000 0000                       |

| PR2    | Timer2 Module Period Register                |         |         |         |         |        |         |         | 1111 1111            | 1111 1111                       |

| TMR2   | Holding Register for the 8-bit TMR2 Register |         |         |         |         |        |         |         | 0000 0000            | 0000 0000                       |

| T2CON  | —                                            | TOUTPS3 | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000            | -000 0000                       |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for Timer2 module.

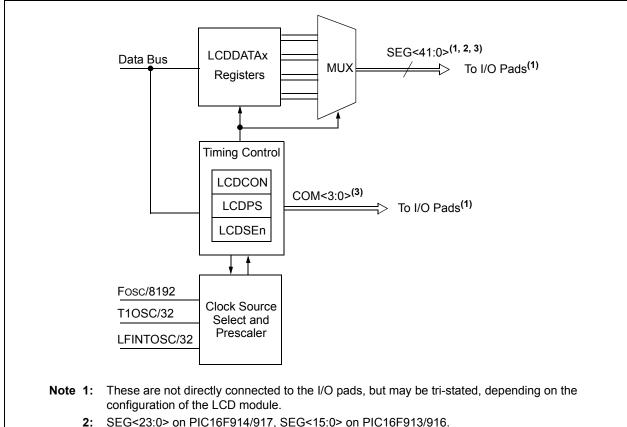

## 10.0 LIQUID CRYSTAL DISPLAY (LCD) DRIVER MODULE

The Liquid Crystal Display (LCD) driver module generates the timing control to drive a static or multiplexed LCD panel. In the PIC16F913/916 devices, the module drives the panels of up to four commons and up to 16 segments. In the PIC16F914/917 devices, the module drives the panels of up to four commons and up to 24 segments. In the PIC16F946 device, the module drives the panels of up to four commons and up to 42 segments. The LCD module also provides control of the LCD pixel data.

The LCD driver module supports:

- Direct driving of LCD panel

- Three LCD clock sources with selectable prescaler

- Up to four commons:

- Static (1 common)

- 1/2 multiplex (2 commons)

- 1/3 multiplex (3 commons)

- 1/4 multiplex (4 commons)

- Segments up to:

- 16 (PIC16F913/916)

- 24 (PIC16F914/917)

- 42 (PIC16F946)

- Static, 1/2 or 1/3 LCD Bias

| Note: | COM3 and SEG15 share the same         |

|-------|---------------------------------------|

|       | physical pin on the PIC16F913/916,    |

|       | therefore SEG15 is not available when |

|       | using 1/4 multiplex displays.         |

## 10.1 LCD Registers

The module contains the following registers:

- LCD Control Register (LCDCON)

- LCD Phase Register (LCDPS)

- Up to 6 LCD Segment Enable Registers (LCDSEn)

- Up to 24 LCD Data Registers (LCDDATA)

#### TABLE 10-1: LCD SEGMENT AND DATA REGISTERS

| Device        | # of LCD Registers |      |  |  |  |

|---------------|--------------------|------|--|--|--|

| Device        | Segment Enable     | Data |  |  |  |

| PIC16F913/916 | 2                  | 8    |  |  |  |

| PIC16F914/917 | 3                  | 12   |  |  |  |

| PIC16F946     | 6                  | 24   |  |  |  |

The LCDCON register (Register 10-1) controls the operation of the LCD driver module. The LCDPS register (Register 10-2) configures the LCD clock source prescaler and the type of waveform; Type-A or Type-B. The LCDSE registers (Register 10-3) configure the functions of the port pins.

The following LCDSE registers are available:

| • | LCDSE0 | SE<7:0>                  |

|---|--------|--------------------------|

| • | LCDSE1 | SE<15:8>                 |

| • | LCDSE2 | SE<23:16>(1)             |

| • | LCDSE3 | SE<31:24> <sup>(2)</sup> |

| • | LCDSE4 | SE<39:32> <sup>(2)</sup> |

| • | LCDSE5 | SE<41:40> <sup>(2)</sup> |

| Note 1: | PIC16F914/917 and PIC16F946 only. |

|---------|-----------------------------------|

| 2:      | PIC16F946 only.                   |

|         |                                   |

Once the module is initialized for the LCD panel, the individual bits of the LCDDATA<11:0> registers are cleared/set to represent a clear/dark pixel, respectively:

| • | LCDDATA0  | SEG<7:0>COM0   |

|---|-----------|----------------|

| • | LCDDATA1  | SEG<15:8>COM0  |

| • | LCDDATA2  | SEG<23:16>COM0 |

| • | LCDDATA3  | SEG<7:0>COM1   |

| • | LCDDATA4  | SEG<15:8>COM1  |

| • | LCDDATA5  | SEG<23:16>COM1 |

| • | LCDDATA6  | SEG<7:0>COM2   |

| • | LCDDATA7  | SEG<15:8>COM2  |

| • | LCDDATA8  | SEG<23:16>COM2 |

| • | LCDDATA9  | SEG<7:0>COM3   |

| • | LCDDATA10 | SEG<15:8>COM3  |

| • | LCDDATA11 | SEG<23:16>COM3 |

| _ |           |                |

The following additional registers are available on the PIC16F946 only:

| • LC | DDA | TA12 | SEG<  | 31:24> | СОМО  |    |

|------|-----|------|-------|--------|-------|----|

| • LC | DDA | TA13 | SEG<  | 39:32> | ·COM0 |    |

| • LC | DDA | TA14 | SEG<4 | 41:40> | ·COM0 |    |

| • LC | DDA | TA15 | SEG<  | 31:24> | ·COM1 |    |

| • LC | DDA | TA16 | SEG<  | 39:32> | ·COM1 |    |

| • LC | DDA | TA17 | SEG<4 | 41:40> | ·COM1 |    |

| • LC | DDA | TA18 | SEG<  | 31:24> | ·COM2 |    |

| • LC | DDA | TA19 | SEG<  | 39:32> | ·COM2 |    |

| • LC | DDA | TA20 | SEG<4 | 41:40> | ·COM2 |    |

| • LC | DDA | TA21 | SEG<  | 31:24> | ·COM3 |    |

| • LC | DDA | TA22 | SEG<  | 39:32> | ·COM3 |    |

| • LC | DDA | TA23 | SEG<4 | 41:40> | ·COM3 |    |

| As   | an  | exam | nple, | LCDD   | ATAx  | is |

As an example, LCDDATAx is detailed in Register 10-4.

Once the module is configured, the LCDEN bit of the LCDCON register is used to enable or disable the LCD module. The LCD panel can also operate during Sleep by clearing the SLPEN bit of the LCDCON register.

| Note: | The LCDDATA2, LCDDATA5, LCDDATA8 |  |  |  |  |  |

|-------|----------------------------------|--|--|--|--|--|

|       | and LCDDATA11 registers are not  |  |  |  |  |  |

|       | implemented in the PIC16F913/916 |  |  |  |  |  |

|       | devices.                         |  |  |  |  |  |

## FIGURE 10-1: LCD DRIVER MODULE BLOCK DIAGRAM

**3:** COM3 and SEG15 share the same physical pin on the PIC16F913/916, therefore SEG15 is not available when using 1/4 multiplex displays.

## 12.1 ADC Configuration

When configuring and using the ADC the following functions must be considered:

- Port configuration

- · Channel selection

- ADC voltage reference selection

- ADC conversion clock source

- Interrupt control

- Results formatting

#### 12.1.1 PORT CONFIGURATION

The ADC can be used to convert both analog and digital signals. When converting analog signals, the I/O pin should be configured for analog by setting the associated TRIS and ANSEL bits. See the corresponding Port section for more information.

| Note: | Analog voltages on any pin that is defined |

|-------|--------------------------------------------|

|       | as a digital input may cause the input     |

|       | buffer to conduct excess current.          |

### 12.1.2 CHANNEL SELECTION

The CHS bits of the ADCON0 register determine which channel is connected to the sample and hold circuit.

When changing channels, a delay is required before starting the next conversion. Refer to **Section 12.2 "ADC Operation"** for more information.

## 12.1.3 ADC VOLTAGE REFERENCE

The VCFG bits of the ADCON0 register provide independent control of the positive and negative voltage references. The positive voltage reference can be either VDD or an external voltage source. Likewise, the negative voltage reference can be either Vss or an external voltage source.

## 12.1.4 CONVERSION CLOCK

The source of the conversion clock is software selectable via the ADCS bits of the ADCON1 register. There are seven possible clock options:

- Fosc/2

- Fosc/4

- Fosc/8

- Fosc/16

- Fosc/32

- Fosc/64

- FRC (dedicated internal oscillator)

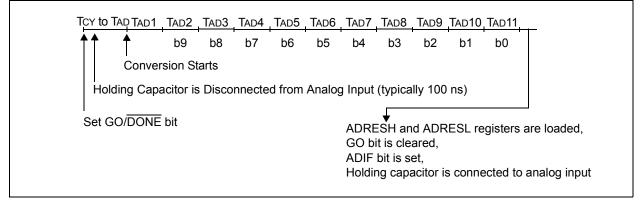

The time to complete one bit conversion is defined as TAD. One full 10-bit conversion requires 11 TAD periods as shown in Figure 12-3.

For correct conversion, the appropriate TAD specification must be met. See A/D conversion requirements in **Section 19.0 "Electrical Specifications"** for more information. Table 12-1 gives examples of appropriate ADC clock selections.

**Note:** Unless using the FRC, any changes in the system clock frequency will change the ADC clock frequency, which may adversely affect the ADC result.

#### TABLE 12-1: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES (VDD > 3.0V)

| ADC Clock        | Period (TAD) | Device Frequency (Fosc) |                         |                         |                         |

|------------------|--------------|-------------------------|-------------------------|-------------------------|-------------------------|

| ADC Clock Source | ADCS<2:0>    | 20 MHz                  | 8 MHz                   | 4 MHz                   | 1 MHz                   |

| Fosc/2           | 000          | 100 ns <sup>(2)</sup>   | 250 ns <sup>(2)</sup>   | 500 ns <sup>(2)</sup>   | 2.0 μs                  |

| Fosc/4           | 100          | 200 ns <sup>(2)</sup>   | 500 ns <sup>(2)</sup>   | 1.0 μs <sup>(2)</sup>   | 4.0 μs                  |

| Fosc/8           | 001          | 400 ns <sup>(2)</sup>   | 1.0 μs <sup>(2)</sup>   | 2.0 μs                  | 8.0 μs <sup>(3)</sup>   |

| Fosc/16          | 101          | 800 ns <sup>(2)</sup>   | 2.0 μs                  | 4.0 μs                  | 16.0 μs <sup>(3)</sup>  |

| Fosc/32          | 010          | 1.6 μs                  | 4.0 μs                  | 8.0 μs <sup>(3)</sup>   | 32.0 μs <sup>(3)</sup>  |

| Fosc/64          | 110          | 3.2 μs                  | 8.0 μs <sup>(3)</sup>   | 16.0 μs <sup>(3)</sup>  | 64.0 μs <sup>(3)</sup>  |

| Frc              | x11          | 2-6 μs <sup>(1,4)</sup> | 2-6 μs <sup>(1,4)</sup> | 2-6 μs <sup>(1,4)</sup> | 2-6 μs <sup>(1,4)</sup> |

**Legend:** Shaded cells are outside of recommended range.

**Note 1:** The FRC source has a typical TAD time of 4  $\mu$ s for VDD > 3.0V.

2: These values violate the minimum required TAD time.

- **3:** For faster conversion times, the selection of another clock source is recommended.

- 4: When the device frequency is greater than 1 MHz, the FRC clock source is only recommended if the conversion will be performed during Sleep.

#### FIGURE 12-2: ANALOG-TO-DIGITAL CONVERSION TAD CYCLES

#### 12.1.5 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital conversion. The ADC interrupt flag is the ADIF bit in the PIR1 register. The ADC interrupt enable is the ADIE bit in the PIE1 register. The ADIF bit must be cleared in software.

| Note: | The ADIF bit is set at the completion of |

|-------|------------------------------------------|

|       | every conversion, regardless of whether  |

|       | or not the ADC interrupt is enabled.     |

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake-up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake-up from Sleep and resume in-line code execution, the global interrupt must be disabled. If the global interrupt is enabled, execution will switch to the Interrupt Service Routine.

Please see **Section 12.1.5** "Interrupts" for more information.

© 2007 Microchip Technology Inc.

#### 13.1.2 READING THE DATA EEPROM MEMORY

To read a data memory location, the user must write the address to the EEADRL register, clear the EEPGD control bit, and then set control bit RD of the EECON1 register. The data is available in the very next cycle, in the EEDATL register; therefore, it can be read in the next instruction. EEDATL will hold this value until another read or until it is written to by the user (during a write operation).

| EXAMPLE 13-1: | DATA EEPROM READ |

|---------------|------------------|

|               |                  |

| BANKSEL | EEADRL         | ;                |

|---------|----------------|------------------|

| MOVF    | DATA_EE_ADDR,W | ;Data Memory     |

| MOVWF   | EEADRL         | ;Address to read |

| BANKSEL | EECON1         | i                |

| BCF     | EECON1, EEPGD  | ;Point to Data   |

|         |                | ;memory          |

| BSF     | EECON1,RD      | ;EE Read         |

| BANKSEL | EEDATL         | i                |

| MOVF    | EEDATL,W       | ;W = EEPROM Data |

|         |                |                  |

## 13.1.3 WRITING TO THE DATA EEPROM MEMORY

To write an EEPROM data location, the user must first write the address to the EEADRL register and the data to the EEDATL register. Then the user must follow a specific sequence to initiate the write for each byte.

The write will not initiate if the sequence described below is not followed exactly (write 55h to EECON2, write AAh to EECON2, then set WR bit) for each byte. Interrupts should be disabled during this code segment.

Additionally, the WREN bit in EECON1 must be set to enable write. This mechanism prevents accidental writes to data EEPROM due to errant (unexpected) code execution (i.e., lost programs). The user should keep the WREN bit clear at all times, except when updating EEPROM. The WREN bit is not cleared by hardware.

After a write sequence has been initiated, clearing the WREN bit will not affect this write cycle. The WR bit will be inhibited from being set unless the WREN bit is set.

At the completion of the write cycle, the WR bit is cleared in hardware and the EE Write Complete Interrupt Flag bit (EEIF) is set. The user can either enable this interrupt or poll this bit. EEIF must be cleared by software. The steps to write to EEPROM data memory are:

- 1. If step 10 is not implemented, check the WR bit to see if a write is in progress.

- 2. Write the address to EEADRL. Make sure that the address is not larger than the memory size of the device.

- 3. Write the 8-bit data value to be programmed in the EEDATL register.

- 4. Clear the EEPGD bit to point to EEPROM data memory.

- 5. Set the WREN bit to enable program operations.

- 6. Disable interrupts (if enabled).

- 7. Execute the special five instruction sequence:

- Write 55h to EECON2 in two steps (first to W, then to EECON2)

- Write AAh to EECON2 in two steps (first to W, then to EECON2)

- Set the WR bit

- 8. Enable interrupts (if using interrupts).

- 9. Clear the WREN bit to disable program operations.

- At the completion of the write cycle, the WR bit is cleared and the EEIF interrupt flag bit is set. (EEIF must be cleared by firmware.) If step 1 is not implemented, then firmware should check for EEIF to be set, or WR to clear, to indicate the end of the program cycle.

#### EXAMPLE 13-2: DATA EEPROM WRITE

|   |             | BANKSEL                 | EECON1         | ;                  |

|---|-------------|-------------------------|----------------|--------------------|

|   |             | BTFSC                   | EECON1,WR      | ;Wait for write    |

|   |             | GOTO                    | \$-1           | ;to complete       |

|   |             | BANKSEL                 | EEADRL         | ;                  |

|   |             | MOVF                    | DATA_EE_ADDR,W | ;Data Memory       |

|   |             | MOVWF                   | EEADRL         | ;Address to write  |

|   |             | MOVF                    | DATA_EE_DATA,W | ;Data Memory Value |

|   |             | MOVWF                   | EEDATL         | ;to write          |

|   |             | BANKSEL                 | EECON1         | ;                  |

|   |             | BCF                     | EECON1, EEPGD  | ;Point to DATA     |

|   |             |                         |                | ;memory            |

|   |             | BSF                     | EECON1,WREN    | ;Enable writes     |

|   |             |                         |                |                    |

|   |             | BCF                     | INTCON,GIE     | ;Disable INTs.     |

| ſ |             | MOVLW                   | 55h            | ;                  |

|   | g g         | MOVWF<br>MOVLW<br>MOVWF | EECON2         | ;Write 55h         |

|   | uire<br>Jen | MOVLW                   | AAh            | ;                  |

|   | equ         | MOVWF                   | EECON2         | ;Write AAh         |

|   | шv          | BSF                     | EECON1,WR      | ;Set WR bit to     |

| l |             |                         |                | ;begin write       |

|   |             | BSF                     | INTCON,GIE     | ;Enable INTs.      |

|   |             | BCF                     | EECON1,WREN    | ;Disable writes    |

|   |             |                         |                |                    |

## 16.2.1 POWER-ON RESET (POR)

The on-chip POR circuit holds the chip in Reset until VDD has reached a high enough level for proper operation. To take advantage of the POR, simply connect the MCLR pin through a resistor to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A maximum rise time for VDD is required. See **Section 19.0 "Electrical Specifications**" for details. If the BOR is enabled, the maximum rise time specification does not apply. The BOR circuitry will keep the device in Reset until VDD reaches VBOR (see **Section 16.2.4 "Brown-Out Reset (BOR)"**).

Note: The POR circuit does not produce an internal Reset when VDD declines. To re-enable the POR, VDD must reach Vss for a minimum of 100 μs.

When the device starts normal operation (exits the Reset condition), device operating parameters (i.e., voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

For additional information, refer to Application Note AN607, *"Power-up Trouble Shooting"* (DS00607).

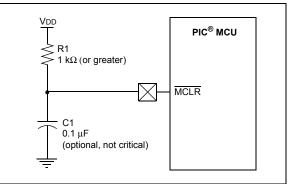

### 16.2.2 MCLR

PIC16F91X/946 has a noise filter in the  $\overline{\text{MCLR}}$  Reset path. The filter will detect and ignore small pulses.

It should be noted that a WDT Reset does not drive MCLR pin low.

Voltages applied to the pin that exceed its specification can result in both MCLR Resets and excessive current beyond the device specification during the ESD event. For this reason, Microchip recommends that the MCLR pin no longer be tied directly to VDD. The use of an RC network, as shown in Figure 16-2, is suggested.

An internal  $\overline{\text{MCLR}}$  option is enabled by clearing the  $\overline{\text{MCLRE}}$  bit in the Configuration Word register. When  $\overline{\text{MCLRE}} = 0$ , the Reset signal to the chip is generated internally. When the  $\overline{\text{MCLRE}} = 1$ , the RE3/ $\overline{\text{MCLR}}$  pin becomes an external Reset input. In this mode, the RE3/ $\overline{\text{MCLR}}$  pin has a weak pull-up to VDD. In-Circuit Serial Programming is not affected by selecting the internal  $\overline{\text{MCLR}}$  option.

#### FIGURE 16-2: F

####

## 16.2.3 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 64 ms (nominal) time-out on power-up only, from POR or Brown-out Reset. The Power-up Timer operates from the 31 kHz LFINTOSC oscillator. For more information, see **Section 4.5 "Internal Clock Modes"**. The chip is kept in Reset as long as PWRT is active. The PWRT delay allows the VDD to rise to an acceptable level. A Configuration bit, PWRTE, can disable (if set) or enable (if cleared or programmed) the Power-up Timer. The Power-up Timer should be enabled when Brown-out Reset is enabled, although it is not required.

The Power-up Timer delay will vary from chip-to-chip and vary due to:

- VDD variation

- Temperature variation

- Process variation

See DC parameters for details (Section 19.0 "Electrical Specifications").

NOTES:

| RLF              | Rotate Left f through Carry                                                                                                                                                                                          |                                    |       |      |      |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-------|------|------|--|--|

| Syntax:          | [ label ]                                                                                                                                                                                                            | [ <i>label</i> ] RLF f,d           |       |      |      |  |  |

| Operands:        | • - · - ·                                                                                                                                                                                                            | $0 \le f \le 127$<br>$d \in [0,1]$ |       |      |      |  |  |

| Operation:       | See des                                                                                                                                                                                                              | scription I                        | belov | v    |      |  |  |

| Status Affected: | С                                                                                                                                                                                                                    |                                    |       |      |      |  |  |

| Description:     | The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry flag. If 'd' is '0', the<br>result is placed in the W register.<br>If 'd' is '1', the result is stored<br>back in register 'f'. |                                    |       |      |      |  |  |

| Words:           | 1                                                                                                                                                                                                                    |                                    |       |      |      |  |  |

| Cycles:          | 1                                                                                                                                                                                                                    |                                    |       |      |      |  |  |

| Example:         | RLF                                                                                                                                                                                                                  | REG1,                              | 0     |      |      |  |  |

|                  | Before                                                                                                                                                                                                               | Instructio                         | n     |      |      |  |  |

|                  | REG1 = 1110 01                                                                                                                                                                                                       |                                    |       |      | 0110 |  |  |

|                  | C = 0                                                                                                                                                                                                                |                                    |       |      |      |  |  |

|                  | After Instruction                                                                                                                                                                                                    |                                    |       |      |      |  |  |

|                  |                                                                                                                                                                                                                      | REG1                               | =     |      | 0110 |  |  |

|                  |                                                                                                                                                                                                                      | W                                  | =     | 1100 | 1100 |  |  |

|                  |                                                                                                                                                                                                                      | C                                  | =     | 1    |      |  |  |

| SLEEP            | Enter Sleep mode                                                                                                                                                                                                       |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SLEEP                                                                                                                                                                                                          |

| Operands:        | None                                                                                                                                                                                                                   |

| Operation:       | $\begin{array}{l} \text{00h} \rightarrow \text{WDT,} \\ 0 \rightarrow \text{WDT prescaler,} \\ 1 \rightarrow \overline{\text{TO}}, \\ 0 \rightarrow \overline{\text{PD}} \end{array}$                                  |

| Status Affected: | TO, PD                                                                                                                                                                                                                 |

| Description:     | The power-down Status bit, $\overline{PD}$ is cleared. Time-out Status bit, $\overline{TO}$ is set. Watchdog Timer and its prescaler are cleared.<br>The processor is put into Sleep mode with the oscillator stopped. |

| RRF              | Rotate Right f through Carry                                                                                                                                                                                                        |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                                            |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                  |

| Operation:       | See description below                                                                                                                                                                                                               |

| Status Affected: | С                                                                                                                                                                                                                                   |

| Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry flag. If 'd' is ' $^{0}$ ', the<br>result is placed in the W register.<br>If 'd' is ' $^{1}$ ', the result is placed<br>back in register 'f'. |

|                  | C Register f                                                                                                                                                                                                                        |

| SUBLW            | Subtract W                  | from literal                                                                             |  |  |  |

|------------------|-----------------------------|------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] SUBLW k    |                                                                                          |  |  |  |

| Operands:        | $0 \leq k \leq 255$         |                                                                                          |  |  |  |

| Operation:       | $k -(W) \to (W)$            | N)                                                                                       |  |  |  |

| Status Affected: | C, DC, Z                    |                                                                                          |  |  |  |

| Description:     | complemen<br>eight-bit lite | ster is subtracted (2's<br>t method) from the<br>ral 'k'. The result is<br>e W register. |  |  |  |

|                  | C = 0                       | W > k                                                                                    |  |  |  |

|                  | <b>C =</b> 1                | $W \leq k$                                                                               |  |  |  |

|                  | DC = 0                      | W<3:0> > k<3:0>                                                                          |  |  |  |

DC = 0 DC = 1

W<3:0> ≤ k<3:0>

## 18.11 PICSTART Plus Development Programmer

The PICSTART Plus Development Programmer is an easy-to-use, low-cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. The PICSTART Plus Development Programmer supports most PIC devices in DIP packages up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus Development Programmer is CE compliant.

## 18.12 PICkit 2 Development Programmer

The PICkit<sup>™</sup> 2 Development Programmer is a low-cost programmer and selected Flash device debugger with an easy-to-use interface for programming many of Microchip's baseline, mid-range and PIC18F families of Flash memory microcontrollers. The PICkit 2 Starter Kit includes a prototyping development board, twelve sequential lessons, software and HI-TECH's PICC<sup>™</sup> Lite C compiler, and is designed to help get up to speed quickly using PIC<sup>®</sup> microcontrollers. The kit provides everything needed to program, evaluate and develop applications using Microchip's powerful, mid-range Flash memory family of microcontrollers.

## 18.13 Demonstration, Development and Evaluation Boards

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart<sup>®</sup> battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Check the Microchip web page (www.microchip.com) and the latest *"Product Selector Guide"* (DS00148) for the complete list of demonstration, development and evaluation kits.

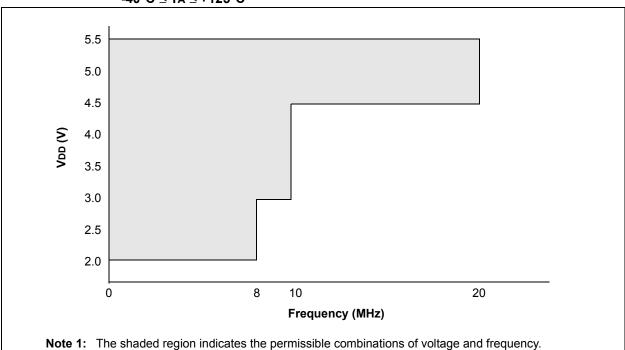

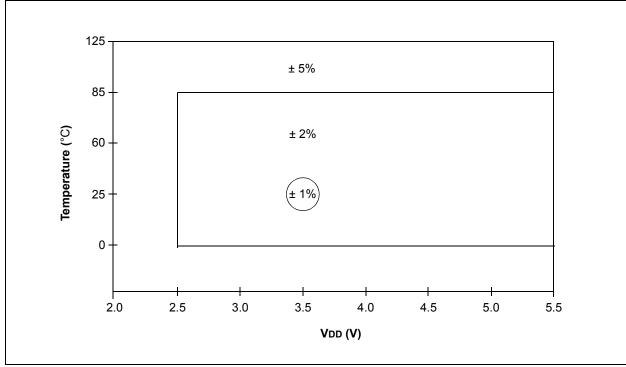

FIGURE 19-1: PIC16F913/914/916/917/946 VOLTAGE-FREQUENCY GRAPH, -40°C  $\leq$  TA  $\leq$  +125°C

#### PIC16F913/914/916/917/946-I (Industrial) 19.5 **DC Characteristics:** PIC16F913/914/916/917/946-E (Extended) (Continued)

| DC CHARACTERISTICS |       | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}\mbox{C} \leq \mbox{TA} \leq +85^{\circ}\mbox{C for industrial} \\ -40^{\circ}\mbox{C} \leq \mbox{TA} \leq +125^{\circ}\mbox{C for extended} \end{array}$ |      |      |      |       |                                                                        |

|--------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|------------------------------------------------------------------------|

| Param<br>No.       | Sym.  | Characteristic                                                                                                                                                                                                                                                                           | Min. | Typ† | Max. | Units | Conditions                                                             |

|                    |       | Capacitive Loading Specs on<br>Output Pins                                                                                                                                                                                                                                               |      |      |      |       |                                                                        |

| D101*              | COSC2 | OSC2 pin                                                                                                                                                                                                                                                                                 | _    | -    | 15   | pF    | In XT, HS and LP modes when<br>external clock is used to drive<br>OSC1 |

| D101A*             | Сю    | All I/O pins                                                                                                                                                                                                                                                                             | —    | _    | 50   | pF    |                                                                        |

|                    |       | Data EEPROM Memory                                                                                                                                                                                                                                                                       |      |      |      |       |                                                                        |

| D120               | ED    | Byte Endurance                                                                                                                                                                                                                                                                           | 100K | 1M   | _    | E/W   | $-40^{\circ}C \le TA \le +85^{\circ}C$                                 |

| D120A              | ED    | Byte Endurance                                                                                                                                                                                                                                                                           | 10K  | 100K | —    | E/W   | $+85^{\circ}C \le TA \le +125^{\circ}C$                                |

| D121               | Vdrw  | VDD for Read/Write                                                                                                                                                                                                                                                                       | VMIN | —    | 5.5  | V     | Using EECON1 to read/write<br>VMIN = Minimum operating<br>voltage      |

| D122               | TDEW  | Erase/Write Cycle Time                                                                                                                                                                                                                                                                   | _    | 5    | 6    | ms    |                                                                        |

| D123               | TRETD | Characteristic Retention                                                                                                                                                                                                                                                                 | 40   | _    | —    | Year  | Provided no other specifications are violated                          |

| D124               | TREF  | Number of Total Erase/Write<br>Cycles before Refresh <sup>(4)</sup>                                                                                                                                                                                                                      | 1M   | 10M  | —    | E/W   | $-40^{\circ}C \le TA \le +85^{\circ}C$                                 |

|                    |       | Program Flash Memory                                                                                                                                                                                                                                                                     |      |      |      |       |                                                                        |

| D130               | Eр    | Cell Endurance                                                                                                                                                                                                                                                                           | 10K  | 100K | —    | E/W   | $-40^{\circ}C \le TA \le +85^{\circ}C$                                 |

| D130A              | ED    | Cell Endurance                                                                                                                                                                                                                                                                           | 1K   | 10K  | _    | E/W   | +85°C ≤ TA ≤ +125°C                                                    |

| D131               | Vpr   | VDD for Read                                                                                                                                                                                                                                                                             | Vmin | -    | 5.5  | V     | VMIN = Minimum operating<br>voltage                                    |

| D132               | VPEW  | VDD for Erase/Write                                                                                                                                                                                                                                                                      | 4.5  | —    | 5.5  | V     |                                                                        |

| D133               | TPEW  | Erase/Write cycle time                                                                                                                                                                                                                                                                   | —    | —    | 3    | ms    |                                                                        |

| D134               | TRETD | Characteristic Retention                                                                                                                                                                                                                                                                 | 40   | -    | —    | Year  | Provided no other specifications are violated                          |

These parameters are characterized but not tested.

t Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

2: Negative current is defined as current sourced by the pin.

3: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

4: See Section 13.0 "Data EEPROM and Flash Program Memory Control" for additional information.

5: Including OSC2 in CLKOUT mode.

#### TABLE 19-9: PIC16F913/914/916/917/946 A/D CONVERSION REQUIREMENTS

| Param<br>No. | Sym. | Characteristic                                                        | Min. | Тур†         | Max. | Units | Conditions                                                                                                                                       |

|--------------|------|-----------------------------------------------------------------------|------|--------------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| AD130*       | TAD  | A/D Clock Period                                                      | 1.6  | _            | 9.0  | μs    | Tosc-based, VREF≥3.0V                                                                                                                            |

|              |      |                                                                       | 3.0  | —            | 9.0  | μs    | Tosc-based, VREF full range                                                                                                                      |

|              |      | A/D Internal RC<br>Oscillator Period                                  | 3.0  | 6.0          | 9.0  | μs    | ADCS<1:0> = 11 (ADRC mode)<br>At VDD = 2.5V                                                                                                      |

|              |      |                                                                       | 1.6  | 4.0          | 6.0  | μs    | At VDD = 5.0V                                                                                                                                    |

| AD131        | TCNV | Conversion Time<br>(not including<br>Acquisition Time) <sup>(1)</sup> | _    | 11           | _    | TAD   | Set GO/DONE bit to new data in A/D<br>Result register                                                                                            |

| AD132*       | TACQ | Acquisition Time                                                      |      | 11.5         |      | μs    |                                                                                                                                                  |

| AD133*       | TAMP | Amplifier Settling Time                                               |      | —            | 5    | μs    |                                                                                                                                                  |

| AD134        | Tgo  | Q4 to A/D Clock Start                                                 | _    | Tosc/2       | _    | —     |                                                                                                                                                  |

|              |      |                                                                       | _    | Tosc/2 + Tcy |      | _     | If the A/D clock source is selected as RC, a time of TcY is added before the A/D clock starts. This allows the SLEEP instruction to be executed. |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** ADRESH and ADRESL registers may be read on the following TCY cycle.

2: See Section 12.3 "A/D Acquisition Requirements" for minimum conditions.

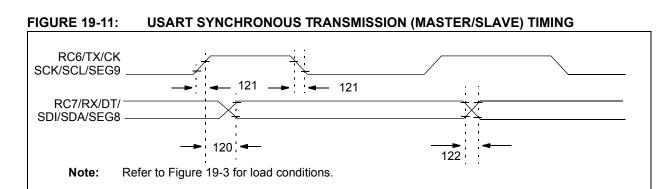

#### TABLE 19-10: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |         |                                   |          |      |       |            |  |  |

|----------------------------------------------------------------------------------------------------------------------|---------|-----------------------------------|----------|------|-------|------------|--|--|

| Param.<br>No.                                                                                                        | Symbol  | Characteristic                    | Min.     | Max. | Units | Conditions |  |  |

| 120                                                                                                                  | TCKH2DT | SYNC XMIT (Master and Slave)      | 3.0-5.5V |      | 80    | ns         |  |  |

| V                                                                                                                    |         | Clock high to data-out valid      | 2.0-5.5V |      | 100   | ns         |  |  |

| 121                                                                                                                  | TCKRF   | Clock out rise time and fall time | 3.0-5.5V |      | 45    | ns         |  |  |

|                                                                                                                      |         | (Master mode)                     | 2.0-5.5V |      | 50    | ns         |  |  |

| 122                                                                                                                  | TDTRF   | Data-out rise time and fall time  | 3.0-5.5V |      | 45    | ns         |  |  |

|                                                                                                                      |         |                                   | 2.0-5.5V | _    | 50    | ns         |  |  |

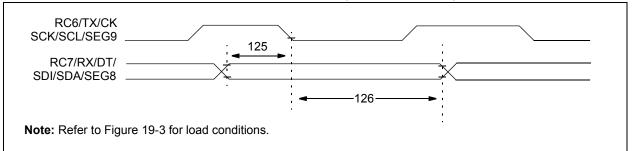

#### FIGURE 19-12: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

#### TABLE 19-11: USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |          |                                                                                |      |      |       |            |  |

|----------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------------|------|------|-------|------------|--|

| Param.<br>No.                                                                                                        | Symbol   | Characteristic                                                                 | Min. | Max. | Units | Conditions |  |

| 125                                                                                                                  | TDTV2CKL | SYNC RCV (Master and Slave)<br>Data-hold before CK $\downarrow$ (DT hold time) | 10   | _    | ns    |            |  |

| 126                                                                                                                  | TCKL2DTL | Data-hold after CK $\downarrow$ (DT hold time)                                 | 15   |      | ns    |            |  |

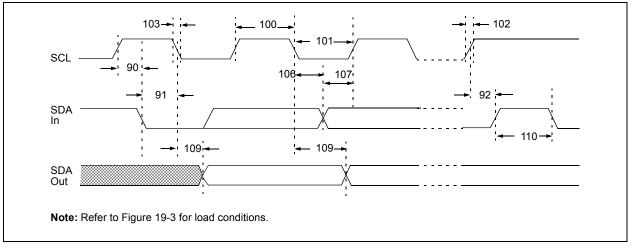

| TABLE 19-15: | I <sup>2</sup> C™ BUS | START/STOP | BITS REQUIREMENTS |

|--------------|-----------------------|------------|-------------------|

|--------------|-----------------------|------------|-------------------|

| Param<br>No. | Symbol  | Charact                       | Min.         | Тур. | Max. | Units | Conditions |                                                       |

|--------------|---------|-------------------------------|--------------|------|------|-------|------------|-------------------------------------------------------|

| 90*          | TSU:STA | Start condition<br>Setup time | 400 kHz mode | 600  | _    | —     | ns         | Only relevant for Repeated Start condition            |

| 91*          | THD:STA | Start condition<br>Hold time  | 400 kHz mode | 600  |      | —     | ns         | After this period, the first clock pulse is generated |

| 92*          | Tsu:sto | Stop condition<br>Setup time  | 400 kHz mode | 600  | —    | —     | ns         |                                                       |

| 93           | THD:STO | Stop condition<br>Hold time   | 400 kHz mode | 600  | —    | —     | ns         |                                                       |

\* These parameters are characterized but not tested.

## FIGURE 19-19: I<sup>2</sup>C<sup>™</sup> BUS DATA TIMING